# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32КВ (32К х 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20e15a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit    | 31             | 30  | 29    | 28 | 27          | 26      | 25      | 24 |

|--------|----------------|-----|-------|----|-------------|---------|---------|----|

|        | PROCESSOR[3:0] |     |       |    | FAMILY[4:1] |         |         |    |

| Access | R              | R   | R     | R  | R           | R       | R       | R  |

| Reset  | р              | р   | р     | р  | f           | f       | f       | f  |

|        |                |     |       |    |             |         |         |    |

| Bit    | 23             | 22  | 21    | 20 | 19          | 18      | 17      | 16 |

|        | FAMILY[0:0]    |     |       |    | SERIE       | ES[5:0] |         |    |

| Access | R              |     | R     | R  | R           | R       | R       | R  |

| Reset  | f              |     | S     | S  | S           | s       | S       | s  |

|        |                |     |       |    |             |         |         |    |

| Bit    | 15             | 14  | 13    | 12 | 11          | 10      | 9       | 8  |

|        |                | DIE | [3:0] |    |             | REVISI  | ON[3:0] |    |

| Access | R              | R   | R     | R  | R           | R       | R       | R  |

| Reset  | d              | d   | d     | d  | r           | r       | r       | r  |

|        |                |     |       |    |             |         |         |    |

| Bit    | 7              | 6   | 5     | 4  | 3           | 2       | 1       | 0  |

|        | DEVSEL[7:0]    |     |       |    |             |         |         |    |

| Access | R              | R   | R     | R  | R           | R       | R       | R  |

| Reset  | x              | x   | x     | x  | х           | x       | х       | x  |

#### Bits 31:28 – PROCESSOR[3:0]: Processor

The value of this field defines the processor used on the device.

### Bits 27:23 – FAMILY[4:0]: Product Family

The value of this field corresponds to the product family part of the ordering code.

#### Bits 21:16 – SERIES[5:0]: Product Series

The value of this field corresponds to the product series part of the ordering code.

#### Bits 15:12 – DIE[3:0]: Die Number

Identifies the die family.

#### Bits 11:8 - REVISION[3:0]: Revision Number

Identifies the die revision number. 0x0=rev.A, 0x1=rev.B etc.

**Note:** The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die.

## Bits 7:0 – DEVSEL[7:0]: Device Selection

This bit field identifies a device within a product family and product series. Refer to the ordering information for device configurations and corresponding values for Flash memory density, pin count, and device variant.

#### 13.13.10 CoreSight ROM Table Entry 0

Name:ENTRY0Offset:0x1000 [ID-00001c14]Reset:0xXXXXX00XProperty:PAC Write-Protection

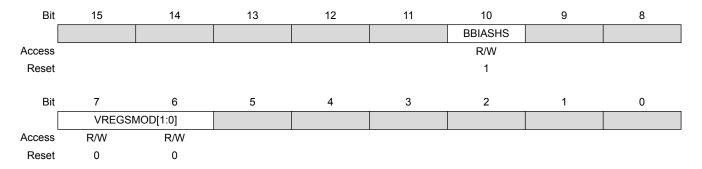

### 19.8.2 Standby Configuration

Name:STDBYCFGOffset:0x08 [ID-00000a2f]Reset:0x0400Property:PAC Write-Protection

## Bit 10 – BBIASHS: Back Bias for HMCRAMCHS

Refer to RAM Automatic Low Power Mode for details.

| Value | Description               |

|-------|---------------------------|

| 0     | No Back Biasing Mode      |

| 1     | Standby Back Biasing Mode |

## Bits 7:6 – VREGSMOD[1:0]: VREG Switching Mode

Refer to for Regulator Automatic Low Power Mode details.

| Value | Name        | Description                    |

|-------|-------------|--------------------------------|

| 0x0   | AUTO        | Automatic Mode                 |

| 0x1   | PERFORMANCE | Performance oriented           |

| 0x2   | LP          | Low Power consumption oriented |

| 0x9   | Reserved    | Reserved                       |

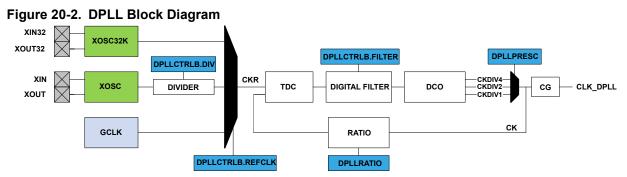

When the controller is disabled, the output clock is low. If the Loop Divider Ratio Fractional part bit field in the DPLL Ratio register (DPLLRATIO.LDRFRAC) is zero, the DPLL works in integer mode. Otherwise, the fractional mode is activated. Note that the fractional part has a negative impact on the jitter of the DPLL.

Example (integer mode only): assuming  $F_{CKR}$  = 32kHz and  $F_{CK}$  = 48MHz, the multiplication ratio is 1500. It means that LDR shall be set to 1499.

Example (fractional mode): assuming  $F_{CKR}$  = 32kHz and  $F_{CK}$  = 48.006MHz, the multiplication ratio is 1500.1875 (1500 + 3/16). Thus LDR is set to 1499 and LDRFRAC to 3.

## **Related Links**

GCLK - Generic Clock Controller OSC32KCTRL – 32KHz Oscillators Controller

#### 20.6.5.1 Basic Operation

#### Initialization, Enabling, Disabling, and Resetting

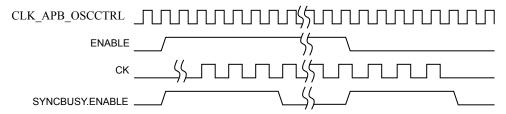

The DPLLC is enabled by writing a '1' to the Enable bit in the DPLL Control A register (DPLLCTRLA.ENABLE). The DPLLC is disabled by writing a zero to this bit.

The DPLLSYNCBUSY.ENABLE is set when the DPLLCTRLA.ENABLE bit is modified. It is cleared when the DPLL output clock CK has sampled the bit at the high level after enabling the DPLL. When disabling the DPLL, DPLLSYNCBUSY.ENABLE is cleared when the output clock is no longer running.

## Figure 20-3. Enable Synchronization Busy Operation

The frequency of the DPLL output clock CK is stable when the module is enabled and when the Lock bit in the DPLL Status register is set (DPLLSTATUS.LOCK).

When the Lock Time bit field in the DPLL Control B register (DPLLCTRLB.LTIME) is non-zero, a user defined lock time is used to validate the lock operation. In this case the lock time is constant. If DPLLCTRLB.LTIME=0, the lock signal is linked with the status bit of the DPLL, and the lock time varies depending on the filter selection and the final target frequency.

Writing '1' to this bit clears the DPLL Lock Rise interrupt flag.

#### Bit 4 – OSC48MRDY: OSC48M Ready

This flag is cleared by writing '1' to it.

This flag is set on 0-to-1 transition of the OSC48M Ready bit in the Status register (STATUS.OSC48MRDY) and will generate an interrupt request if INTENSET.OSC48MRDY is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the OSC48M Ready interrupt flag.

## Bit 1 – CLKFAIL: XOSC Failure Detection

This flag is cleared by writing '1' to it.

This flag is set on a 0-to-1 transition of the XOSC Clock Failure bit in the Status register (STATUS.CLKFAIL) and will generate an interrupt request if INTENSET.CLKFAIL is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the XOSC Clock Fail interrupt flag.

#### Bit 0 – XOSCRDY: XOSC Ready

This flag is cleared by writing '1' to it.

This flag is set on a 0-to-1 transition of the XOSC Ready bit in the Status register (STATUS.XOSCRDY) and will generate an interrupt request if INTENSET.XOSCRDY is '1'.

Writing '0' to this bit has no effect.

Writing '1' to this bit clears the XOSC Ready interrupt flag.

## 20.8.4 Status

Name:

STATUS

Offset:

0x0C [ID-00001eee]

Reset:

0x00000000

Property:

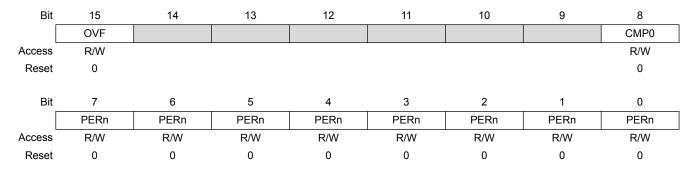

Name: INTENSET Offset: 0x0A Reset: 0x0000 Property: PAC Write-Protection

## Bit 15 – OVF: Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt.

| V | /alue | Description                         |

|---|-------|-------------------------------------|

| 0 |       | The Overflow interrupt is disabled. |

| 1 |       | The Overflow interrupt is enabled.  |

### Bit 8 – CMP0: Compare 0 Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Compare 0 Interrupt Enable bit, which enables the Compare 0 interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The Compare 0 interrupt is disabled. |

| 1     | The Compare 0 interrupt is enabled.  |

#### Bits 7:0 – PERn: Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Periodic Interval n Interrupt Enable bit, which enables the Periodic Interval n interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

## 24.8.5 Interrupt Flag Status and Clear in COUNT32 mode (CTRLA.MODE=0)

Name:INTFLAGOffset:0x0CReset:0x0000Property: -

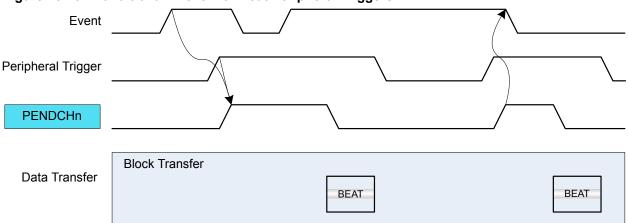

The figure below shows an example where conditional event is enabled with peripheral beat trigger requests.

#### Figure 25-13. Conditional Event with Beat Peripheral Triggers

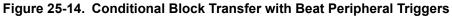

### **Conditional Block Transfer**

The event input is used to trigger a conditional block transfer on peripherals.

Before starting transfers within a block, an event must be received. When received, the event is acknowledged when the block transfer is completed. A software trigger will trigger a transfer.

The figure below shows an example where conditional event block transfer is started with peripheral beat trigger requests.

#### **Channel Suspend**

The event input is used to suspend an ongoing channel operation. The event is acknowledged when the current AHB access is completed. For further details on Channel Suspend, refer to Channel Suspend.

#### **Channel Resume**

The event input is used to resume a suspended channel operation. The event is acknowledged as soon as the event is received and the Channel Suspend Interrupt Flag (CHINTFLAG.SUSP) is cleared. For further details refer to Channel Suspend.

#### Skip Next Block Suspend

This event can be used to skip the next block suspend action. If the channel is suspended before the event rises, the channel operation is resumed and the event is acknowledged. If the event rises before a suspend block action is detected, the event is kept until the next block suspend detection. When the block transfer is completed, the channel continues the operation (not suspended) and the event is acknowledged.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the EIC is reset. See the INTFLAG register for details on how to clear interrupt flags. The EIC has one common interrupt request line for all the interrupt sources, and one interrupt request line for the NMI. The user must read the INTFLAG (or NMIFLAG) register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

**Note:** If an external interrupts (EXTINT) is common on two or more I/O pins, only one will be active (the first one programmed).

#### **Related Links**

Processor and Architecture

### 26.6.7 Events

The EIC can generate the following output events:

• External event from pin (EXTINTx).

Setting an Event Output Control register (EVCTRL.EXTINTEO) enables the corresponding output event. Clearing this bit disables the corresponding output event. Refer to *Event System* for details on configuring the Event System.

When the condition on pin EXTINTx matches the configuration in the CONFIGn register, the corresponding event is generated, if enabled.

#### **Related Links**

EVSYS – Event System

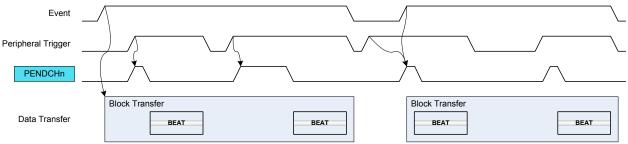

#### 26.6.8 Sleep Mode Operation

In sleep modes, an EXTINTx pin can wake up the device if the corresponding condition matches the configuration in CONFIG0, CONFIG1, CONFIG2, CONFIG3 register, and the corresponding bit in the Interrupt Enable Set register (INTENSET) is written to '1'.

## Figure 26-5. Wake-up Operation Example (High-Level Detection, No Filter, Interrupt Enable Set)

#### 26.6.9 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in control register (CTRLA.SWRST)

- Enable bit in control register (CTRLA.ENABLE)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

### PAC - Peripheral Access Controller

## 29.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | SWRST |

| Access |   |   |   |   |   |   |   | W     |

| Reset  |   |   |   |   |   |   |   | 0     |

# Bit 0 – SWRST: Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the EVSYS to their initial state.

Note: Before applying a Software Reset it is recommended to disable the event generators.

#### **Related Links**

PAC - Peripheral Access Controller

## 29.8.2 Channel Status

Name:

CHSTATUS

Offset:

0x0C [ID-0000120d]

Reset:

0x00000FF

Property:

–

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

## 32.5.9 Analog Connections

Not applicable.

## 32.6 Functional Description

### 32.6.1 Principle of Operation

The SPI is a high-speed synchronous data transfer interface It allows high-speed communication between the device and peripheral devices.

The SPI can operate as master or slave. As master, the SPI initiates and controls all data transactions. The SPI is single buffered for transmitting and double buffered for receiving.

When transmitting data, the Data register can be loaded with the next character to be transmitted during the current transmission.

When receiving, the data is transferred to the two-level receive buffer, and the receiver is ready for a new character.

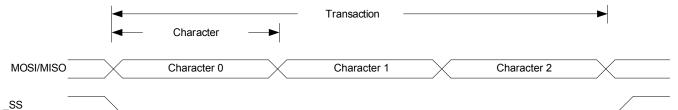

The SPI transaction format is shown in SPI Transaction Format. Each transaction can contain one or more characters. The character size is configurable, and can be either 8 or 9 bits.

## Figure 32-2. SPI Transaction Format

The SPI master must pull the slave select line  $(\overline{SS})$  of the desired slave low to initiate a transaction. The master and slave prepare data to send via their respective shift registers, and the master generates the serial clock on the SCK line.

Data are always shifted from master to slave on the Master Output Slave Input line (MOSI); data is shifted from slave to master on the Master Input Slave Output line (MISO).

Each time character is shifted out from the master, a character will be shifted out from the slave simultaneously. To signal the end of a transaction, the master will pull the  $\overline{SS}$  line high

## 32.6.2 Basic Operation

## 32.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the SPI is disabled (CTRL.ENABLE=0):

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

#### Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Register Empty Interrupt Enable bit, which enables the Data Register Empty interrupt.

| V | alue | Description                                |

|---|------|--------------------------------------------|

| 0 |      | Data Register Empty interrupt is disabled. |

| 1 |      | Data Register Empty interrupt is enabled.  |

### 32.8.6 Interrupt Flag Status and Clear

Name:

INTFLAG

Offset:

0x18 [ID-00000e74]

Reset:

0x00

Property:

| Bit    | 7     | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|-------|---|---|---|-----|-----|-----|-----|

| Γ      | ERROR |   |   |   | SSL | RXC | TXC | DRE |

| Access | R/W   |   |   |   | R/W | R   | R/W | R   |

| Reset  | 0     |   |   |   | 0   | 0   | 0   | 0   |

#### Bit 7 - ERROR: Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. The BUFOVF error will set this interrupt flag.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 3 – SSL: Slave Select Low

This flag is cleared by writing '1' to it.

This bit is set when a high to low transition is detected on the \_SS pin in slave mode and Slave Select Low Detect (CTRLB.SSDE) is enabled.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 2 – RXC: Receive Complete

This flag is cleared by reading the Data (DATA) register or by disabling the receiver.

This flag is set when there are unread data in the receive buffer. If address matching is enabled, the first data received in a transaction will be an address.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

Due to the synchronization mechanism between GCLK\_CAN and GCLK\_CAN\_APB domains, there may be a delay of several GCLK\_CAN\_APB periods between writing to TEST.TX until the new configuration is visible at output pin CAN\_TX. This applies also when reading input pin CAN\_RX via TEST.RX.

Note: Test modes should be used for production tests or self test only. The software control for pin CAN\_TX interferes with all CAN protocol functions. It is not recommended to use test modes for application.

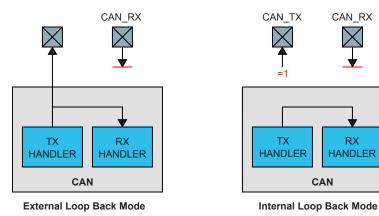

## External Loop Back Mode

The CAN can be set in External Loop Back Mode by programming TEST.LBCK to '1'. In Loop Back Mode, the CAN treats its own transmitted messages as received messages and stores them (if they pass acceptance filtering) into an Rx Buffer or an Rx FIFO. The figure below shows the connection of signals CAN\_TX and CAN\_RX to the CAN in External Loop Back Mode.

This mode is provided for hardware self-test. To be independent from external stimulation, the CAN ignores acknowledge errors (recessive bit sampled in the acknowledge slot of a data/remote frame) in Loop Back Mode. In this mode the CAN performs an internal feedback from its Tx output to its Rx input. The actual value of the CAN\_RX input pin is disregarded by the CAN. The transmitted messages can be monitored at the CAN\_TX pin.

## Internal Loop Back Mode

Internal Loop Back Mode is entered by programming bits TEST.LBCK and CCCR.MON to '1'. This mode can be used for a "Hot Selftest", meaning the CAN can be tested without affecting a running CAN system connected to the pins CAN\_TX and CAN\_RX. In this mode pin CAN\_RX is disconnected from the CAN and pin CAN\_TX is held recessive. The figure below shows the connection of CAN\_TX and CAN\_RX to the CAN in case of Internal Loop Back Mode.

## Figure 34-4. Pin Control in Loop Back Modes

## 34.6.3 Timestamp Generation

For timestamp generation the CAN supplies a 16-bit wrap-around counter. A prescaler TSCC.TCP can be configured to clock the counter in multiples of CAN bit times (1...16). The counter is readable via TSCV.TSC. A write access to register TSCV resets the counter to zero. When the timestamp counter wraps around interrupt flag IR.TSW is set.

On start of frame reception / transmission the counter value is captured and stored into the timestamp section of an Rx Buffer / Rx FIFO (RXTS[15:0]) or Tx Event FIFO (TXTS[15:0]) element.

- Store received frame in Rx Buffer

- Store received frame in Rx Buffer and generate pulse at filter event pin

- Reject received frame

- Set High Priority Message interrupt flag IR.HPM

- Set High Priority Message interrupt flag IR.HPM and store received frame in FIFO 0 or FIFO 1

Acceptance filtering is started after the complete identifier has been received. After acceptance filtering has completed, and if a matching Rx Buffer or Rx FIFO has been found, the Message Handler starts writing the received message data in portions of 32 bit to the matching Rx Buffer or Rx FIFO. If the CAN protocol controller has detected an error condition (e.g. CRC error), this message is discarded with the following impact on the affected Rx Buffer or Rx FIFO:

### Rx Buffer

New Data flag of matching Rx Buffer is not set, but Rx Buffer (partly) overwritten with received data. For error type see PSR.LEC respectively PSR.FLEC.

#### Rx FIFO

Put index of matching Rx FIFO is not updated, but related Rx FIFO element (partly) overwritten with received data. For error type see PSR.LEC respectively PSR.FLEC. In case the matching Rx FIFO is operated in overwrite mode, the boundary conditions described in Rx FIFO Overwrite Mode have to be considered.

Note: When an accepted message is written to one of the two Rx FIFOs, or into an Rx Buffer, the unmodified received identifier is stored independent of the filter(s) used. The result of the acceptance filter process is strongly depending on the sequence of configured filter elements.

### **Range Filter**

The filter matches for all received frames with Message IDs in the range defined by SF1ID/SF2ID for standard frames or EF1ID/EF2ID for extended frames.

There are two possibilities when range filtering is used together with extended frames:

- **EFT = "00"** The Message ID of received frames is AND'ed with the Extended ID AND Mask (XIDAM) before the range filter is applied

- **EFT = "11"** The Extended ID AND Mask (XIDAM) is not used for range filtering

#### Filter for specific IDs

A filter element can be configured to filter for one or two specific Message IDs. To filter for one specific Message ID, the filter element has to be configured with SF1ID = SF2ID resp. EF1ID = EF2ID.

#### Classic Bit Mask Filter

Classic bit mask filtering is intended to filter groups of Message IDs by masking single bits of a received Message ID. With classic bit mask filtering SF1ID/EF1ID is used as Message ID filter, while SF2ID/EF2ID is used as filter mask.

A zero bit at the filter mask will mask out the corresponding bit position of the configured ID filter, e.g. the value of the received Message ID at that bit position is not relevant for acceptance filtering. Only those bits of the received Message ID where the corresponding mask bits are one are relevant for acceptance filtering.

In case all mask bits are one, a match occurs only when the received Message ID and the Message ID filter are identical. If all mask bits are zero, all Message IDs match.

| Value | Description                     |

|-------|---------------------------------|

| 0     | Error_Warning status unchanged. |

| 1     | Error_Warning status changed.   |

#### Bit 23 – EP: Error Passive

| Value | Description                     |  |

|-------|---------------------------------|--|

| 0     | Error_Passive status unchanged. |  |

| 1     | Error_Passive status changed.   |  |

#### Bit 22 – ELO: Error Logging Overflow

| Value | Description                                     |  |  |

|-------|-------------------------------------------------|--|--|

| 0     | CAN Error Logging Counter did not overflow.     |  |  |

| 1     | Overflow of CAN Error Logging Counter occurred. |  |  |

## Bit 21 – BEU: Bit Error Uncorrected

Message RAM bit error detected, uncorrected. Generated by an optional external parity / ECC logic attached to the Message RAM. An uncorrected Message RAM bit sets CCCR.INIT to 1. This is done to avoid transmission of corrupted data.

| Value | Description                                           |  |  |

|-------|-------------------------------------------------------|--|--|

| 0     | Not bit error detected when reading from Message RAM. |  |  |

| 1     | Bit error detected, uncorrected (e.g. parity logic).  |  |  |

#### Bit 20 – BEC: Bit Error Corrected

Message RAM bit error detected and corrected. Generated by an optional external parity / ECC logic attached to the Message RAM.

| Value | Description                                           |  |  |

|-------|-------------------------------------------------------|--|--|

| 0     | Not bit error detected when reading from Message RAM. |  |  |

| 1     | Bit error detected and corrected (e.g. ECC).          |  |  |

#### Bit 19 – DRX: Message stored to Dedicated Rx Buffer

The flag is set whenever a received message has been stored into a dedicated Rx Buffer.

| Value | Description                                            |  |

|-------|--------------------------------------------------------|--|

| 0     | No Rx Buffer updated.                                  |  |

| 1     | At least one received message stored into a Rx Buffer. |  |

## Bit 18 – TOO: Timeout Occurred

| Value | Description      |

|-------|------------------|

| 0     | No timeout.      |

| 1     | Timeout reached. |

## Bit 17 – MRAF: Message RAM Access Failure

The flag is set, when the Rx Handler

- has not completed acceptance filtering or storage of an accepted message until the arbitration field of the following message has been received. In this case acceptance filtering or message storage is aborted and the Rx Handler starts processing of the following message.

- was not able to write a message to the Message RAM. In this case message storage is aborted.

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

## Bits 31:0 – NDn: New Data n [n = 0..31]

The register holds the New Data flags of Rx Buffers 0 to 31. The flags are set when the respective Rx Buffer has been updated from a received frame. The flags remain set until the Host clears them. A flag is cleared by writing 1 to the corresponding bit position. Writing a 0 has no effect. A hard reset will clear the register.

## 34.8.26 New Data 2

Name:

NDAT2

Offset:

0x9C

Reset:

0x0000000

Property:

active node may optionally transmit the ESI bit recessive, but an error passive node will always transmit the ESI bit recessive.

- T0 Bit 30 XTD: Extended Identifier

- 0 : 11-bit standard identifier.

- 1:29-bit extended identifier.

- T0 Bit 29 RTR: Remote Transmission Request

- 0 : Transmit data frame.

- 1 : Transmit remote frame.

**Note:** When RTR = '1', the CAN transmits a remote frame according to ISO 11898-1, even if CCCR.CME enables the transmission in CAN FD format.

• T0 Bits 28:0 - ID[28:0]: Identifier

Standard or extended identifier depending on bit XTD. A standard identifier is stored into ID[28:18].

• T1 Bits 31:24 - MM[7:0]: Message Marker

Written by CPU during Tx Buffer configuration. Copied into Tx Event FIFO element for identification of Tx message status.

• T1 Bit 23 - EFC: Event FIFO Control

0 : Don't store Tx events.

- 1 : Store Tx events.

- T1 Bit 22 Reserved

- TR1 Bit 21 FDF: FD Format

- 0 : Frame transmitted in Classic CAN format.

- 1 : Frame transmitted in CAN FD format.

- T1 Bit 20 BRS: Bit Rate Search

- 0 : CAN FD frames transmitted without bit rate switching.

- 1 : CAN FD frames transmitted with bit rate switching.

**Note:** Bits ESI, FDF, and BRS are only evaluated when CAN FD operation is enabled CCCR.FDOE = '1'. Bit BRS is only evaluated when in addition CCCR.BRSE = '1'.

T1 Bits 19:16 - DLC[3:0]: Data Length Code

0-8 : CAN + CAN FD: received frame has 0-8 data bytes.

9-15 : CAN: received frame has 8 data bytes.

9-15 : CAN FD: received frame has 12/16/20/24/32/48/64 data bytes.

- T1 Bits 15:0 Reserved

- T2 Bits 31:24 DB3[7:0]: Data Byte 3

- T2 Bits 23:16 DB2[7:0]: Data Byte 2

- T2 Bits 15:8 DB1[7:0]: Data Byte 1

- T2 Bits 7:0 DB0[7:0]: Data Byte 0

- T3 Bits 31:24 DB7[7:0]: Data Byte 7

- T3 Bits 23:16 DB6[7:0]: Data Byte 6

- T3 Bits 15:8 DB5[7:0]: Data Byte 5

- T3 Bits 7:0 DB4[7:0]: Data Byte 4

| Value | Name    | Description     |

|-------|---------|-----------------|

| 0x0   | DEFAULT | Default capture |

| 0x1   | CAPTMIN | Minimum capture |

| 0x2   | CAPTMAX | Maximum capture |

| 0x3   |         | Reserved        |

### Bits 20, 21 – COPENx: Capture On Pin x Enable

Bit x of COPEN[1:0] selects the trigger source for capture operation, either events or I/O pin input.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

## Bits 16, 17 – CAPTENx: Capture Channel x Enable

Bit x of CAPTEN[1:0] selects whether channel x is a capture or a compare channel.

These bits are not synchronized.

| Value | Description                           |  |

|-------|---------------------------------------|--|

| 0     | CAPTEN disables capture on channel x. |  |

| 1     | CAPTEN enables capture on channel x.  |  |

#### Bit 11 – ALOCK: Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | The LUPD bit is not affected on overflow/underflow, and re-trigger event. |

| 1     | The LUPD bit is set on each overflow/underflow or re-trigger event.       |

#### Bits 10:8 – PRESCALER[2:0]: Prescaler

These bits select the counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

## Bit 7 – ONDEMAND: Clock On Demand

This bit selects the clock requirements when the TC is stopped.

In standby mode, if the Run in Standby bit (CTRLA.RUNSTDBY) is '0', ONDEMAND is forced to '0'.

This bit is not synchronized.

| Bit    | 15    | 14    | 13       | 12      | 11    | 10        | 9          | 8        |

|--------|-------|-------|----------|---------|-------|-----------|------------|----------|

|        |       |       |          |         |       | SWTRIG    | OFFSETCORR | GAINCORR |

| Access |       |       |          |         |       | R         | R          | R        |

| Reset  |       |       |          |         |       | 0         | 0          | 0        |

|        |       |       |          |         |       |           |            |          |

| Bit    | 7     | 6     | 5        | 4       | 3     | 2         | 1          | 0        |

|        | WINUT | WINLT | SAMPCTRL | AVGCTRL | CTRLC | INPUTCTRL | ENABLE     | SWRST    |

| Access | R     | R     | R        | R       | R     | R         | R          | R        |

| Reset  | 0     | 0     | 0        | 0       | 0     | 0         | 0          | 0        |

## Bit 10 – SWTRIG: Software Trigger Synchronization Busy

This bit is cleared when the synchronization of SWTRIG register between the clock domains is complete.

This bit is set when the synchronization of SWTRIG register between clock domains is started.

#### Bit 9 – OFFSETCORR: Offset Correction Synchronization Busy

This bit is cleared when the synchronization of OFFSETCORR register between the clock domains is complete.

This bit is set when the synchronization of OFFSETCORR register between clock domains is started.

#### Bit 8 – GAINCORR: Gain Correction Synchronization Busy

This bit is cleared when the synchronization of GAINCORR register between the clock domains is complete.

This bit is set when the synchronization of GAINCORR register between clock domains is started.

#### Bit 7 – WINUT: Window Monitor Lower Threshold Synchronization Busy

This bit is cleared when the synchronization of WINUT register between the clock domains is complete.

This bit is set when the synchronization of WINUT register between clock domains is started.

#### Bit 6 – WINLT: Window Monitor Upper Threshold Synchronization Busy

This bit is cleared when the synchronization of WINLT register between the clock domains is complete.

This bit is set when the synchronization of WINLT register between clock domains is started.

## Bit 5 – SAMPCTRL: Sampling Time Control Synchronization Busy

This bit is cleared when the synchronization of SAMPCTRL register between the clock domains is complete.

This bit is set when the synchronization of SAMPCTRL register between clock domains is started.

#### Bit 4 – AVGCTRL: Average Control Synchronization Busy

This bit is cleared when the synchronization of AVGCTRL register between the clock domains is complete.

This bit is set when the synchronization of AVGCTRL register between clock domains is started.

#### Bit 3 – CTRLC: Control C Synchronization Busy

This bit is cleared when the synchronization of CTRLC register between the clock domains is complete.

This bit is set when the synchronization of CTRLC register between clock domains is started.

# 44.7 Register Summary

| Offset | Name      | Bit Pos. |              |   |  |      |         |   |        |       |

|--------|-----------|----------|--------------|---|--|------|---------|---|--------|-------|

| 0x00   | CTRLA     | 7:0      |              |   |  |      |         |   | ENABLE | SWRST |

| 0x01   | CTRLB     | 7:0      |              |   |  |      |         |   |        | START |

| 0x02   | 0504      | 7:0      |              | 1 |  | REFN | UM[7:0] | - | 1      |       |

| 0x03   | CFGA      | 15:8     | DIVREF       |   |  |      |         |   |        |       |

| 0x04   |           |          |              |   |  |      |         |   |        |       |

|        | Reserved  |          |              |   |  |      |         |   |        |       |

| 0x07   |           |          |              |   |  |      |         |   |        |       |

| 0x08   | INTENCLR  | 7:0      |              |   |  |      |         |   |        | DONE  |

| 0x09   | INTENSET  | 7:0      |              |   |  |      |         |   |        | DONE  |

| 0x0A   | INTFLAG   | 7:0      |              |   |  |      |         |   |        | DONE  |

| 0x0B   | STATUS    | 7:0      |              |   |  |      |         |   | OVF    | BUSY  |

| 0x0C   |           | 7:0      |              |   |  |      |         |   | ENABLE | SWRST |

| 0x0D   | EVNOPLIEV | 15:8     |              |   |  |      |         |   |        |       |

| 0x0E   | SYNCBUSY  | 23:16    |              |   |  |      |         |   |        |       |

| 0x0F   |           | 31:24    |              |   |  |      |         |   |        |       |

| 0x10   |           | 7:0      |              |   |  | VALU | IE[7:0] |   |        |       |

| 0x11   | - VALUE   | 15:8     | VALUE[15:8]  |   |  |      |         |   |        |       |

| 0x12   |           | 23:16    | VALUE[23:16] |   |  |      |         |   |        |       |

| 0x13   |           | 31:24    |              |   |  |      |         |   |        |       |

# 44.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description.

## 44.8.1 Control A

Name:CTRLAOffset:0x00 [ID-00000e03]Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Mode    | Conditions                              | Та    | Vcc  | Тур.         | Max.          | Units                    |  |

|---------|-----------------------------------------|-------|------|--------------|---------------|--------------------------|--|

|         |                                         | 105°C | 5.0V | 6.3          | 7.1           |                          |  |

|         | CPU running a CoreMark algorithm        | 25°C  | 3.0V | 5.2          | 5.7           | mA                       |  |

|         |                                         |       | 3.0V | 5.5          | 6.6           |                          |  |

|         | CPU running a CoreMark algorithm.       | 25°C  | 5.0V | 115*Freq+167 | 126*Freq+167  | μA (with freq in<br>MHz) |  |

|         | with GCLKIN as reference                | 105°C | 5.0V | 118*Freq+383 | 110*Freq+1583 |                          |  |

| IDLE    |                                         | 25°C  | 5.0V | 1.2          | 1.7           | mA                       |  |

|         |                                         | 105°C | 5.0V | 1.5          | 2.6           |                          |  |

| STANDBY | _ · · · · · · · · · · · · · · · · · · · | 25°C  | 5.0V | 15.9         | 37.0          | μΑ                       |  |

|         | 1kHz                                    | 105°C | 5.0V | 187.0        | 602.0         |                          |  |

|         | XOSC32K and RTC stopped                 | 25°C  | 5.0V | 14.6         | 35.0          |                          |  |

|         |                                         | 105°C | 5.0V | 185.0        | 600.0         |                          |  |

1. These are based on characterization.

# 47.4 Analog Characteristics

# 47.4.1 Power On Reset (POR) Characteristics Table 47-3. POR Characteristics

| Symbol            | Parameters                               | Min  | Тур  | Мах  | Unit |

|-------------------|------------------------------------------|------|------|------|------|

| V <sub>POT+</sub> | Voltage threshold Level on VDDIN rising  | -    | 2.55 | -    | V    |

| V <sub>POT-</sub> | Voltage threshold Level on VDDIN falling | 1.77 | 1.92 | 2.04 |      |

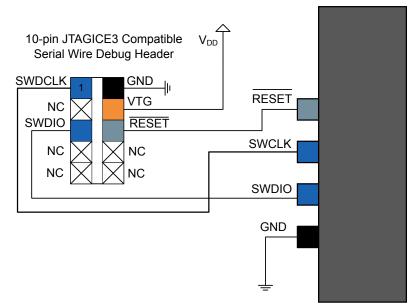

Figure 49-13. 10-pin JTAGICE3 Compatible Serial Wire Debug Interface

Table 49-9.

10-pin JTAGICE3 Compatible Serial Wire Debug Interface

| Header Signal Name | Description                                                      |  |  |  |  |

|--------------------|------------------------------------------------------------------|--|--|--|--|

| SWDCLK             | Serial wire clock pin                                            |  |  |  |  |

| SWDIO              | Serial wire bidirectional data pin                               |  |  |  |  |

| RESET              | Target device reset pin, active low                              |  |  |  |  |

| VTG                | Target voltage sense, should be connected to the device $V_{DD}$ |  |  |  |  |

| GND                | Ground                                                           |  |  |  |  |

## 49.8.3 20-pin IDC JTAG Connector

For debuggers and/or programmers that support the 20-pin IDC JTAG Connector, e.g. the SAM-ICE, the signals should be connected as shown in Figure 49-14 with details described in Table 49-10.