Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20e18a-mut |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

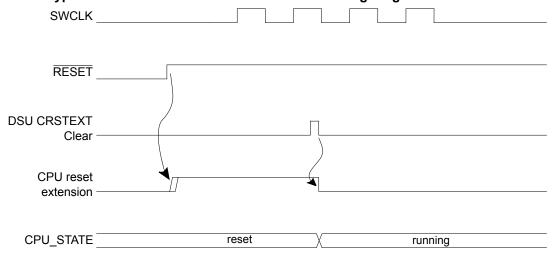

#### 13.6.2 CPU Reset Extension

"CPU reset extension" refers to the extension of the reset phase of the CPU core after the external reset is released. This ensures that the CPU is not executing code at startup while a debugger is connects to the system. The debugger is detected on a RESET release event when SWCLK is low. At startup, SWCLK is internally pulled up to avoid false detection of a debugger if the SWCLK pin is left unconnected. When the CPU is held in the reset extension phase, the CPU Reset Extension bit of the Status A register (STATUSA.CRSTEXT) is set. To release the CPU, write a '1' to STATUSA.CRSTEXT. STATUSA.CRSTEXT will then be set to '0'. Writing a '0' to STATUSA.CRSTEXT has no effect. For security reasons, it is not possible to release the CPU reset extension when the device is protected by the NVMCTRL security bit. Trying to do so sets the Protection Error bit (PERR) of the Status A register (STATUSA.PERR).

Figure 13-2. Typical CPU Reset Extension Set and Clear Timing Diagram

#### **Related Links**

NVMCTRL – Non-Volatile Memory Controller Security Bit

#### 13.6.3 Debugger Probe Detection

#### 13.6.3.1 Cold Plugging

Cold-Plugging is the detection of a debugger when the system is in reset. Cold-Plugging is detected when the CPU reset extension is requested, as described above.

#### 13.6.3.2 Hot Plugging

Hot-Plugging is the detection of a debugger probe when the system is not in reset. Hot-Plugging is not possible under reset because the detector is reset when POR or RESET are asserted. Hot-Plugging is active when a SWCLK falling edge is detected. The SWCLK pad is multiplexed with other functions and the user must ensure that its default function is assigned to the debug system. If the SWCLK function is changed, the Hot-Plugging feature is disabled until a power-reset or external reset occurs. Availability of the Hot-Plugging feature can be read from the Hot-Plugging Enable bit of the Status B register (STATUSB.HPE).

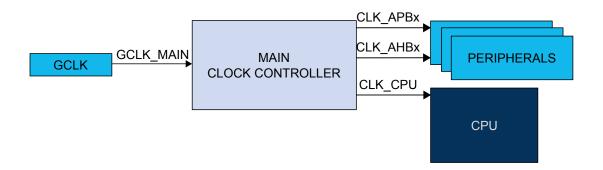

## 17. MCLK - Main Clock

#### 17.1 Overview

The Main Clock (MCLK) controls the synchronous clock generation of the device.

Using a clock provided by the Generic Clock Module (GCLK\_MAIN), the Main Clock Controller provides synchronous system clocks to the CPU and the modules connected to the AHBx and the APBx bus. The synchronous system clocks are divided into a number of clock domains. Each clock domain can run at different frequencies, enabling the user to save power by running peripherals at a relatively low clock frequency, while maintaining high CPU performance or vice versa. In addition, the clock can be masked for individual modules, enabling the user to minimize power consumption.

## 17.2 Features

- Generates CPU, AHB, and APB system clocks

- Clock source and division factor from GCLK

- Clock prescaler with 1x to 128x division

- Safe run-time clock switching from GCLK

- Module-level clock gating through maskable peripheral clocks

## 17.3 Block Diagram

Figure 17-1. MCLK Block Diagram

## 17.4 Signal Description

Not applicable.

## 17.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 17.5.1 I/O Lines

Not applicable.

Table 19-3. RAM Back-Biasing Mode

| STB | YCDFG.BBIASHS             | RAM                                                            |

|-----|---------------------------|----------------------------------------------------------------|

| 0x0 | No Back Biasing           | RAM is not back-biased if the device is in standby sleep mode. |

| 0x1 | Standby Back Biasing mode | RAM is back-biased if the device is in standby sleep mode.     |

#### 19.6.4.2 Regulator Automatic Low Power Mode

In standby mode, the PM selects either the main or the low power voltage regulator to supply the VDDCORE. By default the low power voltage regulator is used.

If a sleepwalking task is working on either asynchronous clocks (generic clocks) or synchronous clock (APB/AHB clocks), the main voltage regulator is used. This behavior can be changed by writing the Voltage Regulator Standby Mode bits in the Standby Configuration register (STDBYCFG.VREGSMOD). Refer to the following table for details.

Table 19-4. Regulator State in Sleep Mode

| Sleep<br>Mode | STDBYCFG.<br>VREGSMOD | SleepWalking | Regulator state for VDDCORE |

|---------------|-----------------------|--------------|-----------------------------|

| Active        | -                     | -            | main voltage regulator      |

| Idle          | -                     | -            | main voltage regulator      |

| Standby       | 0x0: AUTO             | NO           | low power regulator         |

|               |                       | YES          | main voltage regulator      |

|               | 0x1: PERFORMANCE      | -            | main voltage regulator      |

|               | 0x2: LP               | -            | low power regulator         |

## 19.6.5 DMA Operation

Not applicable.

#### 19.6.6 Interrupts

Not applicable.

#### 19.6.7 Events

Not applicable.

## 19.6.8 Sleep Mode Operation

The Power Manager is always active.

| Bit    | 31 | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----|----|----|--------|-----------|----|----|----|

|        |    |    |    | DSTADD | PR[31:24] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |    |    |    | DSTADD | R[23:16]  |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |    |    |    | DSTADI | DR[15:8]  |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

|        |    |    |    | DSTAD  | DR[7:0]   |    |    |    |

| Access |    |    |    |        |           |    |    |    |

## Bits 31:0 - DSTADDR[31:0]: Transfer Destination Address

This bit group holds the destination address corresponding to the last beat transfer address in the block transfer.

## 25.10.5 Next Descriptor Address

Reset

The DESCADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

Name: **DESCADDR**

Offset: 0x0C Property: -

## 27.7 Register Summary

| Offset   | Name      | Bit Pos. |               |      |          |      |                 |             |          |          |

|----------|-----------|----------|---------------|------|----------|------|-----------------|-------------|----------|----------|

| 0x00     |           | 7:0      | CMD[6:0]      |      |          |      |                 |             |          |          |

| 0x01     | CTRLA     | 15:8     |               |      |          | CMDE | EX[7:0]         |             |          |          |

| 0x02     |           |          |               |      |          |      |                 |             |          |          |

|          | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x03     |           |          |               |      |          |      |                 |             |          |          |

| 0x04     |           | 7:0      | MANW          |      |          |      | RW              | S[3:0]      |          |          |

| 0x05     | CTRLB     | 15:8     |               |      |          |      |                 |             | SLEEPF   | PRM[1:0] |

| 0x06     | CTILLE    | 23:16    |               |      |          |      |                 | CACHEDIS    | READM    | ODE[1:0] |

| 0x07     |           | 31:24    |               |      |          |      |                 |             |          |          |

| 0x08     |           | 7:0      |               |      |          | NVM  | P[7:0]          |             |          |          |

| 0x09     | PARAM     | 15:8     |               |      |          | NVM  | P[15:8]         |             |          |          |

| 0x0A     |           | 23:16    |               | RWWE | EEP[3:0] |      |                 |             | PSZ[2:0] |          |

| 0x0B     |           | 31:24    |               |      |          | RWWE | EP[11:4]        |             |          |          |

| 0x0C     | INTENCLR  | 7:0      |               |      |          |      |                 |             | ERROR    | READY    |

| 0x0D     |           |          |               |      |          |      |                 |             |          |          |

|          | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x0F     |           |          |               |      |          |      |                 |             |          |          |

| 0x10     | INTENSET  | 7:0      |               |      |          |      |                 |             | ERROR    | READY    |

| 0x11     | Deserved  |          |               |      |          |      |                 |             |          |          |

| <br>0x13 | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x13     | INTFLAG   | 7:0      |               |      |          |      |                 |             | ERROR    | READY    |

| 0x14     | INTI LAG  | 7.0      |               |      |          |      |                 |             | LKKOK    | KLADI    |

|          | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x17     | 110001100 |          |               |      |          |      |                 |             |          |          |

| 0x18     |           | 7:0      |               |      |          | NVME | LOCKE           | PROGE       | LOAD     | PRM      |

| 0x19     | STATUS    | 15:8     |               |      |          |      |                 |             |          | SB       |

| 0x1A     |           |          |               |      |          |      |                 |             |          |          |

|          | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x1B     |           |          |               |      |          |      |                 |             |          |          |

| 0x1C     |           | 7:0      |               |      |          | ADD  | R[7:0]          |             |          |          |

| 0x1D     | ADDR      | 15:8     |               |      |          | ADDF | R[15:8]         |             |          |          |

| 0x1E     | ADDR      | 23:16    |               |      |          |      |                 | ADDR[20:16] |          |          |

| 0x1F     |           | 31:24    |               |      |          |      |                 |             |          |          |

| 0x20     | LOCK      | 7:0      |               |      |          | LOC  | K[7:0]          |             |          |          |

| 0x21     | LOCK      | 15:8     |               |      |          | LOCK | <b>C</b> [15:8] |             |          |          |

| 0x22     |           |          |               |      |          |      |                 |             |          |          |

|          | Reserved  |          |               |      |          |      |                 |             |          |          |

| 0x27     |           |          |               |      |          |      |                 |             |          |          |

| 0x28     |           | 7:0      |               |      |          |      | ATA[7:0]        |             |          |          |

| 0x29     | PBLDATA0  | 15:8     |               |      |          |      | TA[15:8]        |             |          |          |

| 0x2A     |           | 23:16    |               |      |          |      | ΓA[23:16]       |             |          |          |

| 0x2B     |           | 31:24    |               |      |          |      | ΓA[31:24]       |             |          |          |

| 0x2C     | PBLDATA1  | 7:0      |               |      |          |      | ATA[7:0]        |             |          |          |

| 0x2D     |           | 15:8     | PBLDATA[15:8] |      |          |      |                 |             |          |          |

| Value     | Channel Number             |

|-----------|----------------------------|

| 0x00      | No channel output selected |

| 0x01      | 0                          |

| 0x02      | 1                          |

| 0x03      | 2                          |

| 0x04      | 3                          |

| 0x05      | 4                          |

| 0x06      | 5                          |

| 0x07      | 6                          |

| 0x08      | 7                          |

| 0x09      | 8                          |

| 0x0A      | 9                          |

| 0x0B      | 10                         |

| 0x0C      | 11                         |

| 0x0D-0xFF | Reserved                   |

Table 29-3. User Multiplexer Number

| USERm | User Multiplexer       | Description        | Path Type                                                            |

|-------|------------------------|--------------------|----------------------------------------------------------------------|

| m = 0 | TSENS<br>STARTReserved | Start measurement- | Asynchronous,<br>synchronous, and<br>resynchronized<br>pathsReserved |

| m = 1 | PORT EV0               | Event 0            | Asynchronous path only                                               |

| m = 2 | PORT EV1               | Event 1            | Asynchronous path only                                               |

| m = 3 | PORT EV2               | Event 2            | Asynchronous path only                                               |

| m = 4 | PORT EV3               | Event 3            | Asynchronous path only                                               |

| m = 5 | DMAC CH0               | Channel 0          | Asynchronous, synchronous, and resynchronized paths                  |

| m = 6 | DMAC CH1               | Channel 1          | Asynchronous, synchronous, and resynchronized paths                  |

| m = 7 | DMAC CH2               | Channel 2          | Asynchronous, synchronous, and resynchronized paths                  |

| m = 8 | DMAC CH3               | Channel 3          | Asynchronous, synchronous, and resynchronized paths                  |

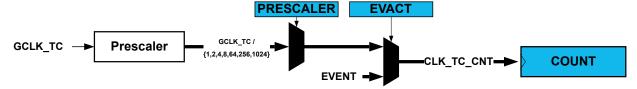

Figure 35-2. Prescaler

#### 35.6.2.4 Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period Value and Period Buffer Value registers (PER and PERBUF).

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

- COUNT32: This mode is achieved by pairing two 16-bit TC peripherals. TC0 is paired with TC1, and TC2 is paired with TC3. TC4 does not support 32-bit resolution. When paired, the TC peripherals are configured using the registers of the even-numbered TC (TC0 or TC2 respectively). The odd-numbered partner (TC1 or TC3 respectively) will act as slave, and the Slave bit in the Status register (STATUS.SLAVE) will be set. The register values of a slave will not reflect the registers of the 32-bit counter. Writing to any of the slave registers will not affect the 32-bit counter. Normal access to the slave COUNT and CCx registers is not allowed.

#### 35.6.2.5 Counter Operations

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TC clock input (CLK TC CNT). A counter clear or reload marks the end of the current counter cycle and the start of a new one.

The counting direction is set by the Direction bit in the Control B register (CTRLB.DIR). If this bit is zero the counter is counting up, and counting down if CTRLB.DIR=1. The counter will count up or down for each tick (clock or event) until it reaches TOP or ZERO. When it is counting up and TOP is reached, the counter will be set to zero at the next tick (overflow) and the Overflow Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF) will be set. When it is counting down, the counter is reloaded with the TOP value when ZERO is reached (underflow), and INTFLAG.OVF is set.

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e. a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. When starting the TC, the COUNT value will be either ZERO or TOP (depending on the counting direction set by CTRLBSET.DIR or CTRLBCLR.DIR), unless a different value has been written to it, or the TC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed during normal operation. See also the figure below.

These bits are not synchronized.

| Value | Name   | Description                                                                    |

|-------|--------|--------------------------------------------------------------------------------|

| 0x0   | GCLK   | Reload or reset the counter on next generic clock                              |

| 0x1   | PRESC  | Reload or reset the counter on next prescaler clock                            |

| 0x2   | RESYNC | Reload or reset the counter on next generic clock. Reset the prescaler counter |

| 0x3   | -      | Reserved                                                                       |

#### Bits 3:2 - MODE[1:0]: Timer Counter Mode

These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 - ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 - SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 35.7.1.2 Control B Clear

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

#### Bit 0 - OVF: Overflow Interrupt Flag

This flag is set on the next CLK\_TC\_CNT cycle after an overflow condition occurs, and will generate an interrupt request if INTENCLR.OVF or INTENSET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

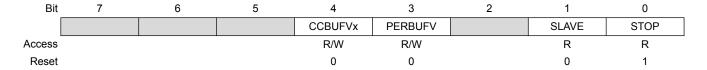

#### 35.7.2.8 Status

Name: STATUS Offset: 0x0B Reset: 0x01

Property: Read-Synchronized

| Bit    | 7 | 6 | 5 | 4       | 3       | 2 | 1     | 0    |

|--------|---|---|---|---------|---------|---|-------|------|

|        |   |   |   | CCBUFVx | PERBUFV |   | SLAVE | STOP |

| Access |   |   |   | R/W     | R/W     |   | R     | R    |

| Reset  |   |   |   | 0       | 0       |   | 0     | 1    |

#### Bit 4 – CCBUFVx: Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

#### Bit 3 - PERBUFV: Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. The bit is cleared by writing '1' to the corresponding location when CTRLB.LUPD is set, or automatically cleared by hardware on UPDATE condition. This bit is available only in 8-bit mode and will always read zero in 16- and 32-bit modes.

#### Bit 1 - SLAVE: Slave Status Flag

This bit is only available in 32-bit mode on the slave TC (i.e., TC1 and/or TC3). The bit is set when the associated master TC (TC0 and TC2, respectively) is set to run in 32-bit mode.

#### Bit 0 - STOP: Stop Status Flag

This bit is set when the TC is disabled, on a Stop command, or on an overflow/underflow condition when the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT) is '1'.

| Value | Description         |

|-------|---------------------|

| 0     | Counter is running. |

| 1     | Counter is stopped. |

#### 35.7.2.9 Waveform Generation Control

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

|        |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

#### Bit 4 - MCx: Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag In capture operation, this flag is automatically cleared when CCx register is read.

#### Bit 1 - ERR: Error Interrupt Flag

This flag is set when a new capture occurs on a channel while the corresponding Match or Capture Channel x interrupt flag is set, in which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Error interrupt flag.

#### Bit 0 - OVF: Overflow Interrupt Flag

This flag is set on the next CLK\_TC\_CNT cycle after an overflow condition occurs, and will generate an interrupt request if INTENCLR.OVF or INTENSET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

#### 35.7.3.8 Status

Name: STATUS Offset: 0x0B Reset: 0x01

**Property:** Read-Synchronized

#### Bit 4 – CCBUFVx: Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

This bit is set when the synchronization of ENABLE bit between clock domains is started.

#### Bit 0 - SWRST: SWRST Synchronization Busy

This bit is cleared when the synchronization of SWRST bit between the clock domains is complete.

This bit is set when the synchronization of SWRST bit between clock domains is started.

## 35.7.3.13 Counter Value, 32-bit Mode

**Note:** Prior to any read access, this register must be synchronized by user by writing the according TC Command value to the Control B Set register (CTRLBSET.CMD=READSYNC).

Name: COUNT

Offset: 0x14 [ID-00001cd8]

Reset: 0x00

Property: PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Bit    | 31           | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |  |  |

|--------|--------------|-----|-----|-------|----------|-----|-----|-----|--|--|--|

|        | COUNT[31:24] |     |     |       |          |     |     |     |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |

| Bit    | 23           | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |  |  |

|        |              |     |     | COUNT | Γ[23:16] |     |     |     |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |

| Bit    | 15           | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |  |  |

|        |              |     |     | COUN  | T[15:8]  |     |     |     |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |

|        |              |     |     |       |          |     |     |     |  |  |  |

| Bit    | 7            | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |  |  |

|        |              |     |     | COUN  | NT[7:0]  |     |     |     |  |  |  |

| Access | R/W          | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |  |

| Reset  | 0            | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |  |

#### Bits 31:0 - COUNT[31:0]: Counter Value

These bits contain the current counter value.

#### 35.7.3.14 Period Value, 32-bit Mode

Name: PER

Offset: 0x1A [ID-00001cd8]

Reset: 0xFFFFFFF

Property: Write-Synchronized

| =      |               |     |     |       |          |     |     |     |  |  |

|--------|---------------|-----|-----|-------|----------|-----|-----|-----|--|--|

| Bit    | 31            | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |  |

|        | PERBUF[31:24] |     |     |       |          |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 23            | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |  |

|        |               |     |     | PERBU | F[23:16] |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 15            | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |  |

|        |               |     |     | PERBL | JF[15:8] |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 7             | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |  |

|        |               |     |     | PERB  | UF[7:0]  |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 1   |  |  |

## Bits 31:0 - PERBUF[31:0]: Period Buffer Value

These bits hold the value of the period buffer register. The value is copied to PER register on UPDATE condition.

## 35.7.3.17 Channel x Compare Buffer Value, 32-bit Mode

Name: CCBUFx

**Offset:** 0x30 + x\*0x04 [x=0..1]

**Reset:** 0x00000000

Property: Write-Synchronized

#### 36.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 36.5.6 Events

The events of this peripheral are connected to the Event System.

#### Related Links

EVSYS - Event System

#### 36.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will halt normal operation. This peripheral can be forced to continue operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

Refer to DBGCTRL register for details.

#### 36.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except for the following:

- Interrupt Flag register (INTFLAG)

- Status register (STATUS)

- Period and Period Buffer registers (PER, PERBUF)

- Compare/Capture and Compare/Capture Buffer registers (CCx, CCBUFx)

- Control Waveform register (WAVE)

- Control Waveform Buffer register (WAVEBUF)

- Pattern Generation Value and Pattern Generation Value Buffer registers (PATT, PATTBUF)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### 36.5.9 Analog Connections

Not applicable.

## 36.6 Functional Description

## 36.6.1 Principle of Operation

The following definitions are used throughout the documentation:

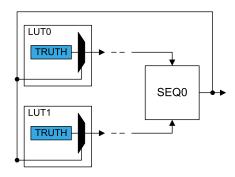

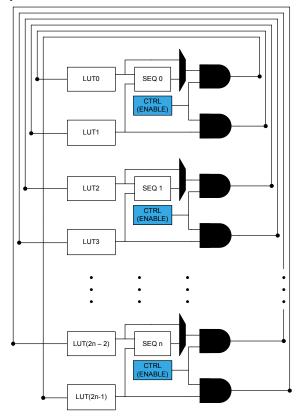

IN[2N][i] = SEQ[N]

IN[2N+1][i] = SEQ[N]

With N representing the sequencer number and i=0,1,2 representing the LUT input index.

For details, refer to Sequential Logic.

Figure 37-4. Feedback Input Selection

#### **FEEDBACK**

## Linked LUT (LINK)

When selected (LUTCTRLx.INSELy=LINK), the subsequent LUT output is used as the LUT input (e.g., LUT2 is the input for LUT1), as shown in this figure:

Figure 37-5. Linked LUT Input Selection

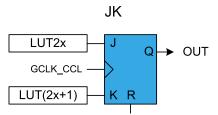

Figure 37-15. JK Flip Flop

When the even LUT is disabled (LUTCTRL0.ENABLE=0 / LUTCTRL2.ENABLE=0), the flip-flop is asynchronously cleared. The reset command (R) is kept enabled for one APB clock cycle. In all other cases, the flip-flop output (OUT) is refreshed on rising edge of the GCLK\_CCL, as shown in Table 37-3.

Table 37-3. JK Characteristics

| R | J | K | оит                    |

|---|---|---|------------------------|

| 1 | X | X | Clear                  |

| 0 | 0 | 0 | Hold state (no change) |

| 0 | 0 | 1 | Clear                  |

| 0 | 1 | 0 | Set                    |

| 0 | 1 | 1 | Toggle                 |

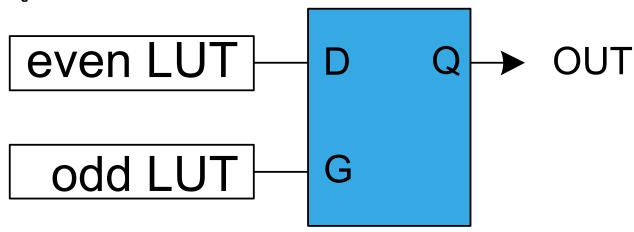

#### Gated D-Latch (DLATCH)

When the DLATCH is selected, the D-input is driven by the even LUT output (LUT0 and LUT2), and the G-input is driven by the odd LUT output (LUT1 and LUT3), as shown in Figure 37-14.

Figure 37-16. D-Latch

When the even LUT is disabled (LUTCTRL0.ENABLE=0 / LUTCTRL2.ENABLE=0), the latch output will be cleared. The G-input is forced enabled for one more APB clock cycle, and the D-input to zero. In all other cases, the latch output (OUT) is refreshed as shown in Table 37-4.

| Bit    | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

|        |     |     |     | WINL | Γ[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        |     |     |     | WINL | T[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

## Bits 15:0 – WINLT[15:0]: Window Lower Threshold

If the window monitor is enabled, these bits define the lower threshold value.

## 38.8.14 Window Monitor Upper Threshold

Name: WINUT

Offset: 0x10 [ID-0000120e]

**Reset:** 0x0000

Property: PAV Write-Protection, Write-Synchronized

| Bit    | 15          | 14  | 13  | 12   | 11     | 10  | 9   | 8   |  |  |  |

|--------|-------------|-----|-----|------|--------|-----|-----|-----|--|--|--|

|        | WINUT[15:8] |     |     |      |        |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

|        |             |     |     |      |        |     |     |     |  |  |  |

| Bit    | 7           | 6   | 5   | 4    | 3      | 2   | 1   | 0   |  |  |  |

|        |             |     |     | WINU | T[7:0] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

## Bits 15:0 - WINUT[15:0]: Window Upper Threshold

If the window monitor is enabled, these bits define the upper threshold value.

#### 38.8.15 Gain Correction

Name: GAINCORR

**Offset:** 0x12 [ID-0000120e]

**Reset:** 0x0000

Property: PAC Write-Protection, Write-Synchronized

- Low-power option

- Single-shot support

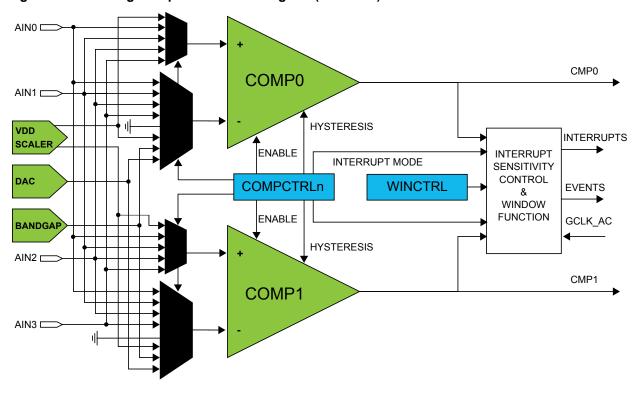

## 40.3 Block Diagram

Figure 40-1. Analog Comparator Block Diagram (First Pair)

Name: DATA

Offset: 0x08 [ID-00000bc7]

**Reset:** 0x0000

Property: PAC Write-Protection, Write-Synchronized

| W |

|---|

| 0 |

|   |

| 0 |

|   |

| W |

| 0 |

| _ |

#### Bits 15:0 - DATA[15:0]: Data value to be converted

DATA register contains the 10-bit value that is converted to a voltage by the DAC. The adjustment of these 10 bits within the 16-bit register is controlled by CTRLB.LEFTADJ.

Four additional bits are also used for the dithering feature according to Dithering mode.

Table 41-1. Valid Data Bits

| CTRLB.DITHER | CTRLB.LEFTADJ | DATA                  | Description             |

|--------------|---------------|-----------------------|-------------------------|

| 0            | 0             | DATA[9:0]             | Right adjusted, 10-bits |

| 0            | 1             | DATA[15:6]            | Left adjusted, 10-bits  |

| 1            | 0             | DATA[13:4], DATA[3:0] | Right adjusted, 14-bits |

| 1            | 1             | DATA[15:6], DATA[5:2] | Left adjusted, 14-bits  |

#### 41.8.9 Data Buffer

Name: DATABUF

**Offset:** 0x0C [ID-00000bc7]

**Reset:** 0x0000

Property: Write-Synchronized

| Bit    | 15            | 14 | 13 | 12    | 11       | 10 | 9 | 8 |  |  |  |

|--------|---------------|----|----|-------|----------|----|---|---|--|--|--|

|        | DATABUF[15:8] |    |    |       |          |    |   |   |  |  |  |

| Access | W             | W  | W  | W     | W        | W  | W | W |  |  |  |

| Reset  | 0             | 0  | 0  | 0     | 0        | 0  | 0 | 0 |  |  |  |

|        |               |    |    |       |          |    |   |   |  |  |  |

| Bit    | 7             | 6  | 5  | 4     | 3        | 2  | 1 | 0 |  |  |  |

|        |               |    |    | DATAB | BUF[7:0] |    |   |   |  |  |  |

| Access | W             | W  | W  | W     | W        | W  | W | W |  |  |  |

| Reset  | 0             | 0  | 0  | 0     | 0        | 0  | 0 | 0 |  |  |  |

## Bits 15:0 - DATABUF[15:0]: Data Buffer

DATABUF contains the value to be transferred into DATA register.

| Symbol | Parameters | Conditions                                                                                                 | Та | Тур. | Max | Units |

|--------|------------|------------------------------------------------------------------------------------------------------------|----|------|-----|-------|

|        |            | fs = 10 ksps / Reference buffer disabled /<br>BIASREFBUF = '111', BIASREFCOMP =<br>'111' VDDANA=Vref= 5.5V |    | 437  | 528 |       |

|        |            | fs = 10 ksps / Reference buffer enabled /<br>BIASREFBUF = '111', BIASREFCOMP =<br>'111' VDDANA=Vref= 5.5V  |    | 553  | 675 |       |

1. These are based on characterization.

# 45.10.5 Sigma-Delta Analog-to-Digital Converter (SDADC) Characteristics Table 45-22. Operating Conditions<sup>(1)</sup>

| Symbol       | Parameters              | Conditions                                 | Min                    | Тур   | Max      | Unit   |

|--------------|-------------------------|--------------------------------------------|------------------------|-------|----------|--------|

| Res          | Resolution              | Differential mode                          | -                      | 16    | -        | bits   |

|              |                         | Single-Ended mode                          | -                      | 15    | -        |        |

| CLK_SDADC    | Sampling Clock Speed    |                                            | 1                      | -     | 6        | MHz    |

| CLK_SDADC_FS | Conversion rate         |                                            | CLK                    | _SDAD | C/4      |        |

| fs           | Output Data Rate        | Free running mode                          | CLK_SD.                | ADC_F | S / OSR  |        |

|              |                         | Single<br>conversion<br>mode SKPCNT<br>= N | (CLK_SDADO             |       |          |        |

| OSR          | Oversampling ratio      | Differential mode                          | 64                     | 256   | 1024     | Cycles |

|              | Input Conversion range  | Differential<br>mode Gaincorr<br>= 0x1     | -0.7xVREF              | -     | 0.7xVREF | V      |

|              |                         | Single-Ended<br>mode Gaincorr<br>= 0x1     | 0                      | -     | 0.7xVREF |        |

| Vref         | Reference voltage range |                                            | 1                      | -     | 5.5      | V      |

| Vcom         | Common mode voltage     | Differential mode                          | 0                      | -     | AVDD     | V      |

| Cin          | Input capacitance       |                                            | 0.425                  | 0,5   | 0.575    | pF     |

| Zin          | Input impedance         | Differential mode                          | 1/(Cin x CLK_SDADC_FS) |       |          | kΩ     |

| Symbol | Parameters   | Conditions | Min | Тур   | Max | Unit |

|--------|--------------|------------|-----|-------|-----|------|

|        | Offset Error |            | -   | 0.042 | -   |      |

|        | Gain Error   |            | -   | 0.041 | -   |      |

- 1. These are based on characterization.

- 2. Hysteresis disabled.

- 3. Hysteresis enabled.

## 47.4.7 Voltage Reference Characteristics

## Table 47-16. Voltage Reference Characteristics<sup>(1)</sup>

| Symbol            | Parameter                                | Conditions                  | Min.  | Тур.         | Max.  | Units |

|-------------------|------------------------------------------|-----------------------------|-------|--------------|-------|-------|

| ADC / SDADC / DAC | ADC, SDADC,<br>DAC Internal<br>reference | nom. 1.024V                 | 1.003 | 1.024        | 1.045 | V     |

| Ref               |                                          | VDDANA=5.0V                 |       |              |       |       |

|                   |                                          | Ta= 25°C                    |       |              |       |       |

|                   |                                          | nom. 2.048V                 | 2.007 | 2.048        | 2.089 |       |

|                   |                                          | VDDANA=5.0V                 |       |              |       |       |

|                   |                                          | Ta= 25°C                    |       |              |       |       |

|                   |                                          | nom. 4.096V                 | 4.014 | 4.096        | 4.178 |       |

|                   |                                          | VDDANA=5.0V                 |       |              |       |       |

|                   |                                          | Ta= 25°C                    |       |              |       |       |

|                   | Reference<br>temperature<br>coefficient  | Drift over [-40, +25]°C     | -     | -0.016/0.028 | -     | %/°C  |

|                   |                                          | Drift over [+25, +85]°C     | _     | -0.022/0.029 | _     |       |

|                   |                                          | Drift over [+25,<br>+105]°C | -     | -0.031/0.03  | -     |       |

|                   | Reference supply coefficient             | Drift over [2.7, 5.5]V      | -     | -0.2/0.3     | -     | %/V   |

1. These are based on characterization.

## 47.5 NVM Characteristics

## Table 47-17. NVM Max Speed caracteristics

| CPU F <sub>MAX</sub> (MHz) | 0WS | 1WS | 2WS |

|----------------------------|-----|-----|-----|

| VDD>2.7V                   | 19  | 38  | 48  |

| VDD>4.5V                   | 19  | 38  | 48  |