#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g15a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Two 24-bit Timer/Counters and one 16-bit Timer/Counter for Control (TCC), with extended functions:

- Up to four compare channels with optional complementary output

- Generation of synchronized pulse width modulation (PWM) pattern across port pins

- Deterministic fault protection, fast decay and configurable dead-time between complementary output

- Dithering that increase resolution with up to 5 bit and reduce quantization error

- Frequency Meter (The division reference clock is only available in the SAM C21N)

- 32-bit Real Time Counter (RTC) with clock/calendar function

- Watchdog Timer (WDT)

- CRC-32 generator

- Up to two Controller Area Network (CAN) interfaces:

- CAN 2.0A/B

- CAN-FD 1.0

- Each CAN interface have two selectable pin locations to switch between two external CAN transceivers (without the need for an external switch)

- Up to eight Serial Communication Interfaces (SERCOM), each configurable to operate as either:

- USART with full-duplex and single-wire half-duplex configuration

- I<sup>2</sup>C up to 3.4 MHz (Except SERCOM6 and SERCOM7)

- SPI

- LIN master/slave

- RS-485

- PMBus

- One Configurable Custom Logic (CCL)

- Up to Two 12-bit, 1 Msps Analog-to-Digital Converter (ADC) with up to 12 channels each (20 unique channels)

- Differential and single-ended input

- Automatic offset and gain error compensation

- Oversampling and decimation in hardware to support 13-, 14-, 15- or 16-bit resolution

- One 16-bit Sigma-Delta Analog-to-Digital Converter (SDADC) with up to 3 differential channels

- 10-bit, 350 ksps Digital-to-Analog Converter (DAC)

- Up to four Analog Comparators (AC) with Window Compare function

- Integrated Temperature Sensor

- Peripheral Touch Controller (PTC)

- 256-Channel capacitive touch and proximity sensing

#### I/O

•

• Up to 84 programmable I/O pins

#### Packages

- 100-pin TQFP

- 64-pin TQFP, QFN

- 56-pin WLCSP

- 48-pin TQFP, QFN

- 32-pin TQFP, QFN

#### General

| 35.2.                                                                                                                                                                                                                                                                                        | Features                                                                                                                                                                                                                                                                                                                                                                                                                             | 701                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 35.3.                                                                                                                                                                                                                                                                                        | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                        | 702                                                                                                                                      |

| 35.4.                                                                                                                                                                                                                                                                                        | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

| 35.5.                                                                                                                                                                                                                                                                                        | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                 | 703                                                                                                                                      |

| 35.6.                                                                                                                                                                                                                                                                                        | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                               | 704                                                                                                                                      |

| 35.7.                                                                                                                                                                                                                                                                                        | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                 | 720                                                                                                                                      |

| 36. TCC                                                                                                                                                                                                                                                                                      | C – Timer/Counter for Control Applications                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |

| 36.1.                                                                                                                                                                                                                                                                                        | Overview                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Features                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

| 37 CCI                                                                                                                                                                                                                                                                                       | _ – Configurable Custom Logic                                                                                                                                                                                                                                                                                                                                                                                                        | 849                                                                                                                                      |

|                                                                                                                                                                                                                                                                                              | Overview                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Features                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| 37.8.                                                                                                                                                                                                                                                                                        | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |

|                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                      | 863                                                                                                                                      |

| 38. ADC                                                                                                                                                                                                                                                                                      | C – Analog-to-Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |

| 38. ADC<br>38.1.                                                                                                                                                                                                                                                                             | C – Analog-to-Digital Converter<br>Overview                                                                                                                                                                                                                                                                                                                                                                                          | 863<br>867<br>867                                                                                                                        |

| 38. ADC<br>38.1.<br>38.2.                                                                                                                                                                                                                                                                    | C – Analog-to-Digital Converter<br>Overview<br>Features                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.                                                                                                                                                                                                                                                           | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.3.                                                                                                                                                                                                                                                  | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.4.<br>38.5.                                                                                                                                                                                                                                         | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies                                                                                                                                                                                                                                                                                                               |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.4.<br>38.5.<br>38.5.<br>38.6.                                                                                                                                                                                                                       | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description.                                                                                                                                                                                                                                                                                    |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.4.<br>38.5.<br>38.6.<br>38.6.<br>38.7.                                                                                                                                                                                                              | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary                                                                                                                                                                                                                                                                 | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>869                                                                              |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> </ul>                                                                                                                                          | C – Analog-to-Digital Converter.<br>Overview.<br>Features.<br>Block Diagram.<br>Signal Description.<br>Product Dependencies.<br>Functional Description.<br>Register Summary.<br>Register Description.                                                                                                                                                                                                                                | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>886<br>886                                                                       |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.4.<br>38.5.<br>38.6.<br>38.7.<br>38.8.<br>39. SDA                                                                                                                                                                                                   | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter                                                                                                                                                                                        |                                                                                                                                          |

| 38. ADC<br>38.1.<br>38.2.<br>38.3.<br>38.4.<br>38.5.<br>38.6.<br>38.6.<br>38.7.<br>38.8.<br>39. SDA<br>39.1.                                                                                                                                                                                 | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview                                                                                                                                                                            | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>886<br>887<br>                                                                   |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> </ul>                                                                                           | C – Analog-to-Digital Converter<br>Overview                                                                                                                                                                                                                                                                                                                                                                                          | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>887<br>886<br>887<br>906<br>906                                                  |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> </ul>                                                                            | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram                                                                                                                           |                                                                                                                                          |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> </ul>                                                             | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description.                                                                                                                        | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>871<br>886<br>887<br>906<br>906<br>907                                           |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> <li>39.5.</li> </ul>                                              | C – Analog-to-Digital Converter<br>Overview<br>Features.<br>Block Diagram<br>Signal Description.<br>Product Dependencies.<br>Functional Description.<br>Register Summary<br>Register Description.<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview.<br>Features<br>Block Diagram.<br>Signal Description.<br>Product Dependencies.                                                                                        | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>887<br>886<br>887<br>906<br>906<br>907<br>907<br>908                             |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> <li>39.5.</li> <li>39.6.</li> </ul>                               | C – Analog-to-Digital Converter<br>Overview<br>Features.<br>Block Diagram<br>Signal Description.<br>Product Dependencies.<br>Functional Description.<br>Register Summary<br>Register Description.<br>ADC – Sigma-Delta Analog-to-Digital Converter.<br>Overview.<br>Features.<br>Block Diagram<br>Signal Description.<br>Product Dependencies.<br>Functional Description.                                                            | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>871<br>886<br>887<br>906<br>906<br>906<br>907<br>907<br>908<br>909               |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> <li>39.5.</li> <li>39.6.</li> <li>39.7.</li> </ul>                | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Product Dependencies<br>Functional Description<br>Register Summary | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>887<br>906<br>906<br>906<br>907<br>907<br>907<br>909<br>917                      |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> <li>39.5.</li> <li>39.6.</li> <li>39.7.</li> </ul>                | C – Analog-to-Digital Converter<br>Overview<br>Features.<br>Block Diagram<br>Signal Description.<br>Product Dependencies.<br>Functional Description.<br>Register Summary<br>Register Description.<br>ADC – Sigma-Delta Analog-to-Digital Converter.<br>Overview.<br>Features.<br>Block Diagram<br>Signal Description.<br>Product Dependencies.<br>Functional Description.                                                            | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>869<br>887<br>906<br>906<br>906<br>907<br>907<br>907<br>909<br>917                      |

| <ul> <li>38. ADC</li> <li>38.1.</li> <li>38.2.</li> <li>38.3.</li> <li>38.4.</li> <li>38.5.</li> <li>38.6.</li> <li>38.7.</li> <li>38.8.</li> <li>39. SDA</li> <li>39.1.</li> <li>39.2.</li> <li>39.3.</li> <li>39.4.</li> <li>39.5.</li> <li>39.6.</li> <li>39.7.</li> <li>39.8.</li> </ul> | C – Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>ADC – Sigma-Delta Analog-to-Digital Converter<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Product Dependencies<br>Functional Description<br>Register Summary | 863<br>867<br>867<br>867<br>869<br>869<br>869<br>880<br>887<br>906<br>906<br>906<br>907<br>907<br>907<br>907<br>908<br>909<br>917<br>918 |

#### PM – Power Manager

#### 11.4.3 Clocks

The PAC bus clock (CLK\_PAC\_APB) can be enabled and disabled in the Main Clock module. The default state of CLK\_PAC\_APB can be found in the related links.

#### Related Links

MCLK – Main Clock Peripheral Clock Masking

#### 11.4.4 DMA

Not applicable.

#### 11.4.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the PAC interrupt requires the Interrupt Controller to be configured first.

#### Table 11-1. Interrupt Lines

| Instances | NVIC Line |

|-----------|-----------|

| PAC       | PACERR    |

#### **Related Links**

Nested Vector Interrupt Controller

#### 11.4.6 Events

The events are connected to the Event System, which may need configuration.

#### Related Links

EVSYS – Event System

#### 11.4.7 Debug Operation

When the CPU is halted in debug mode, write protection of all peripherals is disabled and the PAC continues normal operation.

#### 11.4.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Write Control (WRCTRL) register

- AHB Slave Bus Interrupt Flag Status and Clear (INTFLAGAHB) register

- Peripheral Interrupt Flag Status and Clear n (INTFLAG A/B/C...) registers

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### 11.5 Functional Description

#### 11.5.1 Principle of Operation

The Peripheral Access Control module allows the user to set a write protection on peripheral modules and generate an interrupt in case of a peripheral access violation. The peripheral's protection can be set,

Name:

STATUSA

Offset:

0x34 [ID-00000a18]

Reset:

0x000000

Property:

–

| Bit    | 31   | 30   | 29         | 28      | 27    | 26   | 25  | 24  |

|--------|------|------|------------|---------|-------|------|-----|-----|

|        |      |      |            |         |       |      |     |     |

| Access |      |      |            |         |       |      |     |     |

| Reset  |      |      |            |         |       |      |     |     |

|        |      |      |            |         |       |      |     |     |

| Bit    | 23   | 22   | 21         | 20      | 19    | 18   | 17  | 16  |

|        |      |      |            |         |       |      |     |     |

| Access |      |      |            |         |       |      |     |     |

| Reset  |      |      |            |         |       |      |     |     |

|        |      |      |            |         |       |      |     |     |

| Bit    | 15   | 14   | 13         | 12      | 11    | 10   | 9   | 8   |

|        |      |      |            | TSENS   | FREQM | EIC  | RTC | WDT |

| Access |      |      |            | R       | R     | R    | R   | R   |

| Reset  |      |      |            | 0       | 0     | 0    | 0   | 0   |

|        |      |      |            |         |       |      |     |     |

| Bit    | 7    | 6    | 5          | 4       | 3     | 2    | 1   | 0   |

|        | GCLK | SUPC | OSC32KCTRL | OSCCTRL | RSTC  | MCLK | PM  | PAC |

| Access | R    | R    | R          | R       | R     | R    | R   | R   |

| Reset  | 0    | 0    | 0          | 0       | 0     | 0    | 0   | 0   |

Bit 12 – TSENS: Peripheral TSENS Write Protection Status

Bit 11 – FREQM: Peripheral FREQM Write Protection Status

Bit 10 – EIC: Peripheral EIC Write Protection Status

**Bit 9 – RTC: Peripheral RTC Write Protection Status**

- Bit 8 WDT: Peripheral WDT Write Protection Status

- Bit 7 GCLK: Peripheral GCLK Write Protection Status

- Bit 6 SUPC: Peripheral SUPC Write Protection Status

- Bit 5 OSC32KCTRL: Peripheral OSC32KCTRL Write Protection Status

- Bit 4 OSCCTRL: Peripheral OSCCTRL Write Protection Status

- Bit 3 RSTC: Peripheral RSTC Write Protection Status

- Bit 2 MCLK: Peripheral MCLK Write Protection Status

- Bit 1 PM: Peripheral PM Write Protection Status

- **Bit 0 PAC:** Peripheral PAC Write Protection Status

- CLKFAIL Clock Failure. A 0-to-1 transition on the STATUS.CLKFAIL bit is detected

- OSC48MRDY 48MHz Internal Oscillator Ready: A 0-to-1 transition on the STATUS.OSC48MRDY bit is detected

- DPLL-related:

- DPLLLOCKR DPLL Lock Rise: A 0-to-1 transition of the STATUS.DPLLLOCKR bit is detected

- DPLLLOCKF DPLL Lock Fall: A 0-to-1 transition of the STATUS.DPLLLOCKF bit is detected

- DPLLLTTO DPLL Lock Timer Time-out: A 0-to-1 transition of the STATUS.DPLLLTTO bit is detected

- DPLLLDRTO DPLL Loop Divider Ratio Update Complete. A 0-to-1 transition of the STATUS.DPLLLDRTO bit is detected

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the OSCCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSCCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

Note: The interrupts must be globally enabled for interrupt requests to be generated.

#### 20.6.8 Events

The CFD can generate the following output event:

Clock Failure (CLKFAIL): Generated when the Clock Failure status bit is set in the Status register (STATUS.CLKFAIL). The CFD event is not generated when the Clock Switch bit (STATUS.CLKSW) in the Status register is set.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.CFDEO) enables the CFD output event. Writing a '0' to this bit disables the CFD output event. Refer to the Event System chapter for details on configuring the event system.

#### 20.6.9 Synchronization

#### OSC48M

Due to the multiple clock domains, values in the OSC48M control registers need to be synchronized to other clock domains.

When executing an operation that requires synchronization, the relevant synchronization bit in the Synchronization Busy register (OSC48MSYNCBUSY) will be set immediately, and cleared when synchronization is complete.

The following registers need synchronization when written:

OSC48M Divider register (OSC48MDIV)

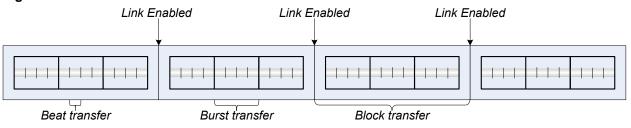

#### Figure 25-2. DMA Transfer Sizes

DMA transaction

- Beat transfer: The size of one data transfer bus access, and the size is selected by writing the Beat Size bit group in the Block Transfer Control register (BTCTRL.BEATSIZE)

- Burst transfer: Defined as n beat transfers, where n will differ from one device family to another. A burst transfer is atomic, cannot be interrupted and the length of the burst is selected by writing the Burst Length bit group in each Channel n Control A register (CHCTRLA.BURSTLEN).

- Block transfer: The amount of data one transfer descriptor can transfer, and the amount can range from 1 to 64k beats. A block transfer can be interrupted, in contrast to the burst transfer.

- Transaction: The DMAC can link several transfer descriptors by having the first descriptor pointing to the second and so forth, as shown in the figure above. A DMA transaction is the complete transfer of all blocks within a linked list.

A transfer descriptor describes how a block transfer should be carried out by the DMAC, and it must remain in SRAM. For further details on the transfer descriptor refer to Transfer Descriptors.

The figure above shows several block transfers linked together, which are called linked descriptors. For further information about linked descriptors, refer to Linked Descriptors.

A DMA transfer is initiated by an incoming transfer trigger on one of the DMA channels. This trigger can be configured to be either a software trigger, an event trigger, or one of the dedicated peripheral triggers. The transfer trigger will result in a DMA transfer request from the specific channel to the arbiter. If there are several DMA channels with pending transfer requests, the arbiter chooses which channel is granted access to become the active channel. The DMA channel granted access as the active channel will carry out the transaction as configured in the transfer descriptor. A current transaction can be interrupted by a higher prioritized channel after each burst transfer, but will resume the block transfer when the according DMA channel is granted access as the active channel again.

For each beat transfer, an optional output event can be generated. For each block transfer, optional interrupts and an optional output event can be generated. When a transaction is completed, dependent of the configuration, the DMA channel will either be suspended or disabled.

#### 25.6.1.2 CRC

The internal CRC engine supports two commonly used CRC polynomials: CRC-16 (CRC-CCITT) and CRC-32 (IEEE 802.3). It can be used on a selectable DMA channel, or on the I/O interface. Refer to CRC Operation for details.

#### 25.6.2 Basic Operation

#### 25.6.2.1 Initialization

The following DMAC registers are enable-protected, meaning that they can only be written when the DMAC is disabled (CTRL.DMAENABLE=0):

- Descriptor Base Memory Address register (BASEADDR)

- Write-Back Memory Base Address register (WRBADDR)

more transfer requests while one is already pending, the additional ones will be lost. All channels pending status flags are also available in the Pending Channels register (PENDCH).

When the transfer starts, the corresponding Channel Busy status flag is set in Channel Status register (CHSTATUS.BUSY). When the trigger action is complete, the Channel Busy status flag is cleared. All channel busy status flags are also available in the Busy Channels register (BUSYCH) in DMAC.

#### 25.6.2.7 Addressing

Each block transfer needs to have both a source address and a destination address defined. The source address is set by writing the Transfer Source Address (SRCADDR) register, the destination address is set by writing the Transfer Destination Address (SRCADDR) register.

The addressing of this DMAC module can be static or incremental, for either source or destination of a block transfer, or both.

Incrementation for the source address of a block transfer is enabled by writing the Source Address Incrementation Enable bit in the Block Transfer Control register (BTCTRL.SRCINC=1). The step size of the incrementation is configurable and can be chosen by writing the Step Selection bit in the Block Transfer Control register (BTCTRL.STEPSEL=1) and writing the desired step size in the Address Increment Step Size bit group in the Block Transfer Control register (BTCTRL.STEPSIZE). If BTCTRL.STEPSEL=0, the step size for the source incrementation will be the size of one beat.

When source address incrementation is configured (BTCTRL.SRCINC=1), SRCADDR is calculated as follows:

#### If **BTCTRL**.STEPSEL=1:

### $SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1) \cdot 2^{STEPSIZE}$

If **BTCTRL**.STEPSEL=0:

$SRCADDR = SRCADDR_{START} + BTCNT \cdot (BEATSIZE + 1)$

- SRCADDR<sub>START</sub> is the source address of the first beat transfer in the block transfer

- BTCNT is the initial number of beats remaining in the block transfer

- BEATSIZE is the configured number of bytes in a beat

- STEPSIZE is the configured number of beats for each incrementation

The following figure shows an example where DMA channel 0 is configured to increment the source address by one beat after each beat transfer (BTCTRL.SRCINC=1), and DMA channel 1 is configured to increment the source address by two beats (BTCTRL.SRCINC=1, BTCTRL.STEPSEL=1, and BTCTRL.STEPSIZE=0x1). As the destination address for both channels are peripherals, destination incrementation is disabled (BTCTRL.DSTINC=0).

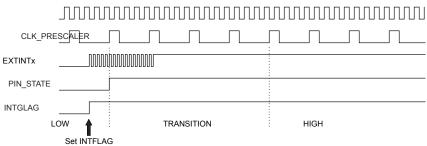

# Figure 26-3. EXTINT Pin Synchronous Debouncing (Rising Edge)

In the synchronous edge detection mode, the EIC clock is required. The synchronous edge detection mode can be used in Idle and Standby sleep modes.

**Asynchronous edge detection** In this mode, the external interrupt (EXTINT) pin directly drives an asynchronous edges detector which triggers any rising or falling edge on the pin:

- 1. Any edge detected that indicates a transition from the current valid pin state will immediately set the valid pin state PINSTATE.PINSTATE[x] to the detected level.

- 2. The external interrupt flag (INTFLAG.EXTINT[x] is immediately changed.

- 3. The edge detector will then be idle until no other rising or falling edge transition is detected during 4 consecutive ticks of the low frequency clock.

- 4. Any rising or falling edge transition detected during the idle state will return the transition counter to 0.

- 5. After 4 consecutive ticks of the low frequency clock without bounce detected, the edge detector is ready for a new detection.

#### Figure 26-4. EXTINT Pin Asynchronous Debouncing (Rising Edge)

In this mode, the EIC clock is requested. The asynchronous edge detection mode can be used in Idle and Standby sleep modes.

#### 26.6.5 DMA Operation

Not applicable.

#### 26.6.6 Interrupts

The EIC has the following interrupt sources:

- External interrupt pins (EXTINTx). See Basic Operation.

- Non-maskable interrupt pin (NMI). See Additional Features.

Each interrupt source has an associated interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when an interrupt condition occurs (NMIFLAG for NMI). Each interrupt, except NMI, can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

© 2017 Microchip Technology Inc.

| Bit    | 31             | 30 | 29 | 28     | 27       | 26 | 25 | 24 |

|--------|----------------|----|----|--------|----------|----|----|----|

|        | PBLDATA[31:24] |    |    |        |          |    |    |    |

| Access | R              | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1              | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |                |    |    |        |          |    |    |    |

| Bit    | 23             | 22 | 21 | 20     | 19       | 18 | 17 | 16 |

|        |                |    |    | PBLDAT | A[23:16] |    |    |    |

| Access | R              | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1              | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |                |    |    |        |          |    |    |    |

| Bit    | 15             | 14 | 13 | 12     | 11       | 10 | 9  | 8  |

|        | PBLDATA[15:8]  |    |    |        |          |    |    |    |

| Access | R              | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1              | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |                |    |    |        |          |    |    |    |

| Bit    | 7              | 6  | 5  | 4      | 3        | 2  | 1  | 0  |

|        |                |    |    | PBLDA  | TA[7:0]  |    |    |    |

| Access | R              | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1              | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

# Bits 31:0 – PBLDATA[31:0]: Page Buffer Load Data (Bits 63:32])Once the dimension element functions are supported the bit description must be updated to bit names becomes PBLDATA[63:32] in the register table.

The PBLDATA register is a holding register for partial AHB writes to the same 64-bit page buffer section. Page buffer loads are performed on a 64-bit basis.

This is a read only register.

| Value | Name | Description                             |

|-------|------|-----------------------------------------|

| 0x2   | CLR  | Clear output register of pin on event.  |

| 0x3   | TGL  | Toggle output register of pin on event. |

#### Table 28-5. PORT Event x Pin Identifier ( x = [3..0] )

| Value | Name  | Description                            |

|-------|-------|----------------------------------------|

| 0x0   | PIN0  | Event action to be executed on PIN 0.  |

| 0x1   | PIN1  | Event action to be executed on PIN 1.  |

|       |       |                                        |

| 0x31  | PIN31 | Event action to be executed on PIN 31. |

#### 28.9.13 Peripheral Multiplexing n

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to 16 Peripheral Multiplexing registers in each group, one for every set of two subsequent I/O lines. The n denotes the number of the set of I/O lines.

Name:PMUXOffset:0x30 + n\*0x01 [n=0..15]Property:PAC Write-Protection

| Bit    | 7          | 6  | 5  | 4  | 3  | 2    | 1      | 0  |

|--------|------------|----|----|----|----|------|--------|----|

|        | PMUXO[3:0] |    |    |    |    | PMUX | Æ[3:0] |    |

| Access | RW         | RW | RW | RW | RW | RW   | RW     | RW |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0    | 0      | 0  |

#### Bits 7:4 – PMUXO[3:0]: Peripheral Multiplexing for Odd-Numbered Pin

These bits select the peripheral function for odd-numbered pins  $(2^n + 1)$  of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations*.

These bits are not synchronized.

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0x0   | Standard-mode (Sm) up to 100 kHz and Fast-mode (Fm) up to 400 kHz |

| 0x1   | Fast-mode Plus (Fm+) up to 1 MHz                                  |

| 0x2   | High-speed mode (Hs-mode) up to 3.4 MHz                           |

| 0x3   | Reserved                                                          |

#### Bit 23 – SEXTTOEN: Slave SCL Low Extend Time-Out

This bit enables the slave SCL low extend time-out. If SCL is cumulatively held low for greater than 25ms from the initial START to a STOP, the slave will release its clock hold if enabled and reset the internal state machine. Any interrupt flags set at the time of time-out will remain set. If the address was recognized, PREC will be set when a STOP is received.

This bit is not synchronized.

| Value | Description       |

|-------|-------------------|

| 0     | Time-out disabled |

| 1     | Time-out enabled  |

#### Bits 21:20 – SDAHOLD[1:0]: SDA Hold Time

These bits define the SDA hold time with respect to the negative edge of SCL.

These bits are not synchronized.

| Value | Name | Description         |

|-------|------|---------------------|

| 0x0   | DIS  | Disabled            |

| 0x1   | 75   | 50-100ns hold time  |

| 0x2   | 450  | 300-600ns hold time |

| 0x3   | 600  | 400-800ns hold time |

#### Bit 16 – PINOUT: Pin Usage

This bit sets the pin usage to either two- or four-wire operation:

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | 4-wire operation disabled |

| 1     | 4-wire operation enabled  |

#### Bit 7 – RUNSTDBY: Run in Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Disabled – All reception is dropped. |

| 1     | Wake on address match, if enabled.   |

#### Bits 4:2 – MODE[2:0]: Operating Mode

These bits must be written to 0x04 to select the I<sup>2</sup>C slave serial communication interface of the SERCOM.

These bits are not synchronized.

#### 34.4 Signal Description

Table 34-1. Signal Description

| Signal | Description  | Туре           |

|--------|--------------|----------------|

| CAN_TX | CAN transmit | Digital output |

| CAN_RX | CAN receive  | Digital input  |

Refer to for details on the pin mapping for this peripheral. One signal can be mapped to one of several pins.

#### **Related Links**

I/O Multiplexing and Considerations

#### 34.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 34.5.1 I/O Lines

Using the CAN's I/O lines requires the I/O pins to be configured.

#### **Related Links**

PORT - I/O Pin Controller

#### 34.5.2 Power Management

The CAN will continue to operate in any Idle sleep mode where the selected source clock is running. The CAN interrupts can be used to wake up the device from sleep modes. Refer to the Power Manager chapter for details on the different sleep modes.

The CAN module has its own low power mode. The clock sources cannot be halted while the CAN is enabled unless this mode is used. Refer to Sleep Mode Operation.

Related Links Sleep Mode Operation

#### 34.5.3 Clocks

The CAN bus clock (CLK\_CAN\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_CAN\_APB can be found in the Peripheral Clock Masking section.

A generic clock (GCLK\_CAN) is required to clock the CAN. This clock must be configured and enabled in the generic clock controller before using the CAN.

This generic clock is asynchronous to the bus clock (CLK\_CAN\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains.

#### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

#### 34.5.4 DMA

The CAN has a built-in Direct Memory Access (DMA) and will read/write data to/from the system RAM when a USB transaction takes place. No CPU or DMA Controller (DMAC) resources are required.

Due to the synchronization mechanism between GCLK\_CAN and GCLK\_CAN\_APB domains, there may be a delay of several GCLK\_CAN\_APB periods between writing to TEST.TX until the new configuration is visible at output pin CAN\_TX. This applies also when reading input pin CAN\_RX via TEST.RX.

Note: Test modes should be used for production tests or self test only. The software control for pin CAN\_TX interferes with all CAN protocol functions. It is not recommended to use test modes for application.

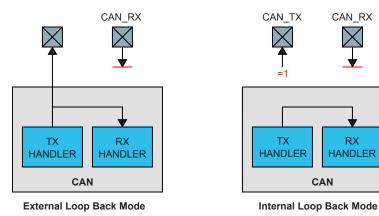

#### External Loop Back Mode

The CAN can be set in External Loop Back Mode by programming TEST.LBCK to '1'. In Loop Back Mode, the CAN treats its own transmitted messages as received messages and stores them (if they pass acceptance filtering) into an Rx Buffer or an Rx FIFO. The figure below shows the connection of signals CAN\_TX and CAN\_RX to the CAN in External Loop Back Mode.

This mode is provided for hardware self-test. To be independent from external stimulation, the CAN ignores acknowledge errors (recessive bit sampled in the acknowledge slot of a data/remote frame) in Loop Back Mode. In this mode the CAN performs an internal feedback from its Tx output to its Rx input. The actual value of the CAN\_RX input pin is disregarded by the CAN. The transmitted messages can be monitored at the CAN\_TX pin.

#### Internal Loop Back Mode

Internal Loop Back Mode is entered by programming bits TEST.LBCK and CCCR.MON to '1'. This mode can be used for a "Hot Selftest", meaning the CAN can be tested without affecting a running CAN system connected to the pins CAN\_TX and CAN\_RX. In this mode pin CAN\_RX is disconnected from the CAN and pin CAN\_TX is held recessive. The figure below shows the connection of CAN\_TX and CAN\_RX to the CAN in case of Internal Loop Back Mode.

#### Figure 34-4. Pin Control in Loop Back Modes

#### 34.6.3 Timestamp Generation

For timestamp generation the CAN supplies a 16-bit wrap-around counter. A prescaler TSCC.TCP can be configured to clock the counter in multiples of CAN bit times (1...16). The counter is readable via TSCV.TSC. A write access to register TSCV resets the counter to zero. When the timestamp counter wraps around interrupt flag IR.TSW is set.

On start of frame reception / transmission the counter value is captured and stored into the timestamp section of an Rx Buffer / Rx FIFO (RXTS[15:0]) or Tx Event FIFO (TXTS[15:0]) element.

| Bit    | 31  | 30  | 29  | 28  | 27    | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-------|-----|-----|-----|

|        |     |     |     |     |       |     |     |     |

| Access |     |     |     |     |       |     |     |     |

| Reset  |     |     |     |     |       |     |     |     |

|        |     |     |     |     |       |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19    | 18  | 17  | 16  |

|        |     |     |     |     |       |     |     |     |

| Access |     |     |     | L   |       |     |     |     |

| Reset  |     |     |     |     |       |     |     |     |

|        |     |     |     |     |       |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9   | 8   |

| [      |     |     |     | TOC | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1   |

|        |     |     |     |     |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0   |

| [      |     |     |     | TOC | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1   |

#### Bits 15:0 – TOC[15:0]: Timeout Counter

The Timeout Counter is decremented in multiples of CAN bit times [1...16] depending on the configuration of TSCC.TCP. When decremented to zero, interrupt flag IR.TOO is set and the Timeout Counter is stopped. Start and reset/restart conditions are configured via TOCC.TOS.

#### 34.8.13 Error Counter

**Note:** When CCCR.ASM is set, the CAN protocol controller does not increment TECand REC when a CAN protocol error is detected, but CEL is still incremented.

Name:

ECR

Offset:

0x40 [ID-0000a4bb]

Reset:

0x00000000

Property:

Read-only

These bits are not synchronized.

| Value | Name   | Description                                                                    |

|-------|--------|--------------------------------------------------------------------------------|

| 0x0   | GCLK   | Reload or reset the counter on next generic clock                              |

| 0x1   | PRESC  | Reload or reset the counter on next prescaler clock                            |

| 0x2   | RESYNC | Reload or reset the counter on next generic clock. Reset the prescaler counter |

| 0x3   | -      | Reserved                                                                       |

#### Bits 3:2 – MODE[1:0]: Timer Counter Mode

These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 35.7.1.2 Control B Clear

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

| Value | Name | Description                                |

|-------|------|--------------------------------------------|

| 0x6   | PWP  | Period captured in CC1, pulse width in CC0 |

| 0x7   | PW   | Pulse width capture                        |

#### 35.7.3.5 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

|        |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

#### Bit 4 – MCx: Match or Capture Channel x Interrupt Enable

Writing a '0' to these bits has no effect.

Writing a '1' to MCx will clear the corresponding Match or Capture Channel x Interrupt Enable bit, which disables the Match or Capture Channel x interrupt.

|   | /alue | Description                                           |

|---|-------|-------------------------------------------------------|

| ( | )     | The Match or Capture Channel x interrupt is disabled. |

| • |       | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR: Error Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### **Bit 0 – OVF: Overflow Interrupt Disable**

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### 35.7.3.6 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Value  | Name | Description     |

|--------|------|-----------------|

| 0x18   | GND  | Internal ground |

| 0x19 - | -    | Reserved        |

| 0x1F   |      |                 |

#### Bits 4:0 – MUXPOS[4:0]: Positive MUX Input Selection

These bits define the MUX selection for the positive ADC input. If the internal bandgap voltage input channel is selected, then the Sampling Time Length bit group in the Sampling Control register must be written with a corresponding value.

| Value | Name    | Description     |

|-------|---------|-----------------|

| 0x00  | AIN0    | ADC AIN0 pin    |

| 0x01  | AIN1    | ADC AIN1 pin    |

| 0x02  | AIN2    | ADC AIN2 pin    |

| 0x03  | AIN3    | ADC AIN3 pin    |

| 0x04  | AIN4    | ADC AIN4 pin    |

| 0x05  | AIN5    | ADC AIN5 pin    |

| 0x06  | AIN6    | ADC AIN6 pin    |

| 0x07  | AIN7    | ADC AIN7 pin    |

| 0x08  | AIN8    | ADC AIN8 pin    |

| 0x09  | AIN9    | ADC AIN9 pin    |

| 0x0A  | AIN10   | ADC AIN10 pin   |

| 0x0B  | AIN11   | ADC AIN11 pin   |

| 0xC - | -       | Reserved        |

| 0x17  |         |                 |

| 0x18  | -       | Reserved        |

| 0x19  | BANDGAP | Bandgap Voltage |

| 0x1C  | DAC     | DAC Output      |

| 0x1E  | -       | Reserved        |

| 0x1F  | -       | Reserved        |

#### 38.8.10 Control C

Name:CTRLCOffset:0x0A [ID-0000120e]Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

Name:CTRLBOffset:0x01Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |