#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g16a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SAM C20/C21

| SAM  | Pin <sup>(1)</sup><br>SAM | SAM C21J  | I/O Pin | Supply | A          | REF | ADC0    |         | B <sup>(2)(3)</sup><br>AC | РТС         | DAC | SDADC | C<br>SERCOM 2(3)   | D<br>SERCOM-ALT    | E<br>TC    | F<br>TCC       | G<br>COM             | H<br>AC/GCLK | I<br>CCL        |

|------|---------------------------|-----------|---------|--------|------------|-----|---------|---------|---------------------------|-------------|-----|-------|--------------------|--------------------|------------|----------------|----------------------|--------------|-----------------|

| C21E | C21G                      | SAW C2 IJ |         |        | EIC        | KEF | ADCU    | ADCT    | AC                        | FIC         | DAC | SDADC | (4)                | SERCOM-ALT         | тсс        |                | COM                  | AC/GOLK      | CCL             |

|      |                           |           |         |        |            |     |         |         |                           |             |     |       |                    |                    |            |                |                      |              | IN[3]           |

| 12   | 14                        | 18        | PA09    | VDDIO  | EXTINT[9]  |     | AIN[9]  | AIN[11] |                           | X[1]/Y[17]  |     |       | SERCOM0/<br>PAD[1] | SERCOM2/<br>PAD[1] | TCC0/WO[1] | TCC1/<br>WO[3] |                      |              | CCL1/<br>IN[4]  |

| 13   | 15                        | 19        | PA10    | VDDIO  | EXTINT[10] |     | AIN[10] |         |                           | X[2]/Y[18]  |     |       | SERCOM0/<br>PAD[2] | SERCOM2/<br>PAD[2] | TCC1/WO[0] | TCC0/<br>WO[2] |                      | GCLK_IO[4]   | CCL1/<br>IN[5]  |

| 14   | 16                        | 20        | PA11    | VDDIO  | EXTINT[11] |     | AIN[11] |         |                           | X[3]/Y[19]  |     |       | SERCOM0/<br>PAD[3] | SERCOM2/<br>PAD[3] | TCC1/WO[1] | TCC0/<br>WO[3] |                      | GCLK_IO[5]   | CCL1/<br>OUT[1] |

|      | 19                        | 23        | PB10    | VDDIO  | EXTINT[10] |     |         |         |                           |             |     |       |                    | SERCOM4/<br>PAD[2] | TC1/WO[0]  | TCC0/<br>WO[4] | CAN1/TX              | GCLK_IO[4]   | CCL1/<br>IN[5]  |

|      | 20                        | 24        | PB11    | VDDIO  | EXTINT[11] |     |         |         |                           |             |     |       |                    | SERCOM4/<br>PAD[3] | TC1/WO[1]  | TCC0/<br>WO[5] | CAN1/RX              | GCLK_IO[5]   | CCL1/<br>OUT[1] |

|      |                           | 25        | PB12    | VDDIO  | EXTINT[12] |     |         |         |                           | X[12]/Y[28] |     |       | SERCOM4/<br>PAD[0] |                    | TC0/WO[0]  | TCC0/<br>WO[6] |                      | GCLK_IO[6]   |                 |

|      |                           | 26        | PB13    | VDDIO  | EXTINT[13] |     |         |         |                           | X[13]/Y[29] |     |       | SERCOM4/<br>PAD[1] |                    | TC0/WO[1]  | TCC0/<br>WO[7] |                      | GCLK_IO[7]   |                 |

|      |                           | 27        | PB14    | VDDIO  | EXTINT[14] |     |         |         |                           | X[14]/Y[30] |     |       | SERCOM4/<br>PAD[2] |                    | TC1/WO[0]  |                | CAN1/TX              | GCLK_IO[0]   | CCL3/<br>IN[9]  |

|      |                           | 28        | PB15    | VDDIO  | EXTINT[15] |     |         |         |                           | X[15]/Y[31] |     |       | SERCOM4/<br>PAD[3] |                    | TC1/WO[1]  |                | CAN1/RX              | GCLK_IO[1]   | CCL3/<br>IN[10] |

|      | 21                        | 29        | PA12    | VDDIO  | EXTINT[12] |     |         |         |                           |             |     |       | SERCOM2/<br>PAD[0] | SERCOM4/<br>PAD[0] | TCC2/WO[0] | TCC0/<br>WO[6] |                      | AC/CMP[0]    |                 |

|      | 22                        | 30        | PA13    | VDDIO  | EXTINT[13] |     |         |         |                           |             |     |       | SERCOM2/<br>PAD[1] | SERCOM4/<br>PAD[1] | TCC2/WO[1] | TCC0/<br>WO[7] |                      | AC/CMP[1]    |                 |

| 15   | 23                        | 31        | PA14    | VDDIO  | EXTINT[14] |     |         |         |                           |             |     |       | SERCOM2/<br>PAD[2] | SERCOM4/<br>PAD[2] | TC4/WO[0]  | TCC0/<br>WO[4] |                      | GCLK_IO[0]   |                 |

| 16   | 24                        | 32        | PA15    | VDDIO  | EXTINT[15] |     |         |         |                           |             |     |       | SERCOM2/<br>PAD[3] | SERCOM4/<br>PAD[3] | TC4/WO[1]  | TCC0/<br>WO[5] |                      | GCLK_IO[1]   |                 |

| 17   | 25                        | 35        | PA16    | VDDIO  | EXTINT[0]  |     |         |         |                           | X[4]/Y[20]  |     |       | SERCOM1/<br>PAD[0] | SERCOM3/<br>PAD[0] | TCC2/WO[0] | TCC0/<br>WO[6] |                      | GCLK_IO[2]   | CCL0/<br>IN[0]  |

| 18   | 26                        | 36        | PA17    | VDDIO  | EXTINT[1]  |     |         |         |                           | X[5]/Y[21]  |     |       | SERCOM1/<br>PAD[1] | SERCOM3/<br>PAD[1] | TCC2/WO[1] | TCC0/<br>WO[7] |                      | GCLK_IO[3]   | CCL0/<br>IN[1]  |

| 19   | 27                        | 37        | PA18    | VDDIO  | EXTINT[2]  |     |         |         |                           | X[6]/Y[22]  |     |       | SERCOM1/<br>PAD[2] | SERCOM3/<br>PAD[2] | TC4/WO[0]  | TCC0/<br>WO[2] |                      | AC/CMP[0]    | CCL0/<br>IN[2]  |

| 20   | 28                        | 38        | PA19    | VDDIO  | EXTINT[3]  |     |         |         |                           | X[7]/Y[23]  |     |       | SERCOM1/<br>PAD[3] | SERCOM3/<br>PAD[3] | TC4/WO[1]  | TCC0/<br>WO[3] |                      | AC/CMP[1]    | CCL0/<br>OUT[0] |

|      |                           | 39        | PB16    | VDDIO  | EXTINT[0]  |     |         |         |                           |             |     |       | SERCOM5/<br>PAD[0] |                    | TC2/WO[0]  | TCC0/<br>WO[4] |                      | GCLK_IO[2]   | CCL3/<br>IN[11] |

|      |                           | 40        | PB17    | VDDIO  | EXTINT[1]  |     |         |         |                           |             |     |       | SERCOM5/<br>PAD[1] |                    | TC2/WO[1]  | TCC0/<br>WO[5] |                      | GCLK_IO[3]   | CCL3/<br>OUT[3] |

|      | 29                        | 41        | PA20    | VDDIO  | EXTINT[4]  |     |         |         |                           | X[8]/Y[24]  |     |       | SERCOM5/<br>PAD[2] | SERCOM3/<br>PAD[2] | TC3/WO[0]  | TCC0/<br>WO[6] |                      | GCLK_IO[4]   |                 |

|      | 30                        | 42        | PA21    | VDDIO  | EXTINT[5]  |     |         |         |                           | X[9]/Y[25]  |     |       | SERCOM5/<br>PAD[3] | SERCOM3/<br>PAD[3] | TC3/WO[1]  |                |                      | GCLK_IO[5]   |                 |

| 21   | 31                        | 43        | PA22    | VDDIO  | EXTINT[6]  |     |         |         |                           | X[10]/Y[26] |     |       | SERCOM3/<br>PAD[0] | SERCOM5/<br>PAD[0] | TC0/WO[0]  | TCC0/<br>WO[4] |                      | GCLK_IO[6]   | CCL2/<br>IN[6]  |

| 22   | 32                        | 44        | PA23    | VDDIO  | EXTINT[7]  |     |         |         |                           | X[11]/Y[27] |     |       | SERCOM3/<br>PAD[1] | SERCOM5/<br>PAD[1] | TC0/WO[1]  | TCC0/<br>WO[5] |                      | GCLK_IO[7]   | CCL2/<br>IN[7]  |

| 23   | 33                        | 45        | PA24    | VDDIO  | EXTINT[12] |     |         |         |                           |             |     |       | SERCOM3/<br>PAD[2] | SERCOM5/<br>PAD[2] | TC1/WO[0]  | TCC1/<br>WO[2] | CAN0/TX              | AC/CMP[2]    | CCL2/<br>IN[8]  |

| 24   | 34                        | 46        | PA25    | VDDIO  | EXTINT[13] |     |         |         |                           |             |     |       | SERCOM3/<br>PAD[3] | SERCOM5/<br>PAD[3] | TC1/WO[1]  | TCC1/<br>WO[3] | CAN0/RX              | AC/CMP[3]    | CCL2/<br>OUT[2] |

|      | 37                        | 49        | PB22    | VDDIN  | EXTINT[6]  |     |         |         |                           |             |     |       |                    | SERCOM5/<br>PAD[2] | TC3/WO[0]  |                | CAN0/TX              | GCLK_IO[0]   | CCL0/<br>IN[0]  |

|      | 38                        | 50        | PB23    | VDDIN  | EXTINT[7]  |     |         |         |                           |             |     |       |                    | SERCOM5/<br>PAD[3] | TC3/WO[1]  |                | CAN0/RX              | GCLK_IO[1]   |                 |

| 25   | 39                        | 51        | PA27    | VDDIN  | EXTINT[15] |     |         |         |                           |             | _   |       |                    | [0]                |            |                |                      | GCLK_IO[0]   |                 |

| 27   | 41                        | 53        | PA28    | VDDIN  | EXTINT[8]  |     |         |         |                           |             |     |       |                    |                    |            |                |                      | GCLK_IO[0]   |                 |

| 31   | 45                        | 57        | PA30    | VDDIN  | EXTINT[10] |     |         |         |                           |             |     |       |                    | SERCOM1/<br>PAD[2] | TCC1/WO[0] |                | CORTEX_M0P/<br>SWCLK | GCLK_IO[0]   | CCL1/<br>IN[3]  |

| 32   | 46                        | 58        | PA31    | VDDIN  | EXTINT[11] |     |         |         |                           |             |     |       |                    | SERCOM1/<br>PAD[3] | TCC1/WO[1] |                | CORTEX_M0P/<br>SWDIO |              | CCL1/<br>OUT[1] |

|      |                           | 59        | PB30    | VDDIN  | EXTINT[14] |     |         |         |                           |             |     |       |                    | SERCOM5/<br>PAD[0] | TCC0/WO[0] | TCC1/<br>WO[2] |                      | AC/CMP[2]    |                 |

|      |                           | 60        | PB31    |        | EXTINT[15] |     |         |         |                           |             |     |       |                    | SERCOM5/<br>PAD[1] | TCC0/WO[1] | TCC1/<br>WO[3] |                      | AC/CMP[3]    |                 |

|      |                           | 61        | PB00    | VDDANA | EXTINT[0]  |     |         | AIN[0]  |                           | Y[6]        |     |       |                    | SERCOM5/<br>PAD[2] | TC3/WO[0]  |                |                      |              | CCL0/<br>IN[1]  |

|      |                           | 62        | PB01    | VDDANA | EXTINT[1]  |     |         | AIN[1]  |                           | Y[7]        |     |       |                    | SERCOM5/<br>PAD[3] | TC3/WO[1]  |                |                      |              | CCL0/<br>IN[2]  |

|      | 47                        | 63        | PB02    | VDDANA | EXTINT[2]  |     |         | AIN[2]  |                           | Y[8]        |     |       |                    | SERCOM5/<br>PAD[0] | TC2/WO[0]  |                |                      |              | CCL0/<br>OUT[0] |

|      | 48                        | 64        | PB03    | VDDANA | EXTINT[3]  |     |         | AIN[3]  |                           | Y[9]        |     |       |                    | SERCOM5/<br>PAD[1] | TC2/WO[1]  |                |                      |              |                 |

# SAM C20/C21

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | B Clock             | AP    | B Clock             | Generic<br>Clock         | F     | PAC              |                                    | Events                                        | DMA                        |                  |

|---------------------|-----------------|-------------|-------|---------------------|-------|---------------------|--------------------------|-------|------------------|------------------------------------|-----------------------------------------------|----------------------------|------------------|

|                     |                 |             | Index | Enabled<br>at Reset | Index | Enabled<br>at Reset | Index                    | Index | Prot at<br>Reset | User                               | Generator                                     | Index                      | Sleep<br>Walking |

|                     |                 |             |       |                     |       |                     |                          |       |                  | 45: STOP                           |                                               |                            |                  |

| AHB-APB<br>Bridge C | 0x42000000      |             | 2     | Y                   |       |                     |                          |       |                  |                                    |                                               |                            | N/A              |

| EVSYS               | 0x42000000      | 8           |       |                     | 0     | N                   | 6-17: one per<br>CHANNEL | 0     | N                |                                    |                                               |                            | Y                |

| SERCOM0             | 0x42000400      | 9           |       |                     | 1     | N                   | 19: CORE<br>18: SLOW     | 1     | N                |                                    |                                               | 2: RX<br>3: TX             | Y                |

| SERCOM1             | 0x42000800      | 10          |       |                     | 2     | N                   | 20: CORE<br>18: SLOW     | 2     | N                |                                    |                                               | 4: RX<br>5: TX             | Y                |

| SERCOM2             | 0x42000C00      | 11          |       |                     | 3     | N                   | 21: CORE<br>18: SLOW     | 3     | N                |                                    |                                               | 6: RX<br>7: TX             | Y                |

| SERCOM3             | 0x42001000      | 12          |       |                     | 4     | N                   | 22: CORE<br>18: SLOW     | 4     | N                |                                    |                                               | 8: RX<br>9: TX             | Y                |

| SERCOM4             | 0x42001400      | 13          |       |                     | 5     | N                   | 23: CORE<br>18: SLOW     | 5     | N                |                                    |                                               | 10: RX<br>11: TX           | Y                |

| SERCOM5             | 0x42001800      | 14          |       |                     | 6     | N                   | 25: CORE<br>24: SLOW     | 6     | N                |                                    |                                               | 12: RX<br>13: TX           | Y                |

| CAN0                | 0x42001C00      | 15          | 8     | N                   |       |                     | 26                       |       |                  |                                    |                                               | 14: DEBUG                  | N/A              |

| CAN1                | 0x42002000      | 16          | 9     | N                   |       |                     | 27                       |       |                  |                                    |                                               | 15: DEBUG                  | N/A              |

| TCC0                | 0x42002400      | 17          |       |                     | 9     | N                   | 28                       | 9     | N                | 9-10: EV0-1<br>11-14:<br>MC0-3     | 34: OVF<br>35: TRG<br>36: CNT<br>37-40: MC0-3 | 16: OVF<br>17-20:<br>MC0-3 | Y                |

| TCC1                | 0x42002800      | 18          |       |                     | 10    | N                   | 28                       | 10    | N                | 15-16:<br>EV0-1<br>17-18:<br>MC0-1 | 41: OVF<br>42: TRG<br>43: CNT<br>44-45: MC0-1 | 21: OVF<br>22-23:<br>MC0-1 | Y                |

| TCC2                | 0x42002C00      | 19          |       |                     | 11    | N                   | 29                       | 11    | N                | 19-20:<br>EV0-1<br>21-22:<br>MC0-1 | 46: OVF<br>47: TRG<br>48: CNT<br>49-50: MC0-1 | 24: OVF<br>25-26:<br>MC0-1 | Y                |

| TCO                 | 0x42003000      | 20          |       |                     | 12    | N                   | 30                       | 12    | N                | 23: EVU                            | 51: OVF<br>52-53: MC0-1                       | 27: OVF<br>28-29:<br>MC0-1 | Y                |

| TC1                 | 0x42003400      | 21          |       |                     | 13    | N                   | 30                       | 13    | N                | 24: EVU                            | 54: OVF<br>55-56: MC0-1                       | 30: OVF<br>21-32:<br>MC0-1 | Y                |

| TC2                 | 0x42003800      | 22          |       |                     | 14    | N                   | 31                       | 14    | N                | 25: EVU                            | 57: OVF<br>58-59: MC0-1                       | 33: OVF<br>23-35:<br>MC0-1 | Y                |

| ТСЗ                 | 0x42003C00      | 23          |       |                     | 15    | N                   | 31                       | 15    | N                | 26: EVU                            | 60: OVF<br>61-62: MC0-1                       | 36: OVF<br>37-38:<br>MC0-1 | Y                |

| TC4                 | 0x42004000      | 24          |       |                     | 16    | N                   | 32                       | 16    | N                | 27: EVU                            | 63: OVF<br>64-65: MC0-1                       | 39: OVF<br>40-41:<br>MC0-1 | Y                |

| ADC0                | 0x42004400      | 25          |       |                     | 17    | N                   | 33                       | 17    | N                | 28: START<br>29: SYNC              | 66: RESRDY<br>67: WINMON                      | 42:<br>RESRDY              | Y                |

| ADC1                | 0x42004800      | 26          |       |                     | 18    | N                   | 34                       | 18    | N                | 30: START<br>31: SYNC              | 68: RESRDY<br>69: WINMON                      | 43:<br>RESRDY              | Y                |

| SDADC               | 0x42004C00      | 29          |       |                     | 19    | N                   | 35                       | 19    | N                | 32: START<br>33: FLUSH             | 70: RESRDY<br>71: WINMON                      | 44:<br>RESRDY              | Y                |

| AC                  | 0x42005000      | 27          |       |                     | 20    | N                   | 34                       | 20    | N                | 34-37:<br>SOC0-3                   | 72-75: COMP0-3<br>76-77: WIN0-1               |                            | Y                |

| Bit    | 31  | 30            | 29   | 28      | 27       | 26  | 25  | 24  |  |  |  |  |

|--------|-----|---------------|------|---------|----------|-----|-----|-----|--|--|--|--|

| [      |     |               |      | LENGT   | +[29:22] |     |     |     |  |  |  |  |

| Access | R/W | R/W           | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0   | 0             | 0    | 0       | 0        | 0   | 0   | 0   |  |  |  |  |

|        |     |               |      |         |          |     |     |     |  |  |  |  |

| Bit    | 23  | 22            | 21   | 20      | 19       | 18  | 17  | 16  |  |  |  |  |

|        |     | LENGTH[21:14] |      |         |          |     |     |     |  |  |  |  |

| Access | R/W | R/W           | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0   | 0             | 0    | 0       | 0        | 0   | 0   | 0   |  |  |  |  |

|        |     |               |      |         |          |     |     |     |  |  |  |  |

| Bit    | 15  | 14            | 13   | 12      | 11       | 10  | 9   | 8   |  |  |  |  |

|        |     |               |      | LENGT   | H[13:6]  |     |     |     |  |  |  |  |

| Access | R/W | R/W           | R/W  | R/W     | R/W      | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0   | 0             | 0    | 0       | 0        | 0   | 0   | 0   |  |  |  |  |

|        |     |               |      |         |          |     |     |     |  |  |  |  |

| Bit    | 7   | 6             | 5    | 4       | 3        | 2   | 1   | 0   |  |  |  |  |

|        |     |               | LENG | TH[5:0] |          |     |     |     |  |  |  |  |

| Access | R/W | R/W           | R/W  | R/W     | R/W      | R/W |     |     |  |  |  |  |

| Reset  | 0   | 0             | 0    | 0       | 0        | 0   |     |     |  |  |  |  |

## Bits 31:2 – LENGTH[29:0]: Length

Length in words needed for memory operations.

#### 13.13.6 Data

| Name:     | DATA                 |

|-----------|----------------------|

| Offset:   | 0x000C               |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

## 24.11 Register Summary - CLOCK

| Offset | Name       | Bit Pos. |           |        |        |        |            |          |          |           |

|--------|------------|----------|-----------|--------|--------|--------|------------|----------|----------|-----------|

| 0x00   |            | 7:0      | MATCHCLR  | CLKREP |        |        | MOE        | DE[1:0]  | ENABLE   | SWRST     |

| 0x01   | CTRLA      | 15:8     | CLOCKSYNC |        |        |        |            | PRESCA   | LER[3:0] |           |

| 0x02   |            |          |           |        |        |        |            |          |          |           |

|        | Reserved   |          |           |        |        |        |            |          |          |           |

| 0x03   |            |          |           |        |        |        |            |          |          |           |

| 0x04   |            | 7:0      | PEREOn    | PEREOn | PEREOn | PEREOn | PEREOn     | PEREOn   | PEREOn   | PEREOn    |

| 0x05   | EVCTRL     | 15:8     | OVFEO     |        |        |        |            |          |          | ALARMO0   |

| 0x06   | LVOIRE     | 23:16    |           |        |        |        |            |          |          |           |

| 0x07   |            | 31:24    |           |        |        |        |            |          |          |           |

| 0x08   | INTENCLR   | 7:0      | PERn      | PERn   | PERn   | PERn   | PERn       | PERn     | PERn     | PERn      |

| 0x09   | INTENCER   | 15:8     | OVF       |        |        |        |            |          |          | ALARM0    |

| 0x0A   | INTENSET   | 7:0      | PERn      | PERn   | PERn   | PERn   | PERn       | PERn     | PERn     | PERn      |

| 0x0B   | INTENSET   | 15:8     | OVF       |        |        |        |            |          |          | ALARM0    |

| 0x0C   | INTFLAG    | 7:0      | PERn      | PERn   | PERn   | PERn   | PERn       | PERn     | PERn     | PERn      |

| 0x0D   | INTELAG    | 15:8     | OVF       |        |        |        |            |          |          | ALARM0    |

| 0x0E   | DBGCTRL    | 7:0      |           |        |        |        |            |          |          | DBGRUN    |

| 0x0F   | Reserved   |          |           |        |        |        |            |          |          |           |

| 0x10   | - SYNCBUSY | 7:0      |           |        | ALARM0 |        | CLOCK      | FREQCORR | ENABLE   | SWRST     |

| 0x11   |            | 15:8     | CLOCKSYNC |        |        |        | MASK0      |          |          |           |

| 0x12   | 311000031  | 23:16    |           |        |        |        |            |          |          |           |

| 0x13   |            | 31:24    |           |        |        |        |            |          |          |           |

| 0x14   | FREQCORR   | 7:0      | SIGN      |        |        |        | VALUE[6:0] |          |          |           |

| 0x15   |            |          |           |        |        |        |            |          |          |           |

|        | Reserved   |          |           |        |        |        |            |          |          |           |

| 0x17   |            |          |           |        |        |        |            |          |          |           |

| 0x18   |            | 7:0      | MINUT     | E[1:0] |        |        | SECO       | ND[5:0]  |          |           |

| 0x19   | CLOCK      | 15:8     |           | HOU    | R[3:0] |        |            | MINUT    | E[5:2]   |           |

| 0x1A   | GEOGIA     | 23:16    | MONT      | H[1:0] |        |        | DAY[4:0]   |          |          | HOUR[4:4] |

| 0x1B   |            | 31:24    |           |        | YEAR   | R[5:0] |            |          | MON      | TH[3:2]   |

| 0x1C   |            |          |           |        |        |        |            |          |          |           |

|        | Reserved   |          |           |        |        |        |            |          |          |           |

| 0x1F   |            |          |           |        |        |        |            |          |          |           |

| 0x20   |            | 7:0      | MINUT     |        |        |        | SECO       | ND[5:0]  |          |           |

| 0x21   | ALARM      | 15:8     |           | HOU    | R[3:0] |        |            | MINUT    | E[5:2]   |           |

| 0x22   |            | 23:16    | MONT      | H[1:0] |        |        | DAY[4:0]   |          |          | HOUR[4:4] |

| 0x23   |            | 31:24    |           |        | YEAF   | R[5:0] | M          |          |          | FH[3:2]   |

| 0x24   | MASK       | 7:0      |           |        |        |        |            |          | SEL[2:0] |           |

## 24.12 Register Description - CLOCK

This Register Description section is valid if the RTC is in Clock/Calendar mode (CTRLA.MODE=2).

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

#### 24.12.10 Alarm Value in Clock/Calendar mode (CTRLA.MODE=2)

The 32-bit value of ALARM is continuously compared with the 32-bit CLOCK value, based on the masking set by MASK.SEL. When a match occurs, the Alarm n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.ALARM) is set on the next counter cycle, and the counter is cleared if CTRLA.MATCHCLR is '1'.

Name: ALARM Offset: 0x20 Reset: 0x0000000 Property: PAC Write-Protection, Write-Synchronized

| Bit    | 31   | 30      | 29     | 28     | 27          | 26       | 25  | 24  |

|--------|------|---------|--------|--------|-------------|----------|-----|-----|

|        |      |         | YEAF   | R[5:0] |             | MON      |     |     |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W      | R/W | R/W |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0        | 0   | 0   |

|        |      |         |        |        |             |          |     |     |

| Bit    | 23   | 22      | 21     | 20     | 19          | 18       | 17  | 16  |

|        | MON  | FH[1:0] |        |        | DAY[4:0]    | DAY[4:0] |     |     |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W      | R/W | R/W |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0        | 0   | 0   |

|        |      |         |        |        |             |          |     |     |

| Bit    | 15   | 14      | 13     | 12     | 11          | 10       | 9   | 8   |

|        |      | HOU     | R[3:0] |        | MINUTE[5:2] |          |     |     |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W      | R/W | R/W |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0        | 0   | 0   |

|        |      |         |        |        |             |          |     |     |

| Bit    | 7    | 6       | 5      | 4      | 3           | 2        | 1   | 0   |

|        | MINU | TE[1:0] |        |        | SECO        | ND[5:0]  |     |     |

| Access | R/W  | R/W     | R/W    | R/W    | R/W         | R/W      | R/W | R/W |

| Reset  | 0    | 0       | 0      | 0      | 0           | 0        | 0   | 0   |

#### Bits 31:26 - YEAR[5:0]: Year

The alarm year. Years are only matched if MASK.SEL is 6

#### Bits 25:22 - MONTH[3:0]: Month

The alarm month. Months are matched only if MASK.SEL is greater than 4.

#### Bits 21:17 – DAY[4:0]: Day

The alarm day. Days are matched only if MASK.SEL is greater than 3.

#### Bits 16:12 - HOUR[4:0]: Hour

The alarm hour. Hours are matched only if MASK.SEL is greater than 2.

#### Bits 11:6 - MINUTE[5:0]: Minute

The alarm minute. Minutes are matched only if MASK.SEL is greater than 1.

#### Bits 5:0 – SECOND[5:0]: Second

The alarm second. Seconds are matched only if MASK.SEL is greater than 0.

If CRC calculation is needed, the CRC engine must be configured before it is enabled, as outlined by the following steps:

- The CRC input source must selected by writing the CRC Input Source bit group in the CRC Control register (CRCCTRL.CRCSRC)

- The type of CRC calculation must be selected by writing the CRC Polynomial Type bit group in the CRC Control register (CRCCTRL.CRCPOLY)

- If I/O is selected as input source, the beat size must be selected by writing the CRC Beat Size bit group in the CRC Control register (CRCCTRL.CRCBEATSIZE)

#### **Related Links**

BASEADDR CHCTRLA CHCTRLB CRCCHKSUM CRCCTRL CTRL WRBADDR BTCTRL BTCNT DSTADDR SRCADDR

#### 25.6.2.2 Enabling, Disabling, and Resetting

The DMAC is enabled by writing the DMA Enable bit in the Control register (CTRL.DMAENABLE) to '1'. The DMAC is disabled by writing a '0' to CTRL.DMAENABLE.

A DMA channel is enabled by writing the Enable bit in the Channel Control A register (CHCTRLA.ENABLE) to '1', after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). A DMA channel is disabled by writing a '0' to CHCTRLA.ENABLE.

The CRC is enabled by writing a '1' to the CRC Enable bit in the Control register (CTRL.CRCENABLE). The CRC is disabled by writing a '0' to CTRL.CRCENABLE.

The DMAC is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST) while the DMAC and CRC are disabled. All registers in the DMAC except DBGCTRL will be reset to their initial state.

A DMA channel is reset by writing a '1' to the Software Reset bit in the Channel Control A register (CHCTRLA.SWRST), after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). The channel registers will be reset to their initial state. The corresponding DMA channel must be disabled in order for the reset to take effect.

#### 25.6.2.3 Transfer Descriptors

Together with the channel configurations the transfer descriptors decides how a block transfer should be executed. Before a DMA channel is enabled (CHCTRLA.ENABLE is written to one), and receives a transfer trigger, its first transfer descriptor has to be initialized and valid (BTCTRL.VALID). The first transfer descriptor describes the first block transfer of a transaction.

All transfer descriptors must reside in SRAM. The addresses stored in the Descriptor Memory Section Base Address (BASEADDR) and Write-Back Memory Section Base Address (WRBADDR) registers tell the DMAC where to find the descriptor memory section and the write-back memory section.

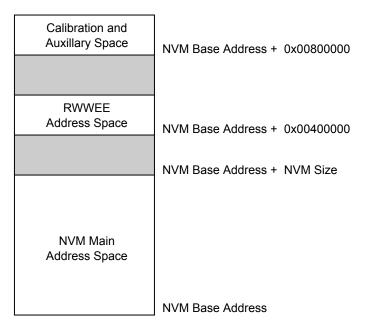

#### Figure 27-3. NVM Memory Organization

The lower rows in the NVM main address space can be allocated as a boot loader section by using the BOOTPROT fuses, and the upper rows can be allocated to EEPROM, as shown in the figure below.

The boot loader section is protected by the lock bit(s) corresponding to this address space and by the BOOTPROT[2:0] fuse. The EEPROM rows can be written regardless of the region lock status.

The number of rows protected by BOOTPROT is given in Boot Loader Size, the number of rows allocated to the EEPROM are given in EEPROM Size.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | The PMUXn registers of the selected pins will not be updated. |

| 1     | The PMUXn registers of the selected pins will be updated.     |

#### Bits 27:24 – PMUX[3:0]: Peripheral Multiplexing

These bits determine the new value written to the Peripheral Multiplexing register (PMUXn) for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPMUX bit is set.

These bits will always read as zero.

#### Bit 22 – DRVSTR: Output Driver Strength Selection

This bit determines the new value written to PINCFGy.DRVSTR for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 18 – PULLEN: Pull Enable

This bit determines the new value written to PINCFGy.PULLEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 17 – INEN: Input Enable

This bit determines the new value written to PINCFGy.INEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 16 – PMUXEN: Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bits 15:0 – PINMASK[15:0]: Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

#### 28.9.12 Event Input Control

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

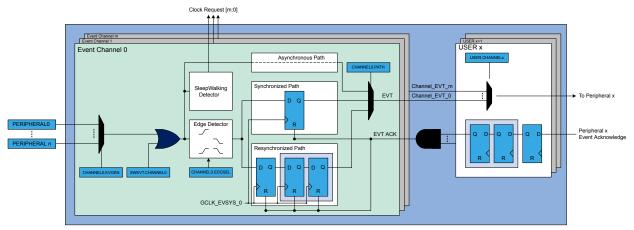

## 29. EVSYS – Event System

#### 29.1 Overview

The Event System (EVSYS) allows autonomous, low-latency and configurable communication between peripherals.

Several peripherals can be configured to generate and/or respond to signals known as events. The exact condition to generate an event, or the action taken upon receiving an event, is specific to each peripheral. Peripherals that respond to events are called event users. Peripherals that generate events are called event generators. A peripheral can have one or more event generators and can have one or more event users.

Communication is made without CPU intervention and without consuming system resources such as bus or RAM bandwidth. This reduces the load on the CPU and other system resources, compared to a traditional interrupt-based system.

## 29.2 Features

- 12 configurable event channels, where each channel can:

- Be connected to any event generator.

- Provide a pure asynchronous, resynchronized or synchronous path

- 87 event generators.

- 47 event users.

- Configurable edge detector.

- Peripherals can be event generators, event users, or both.

- SleepWalking and interrupt for operation in sleep modes.

- Software event generation.

- Each event user can choose which channel to respond to.

## 29.3 Block Diagram

#### Figure 29-1. Event System Block Diagram

# Name: CTRLB Offset: 0x04 Reset: 0x00000000

#### Property: PAC Write-Protection, Enable-Protected, Write-Synchronized

| Bit    | 31 | 30     | 29    | 28 | 27 | 26  | 25          | 24      |

|--------|----|--------|-------|----|----|-----|-------------|---------|

|        |    |        |       |    |    |     | LINC        | ID[1:0] |

| Access |    |        |       |    |    |     | R/W         | R/W     |

| Reset  |    |        |       |    |    |     | 0           | 0       |

|        |    |        |       |    |    |     |             |         |

| Bit    | 23 | 22     | 21    | 20 | 19 | 18  | 17          | 16      |

|        |    |        |       |    |    |     | RXEN        | TXEN    |

| Access |    |        |       |    | -  |     | R/W         | R/W     |

| Reset  |    |        |       |    |    |     | 0           | 0       |

|        |    |        |       |    |    |     |             |         |

| Bit    | 15 | 14     | 13    | 12 | 11 | 10  | 9           | 8       |

|        |    |        | PMODE |    |    | ENC | SFDE        | COLDEN  |

| Access |    |        | R/W   |    |    | R/W | R/W         | R/W     |

| Reset  |    |        | 0     |    |    | 0   | 0           | 0       |

|        |    |        |       |    |    |     |             |         |

| Bit    | 7  | 6      | 5     | 4  | 3  | 2   | 1           | 0       |

|        |    | SBMODE |       |    |    |     | CHSIZE[2:0] |         |

| Access |    | R/W    |       |    |    | R/W | R/W         | R/W     |

| Reset  |    | 0      |       |    |    | 0   | 0           | 0       |

|        |    |        |       |    |    |     |             |         |

#### Bits 25:24 – LINCMD[1:0]: LIN Command

These bits define the LIN header transmission control. This field is only valid in LIN master mode (CTRLA.FORM= LIN Master).

These are strobe bits and will always read back as zero.

These bits are not enable-protected.

| Value | Description                                                                                        |

|-------|----------------------------------------------------------------------------------------------------|

| 0x0   | Normal USART transmission.                                                                         |

| 0x1   | Break field is transmitted when DATA is written.                                                   |

| 0x2   | Break, sync and identifier are automatically transmitted when DATA is written with the identifier. |

| 0x3   | Reserved                                                                                           |

#### Bit 17 – RXEN: Receiver Enable

Writing '0' to this bit will disable the USART receiver. Disabling the receiver will flush the receive buffer and clear the FERR, PERR and BUFOVF bits in the STATUS register.

Writing '1' to CTRLB.RXEN when the USART is disabled will set CTRLB.RXEN immediately. When the USART is enabled, CTRLB.RXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled, CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the USART is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

For RS485 mode, the guard time is programmable from 0-7 bit times and defines the time that the transmit enable pin (TE) remains high after the last stop bit is transmitted and there is no remaining data to be transmitted.

#### 31.8.4 Baud

Name:BAUDOffset:0x0C [ID-00000fa7]Reset:0x0000Property:Enable-Protected, PAC Write-Protection

| Bit    | 15  | 14         | 13  | 12   | 11     | 10  | 9   | 8   |  |  |  |  |  |  |

|--------|-----|------------|-----|------|--------|-----|-----|-----|--|--|--|--|--|--|

|        |     | BAUD[15:8] |     |      |        |     |     |     |  |  |  |  |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |  |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |  |  |  |

|        |     |            |     |      |        |     |     |     |  |  |  |  |  |  |

| Bit    | 7   | 6          | 5   | 4    | 3      | 2   | 1   | 0   |  |  |  |  |  |  |

|        |     |            |     | BAUI | D[7:0] |     |     |     |  |  |  |  |  |  |

| Access | R/W | R/W        | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |  |  |  |

| Reset  | 0   | 0          | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |  |  |  |

#### Bits 15:0 – BAUD[15:0]: Baud Value

Arithmetic Baud Rate Generation (CTRLA.SAMPR[0]=0):

These bits control the clock generation, as described in the SERCOM Baud Rate section.

If Fractional Baud Rate Generation (CTRLA.SAMPR[0]=1) bit positions 15 to 13 are replaced by FP[2:0] Fractional Part:

#### • Bits 15:13 - FP[2:0]: Fractional Part

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

#### • Bits 12:0 - BAUD[21:0]: Baud Value

These bits control the clock generation, as described in the SERCOM Clock Generation – Baud-Rate Generator section.

#### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

#### 31.8.5 Receive Pulse Length Register

Name:RXPLOffset:0x0E [ID-00000fa7]Reset:0x00Property:PAC Write-Protection

| Bit    | 31 | 30 | 29 | 28 | 27 | 26        | 25   | 24  |

|--------|----|----|----|----|----|-----------|------|-----|

|        |    |    |    |    |    |           | TEFL | EFF |

| Access |    |    |    |    |    |           | R    | R   |

| Reset  |    |    |    |    |    |           | 0    | 0   |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18        | 17   | 16  |

| 2.0    |    |    |    |    |    | EFP[4:0]  |      |     |

| Access |    |    |    | R  | R  | R         | R    | R   |

| Reset  |    |    |    | 0  | 0  | 0         | 0    | 0   |

|        |    |    |    |    |    |           |      |     |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10        | 9    | 8   |

|        |    |    |    |    |    | EFGI[4:0] |      |     |

| Access |    |    |    | R  | R  | R         | R    | R   |

| Reset  |    |    |    | 0  | 0  | 0         | 0    | 0   |

|        |    |    |    |    |    |           |      |     |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2         | 1    | 0   |

|        |    |    |    |    |    | EFFI[4:0] |      |     |

| Access |    |    |    | R  | R  | R         | R    | R   |

| Reset  |    |    |    | 0  | 0  | 0         | 0    | 0   |

#### Bit 25 – TEFL: Tx Event FIFO Element Lost

This bit is a copy of interrupt flag IR.TEFL. When IR.TEFL is reset, this bit is also reset.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | No Tx Event FIFO element lost.                                                          |

| 1     | Tx Event FIFO element lost, also set after write attempt to Tx Event FIFO of size zero. |

#### Bit 24 – EFF: Event FIFO Full

| Value | Description             |

|-------|-------------------------|

| 0     | Tx Event FIFO not full. |

| 1     | Tx Event FIFO full.     |

#### Bits 20:16 – EFP[4:0]: Event FIFO Put Index

Tx Event FIFO write index pointer, range 0 to 31.

#### Bits 12:8 – EFGI[4:0]: Event FIFO Get Index

Tx Event FIFO read index pointer, range 0 to 31.

#### Bits 4:0 – EFFI[4:0]: Event FIFO Fill Level

Number of elements stored in Tx Event FIFO, range 0 to 32.

#### 34.8.47 Tx Event FIFO Acknowledge

Name:

TXEFA

Offset:

0xF8 [ID-0000a4bb]

Reset:

0x0000000

Property:

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

#### Bit 11 – DFS: Non-Recoverable Debug Fault State Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after an Debug Fault State occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Debug Fault State interrupt flag.

#### Bit 10 – UFS: Non-Recoverable Update Fault

This flag is set when the RAMP index changes and the Lock Update bit is set (CTRLBSET.LUPD).

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Non-Recoverable Update Fault interrupt flag.

#### Bit 3 – ERR: Error Interrupt Flag

This flag is set if a new capture occurs on a channel when the corresponding Match or Capture Channel x interrupt flag is one. In which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the error interrupt flag.

#### Bit 2 – CNT: Counter Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a counter event occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the CNT interrupt flag.

#### Bit 1 – TRG: Retrigger Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a counter retrigger occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the re-trigger interrupt flag.

#### Bit 0 – OVF: Overflow Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after an overflow condition occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

#### 36.8.13 Status

Name:

STATUS

Offset:

0x30 [ID-00002e48]

Reset:

0x00000001

Property:

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result<br>Precision | Number of<br>Automatic<br>Right<br>Shifts | Division<br>Factor | AVGCTRL.ADJRES | Total<br>Number<br>of Right<br>Shifts | Final<br>Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|--------------------|----------------|---------------------------------------|------------------------------|---------------------------------|

| 64                                  | 0x6                   | 18                                  | 2                                         | 16                 | 0x4            | 6                                     | 12 bits                      | 4                               |

| 128                                 | 0x7                   | 19                                  | 3                                         | 16                 | 0x4            | 7                                     | 12 bits                      | 8                               |

| 256                                 | 0x8                   | 20                                  | 4                                         | 16                 | 0x4            | 8                                     | 12 bits                      | 16                              |

| 512                                 | 0x9                   | 21                                  | 5                                         | 16                 | 0x4            | 9                                     | 12 bits                      | 32                              |

| 1024                                | 0xA                   | 22                                  | 6                                         | 16                 | 0x4            | 10                                    | 12 bits                      | 64                              |

| Reserved                            | 0xB –0xF              |                                     |                                           |                    | 0x0            |                                       | 12 bits                      | 0                               |

#### 38.6.2.11 Oversampling and Decimation

By using oversampling and decimation, the ADC resolution can be increased from 12 bits up to 16 bits, for the cost of reduced effective sampling rate.

To increase the resolution by n bits, 4<sup>n</sup> samples must be accumulated. The result must then be rightshifted by n bits. This right-shift is a combination of the automatic right-shift and the value written to AVGCTRL.ADJRES. To obtain the correct resolution, the ADJRES must be configured as described in the table below. This method will result in n bit extra LSB resolution.

| Result<br>Resolution | Number of<br>Samples to<br>Average | AVGCTRL.SAMPLENUM[3:0] | Number of<br>Automatic<br>Right Shifts | AVGCTRL.ADJRES[2:0] |

|----------------------|------------------------------------|------------------------|----------------------------------------|---------------------|

| 13 bits              | 4 <sup>1</sup> = 4                 | 0x2                    | 0                                      | 0x1                 |

| 14 bits              | 4 <sup>2</sup> = 16                | 0x4                    | 0                                      | 0x2                 |

| 15 bits              | 4 <sup>3</sup> = 64                | 0x6                    | 2                                      | 0x1                 |

| 16 bits              | 4 <sup>4</sup> = 256               | 0x8                    | 4                                      | 0x0                 |

Table 38-3. Configuration Required for Oversampling and Decimation

#### 38.6.2.12 Automatic Sequences

The ADC has the ability to automatically sequence a series of conversions. This means that each time the ADC receives a start-of-conversion request, it can perform multiple conversions automatically. All of the 32 positive inputs can be included in a sequence by writing to corresponding bits in the Sequence Control register (SEQCTRL). The order of the conversion in a sequence is the lower positive MUX selection to upper positive MUX (AIN0, AIN1, AIN2 ...). In differential mode, the negative inputs selected by MUXNEG field, will be used for the entire sequence.

When a sequence starts, the Sequence Busy status bit in Sequence Status register (SEQSTATUS.SEQBUSY) will be set. When the sequence is complete, the Sequence Busy status bit will be cleared.

Each time a conversion is completed, the Sequence State bit in Sequence Status register (SEQSTATUS.SEQSTATE) will store the input number from which the conversion is done. The result will be stored in the RESULT register, and the Result Ready Interrupt Flag (INTFLAG.RESRDY) is set.

If additional inputs must be scanned, the ADC will automatically start a new conversion on the next input present in the sequence list.

Note that if SEQCTRL register has no bits set to '1', the conversion is done with the selected MUXPOS input.

| Value  | Name | Description     |

|--------|------|-----------------|

| 0x18   | GND  | Internal ground |

| 0x19 - | -    | Reserved        |

| 0x1F   |      |                 |

#### Bits 4:0 – MUXPOS[4:0]: Positive MUX Input Selection

These bits define the MUX selection for the positive ADC input. If the internal bandgap voltage input channel is selected, then the Sampling Time Length bit group in the Sampling Control register must be written with a corresponding value.

| Value | Name    | Description     |

|-------|---------|-----------------|

| 0x00  | AIN0    | ADC AIN0 pin    |

| 0x01  | AIN1    | ADC AIN1 pin    |

| 0x02  | AIN2    | ADC AIN2 pin    |

| 0x03  | AIN3    | ADC AIN3 pin    |

| 0x04  | AIN4    | ADC AIN4 pin    |

| 0x05  | AIN5    | ADC AIN5 pin    |

| 0x06  | AIN6    | ADC AIN6 pin    |

| 0x07  | AIN7    | ADC AIN7 pin    |

| 0x08  | AIN8    | ADC AIN8 pin    |

| 0x09  | AIN9    | ADC AIN9 pin    |

| 0x0A  | AIN10   | ADC AIN10 pin   |

| 0x0B  | AIN11   | ADC AIN11 pin   |

| 0xC - | -       | Reserved        |

| 0x17  |         |                 |

| 0x18  | -       | Reserved        |

| 0x19  | BANDGAP | Bandgap Voltage |

| 0x1C  | DAC     | DAC Output      |

| 0x1E  | -       | Reserved        |

| 0x1F  | -       | Reserved        |

#### 38.8.10 Control C

Name:CTRLCOffset:0x0A [ID-0000120e]Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

When executing an operation that requires synchronization, the corresponding synchronization bit is set in Synchronization Busy register (SYNCBUSY) and cleared when synchronization is complete.

If an operation that require synchronization is executed while its busy bit is on, the operation is discarded and a bus error is generated.

The following bits need synchronization when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

Write-synchronization is denoted by the Write-Synchronized property in the register description.

The following registers need synchronization when written:

- Input Control register (INPUTCTRL)

- Reference Control register (REFCTRL)

- Control C register (CTRLC)

- Window Monitor Lower Threshold register (WINLT)

- Window Monitor Upper Threshold register (WINUT)

- Offset correction register (OFFSETCORR)

- Gain correction register (GAINCORR)

- Shift correction register (SHIFTCORR)

- Software Trigger register (SWTRIG)

- Analog Control Register (ANACTRL)

Write-synchronization is denoted by the Write-Synchronized property in the register description.

## 40.7 Register Summary

| Offset | Name      | Bit Pos. |        |           |             |           |           |         |             |         |

|--------|-----------|----------|--------|-----------|-------------|-----------|-----------|---------|-------------|---------|

| 0x00   | CTRLA     | 7:0      |        |           |             |           |           |         | ENABLE      | SWRST   |

| 0x01   | CTRLB     | 7:0      |        |           |             |           | STARTx    | STARTx  | STARTx      | STARTx  |

| 0x02   | EVICTO    | 7:0      |        |           | WINEOx      | WINEOx    | COMPEOx   | COMPEOx | COMPEOx     | COMPEOx |

| 0x03   | EVCTRL    | 15:8     | INVEIx | INVEIx    | INVEIx      | INVEIx    | COMPEIx   | COMPEIx | COMPEIx     | COMPEIx |

| 0x04   | INTENCLR  | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x05   | INTENSET  | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x06   | INTFLAG   | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x07   | STATUSA   | 7:0      | WSTA   | TE1[1:0]  | WSTAT       | E0[1:0]   | STATEx    | STATEx  | STATEx      | STATEx  |

| 0x08   | STATUSB   | 7:0      |        |           |             |           | READYx    | READYx  | READYx      | READYx  |

| 0x09   | DBGCTRL   | 7:0      |        |           |             |           |           |         |             | DBGRUN  |

| 0x0A   | WINCTRL   | 7:0      |        | WINTS     | EL1[1:0]    | WEN1      |           | WINTS   | EL0[1:0]    | WEN0    |

| 0x0B   | Reserved  |          |        |           |             |           |           |         |             |         |

| 0x0C   | SCALERn0  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x0D   | SCALERn1  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x0E   | SCALERn2  | 7:0      |        |           | VALUE[5:0]  |           |           |         |             |         |

| 0x0F   | SCALERn3  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x10   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x11   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x12   | COMPCTRL0 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x13   |           | 31:24    |        |           | OUT         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x14   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x15   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x16   | COMPCTRL1 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x17   |           | 31:24    |        |           | τυο         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x18   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x19   | COMPCTRL2 | 15:8     | SWAP   |           | MUXPOS[2:0] | -         |           |         | MUXNEG[2:0] |         |

| 0x1A   | COWPCTRL2 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x1B   |           | 31:24    |        |           | τυο         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x1C   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x1D   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x1E   | COMPCTRL3 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x1F   |           | 31:24    |        |           | τυο         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x20   |           | 7:0      |        | COMPCTRLx | COMPCTRLx   | COMPCTRLx | COMPCTRLx | WINCTRL | ENABLE      | SWRST   |

| 0x21   | EVNOPLIEV | 15:8     |        |           |             |           |           |         |             |         |

| 0x22   | SYNCBUSY  | 23:16    |        |           |             |           |           |         |             |         |

| 0x23   |           | 31:24    |        |           |             |           |           |         |             |         |

## 40.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

#### 43.8.6 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

Name:INTENSETOffset:0x05 [ID-00001f13]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3   | 2      | 1       | 0      |

|--------|---|---|---|---|-----|--------|---------|--------|

|        |   |   |   |   | OVF | WINMON | OVERRUN | RESRDY |

| Access |   |   |   |   | R/W | R/W    | R/W     | R/W    |

| Reset  |   |   |   |   | 0   | 0      | 0       | 0      |

#### Bit 3 – OVF: Overflow Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Overflow Interrupt bit, which enables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### Bit 2 – WINMON: Window Monitor Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Window Monitor Interrupt bit, which enables the Window Monitor interrupt.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Window Monitor interrupt is disabled. |

| 1     | The Window Monitor interrupt is enabled.  |

#### **Bit 1 – OVERRUN: Overrun Interrupt Enable**

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Overrun Interrupt Enable bit, which enables the corresponding interrupt request.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Overrun interrupt is disabled. |

| 1     | The Overrun interrupt is enabled.  |

#### Bit 0 – RESRDY: Result Ready Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will set the Result Ready Interrupt bit, which enables the Result Ready interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Result Ready interrupt is disabled. |

| 1     | The Result Ready interrupt is enabled.  |

#### 43.8.7 Interrupt Flag Status and Clear

| Mode    | Conditions                                                    | Та    | Vcc  | Тур.         | Max.          | Units                 |  |

|---------|---------------------------------------------------------------|-------|------|--------------|---------------|-----------------------|--|

|         |                                                               | 105°C | 5.0V | 6.3          | 7.1           |                       |  |

|         | CPU running a CoreMark algorithm                              | 25°C  | 3.0V | 5.2          | 5.7           | mA                    |  |

|         |                                                               | 105°C | 3.0V | 5.5          | 6.6           |                       |  |

|         | CPU running a CoreMark algorithm.<br>with GCLKIN as reference | 25°C  | 5.0V | 115*Freq+167 | 126*Freq+167  | $\mu A$ (with freq in |  |

|         |                                                               | 105°C | 5.0V | 118*Freq+383 | 110*Freq+1583 | MHz)                  |  |

| IDLE    |                                                               | 25°C  | 5.0V | 1.2          | 1.7           | mA                    |  |

|         |                                                               | 105°C | 5.0V | 1.5          | 2.6           |                       |  |

| STANDBY | XOSC32K running RTC running at 1kHz                           | 25°C  | 5.0V | 15.9         | 37.0          | μΑ                    |  |

|         |                                                               | 105°C | 5.0V | 187.0        | 602.0         |                       |  |

|         | XOSC32K and RTC stopped                                       | 25°C  | 5.0V | 14.6         | 35.0          |                       |  |

|         |                                                               | 105°C | 5.0V | 185.0        | 600.0         |                       |  |

1. These are based on characterization.

## 47.4 Analog Characteristics

## 47.4.1 Power On Reset (POR) Characteristics Table 47-3. POR Characteristics

| Symbol            | Parameters                               | Min  | Тур  | Мах  | Unit |

|-------------------|------------------------------------------|------|------|------|------|

| V <sub>POT+</sub> | Voltage threshold Level on VDDIN rising  | -    | 2.55 | -    | V    |

| V <sub>POT-</sub> | Voltage threshold Level on VDDIN falling | 1.77 | 1.92 | 2.04 |      |

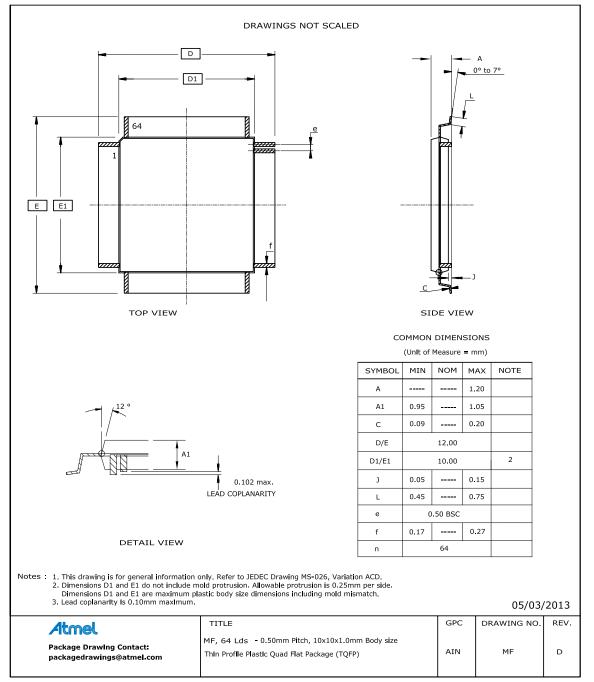

#### Table 48-4. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | e3     |

#### 48.2.2 64 pin TQFP

#### Table 48-5. Device and Package Maximum Weight

300

mg