Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g16a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 13.5.3 Clocks

The DSU bus clocks (CLK\_DSU\_APB and CLK\_DSU\_AHB) can be enabled and disabled by the Main Clock Controller.

#### **Related Links**

PM – Power Manager MCLK – Main Clock Peripheral Clock Masking

#### 13.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to DMAC – Direct Memory Access Controller for details.

#### 13.5.5 Interrupts

Not applicable.

#### 13.5.6 Events

Not applicable.

#### 13.5.7 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except for the following:

- Debug Communication Channel 0 register (DCC0)

- Debug Communication Channel 1 register (DCC1)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

#### 13.5.8 Analog Connections

Not applicable.

#### 13.6 Debug Operation

#### 13.6.1 Principle of Operation

The DSU provides basic services to allow on-chip debug using the ARM Debug Access Port and the ARM processor debug resources:

- CPU reset extension

- Debugger probe detection

For more details on the ARM debug components, refer to the ARM Debug Interface v5 Architecture Specification.

#### Bit 2 – TC5: TC5 APBd Mask Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBD clock for the TC5 is stopped. |

| 1     | The APBD clock for the TC5 is enabled. |

#### Bit 1 – SERCOM7: SERCOM7 APBD Mask Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBD clock for the SERCOM7 is stopped. |

| 1     | The APBD clock for the SERCOM7 is enabled. |

#### Bit 0 – SERCOM6: SERCOM6 APBD Mask Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBD clock for the SERCOM6 is stopped. |

| 1     | The APBD clock for the SERCOM6 is enabled. |

#### Note:

- 1. Start-up time is given by STARTUP + three OSC32K cycles.

- 2. The given time assumes an XTAL frequency of 32.768kHz.

#### Bit 7 – ONDEMAND: On Demand Control

This bit controls how the OSC32K behaves when a peripheral clock request is detected. For details, refer to OSC32K Sleep Behavior.

#### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the OSC32K behaves during standby sleep mode. For details, refer to OSC32K Sleep Behavior.

#### Bit 3 – EN1K: 1KHz Output Enable

| Value | Description                  |

|-------|------------------------------|

| 0     | The 1KHz output is disabled. |

| 1     | The 1KHz output is enabled.  |

#### Bit 2 – EN32K: 32KHz Output Enable

| Value | Description                   |

|-------|-------------------------------|

| 0     | The 32KHz output is disabled. |

| 1     | The 32KHz output is enabled.  |

#### Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

#### 21.8.9 32KHz Ultra Low Power Internal Oscillator (OSCULP32K) Control

Name:OSCULP32KOffset:0x1C [ID-00001010]Reset:0x0000XX06Property:PAC Write-Protection

#### 22.5.5 Interrupts

The interrupt request lines are connected to the interrupt controller. Using the SUPC interrupts requires the interrupt controller to be configured first.

#### **Related Links**

Nested Vector Interrupt Controller

#### 22.5.6 Events

Not applicable.

#### 22.5.7 Debug Operation

When the CPU is halted in debug mode, the SUPC continues normal operation. If the SUPC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

If debugger cold-plugging is detected by the system, BODVDD and BODCORE resets will be masked. The BOD resets keep running under hot-plugging. This allows to correct a BODVDD user level too high for the available supply.

#### 22.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

Note: Not all registers with write-access can be write-protected.

PAC Write-Protection is not available for the following registers:

• Interrupt Flag Status and Clear register (INTFLAG)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

#### **Related Links**

PAC - Peripheral Access Controller

## 22.5.9 Analog Connections

Not applicable.

#### 22.6 Functional Description

#### 22.6.1 Voltage Regulator System Operation

#### 22.6.1.1 Enabling, Disabling, and Resetting

The LDO main voltage regulator is enabled after any Reset. The main voltage regulator (MAINVREG) can be disabled by writing the Enable bit in the VREG register (VREG.ENABLE) to zero. The main voltage regulator output supply level is automatically defined by the sleep mode selected in the Power Manager module.

#### **Related Links**

PM – Power Manager

#### 22.6.1.2 Initialization

After a Reset, the LDO voltage regulator supplying VDDCORE is enabled.

#### 22.6.1.3 Sleep Mode Operation

In standby mode, the low power voltage regulator (LPVREG) is used to supply VDDCORE.

# SAM C20/C21

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|--------|------|------|------|------|------|------|------|------|

|        | OVF  |      |      |      |      |      | CMPn | CMPn |

| Access | R/W  |      |      |      |      |      | R/W  | R/W  |

| Reset  | 0    |      |      |      |      |      | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | PERn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|        | R/W  | R/V  |

#### Bit 15 – OVF: Overflow Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### Bits 9:8 – CMPn: Compare n Interrupt Enable [n = 1..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Compare n Interrupt Enable bit, which and enables the Compare n interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The Compare n interrupt is disabled. |

| 1     | The Compare n interrupt is enabled.  |

#### Bits 7:0 – PERn: Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Periodic Interval n Interrupt Enable bit, which enables the Periodic Interval n interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

#### 24.10.5 Interrupt Flag Status and Clear in COUNT16 mode (CTRLA.MODE=1)

| Name:            | INTFLAG |

|------------------|---------|

| Offset:          | 0x0C    |

| Reset:           | 0x0000  |

| <b>Property:</b> | -       |

#### 27.8.10 Page Buffer Load Data 0

| Name:     | PBLDATA0   |

|-----------|------------|

| Offset:   | 0x28       |

| Reset:    | 0xFFFFFFFF |

| Property: | -          |

| Bit    | 31 | 30 | 29 | 28     | 27       | 26 | 25 | 24 |

|--------|----|----|----|--------|----------|----|----|----|

|        |    |    |    | PBLDAT | A[31:24] |    |    |    |

| Access | R  | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1  | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19       | 18 | 17 | 16 |

|        |    |    |    | PBLDAT | A[23:16] |    |    |    |

| Access | R  | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1  | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11       | 10 | 9  | 8  |

|        |    |    |    | PBLDA  | TA[15:8] |    |    |    |

| Access | R  | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1  | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

|        |    |    |    |        |          |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3        | 2  | 1  | 0  |

|        |    |    |    | PBLDA  | TA[7:0]  |    |    |    |

| Access | R  | R  | R  | R      | R        | R  | R  | R  |

| Reset  | 1  | 1  | 1  | 1      | 1        | 1  | 1  | 1  |

#### Bits 31:0 – PBLDATA[31:0]: Page Buffer Load Data

The PBLDATA register is a holding register for partial AHB writes to the same 64-bit page buffer section. Page buffer loads are performed on a 64-bit basis.

This is a read only register.

#### 27.8.11 Page Buffer Load Data 1

Name:PBLDATA1Offset:0x2CReset:0xFFFFFFFProperty: -

# SAM C20/C21

| Bit    | 31       | 30       | 29  | 28   | 27     | 26      | 25        | 24  |

|--------|----------|----------|-----|------|--------|---------|-----------|-----|

|        |          |          |     |      |        |         |           |     |

| Access |          |          |     |      |        |         |           |     |

| Reset  |          |          |     |      |        |         |           |     |

|        |          |          |     |      |        |         |           |     |

| Bit    | 23       | 22       | 21  | 20   | 19     | 18      | 17        | 16  |

|        |          |          |     |      |        |         |           |     |

| Access |          | •        | •   |      |        |         |           |     |

| Reset  |          |          |     |      |        |         |           |     |

|        |          |          |     |      |        |         |           |     |

| Bit    | 15       | 14       | 13  | 12   | 11     | 10      | 9         | 8   |

|        | ONDEMAND | RUNSTDBY |     |      | EDGS   | EL[1:0] | PATH[1:0] |     |

| Access | R/W      | R/W      |     |      | R/W    | R/W     | R/W       | R/W |

| Reset  | 0        | 0        |     |      | 0      | 0       | 0         | 0   |

|        |          |          |     |      |        |         |           |     |

| Bit    | 7        | 6        | 5   | 4    | 3      | 2       | 1         | 0   |

|        |          |          |     | EVGE | N[7:0] |         |           |     |

| Access | R/W      | R/W      | R/W | R/W  | R/W    | R/W     | R/W       | R/W |

| Reset  | 0        | 0        | 0   | 0    | 0      | 0       | 0         | 0   |

#### Bit 15 – ONDEMAND: Generic Clock On Demand

| Value | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock source is enabled. |

| 1     | Generic clock is requested on demand while an event is handled                                              |

#### Bit 14 – RUNSTDBY: Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                                       |

| 1     | The channel is not stopped in standby sleep mode and depends on the CHANNEL.ONDEMAND |

#### Bits 11:10 – EDGSEL[1:0]: Edge Detection Selection

These bits set the type of edge detection to be used on the channel.

These bits must be written to zero when using the asynchronous path.

| Value | Name          | Description                                                                        |

|-------|---------------|------------------------------------------------------------------------------------|

| 0x0   | NO_EVT_OUTPUT | No event output when using the resynchronized or synchronous path                  |

| 0x1   | RISING_EDGE   | Event detection only on the rising edge of the signal from the event generator     |

| 0x2   | FALLING_EDGE  | Event detection only on the falling edge of the signal from the event generator    |

| 0x3   | BOTH_EDGES    | Event detection on rising and falling edges of the signal from the event generator |

#### Bits 9:8 – PATH[1:0]: Path Selection

These bits are used to choose which path will be used by the selected channel.

The path choice can be limited by the channel source, see the table in USERm.

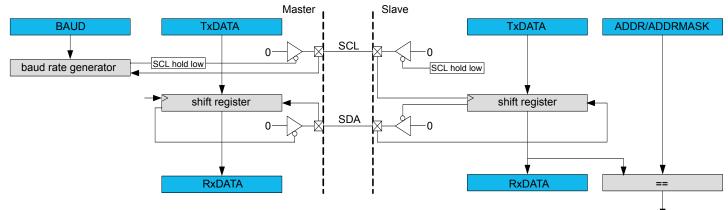

#### 33.3 Block Diagram

Figure 33-1. I<sup>2</sup>C Single-Master Single-Slave Interconnection

#### 33.4 Signal Description

| Signal Name | Туре        | Description                |

|-------------|-------------|----------------------------|

| PAD[0]      | Digital I/O | SDA                        |

| PAD[1]      | Digital I/O | SCL                        |

| PAD[2]      | Digital I/O | SDA_OUT (4-wire operation) |

| PAD[3]      | Digital I/O | SCL_OUT (4-wire operation) |

One signal can be mapped on several pins.

Not all the pins are I<sup>2</sup>C pins.

#### **Related Links**

I/O Multiplexing and Considerations 4-Wire Mode

#### 33.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 33.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

When the SERCOM is used in I<sup>2</sup>C mode, the SERCOM controls the direction and value of the I/O pins. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver or transmitter is disabled, these pins can be used for other purposes.

#### **Related Links**

PORT: IO Pin Controller

#### Bit 7 – CLKHOLD: Clock Hold

The slave Clock Hold bit (STATUS.CLKHOLD) is set when the slave is holding the SCL line low, stretching the I2C clock. Software should consider this bit a read-only status flag that is set when INTFLAG.DRDY or INTFLAG.AMATCH is set.

This bit is automatically cleared when the corresponding interrupt is also cleared.

#### Bit 6 – LOWTOUT: SCL Low Time-out

This bit is set if an SCL low time-out occurs.

This bit is cleared automatically if responding to a new start condition with ACK or NACK (write 3 to CTRLB.CMD) or when INTFLAG.AMATCH is cleared.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the status.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No SCL low time-out has occurred. |

| 1     | SCL low time-out has occurred.    |

#### Bit 4 – SR: Repeated Start

When INTFLAG.AMATCH is raised due to an address match, SR indicates a repeated start or start condition.

This flag is only valid while the INTFLAG.AMATCH flag is one.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Start condition on last address match          |

| 1     | Repeated start condition on last address match |

#### Bit 3 – DIR: Read / Write Direction

The Read/Write Direction (STATUS.DIR) bit stores the direction of the last address packet received from a master.

| Value | Description                            |

|-------|----------------------------------------|

| 0     | Master write operation is in progress. |

| 1     | Master read operation is in progress.  |

#### Bit 2 – RXNACK: Received Not Acknowledge

This bit indicates whether the last data packet sent was acknowledged or not.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Master responded with ACK.  |

| 1     | Master responded with NACK. |

#### Bit 1 – COLL: Transmit Collision

If set, the I2C slave was not able to transmit a high data or NACK bit, the I2C slave will immediately release the SDA and SCL lines and wait for the next packet addressed to it.

This flag is intended for the SMBus address resolution protocol (ARP). A detected collision in non-ARP situations indicates that there has been a protocol violation, and should be treated as a bus error.

Note that this status will not trigger any interrupt, and should be checked by software to verify that the data were sent correctly. This bit is cleared automatically if responding to an address match with an ACK or a NACK (writing 0x3 to CTRLB.CMD), or INTFLAG.AMATCH is cleared.

#### **Bit 9 – TC: Timestamp Completed**

| Value | Description                |

|-------|----------------------------|

| 0     | No transmission completed. |

| 1     | Transmission completed.    |

#### **Bit 8 – HPM: High Priority Message**

| Value | Description                        |  |  |

|-------|------------------------------------|--|--|

| 0     | No high priority message received. |  |  |

| 1     | High priority message received.    |  |  |

#### Bit 7 – RF1L: Rx FIFO 1 Message Lost

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | No Rx FIFO 1 message lost.                                                      |

| 1     | Rx FIFO 1 message lost. also set after write attempt to Rx FIFO 1 of size zero. |

#### Bit 6 – RF1F: Rx FIFO 1 Full

| Value | Description         |

|-------|---------------------|

| 0     | Rx FIFO 1 not full. |

| 1     | Rx FIFO 1 full.     |

#### Bit 5 – RF1W: Rx FIFO 1 Watermark Reached

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Rx FIFO 1 fill level below watermark.   |

| 1     | Rx FIFO 1 fill level reached watermark. |

#### Bit 4 – RF1N: Rx FIFO 1 New Message

| Value | Description                          |  |  |  |

|-------|--------------------------------------|--|--|--|

| 0     | No new message written to Rx FIFO 1. |  |  |  |

| 1     | New message written to Rx FIFO 1.    |  |  |  |

#### Bit 3 – RF0L: Rx FIFO 0 Message Lost

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | No Rx FIFO 0 message lost.                                                      |

| 1     | Rx FIFO 0 message lost. also set after write attempt to Rx FIFO 0 of size zero. |

#### Bit 2 – RF0F: Rx FIFO 0 Full

| Value | Description         |  |  |

|-------|---------------------|--|--|

| 0     | Rx FIFO 0 not full. |  |  |

| 1     | Rx FIFO 0 full.     |  |  |

#### Bit 1 – RF0W: Rx FIFO 0 Watermark Reached

| Value | Description                             |  |  |  |

|-------|-----------------------------------------|--|--|--|

| 0     | Rx FIFO 0 fill level below watermark.   |  |  |  |

| 1     | Rx FIFO 0 fill level reached watermark. |  |  |  |

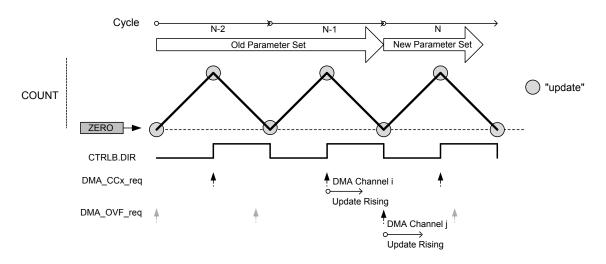

#### Figure 36-38. DMA Triggers in DSBOTH Operation Mode and Circular Buffer Enabled

#### 36.6.5.2 Interrupts

The TCC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Retrigger (TRG)

- Count (CNT) refer also to description of EVCTRL.CNTSEL.

- Capture Overflow Error (ERR)

- Non-Recoverable Update Fault (UFS)

- Debug Fault State (DFS)

- Recoverable Faults (FAULTn)

- Non-recoverable Faults (FAULTx)

- Compare Match or Capture Channels (MCx)

These interrupts are asynchronous wake-up sources. See Sleep Mode Entry and Exit Table in PM/Sleep Mode Controller section for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TCC is reset. See INTFLAG for details on how to clear interrupt flags. The TCC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller Sleep Mode Controller

#### 36.6.5.3 Events

The TCC can generate the following output events:

| Value | Description                         |  |  |  |

|-------|-------------------------------------|--|--|--|

| 0     | The Overflow interrupt is disabled. |  |  |  |

| 1     | The Overflow interrupt is enabled.  |  |  |  |

#### 36.8.12 Interrupt Flag Status and Clear

| Name:    | INTFLAG            |

|----------|--------------------|

| Offset:  | 0x2C [ID-00002e48] |

| Reset:   | 0x0000000          |

| Property | :-                 |

| Bit    | 23     | 22     | 21     | 20     | 19  | 18  | 17  | 16  |

|--------|--------|--------|--------|--------|-----|-----|-----|-----|

|        |        |        |        |        | MCx | MCx | MCx | MCx |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

|        |        |        |        |        |     |     |     |     |

| Bit    | 15     | 14     | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx | FAULTx | FAULTB | FAULTA | DFS | UFS |     |     |

| Access | R/W    | R/W    | R/W    | R/W    | R/W | R/W |     |     |

| Reset  | 0      | 0      | 0      | 0      | 0   | 0   |     |     |

|        |        |        |        |        |     |     |     |     |

| Bit    | 7      | 6      | 5      | 4      | 3   | 2   | 1   | 0   |

|        |        |        |        |        | ERR | CNT | TRG | OVF |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

#### Bits 19,18,17,16 – MCx: Match or Capture Channel x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a match with the compare condition or once CCx register contain a valid capture value.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In Capture operation, this flag is automatically cleared when CCx register is read.

#### Bits 15,14 – FAULTx: Non-Recoverable Fault x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Non-Recoverable Fault x occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Non-Recoverable Fault x interrupt flag.

#### Bit 13 – FAULTB: Recoverable Fault B Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

#### Bit 12 – FAULTA: Recoverable Fault A Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

© 2017 Microchip Technology Inc.

#### Analog-to-Digital Converter (ADC) Characteristics

#### 38.6.2.6 ADC Resolution

The ADC supports 8-bit, 10-bit or 12-bit resolution. Resolution can be changed by writing the Resolution bit group in the Control C register (CTRLC.RESSEL). By default, the ADC resolution is set to 12 bits. The resolution affects the propagation delay, see also Conversion Timing and Sampling Rate.

#### 38.6.2.7 Differential and Single-Ended Conversions

The ADC has two conversion options: differential and single-ended:

If the positive input is always positive, the single-ended conversion should be used in order to have full 12-bit resolution in the conversion.

If the positive input may go below the negative input, the differential mode should be used in order to get correct results.

The differential mode is enabled by setting DIFFMODE bit in the Control C register (CTRLC.DIFFMODE). Both conversion types could be run in single mode or in free-running mode. When the free-running mode is selected, an ADC input will continuously sample the input and performs a new conversion. The INTFLAG.RESRDY bit will be set at the end of each conversion.

#### 38.6.2.8 Conversion Timing and Sampling Rate

The following figure shows the ADC timing for one single conversion. A conversion starts after the software or event start are synchronized with the GCLK\_ADCx clock. The input channel is sampled in the first half CLK\_ADCx period.

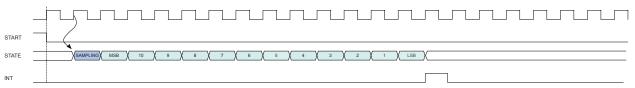

#### Figure 38-3. ADC Timing for One Conversion in 12-bit Resolution

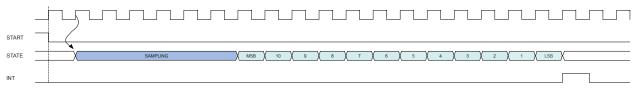

The sampling time can be increased by using the Sampling Time Length bit group in the Sampling Time Control register (SAMPCTRL.SAMPLEN). As example, the next figure is showing the timing conversion with sampling time increased to six CLK\_ADC cycles.

#### Figure 38-4. ADC Timing for One Conversion with Increased Sampling Time, 12-bit

The ADC provides also offset compensation, see the following figure. The offset compensation is enabled by the Offset Compensation bit in the Sampling Control register (SAMPCTRL.OFFCOMP).

Note: If offset compensation is used, the sampling time must be set to one cycle of CLK\_ADCx.

In free running mode, the sampling rate R<sub>S</sub> is calculated by

$R_{S} = f_{CLK\_ADC} / (n_{SAMPLING} + n_{OFFCOMP} + n_{DATA})$

Here,  $n_{SAMPLING}$  is the sampling duration in CLK\_ADC cycles,  $n_{OFFCOMP}$  is the offset compensation duration in clock cycles, and  $n_{DATA}$  is the bit resolution.  $f_{CLK\_ADC}$  is the ADC clock frequency from the internal prescaler:  $f_{CLK\_ADC} = f_{GCLK\_ADC} / 2^{(1 + CTRLB.PRESCALER)}$

- Select the interrupt source with COMPCTRLx.INTSEL.

- Select the positive and negative input sources with the COMPCTRLx.MUXPOS and COMPCTRLx.MUXNEG bits. See Selecting Comparator Inputs for more details.

- Select the filtering option with COMPCTRLx.FLEN.

- Select standby operation with Run in Standby bit (COMPCTRLx.RUNSTDBY).

The individual comparators are enabled by writing a '1' to the Enable bit in the Comparator x Control registers (COMPCTRLx.ENABLE). The individual comparators are disabled by writing a '0' to COMPCTRLx.ENABLE. Writing a '0' to CTRLA.ENABLE will also disable all the comparators, but will not clear their COMPCTRLx.ENABLE bits.

#### 40.6.2.4 Starting a Comparison

Each comparator channel can be in one of two different measurement modes, determined by the Single bit in the Comparator x Control register (COMPCTRLx.SINGLE):

- Continuous measurement

- Single-shot

After being enabled, a start-up delay is required before the result of the comparison is ready. This start-up time is measured automatically to account for environmental changes, such as temperature or voltage supply level, and is specified in *Electrical Characteristics*. During the start-up time, the COMP output is not available.

The comparator can be configured to generate interrupts when the output toggles, when the output changes from '0' to '1' (rising edge), when the output changes from '1' to '0' (falling edge) or at the end of the comparison. An end-of-comparison interrupt can be used with the single-shot mode to chain further events in the system, regardless of the state of the comparator outputs. The interrupt mode is set by the Interrupt Selection bit group in the Comparator Control register (COMPCTRLx.INTSEL). Events are generated using the comparator output state, regardless of whether the interrupt is enabled or not.

#### **Related Links**

Electrical Characteristics 85°C (SAM C20/C21 E/G/J)

#### **Continuous Measurement**

Continuous measurement is selected by writing COMPCTRLx.SINGLE to zero. In continuous mode, the comparator is continuously enabled and performing comparisons. This ensures that the result of the latest comparison is always available in the Current State bit in the Status A register (STATUSA.STATEx).

After the start-up time has passed, a comparison is done and STATUSA is updated. The Comparator x Ready bit in the Status B register (STATUSB.READYx) is set, and the appropriate peripheral events and interrupts are also generated. New comparisons are performed continuously until the COMPCTRLx.ENABLE bit is written to zero. The start-up time applies only to the first comparison.

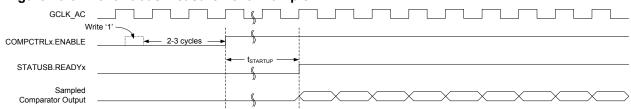

In continuous operation, edge detection of the comparator output for interrupts is done by comparing the current and previous sample. The sampling rate is the GCLK\_AC frequency. An example of continuous measurement is shown in the Figure 40-3.

#### Figure 40-3. Continuous Measurement Example

| Value   | Name | Description                      |

|---------|------|----------------------------------|

| 0x0     | OFF  | No filtering                     |

| 0x1     | MAJ3 | 3-bit majority function (2 of 3) |

| 0x2     | MAJ5 | 5-bit majority function (3 of 5) |

| 0x3-0x7 | N/A  | Reserved                         |

#### Bit 19 – HYSTEN: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn.SINGLE=0).

This bit is not synchronized.

| Value | Description             |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

#### Bits 17:16 – SPEED[1:0]: Speed Selection

This bit indicates the speed/propagation delay mode of comparator n. COMPCTRLn.SPEED can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | LOW  | Low speed   |

| 0x3   | HIGH | High speed  |

#### Bit 15 – SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

#### Bits 14:12 – MUXPOS[2:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value   | Name   | Description |

|---------|--------|-------------|

| 0x0     | PIN0   | I/O pin 0   |

| 0x1     | PIN1   | I/O pin 1   |

| 0x2     | PIN2   | I/O pin 2   |

| 0x3     | PIN3   | I/O pin 3   |

| 0x4     | VSCALE | VDD scaler  |

| 0x5–0x7 |        | Reserved    |

Name:CTRLAOffset:0x00 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection, Write-Synchronized

#### Bit 6 – RUNSTDBY: Run in Standby

This bit is not synchronized

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | The DAC output buffer is disabled in standby sleep mode.    |

| 1     | The DAC output buffer can be enabled in standby sleep mode. |

#### Bit 1 – ENABLE: Enable DAC Controller

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

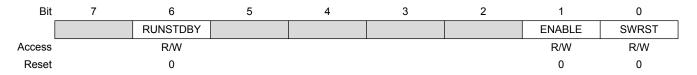

#### Bit 0 – SWRST: Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the DAC to their initial state, and the DAC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 41.8.2 Control B

Name:CTRLBOffset:0x01 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection, Enable-Protected

# 46. Electrical Characteristics 105°C (SAM C20/C21 E/G/J)

#### 46.1 Disclaimer

All typical values are measured at Ta = 25°C unless otherwise specified. All minimum and maximum values are valid across operating temperature and voltage unless otherwise specified.

This chapter contains only characteristics specific for the SAM C20/C21 E/G/J (Ta = 105°C). For all other values or missing characteristics, refer to the 85°C chapter.

### 46.2 General Operating Ratings

The device must operate within the ratings listed in the table below in order for all other electrical characteristics and typical characteristics of the device to be valid.

Table 46-1. General operating conditions

| Symbol         | Parameter            | Min. | Тур. | Max. | Units |

|----------------|----------------------|------|------|------|-------|

| T <sub>A</sub> | Temperature range    | -40  | 25   | 105  | °C    |

| TJ             | Junction temperature | -    | -    | 125  | °C    |

#### 46.3 Power Consumption

#### Table 46-2. Power Consumption<sup>(1)</sup>

| Mode   | Conditions                           | Та    | Vcc  | Тур.        | Max.        | Units         |  |

|--------|--------------------------------------|-------|------|-------------|-------------|---------------|--|

| ACTIVE | CPU running a While 1<br>algorithm   | 25°C  | 5.0V | 3.8         | 4.2         | mA            |  |

|        |                                      | 105°C | 5.0V | 4.0         | 4.5         |               |  |

|        | CPU running a While 1                | 25°C  | 3.0V | 3.7         | 4.1         | mA            |  |

|        | algorithm                            | 105°C | 3.0V | 4.0         | 4.5         |               |  |

|        | CPU running a While 1                | 25°C  | 5.0V | 71*Freq+160 | 78*Freq+162 | μA (with freq |  |

|        | algorithm. with GCLKIN as reference  | 105°C | 5.0V | 71*Freq+374 | 72*Freq+819 | in MHz)       |  |

|        | CPU running a Fibonacci<br>algorithm | 25°C  | 5.0V | 4.7         | 5.2         | mA            |  |

|        |                                      | 105°C | 5.0V | 5.0         | 5.5         |               |  |

|        | CPU running a Fibonacci<br>algorithm | 25°C  | 3.0V | 4.7         | 5.1         | mA            |  |

|        |                                      | 105°C | 3.0V | 5.0         | 5.5         |               |  |

|        | CPU running a Fibonacci              | 25°C  | 5.0V | 90*Freq+163 | 99*Freq+168 | μA (with freq |  |

|        | algorithm. with GCLKIN as reference  | 105°C | 5.0V | 90*Freq+379 | 92*Freq+820 | in MHz)       |  |

|        | CPU running a CoreMark               | 25°C  | 5.0V | 5.9         | 6.4         | mA            |  |

|        | algorithm                            | 105°C | 5.0V | 6.3         | 6.9         |               |  |

#### Table 47-20. Digital Clock Characteristics<sup>(1)</sup>

| Symbol               | Parameter              | Condition    | Тур    | Units |

|----------------------|------------------------|--------------|--------|-------|

| f <sub>CPXIN32</sub> | XIN32 clock frequency  | Digital mode | 32.768 | kHz   |

| DC <sub>XIN32</sub>  | XIN32 clock duty cycle | Digital mode | 50     | %     |

1. These are based on simulation. These values are not covered by test or characterization

The following table describes the characteristics for the oscillator when a crystal is connected between XIN32 and XOUT32.

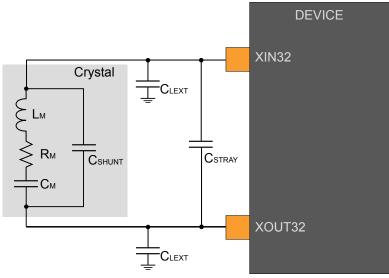

#### Figure 47-6. Oscillator Connection

The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of CL can be found in the crystal datasheet. The capacitance of the external capacitors (CLEXT) can then be computed as follows:

$C_{LEXT}=2 (C_{L}-C_{STRAY}-C_{SHUNT})$

where  $\texttt{C}_{\texttt{STRAY}}$  is the capacitance of the pins and PCB and <code>CSHUNT</code> is the shunt capacitance of the <code>crystal</code>.

| Table 47-21. 32kHz Crysta | Oscillator Characteristics |

|---------------------------|----------------------------|

|---------------------------|----------------------------|

| Symbol                            | Parameter                                     | Conditions                                | Min. | Тур.  | Max  | Units |

|-----------------------------------|-----------------------------------------------|-------------------------------------------|------|-------|------|-------|

| f <sub>OUT</sub> <sup>(1)</sup>   | Crystal oscillator frequency                  |                                           | -    | 32768 | -    | Hz    |

| C <sub>L</sub> <sup>(1)</sup>     | Crystal load capacitance                      |                                           | -    | -     | 12.5 | pF    |

| C <sub>SHUNT</sub> <sup>(1)</sup> | Crystal shunt capacitance                     |                                           | -    | -     | 1.75 |       |

| C <sub>M</sub> <sup>(1)</sup>     | Motional capacitance                          |                                           | -    | 1.25  | -    | fF    |

| ESR                               | Crystal Equivalent Series Resistance - SF = 3 | F = 32.768kHz, C <sub>L</sub> =12.5<br>pF | -    | -     | 70   | kΩ    |

| C <sub>XIN32K</sub>               | Parasitic capacitor load                      |                                           | -    | 3.8   | -    | pF    |

# Table 48-12. Package Characteristics Moisture Sensitivity Level MSL1 Table 48-13. Package Reference JEDEC Drawing Reference N/A JESD97 Classification e1

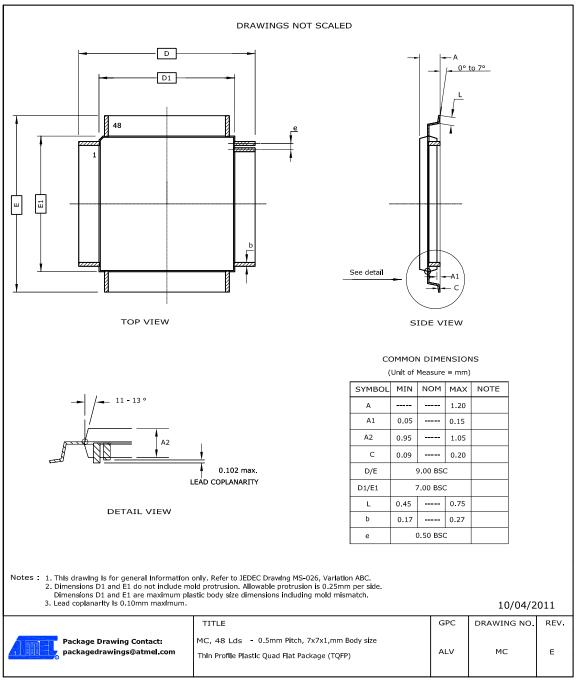

#### 48.2.5 48 pin TQFP

|                                                         | <ul> <li>Digital Phase Locked Loop (DPLL) Characteristics:<br/>Updated values.</li> <li>48 MHz RC Oscillator (OSC48M) Characteristics:<br/>Added note on the output frequency regarding<br/>accuracy for the WLCSP package.</li> </ul>                                                                                                                                                                                                              |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Characteristics 105°C (SAM<br>C20/C21 E/G/J) | <ul> <li>Power Consumption: Standby typical values updated<br/>and maximum values added.</li> <li>NVM Characteristics: New section added.</li> <li>Analog Comparator (AC) Characteristics: Updated<br/>IDDANA units from nA to μA and updated condition for<br/>IDD with voltage scaler disabled<br/>(COMPCTRLn.SPEED = 0x1 changed to 0x3).</li> <li>Digital Phase Locked Loop (DPLL) Characteristics:<br/>Characterization data added.</li> </ul> |

| Packaging Information                                   | <ul> <li>Added package outline drawing (POD) for 56-Ball<br/>WLCSP.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                      |

| Schematic Checklist                                     | <ul> <li>External Analog Reference Connections:<br/>Recommended pin connections column updated.</li> <li>External Reset Circuit: Updated description.</li> </ul>                                                                                                                                                                                                                                                                                    |

## 50.6 Rev H - 05/2016

| Product Mapping                                    | <ul> <li>AHB-APB Bridge B:</li> <li>DMAC base address corrected from 0x41004400 to 0x4106000.</li> <li>MTB base address corrected from 0x41004800 to 0x41008000.</li> <li>Reserved space corrected from 0x41005000 to</li> </ul> |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Micro Trace Buffer                                 | 0x41009000.<br>MTB base address corrected from 0x41006000 to<br>0x41008000.                                                                                                                                                      |

| SUPC – Supply Controller                           | VDD Brown-Out Detector (BODVDD): Removed references<br>to battery backup (VBAT) and voltage monitored bit<br>(BODVDD.VMON).                                                                                                      |

| ADC – Analog-to-Digital Converter                  | Updated formula to increase the resolution by n bits in<br>Oversampling and Decimation.                                                                                                                                          |

| SDADC – Sigma-Delta Analog-to-Digital<br>Converter | Decimation Filter: Removed figure of spectral mask of an OSR=32. This option is not available.                                                                                                                                   |

| TSENS – Temperature Sensor                         | <ul><li>INTFLAG.OVF bit description updated.</li><li>GAIN and OFFSET register bit description updated.</li></ul>                                                                                                                 |