Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g17a-mnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name:<br>Offset:<br>Reset: | EVCTRL<br>0x04<br>0x00 |                             |                             |                             |                                           |                                           |                             |

|----------------------------|------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------------------|-------------------------------------------|-----------------------------|

| 7                          | 6                      | 5                           | 4                           | 3                           | 2                                         | 1                                         | 0                           |

|                            |                        |                             |                             |                             |                                           |                                           | ERREO                       |

|                            |                        |                             |                             |                             |                                           |                                           | RW                          |

|                            |                        |                             |                             |                             |                                           |                                           | 0                           |

| (                          | Offset:<br>Reset:      | Dffset: 0x04<br>Reset: 0x00 | Dffset: 0x04<br>Reset: 0x00 | Dffset: 0x04<br>Reset: 0x00 | <b>Dffset:</b> 0x04<br><b>Reset:</b> 0x00 | <b>Dffset:</b> 0x04<br><b>Reset:</b> 0x00 | Dffset: 0x04<br>Reset: 0x00 |

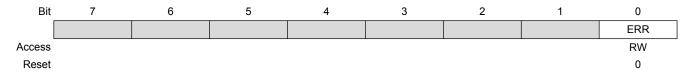

## Bit 0 – ERREO: Peripheral Access Error Event Output

This bit indicates if the Peripheral Access Error Event Output is enabled or disabled. When enabled, an event will be generated when one of the interrupt flag registers bits (INTFLAGAHB, INTFLAGn) is set:

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Peripheral Access Error Event Output is disabled. |

| 1     | Peripheral Access Error Event Output is enabled.  |

## 11.7.3 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

## Bit 0 – ERR: Peripheral Access Error Interrupt Disable

This bit indicates that the Peripheral Access Error Interrupt is disabled and an interrupt request will be generated when one of the interrupt flag registers bits (INTFLAGAHB, INTFLAGn) is set:

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Peripheral Access Error interrupt Enable bit and disables the corresponding interrupt request.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Peripheral Access Error interrupt is disabled. |

| 1     | Peripheral Access Error interrupt is enabled.  |

## 11.7.4 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENCLR).

## 12. Peripherals Configuration Summary

## 12.1 SAM C20/C21 N

## Table 12-1. Peripherals Configuration Summary SAM C21 N

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | 3 Clock             | AP | B Clock             | Generic<br>Clock                                  | P     | AC               |                       | Events                                                 | DMA            |                  |

|---------------------|-----------------|-------------|-------|---------------------|----|---------------------|---------------------------------------------------|-------|------------------|-----------------------|--------------------------------------------------------|----------------|------------------|

|                     |                 |             | Index | Enabled<br>at Reset |    | Enabled<br>at Reset | Index                                             | Index | Prot at<br>Reset | User                  | Generator                                              | Index          | Sleep<br>Walking |

| AHB-APB<br>Bridge A | 0x40000000      |             | 0     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| PAC                 | 0x40000000      | 0           | 10    | Y                   | 0  | Y                   |                                                   | 0     | Ν                |                       | 85 : ACCERR                                            |                | N/A              |

| PM                  | 0x40000400      | 0           |       |                     | 1  | Y                   |                                                   | 1     | Ν                |                       |                                                        |                | N/A              |

| MCLK                | 0x40000800      | 0           |       |                     | 2  | Y                   |                                                   | 2     | N                |                       |                                                        |                | Y                |

| RSTC                | 0x40000C00      |             |       |                     | 3  | Y                   |                                                   | 3     | N                |                       |                                                        |                | N/A              |

| OSCCTRL             | 0x40001000      | 0           |       |                     | 4  | Y                   | 0: FDPLL96M<br>clk source<br>1: FDPLL96M<br>32kHz | 4     | Ν                |                       | 0: XOSC_FAIL                                           |                | Y                |

| OSC32KCTRL          | 0x40001400      | 0           |       |                     | 5  | Y                   |                                                   | 5     | Ν                |                       | 1: XOSC32K_FAIL                                        |                | Y                |

| SUPC                | 0x40001800      | 0           |       |                     | 6  | Y                   |                                                   | 6     | Ν                |                       |                                                        |                | N/A              |

| GCLK                | 0x40001C00      |             |       |                     | 7  | Y                   |                                                   | 7     | N                |                       |                                                        |                | N/A              |

| WDT                 | 0x40002000      | 1           |       |                     | 8  | Y                   |                                                   | 8     | Ν                |                       |                                                        |                | Y                |

| RTC                 | 0x40002400      | 2           |       |                     | 9  | Y                   |                                                   | 9     | Ν                |                       | 2: CMP0/ALARM0<br>3: CMP1<br>4: OVF5-1<br>5:12: PER0-7 |                | Y                |

| EIC                 | 0x40002800      | 3,<br>NMI   |       |                     | 10 | Y                   | 2                                                 | 10    | N                |                       | 13-28: EXTINT0-15                                      |                | Y                |

| FREQM               | 0x40002C00      | 4           |       |                     | 11 | Y                   | 3: Measure<br>4: Reference                        | 11    | N                |                       |                                                        |                | N/A              |

| TSENS               | 0x40003000      | 5           |       |                     | 12 | Ν                   | 5                                                 | 12    | Ν                | 0: START              | 29: WINMON                                             | 1: RESRDY      | A                |

| AHB-APB<br>Bridge B | 0x41000000      |             | 1     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| PORT                | 0x41000000      |             |       |                     | 0  | Y                   |                                                   | 0     | Ν                | 1-4 : EV0-3           |                                                        |                | Y                |

| DSU                 | 0x41002000      |             | 3     | Y                   | 1  | Y                   |                                                   | 1     | Y                |                       |                                                        |                | N/A              |

| NVMCTRL             | 0x41004000      | 6           | 5     | Y                   | 2  | Y                   | 39                                                | 2     | Ν                |                       |                                                        |                | Y                |

| DMAC                | 0x41006000      | 7           | 7     | Y                   |    |                     |                                                   | 3     | Ν                | 5-8: CH0-3            | 30-33: CH0-3                                           |                | Y                |

| MTB                 | 0x41008000      |             |       |                     |    |                     |                                                   |       | N                | 45: START<br>46: STOP |                                                        |                | N/A              |

| AHB-APB<br>Bridge C | 0x42000000      |             | 2     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| EVSYS               | 0x42000000      | 8           |       |                     | 0  | Ν                   | 6-17: one per<br>CHANNEL                          | 0     | Ν                |                       |                                                        |                | Y                |

| SERCOM0             | 0x42000400      | 9           |       |                     | 1  | N                   | 19: CORE<br>18: SLOW                              | 1     | N                |                       |                                                        | 2: RX<br>3: TX | Y                |

| SERCOM1             | 0x42000800      | 10          |       |                     | 2  | N                   | 20: CORE<br>18: SLOW                              | 2     | N                |                       |                                                        | 4: RX<br>5: TX | Y                |

| SERCOM2             | 0x42000C00      | 11          |       |                     | 3  | N                   | 21: CORE<br>18: SLOW                              | 3     | N                |                       |                                                        | 6: RX<br>7: TX | Y                |

| SERCOM3             | 0x42001000      | 12          |       |                     | 4  | N                   | 22: CORE<br>18: SLOW                              | 4     | Ν                |                       |                                                        | 8: RX<br>9: TX | Y                |

## Bit 2 – VREFOE: Voltage Reference Output Enable

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The Voltage Reference output is not available as an ADC input channel. |

| 1     | The Voltage Reference output is routed to an ADC input channel.        |

## Bit 1 – TSEN: Temperature Sensor Enable

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | Temperature Sensor is disabled.                                   |

| 1     | Temperature Sensor is enabled and routed to an ADC input channel. |

The following DMAC bit is enable-protected, meaning that it can only be written when both the DMAC and CRC are disabled (CTRL.DMAENABLE=0 and CTRL.CRCENABLE=0):

• Software Reset bit in Control register (CTRL.SWRST)

The following DMA channel register is enable-protected, meaning that it can only be written when the corresponding DMA channel is disabled (CHCTRLA.ENABLE=0):

Channel Control B (CHCTRLB) register, except the Command bit (CHCTRLB.CMD) and the Channel Arbitration Level bit (CHCTRLB.LVL)

The following DMA channel bit is enable-protected, meaning that it can only be written when the corresponding DMA channel is disabled:

• Channel Software Reset bit in Channel Control A register (CHCTRLA.SWRST)

The following CRC registers are enable-protected, meaning that they can only be written when the CRC is disabled (CTRL.CRCENABLE=0):

- CRC Control register (CRCCTRL)

- CRC Checksum register (CRCCHKSUM)

Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before the DMAC is enabled it must be configured, as outlined by the following steps:

- The SRAM address of where the descriptor memory section is located must be written to the Description Base Address (BASEADDR) register

- The SRAM address of where the write-back section should be located must be written to the Write-Back Memory Base Address (WRBADDR) register

- Priority level x of the arbiter can be enabled by setting the Priority Level x Enable bit in the Control register (CTRL.LVLENx=1)

Before a DMA channel is enabled, the DMA channel and the corresponding first transfer descriptor must be configured, as outlined by the following steps:

- DMA channel configurations

- The channel number of the DMA channel to configure must be written to the Channel ID (CHID) register

- Trigger action must be selected by writing the Trigger Action bit group in the Channel Control B register (CHCTRLB.TRIGACT)

- Trigger source must be selected by writing the Trigger Source bit group in the Channel Control B register (CHCTRLB.TRIGSRC)

- Transfer Descriptor

- The size of each access of the data transfer bus must be selected by writing the Beat Size bit group in the Block Transfer Control register (BTCTRL.BEATSIZE)

- The transfer descriptor must be made valid by writing a one to the Valid bit in the Block Transfer Control register (BTCTRL.VALID)

- Number of beats in the block transfer must be selected by writing the Block Transfer Count (BTCNT) register

- Source address for the block transfer must be selected by writing the Block Transfer Source Address (SRCADDR) register

- Destination address for the block transfer must be selected by writing the Block Transfer Destination Address (DSTADDR) register

#### OSC32KCTRL - 32KHz Oscillators Controller

## 26.5.4 DMA

Not applicable.

## 26.5.5 Interrupts

There are two interrupt request lines, one for the external interrupts (EXTINT) and one for non-maskable interrupt (NMI).

The EXTINT interrupt request line is connected to the interrupt controller. Using the EIC interrupt requires the interrupt controller to be configured first.

The NMI interrupt request line is also connected to the interrupt controller, but does not require the interrupt to be configured.

#### **Related Links**

Nested Vector Interrupt Controller

## 26.5.6 Events

The events are connected to the Event System. Using the events requires the Event System to be configured first.

## **Related Links**

EVSYS – Event System

## 26.5.7 Debug Operation

When the CPU is halted in debug mode, the EIC continues normal operation. If the EIC is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 26.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Non-Maskable Interrupt Flag Status and Clear register (NMIFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

26.5.9 Analog Connections

Not applicable.

## 26.6 Functional Description

## 26.6.1 Principle of Operation

The EIC detects edge or level condition to generate interrupts to the CPU interrupt controller or events to the Event System. Each external interrupt pin (EXTINT) can be filtered using majority vote filtering, clocked by GCLK\_EIC or by CLK\_ULP32K.

| Bit    | 31 | 30 | 29 | 28    | 27       | 26 | 25 | 24 |

|--------|----|----|----|-------|----------|----|----|----|

|        |    |    |    | DIRSE | Г[31:24] |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19       | 18 | 17 | 16 |

|        |    |    |    | DIRSE | Г[23:16] |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9  | 8  |

|        |    |    |    | DIRSE | T[15:8]  |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0  |

|        |    |    |    | DIRSE | ET[7:0]  |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

## Bits 31:0 – DIRSET[31:0]: Port Data Direction Set

Writing '0' to a bit has no effect.

Writing '1' to a bit will set the corresponding bit in the DIR register, which configures the I/O pin as an output.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration. |

| 1     | The corresponding I/O pin in the PORT group is configured as an output.  |

#### 28.9.4 Data Direction Toggle

This register allows the user to toggle the direction of one or more I/O pins, without doing a read-modifywrite operation. Changes in this register will also be reflected in the Data Direction (DIR), Data Direction Set (DIRSET) and Data Direction Clear (DIRCLR) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

Name:DIRTGLOffset:0x0CReset:0x00000000Property:PAC Write-Protection

## SAM C20/C21

| CPOL | TxD Change       | RxD Sample       |

|------|------------------|------------------|

| 0x0  | Rising XCK edge  | Falling XCK edge |

| 0x1  | Falling XCK edge | Rising XCK edge  |

## Bit 28 – CMODE: Communication Mode

This bit selects asynchronous or synchronous communication.

This bit is not synchronized.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Asynchronous communication. |

| 1     | Synchronous communication.  |

## Bits 27:24 – FORM[3:0]: Frame Format

These bits define the frame format.

These bits are not synchronized.

| FORM[3:0] | Description                                                             |

|-----------|-------------------------------------------------------------------------|

| 0x0       | USART frame                                                             |

| 0x1       | USART frame with parity                                                 |

| 0x2       | LIN Master - Break and sync generation. See LIN Command (CTRLB.LINCMD). |

| 0x3       | Reserved                                                                |

| 0x4       | Auto-baud - break detection and auto-baud.                              |

| 0x5       | Auto-baud - break detection and auto-baud with parity                   |

| 0x6-0xF   | Reserved                                                                |

## Bits 23:22 – SAMPA[1:0]: Sample Adjustment

These bits define the sample adjustment.

These bits are not synchronized.

| SAMPA[1:0] | 16x Over-sampling (CTRLA.SAMPR=0 or 1) | 8x Over-sampling (CTRLA.SAMPR=2 or 3) |

|------------|----------------------------------------|---------------------------------------|

| 0x0        | 7-8-9                                  | 3-4-5                                 |

| 0x1        | 9-10-11                                | 4-5-6                                 |

| 0x2        | 11-12-13                               | 5-6-7                                 |

| 0x3        | 13-14-15                               | 6-7-8                                 |

## Bits 21:20 – RXPO[1:0]: Receive Data Pinout

These bits define the receive data (RxD) pin configuration.

These bits are not synchronized.

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28 | 27 | 26    | 25     | 24    |

|--------|----|----|----|----|----|-------|--------|-------|

|        |    |    |    |    |    |       |        |       |

| Access |    |    |    |    |    |       |        |       |

| Reset  |    |    |    |    |    |       |        |       |

|        |    |    |    |    |    |       |        |       |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18    | 17     | 16    |

|        |    |    |    |    |    |       |        |       |

| Access |    |    |    |    |    |       |        |       |

| Reset  |    |    |    |    |    |       |        |       |

|        |    |    |    |    |    |       |        |       |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10    | 9      | 8     |

| [      |    |    |    |    |    |       |        |       |

| Access |    |    |    |    |    |       |        |       |

| Reset  |    |    |    |    |    |       |        |       |

|        |    |    |    |    |    |       |        |       |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2     | 1      | 0     |

|        |    |    |    |    |    | CTRLB | ENABLE | SWRST |

| Access |    |    |    |    |    | R     | R      | R     |

| Reset  |    |    |    |    |    | 0     | 0      | 0     |

## Bit 2 – CTRLB: CTRLB Synchronization Busy

Writing to the CTRLB register when the SERCOM is enabled requires synchronization. When writing to CTRLB the SYNCBUSY.CTRLB bit will be set until synchronization is complete. If CTRLB is written while SYNCBUSY.CTRLB is asserted, an APB error will be generated.

| Value | Description                        |

|-------|------------------------------------|

| 0     | CTRLB synchronization is not busy. |

| 1     | CTRLB synchronization is busy.     |

## Bit 1 – ENABLE: SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

Writes to any register (except for CTRLA.SWRST) while enable synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

#### Bit 0 – SWRST: Software Reset Synchronization Busy

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

Writes to any register while synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                        |  |  |  |

|-------|------------------------------------|--|--|--|

| 0     | SWRST synchronization is not busy. |  |  |  |

| 1     | SWRST synchronization is busy.     |  |  |  |

## 31.8.11 Data

| Value | Description               |

|-------|---------------------------|

| 0     | MSB is transferred first. |

| 1     | LSB is transferred first. |

#### Bit 29 – CPOL: Clock Polarity

In combination with the Clock Phase bit (CPHA), this bit determines the SPI transfer mode.

This bit is not synchronized.

| Va | alue | Description                                                                                                           |

|----|------|-----------------------------------------------------------------------------------------------------------------------|

| 0  |      | SCK is low when idle. The leading edge of a clock cycle is a rising edge, while the trailing edge is a falling edge.  |

| 1  |      | SCK is high when idle. The leading edge of a clock cycle is a falling edge, while the trailing edge is a rising edge. |

#### Bit 28 – CPHA: Clock Phase

In combination with the Clock Polarity bit (CPOL), this bit determines the SPI transfer mode.

This bit is not synchronized.

| Mode | CPOL | СРНА | Leading Edge    | Trailing Edge   |

|------|------|------|-----------------|-----------------|

| 0x0  | 0    | 0    | Rising, sample  | Falling, change |

| 0x1  | 0    | 1    | Rising, change  | Falling, sample |

| 0x2  | 1    | 0    | Falling, sample | Rising, change  |

| 0x3  | 1    | 1    | Falling, change | Rising, sample  |

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | The data is sampled on a leading SCK edge and changed on a trailing SCK edge. |

| 1     | The data is sampled on a trailing SCK edge and changed on a leading SCK edge. |

#### Bits 27:24 – FORM[3:0]: Frame Format

This bit field selects the various frame formats supported by the SPI in slave mode. When the 'SPI frame with address' format is selected, the first byte received is checked against the ADDR register.

| FORM[3:0] | Name     | Description            |

|-----------|----------|------------------------|

| 0x0       | SPI      | SPI frame              |

| 0x1       | -        | Reserved               |

| 0x2       | SPI_ADDR | SPI frame with address |

| 0x3-0xF   | -        | Reserved               |

## Bits 21:20 – DIPO[1:0]: Data In Pinout

These bits define the data in (DI) pad configurations.

In master operation, DI is MISO.

In slave operation, DI is MOSI.

These bits are not synchronized.

# SAM C20/C21

| Bit    | 31 | 30 | 29       | 28 | 27 | 26 | 25     | 24    |

|--------|----|----|----------|----|----|----|--------|-------|

|        |    |    |          |    |    |    |        |       |

| Access |    |    |          |    |    |    |        |       |

| Reset  |    |    |          |    |    |    |        |       |

|        |    |    |          |    |    |    |        |       |

| Bit    | 23 | 22 | 21       | 20 | 19 | 18 | 17     | 16    |

|        |    |    |          |    |    |    |        |       |

| Access |    | ļ  | <u> </u> | L  |    |    |        |       |

| Reset  |    |    |          |    |    |    |        |       |

|        |    |    |          |    |    |    |        |       |

| Bit    | 15 | 14 | 13       | 12 | 11 | 10 | 9      | 8     |

| [      |    |    |          |    |    |    |        |       |

| Access |    |    |          |    |    |    |        |       |

| Reset  |    |    |          |    |    |    |        |       |

|        |    |    |          |    |    |    |        |       |

| Bit    | 7  | 6  | 5        | 4  | 3  | 2  | 1      | 0     |

|        |    |    |          |    |    |    | ENABLE | SWRST |

| Access |    |    |          |    |    |    | R      | R     |

| Reset  |    |    |          |    |    |    | 0      | 0     |

## Bit 1 – ENABLE: SERCOM Enable Synchronization Busy

Enabling and disabling the SERCOM (CTRLA.ENABLE) requires synchronization. When written, the SYNCBUSY.ENABLE bit will be set until synchronization is complete.

Writes to any register (except for CTRLA.SWRST) while enable synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Enable synchronization is not busy. |

| 1     | Enable synchronization is busy.     |

#### **Bit 0 – SWRST: Software Reset Synchronization Busy**

Resetting the SERCOM (CTRLA.SWRST) requires synchronization. When written, the SYNCBUSY.SWRST bit will be set until synchronization is complete.

Writes to any register while synchronization is on-going will be discarded and an APB error will be generated.

| Value | Description                        |  |

|-------|------------------------------------|--|

| 0     | SWRST synchronization is not busy. |  |

| 1     | SWRST synchronization is busy.     |  |

#### 33.8.8 Address

Name:ADDROffset:0x24 [ID-00001bb3]Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 7     | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|--------|-------|---|---|---|---|---|-----|-----|

|        | ERROR |   |   |   |   |   | SB  | MB  |

| Access | R/W   |   |   |   |   |   | R/W | R/W |

| Reset  | 0     |   |   |   |   |   | 0   | 0   |

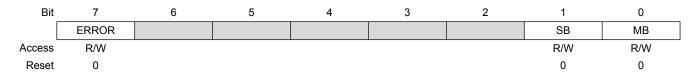

## Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

#### Bit 1 – SB: Slave on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Slave on Bus Interrupt Enable bit, which enables the Slave on Bus interrupt.

| Value | Description                             |  |

|-------|-----------------------------------------|--|

| 0     | The Slave on Bus interrupt is disabled. |  |

| 1     | The Slave on Bus interrupt is enabled.  |  |

## Bit 0 – MB: Master on Bus Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Master on Bus Interrupt Enable bit, which enables the Master on Bus interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Master on Bus interrupt is disabled. |

| 1     | The Master on Bus interrupt is enabled.  |

#### 33.10.6 Interrupt Flag Status and Clear

Name:

INTFLAG

Offset:

0x18 [ID-00001bb3]

Reset:

0x00

Property:

## Bit 7 – ERROR: Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status bits in the STATUS register. These status bits are LENERR, SEXTTOUT, MEXTTOUT, LOWTOUT, ARBLOST, and BUSERR.

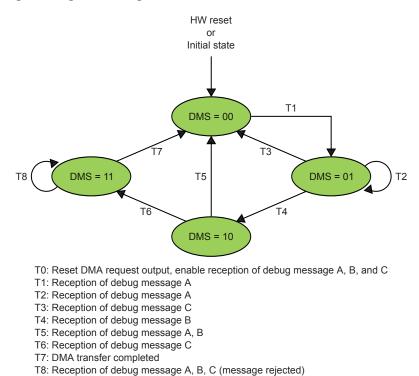

| Filter Element | SFID1[10:0] / EFID1[28:0] | SFID2[10:9] / EFID2[10:9] | SFID2[5:0] / EFID2[5:0] |

|----------------|---------------------------|---------------------------|-------------------------|

| 0              | ID debug message A        | 01                        | 11 1101                 |

| 1              | ID debug message B        | 10                        | 11 1110                 |

| 2              | ID debug message C        | 11                        | 11 1111                 |

Table 34-5. Example Filter Configuration for Debug Messages

## **Debug Message Handling**

The debug message handling state machine assures that debug messages are stored to three consecutive Rx Buffers in correct order. In case of missing messages the process is restarted. The DMA request is activated only when all three debug messages A, B, C have been received in correct order.

#### Figure 34-9. Debug Message Handling State Machine

## 34.6.6 Tx Handling

The Tx Handler handles transmission requests for the dedicated Tx Buffers, the Tx FIFO, and the Tx Queue. It controls the transfer of transmit messages to the CAN Core, the Put and Get Indices, and the Tx Event FIFO. Up to 32 Tx Buffers can be set up for message transmission. The CAN mode for transmission (Classic CAN or CAN FD) can be configured separately for each Tx Buffer element. The Tx Buffer element is described in Tx Buffer Element. The table below describes the possible configurations for frame transmission.

## 34.6.8 Interrupts

The CAN has the following interrupt sources:

- Access to Reserved Address

- Protocol Errors (Data Phase / Arbitration Phase)

- Watchdog Interrupt

- Bus Off Status

- Error Warning & Passive

- Error Logging Overflow

- Message RAM Bit Errors (Uncorrected / Corrected)

- Message stored to Dedicated Rx Buffer

- Timeout Occurred

- Message RAM Access Failure

- Timestamp Wraparound

- Tx Event FIFO statuses (Element Lost / Full / Watermark Reached / New Entry)

- Tx FIFO Empty

- Transmission Cancellation Finished

- Timestamp Completed

- High Priority Message

- Rx FIFO 1 Statuses (Message Lost / Full / Watermark Reached / New Message)

- Rx FIFO 0 Statuses (Message Lost / Full / Watermark Reached / New Message)

Each interrupt source has an interrupt flag associated with it. The interrupt flag register (IR) is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing '1' or disabled by writing '0' to the corresponding bit in the interrupt enable register (IE). Each interrupt flag can be assigned to one of two interrupt service lines.

An interrupt request is generated when an interrupt flag is set, the corresponding interrupt enable is set, and the corresponding service line enable assigned to the interrupt is set. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, the service line is disabled, or the CAN is reset. Refer to IR for details on how to clear interrupt flags. All interrupt requests from the peripheral are sent to the NVIC. The user must read the IR register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

Nested Vector Interrupt Controller

## 34.6.9 Sleep Mode Operation

The CAN can be configured to operate in any idle sleep mode. Tha CAN cannot operate in Standby sleep mode.

The CAN has its own low power mode that may be used at any time without disabling the CAN. It is also mandatory to allow the CAN to complete all pending transactions before entering standby by activating this low power mode. This is performed by writing one to the Clock Stop Request bit in the CC Control register (CCCR.CSR = 1). Once all pending transactions are completed and the idle bus state is detected, the CAN will automatically set the Clock Stop Acknowledge bit (CCCR.CSA = 1). The CAN then reverts back to its initial state (CCCR.INIT = 1), blocking further transfers, and it is now safe for CLK\_CANx\_APB and GCLK\_CANx to be switched off and the system may go to standby.

# SAM C20/C21

| Bit    | 21 | 20 | 29 | 28 | 27 | 26 | 25  | 24     |

|--------|----|----|----|----|----|----|-----|--------|

| ы      | 31 | 30 | 29 | 20 | 27 | 20 | 25  | 24     |

|        |    |    |    |    |    |    |     |        |

| Access |    |    |    |    |    |    |     |        |

| Reset  |    |    |    |    |    |    |     |        |

|        |    |    |    |    |    |    |     |        |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17  | 16     |

|        |    |    |    |    |    |    |     |        |

| Access |    | •  | •  | •  |    |    |     |        |

| Reset  |    |    |    |    |    |    |     |        |

|        |    |    |    |    |    |    |     |        |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9   | 8      |

|        |    |    |    |    |    |    |     |        |

| Access |    |    |    |    |    |    |     |        |

| Reset  |    |    |    |    |    |    |     |        |

|        |    |    |    |    |    |    |     |        |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0      |

|        | -  | -  | -  | _  | -  | _  |     | S[1:0] |

| Access |    |    |    |    |    |    | R/W | R/W    |

|        |    |    |    |    |    |    |     |        |

| Reset  |    |    |    |    |    |    | 1   | 0      |

## Bits 1:0 – DQOS[1:0]: Data Quality of Service

This field defines the memory priority access during the Message RAM read/write data operation.

| Value | Name    | Description                         |

|-------|---------|-------------------------------------|

| 0x0   | DISABLE | Background (no sensitive operation) |

| 0x1   | LOW     | Sensitive bandwidth                 |

| 0x2   | MEDIUM  | Sensitive latency                   |

| 0x3   | HIGH    | Critical latency                    |

#### 34.8.4 Data Bit Timing and Prescaler

This register is write-restricted and only writable if bit fields CCCR.CCE = 1 and CCCR.INIT = 1.

The CAN bit time may be programmed in the range of 4 to 49 time quanta. The CAN time quantum may be programmed in the range of 1 to 32 GCLK\_CAN periods.  $t_q = (DBRP + 1) mtq$ .

#### Note:

With a GCLK\_CAN of 8MHz, the reset value 0x00000A33 configures the CAN for a fast bit rate of 500 kBits/s.

The bit rate configured for the CAN FD data phase via DBTP must be higher or equal to the bit rate configured for the arbitration phase via NBTP.

Name:DBTPOffset:0x0C [ID-0000a4bb]Reset:0x00000A33Property:Write-restricted

## Bit 8 – OVFEO: Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

## Bit 5 – TCEI: TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

## Bit 4 – TCINV: TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Input event source is not inverted. |

| 1     | Input event source is inverted.     |

## Bits 2:0 – EVACT[2:0]: Event Action

These bits define the event action the TC will perform on an event.

| Value | Name      | Description                                |

|-------|-----------|--------------------------------------------|

| 0x0   | OFF       | Event action disabled                      |

| 0x1   | RETRIGGER | Start, restart or retrigger TC on event    |

| 0x2   | COUNT     | Count on event                             |

| 0x3   | START     | Start TC on event                          |

| 0x4   | STAMP     | Time stamp capture                         |

| 0x5   | PPW       | Period captured in CC0, pulse width in CC1 |

| 0x6   | PWP       | Period captured in CC1, pulse width in CC0 |

| 0x7   | PW        | Pulse width capture                        |

#### 35.7.2.5 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

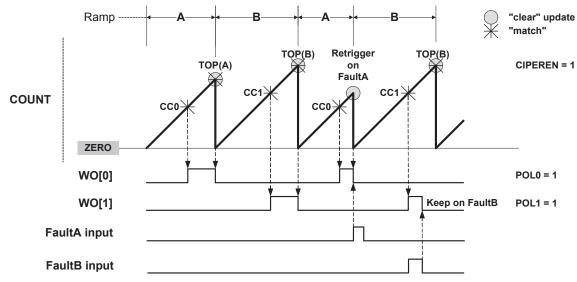

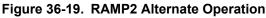

A, odd channel output is disabled, and in cycle B, even channel output is disabled. The ramp index changes after each update, but can be software modified using the Ramp index command bits in Control B Set register (CTRLBSET.IDXCMD).

## Standard RAMP2 (RAMP2) Operation

Ramp A and B periods are controlled by the PER register value. The PER value can be different on each ramp by the Circular Period buffer option in the Wave register (WAVE.CIPEREN=1). This mode uses a two-channel TCC to generate two output signals, or one output signal with another CC channel enabled in capture mode.

## Figure 36-18. RAMP2 Standard Operation

## Alternate RAMP2 (RAMP2A) Operation

Alternate RAMP2 operation is similar to RAMP2, but CC0 controls both WO[0] and WO[1] waveforms when the corresponding circular buffer option is enabled (CIPEREN=1). The waveform polarity is the same on both outputs. Channel 1 can be used in capture mode.

Channel For a capture channel, the request is set when valid data is present in the CCx register, and cleared once the CCx register is read.(MCx) In this operation mode, the CTRLA.DMAOS bit value is ignored.

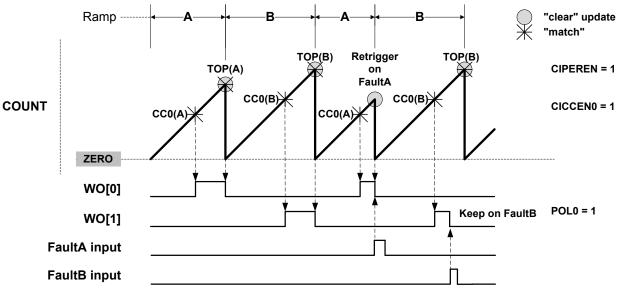

## DMA Operation with Circular Buffer

When circular buffer operation is enabled, the buffer registers must be written in a correct order and synchronized to the update times of the timer. The DMA triggers of the TCC provide a way to ensure a safe and correct update of circular buffers.

Note: Circular buffer are intended to be used with RAMP2, RAMP2A and DSBOTH operation only.

## DMA Operation with Circular Buffer in RAMP and RAMP2A Mode

When a CCx channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of ramp B.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of ramp A with an effective DMA transfer on previous ramp B (DMA acknowledge).

The update of all circular buffer values for ramp A can be done through a DMA channel triggered on a MC trigger. The update of all circular buffer values for ramp B, can be done through a second DMA channel triggered by the overflow DMA request.

Figure 36-37. DMA Triggers in RAMP and RAMP2 Operation Mode and Circular Buffer Enabled

DMA Operation with Circular Buffer in DSBOTH Mode

When a CC channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of down-counting phase.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of upcounting phase with an effective DMA transfer on previous down-counting phase (DMA acknowledge).

When up-counting, all circular buffer values can be updated through a DMA channel triggered by MC trigger. When down-counting, all circular buffer values can be updated through a second DMA channel, triggered by the OVF DMA request.

| Bit    | 23     | 22     | 21     | 20     | 19  | 18  | 17  | 16  |

|--------|--------|--------|--------|--------|-----|-----|-----|-----|

|        |        |        |        |        | MCx | MCx | MCx | MCx |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

|        |        |        |        |        |     |     |     |     |

| Bit    | 15     | 14     | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx | FAULTx | FAULTB | FAULTA | DFS | UFS |     |     |

| Access | R/W    | R/W    | R/W    | R/W    | R/W | R/W |     |     |

| Reset  | 0      | 0      | 0      | 0      | 0   | 0   |     |     |

|        |        |        |        |        |     |     |     |     |

| Bit    | 7      | 6      | 5      | 4      | 3   | 2   | 1   | 0   |

|        |        |        |        |        | ERR | CNT | TRG | OVF |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

## Bits 19,18,17,16 – MCx: Match or Capture Channel x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the corresponding Match or Capture Channel x Interrupt Disable/Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

## Bits 15,14 – FAULTx: Non-Recoverable Fault x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Non-Recoverable Fault x Interrupt Disable/Enable bit, which enables the Non-Recoverable Fault x interrupt.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The Non-Recoverable Fault x interrupt is disabled. |

| 1     | The Non-Recoverable Fault x interrupt is enabled.  |

#### Bit 13 – FAULTB: Recoverable Fault B Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault B Interrupt Disable/Enable bit, which enables the Recoverable Fault B interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Recoverable Fault B interrupt is disabled. |

| 1     | The Recoverable Fault B interrupt is enabled.  |

#### Bit 12 – FAULTA: Recoverable Fault A Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault A Interrupt Disable/Enable bit, which enables the Recoverable Fault A interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Recoverable Fault A interrupt is disabled. |

| 1     | The Recoverable Fault A interrupt is enabled.  |

## Table 37-1. Truth Table of LUT

| IN[2] | IN[1] | IN[0] | OUT      |

|-------|-------|-------|----------|

| 0     | 0     | 0     | TRUTH[0] |

| 0     | 0     | 1     | TRUTH[1] |

| 0     | 1     | 0     | TRUTH[2] |

| 0     | 1     | 1     | TRUTH[3] |

| 1     | 0     | 0     | TRUTH[4] |

| 1     | 0     | 1     | TRUTH[5] |

| 1     | 1     | 0     | TRUTH[6] |

| 1     | 1     | 1     | TRUTH[7] |

## 37.6.2.4 Truth Table Inputs Selection

## Input Overview

The inputs can be individually:

- Masked

- Driven by peripherals:

- Analog comparator output (AC)

- Timer/Counters waveform outputs (TC)

- Serial Communication output transmit interface (SERCOM)

- Driven by internal events from Event System

- Driven by other CCL sub-modules

The Input Selection for each input y of LUT x is configured by writing the Input y Source Selection bit in the LUT x Control register (LUTCTRLx.INSELy).

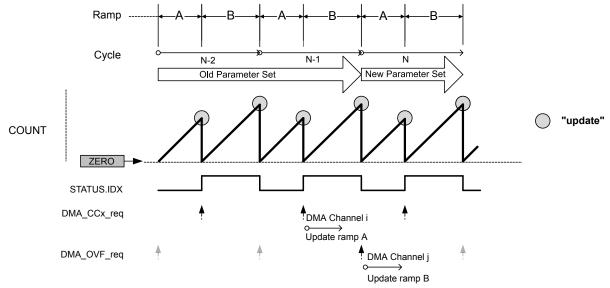

## Masked Inputs (MASK)

When a LUT input is masked (LUTCTRLx.INSELy=MASK), the corresponding TRUTH input (IN) is internally tied to zero, as shown in this figure:

## Figure 37-3. Masked Input Selection

## Internal Feedback Inputs (FEEDBACK)

When selected (LUTCTRLx.INSELy=FEEDBACK), the Sequential (SEQ) output is used as input for the corresponding LUT.

The output from an internal sequential sub-module can be used as input source for the LUT, see figure below for an example for LUT0 and LUT1. The sequential selection for each LUT follows the formula:

© 2017 Microchip Technology Inc.

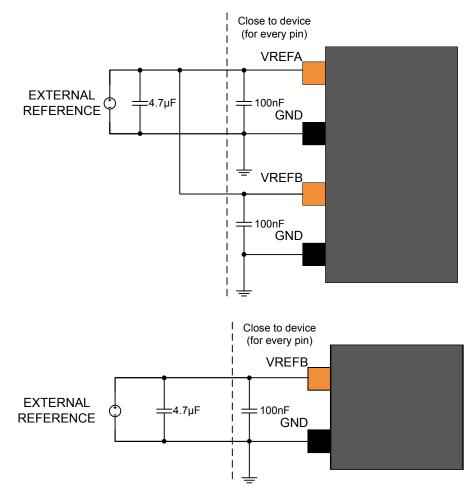

Figure 49-4. External Analog Reference Schematic With One Reference

| Signal Name | Recommended Pin Connection                                                     | Description                                           |  |

|-------------|--------------------------------------------------------------------------------|-------------------------------------------------------|--|

| VREFA       | 2.0V to V <sub>DDANA</sub> - 0.6V for ADC                                      | External reference from VREFA pin on the analog port. |  |

|             | 1.0V to V <sub>DDANA</sub> - 0.6V for DAC                                      |                                                       |  |

|             | Decoupling/filtering capacitors: 100nF <sup>(1)(2)</sup> and 4.7 $\mu F^{(1)}$ |                                                       |  |

| VREFB       | 1.0V to 5.5V for SDADC                                                         | External reference from VREFB                         |  |

|             | Decoupling/filtering capacitors: $100nF^{(1)(2)}$ and $4.7\mu F^{(1)}$         | pin on the analog port.                               |  |

| GND         |                                                                                | Ground                                                |  |

## Note:

- 1. These values are given as a typical example.

- 2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.