Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16К х 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g17a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 16.6.                                                                                                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 143                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16.7.                                                                                                                                                                                     | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 149                                                                                                                                                                  |

| 16.8.                                                                                                                                                                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 154                                                                                                                                                                  |

| 17 MCI                                                                                                                                                                                    | K – Main Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 163                                                                                                                                                                  |

|                                                                                                                                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|                                                                                                                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|                                                                                                                                                                                           | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

|                                                                                                                                                                                           | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

|                                                                                                                                                                                           | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|                                                                                                                                                                                           | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|                                                                                                                                                                                           | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

|                                                                                                                                                                                           | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

|                                                                                                                                                                                           | C – Reset Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

|                                                                                                                                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

|                                                                                                                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                      |

| 18.3.                                                                                                                                                                                     | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |

| 18.4.                                                                                                                                                                                     | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 183                                                                                                                                                                  |

| 18.5.                                                                                                                                                                                     | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 18.6.                                                                                                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

|                                                                                                                                                                                           | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

| 18.8.                                                                                                                                                                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 19. PM -                                                                                                                                                                                  | – Power Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

|                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 19.1.                                                                                                                                                                                     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 187                                                                                                                                                                  |

|                                                                                                                                                                                           | OverviewFeatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                      |

| 19.2.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 19.2.<br>19.3.                                                                                                                                                                            | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 187<br>187                                                                                                                                                           |

| 19.2.<br>19.3.<br>19.4.                                                                                                                                                                   | Features<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.                                                                                                                                                          | Features<br>Block Diagram<br>Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.                                                                                                                                                 | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.                                                                                                                                        | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies.<br>Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.                                                                                                                               | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br>20. OSC                                                                                                                    | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.                                                                                                    | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.                                                                                           | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.                                                                                  | Features Block Diagram Signal Description Product Dependencies Functional Description Register Summary Register Description CCTRL – Oscillators Controller Overview Features Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.                                                                         | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.                                                                | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.<br>20.6.                                                       | Features Block Diagram Signal Description Product Dependencies Functional Description Register Summary Register Description CCTRL – Oscillators Controller Overview Features Block Diagram Signal Description Product Dependencies Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.                                              | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.<br>20.8.                                     | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description                                                                                                                                                                                                                                                                                                                                                                                   | 187<br>187<br>187<br>187<br>187<br>188<br>192<br>192<br>192<br>194<br>194<br>194<br>194<br>195<br>195<br>195<br>195<br>195<br>206<br>207                             |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.<br>20.8.                                     | Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description<br>CCTRL – Oscillators Controller<br>Overview<br>Features<br>Block Diagram<br>Signal Description<br>Product Dependencies<br>Functional Description<br>Register Summary                                                                                                                                                                                                                                                                                                                                                                                                           | 187<br>187<br>187<br>187<br>187<br>188<br>192<br>192<br>192<br>194<br>194<br>194<br>194<br>195<br>195<br>195<br>195<br>195<br>206<br>207                             |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.3.<br>20.4.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.<br>20.8.<br><b>21. OSC</b><br>21.1. | Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         CCTRL – Oscillators Controller.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Summary.         Register Description.         C32KCTRL – 32KHz Oscillators Controller.         Overview. |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br><b>20. OSC</b><br>20.1.<br>20.3.<br>20.4.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.<br>20.8.<br><b>21. OSC</b><br>21.1. | Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         CCTRL – Oscillators Controller.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         Register Description.         Register Description.         C32KCTRL – 32KHz Oscillators Controller.                   |                                                                                                                                                                      |

| 19.2.<br>19.3.<br>19.4.<br>19.5.<br>19.6.<br>19.7.<br>19.8.<br>20. OSC<br>20.1.<br>20.2.<br>20.3.<br>20.4.<br>20.5.<br>20.6.<br>20.7.<br>20.8.<br>21. OSC<br>21.1.<br>21.2.               | Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Description.         CCTRL – Oscillators Controller.         Overview.         Features.         Block Diagram.         Signal Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Product Dependencies.         Functional Description.         Register Summary.         Register Summary.         Register Description.         C32KCTRL – 32KHz Oscillators Controller.         Overview. | 187<br>187<br>187<br>187<br>187<br>188<br>192<br>192<br>192<br>192<br>194<br>194<br>194<br>194<br>195<br>195<br>195<br>195<br>195<br>206<br>207<br>228<br>228<br>228 |

# SAM C20/C21

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | B Clock             | AP    | B Clock             | Generic<br>Clock     | P     | AC               |                                    | Events                                        | DMA                             |                 |

|---------------------|-----------------|-------------|-------|---------------------|-------|---------------------|----------------------|-------|------------------|------------------------------------|-----------------------------------------------|---------------------------------|-----------------|

|                     |                 |             | Index | Enabled<br>at Reset | Index | Enabled<br>at Reset | Index                | Index | Prot at<br>Reset | User                               | Generator                                     | Index                           | Sleep<br>Walkin |

| SERCOM4             | 0x42001400      | 13          |       |                     | 5     | N                   | 23: CORE<br>18: SLOW | 5     | N                |                                    |                                               | 10: RX<br>11: TX                | Y               |

| SERCOM5             | 0x42001800      | 14          |       |                     | 6     | N                   | 25: CORE<br>24: SLOW | 6     | N                |                                    |                                               | 12: RX<br>13: TX                | Y               |

| CAN0                | 0x42001C00      | 15          | 8     | N                   |       |                     | 26                   | 7     |                  |                                    |                                               | 14: DEBUG                       | N/A             |

| CAN1                | 0x42002000      | 16          | 9     | N                   |       |                     | 27                   | 8     |                  |                                    |                                               | 15: DEBUG                       | N/A             |

| TCC0                | 0x42002400      | 17          |       |                     | 9     | N                   | 28                   | 9     | N                | 9-10: EV0-1<br>11-14:<br>MC0-3     | 34: OVF<br>35: TRG<br>36: CNT<br>37-40: MC0-3 | 16: OVF<br>17-20:<br>MC0-3      | Y               |

| TCC1                | 0x42002800      | 18          |       |                     | 10    | N                   | 28                   | 10    | Ν                | 15-16:<br>EV0-1<br>17-18:<br>MC0-1 | 41: OVF<br>42: TRG<br>43: CNT<br>44-45: MC0-1 | 21: OVF<br>22-23:<br>MC0-1      | Y               |

| TCC2                | 0x42002C00      | 19          |       |                     | 11    | N                   | 29                   | 11    | N                | 19-20:<br>EV0-1<br>21-22:<br>MC0-1 | 46: OVF<br>47: TRG<br>48: CNT<br>49-50: MC0-1 | 24: OVF<br>25-26:<br>MC0-1      | Y               |

| TC0                 | 0x42003000      | 20          |       |                     | 12    | N                   | 30                   | 12    | N                | 23: EVU                            | 51: OVF<br>52-53: MC0-1                       | 27: OVF<br>28-29:<br>MC0-1      | Y               |

| TC1                 | 0x42003400      | 21          |       |                     | 13    | N                   | 30                   | 13    | N                | 24: EVU                            | 54: OVF<br>55-56: MC0-1                       | 30: OVF<br>31-32:<br>MC0-1      | Y               |

| TC2                 | 0x42003800      | 22          |       |                     | 14    | N                   | 31                   | 14    | N                | 25: EVU                            | 57: OVF<br>58-59: MC0-1                       | 33: OVF<br>34-35:<br>MC0-1      | Y               |

| TC3                 | 0x42003C00      | 23          |       |                     | 15    | N                   | 31                   | 15    | N                | 26: EVU                            | 60: OVF<br>61-62: MC0-1                       | 36: OVF<br>37-38:<br>MC0-1      | Y               |

| TC4                 | 0x42004000      | 24          |       |                     | 16    | N                   | 32                   | 16    | N                | 27: EVU                            | 63: OVF<br>64-65: MC0-1                       | 39: OVF<br>40-41:<br>MC0-1      | Y               |

| ADC0                | 0x42004400      | 25          |       |                     | 17    | N                   | 33                   | 17    | N                | 28: START<br>29: SYNC              | 66: RESRDY<br>67: WINMON                      | 42: RESRDY                      | Y               |

| ADC1                | 0x42004800      | 26          |       |                     | 18    | N                   | 34                   | 18    | N                | 30: START<br>31: SYNC              | 68: RESRDY<br>69: WINMON                      | 43: RESRDY                      | Y               |

| SDADC               | 0x42004C00      | 29          |       |                     | 19    | N                   | 35                   | 19    | N                | 32: START<br>33: FLUSH             | 70: RESRDY<br>71: WINMON                      | 44: RESRDY                      | Y               |

| AC                  | 0x42005000      | 27          |       |                     | 20    | N                   | 40                   | 20    | N                | 34-37:<br>SOC0-3                   | 72-75: COMP0-3<br>76-77: WIN0-1               |                                 | Y               |

| DAC                 | 0x42005400      | 28          |       |                     | 21    | N                   | 36                   | 21    | N                | 38: START                          | 78: EMPTY                                     | 45: EMPTY                       | Y               |

| PTC                 | 0x42005800      | 30          |       |                     | 22    | N                   | 37                   | 22    | N                | 39:<br>STCONV                      | 79: EOC<br>80: WCOMP                          | EOC: 46<br>WCOMP: 47<br>SEQ: 48 |                 |

|                     | 0x42005C00      |             | 10    | Y                   | 23    | N                   | 38                   | 23    | N                | 40-43 :<br>LUTIN0-3                | 81-84: LUTOUT0-3                              |                                 | Y               |

| AHB-APB<br>Bridge D | 0x43000000      |             | 13    | Y                   | 0     |                     |                      |       |                  |                                    |                                               |                                 | N/A             |

| SERCOM6             | 0x43000000      | 9           |       |                     | 0     | N                   | 41: CORE<br>18: SLOW | 0     | N                |                                    |                                               | 49: RX<br>50: TX                | Y               |

Name:

SYNCBUSY

Offset:

0x04

Reset:

0x0000000

Property:

–

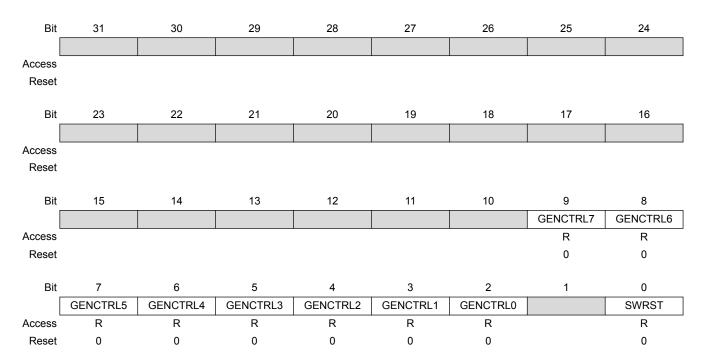

# Bits 2, 3, 4, 5, 6, 7, 8, 9 – GENCTRL: Generator Control n Synchronization Busy

This bit is cleared when the synchronization of the Generator Control n register (GENCTRLn) between clock domains is complete, or when clock switching operation is complete.

This bit is set when the synchronization of the Generator Control n register (GENCTRLn) between clock domains is started.

## Bit 0 – SWRST: Software Reset Synchronization Busy

This bit is cleared when the synchronization of the CTRLA.SWRST register bit between clock domains is complete.

This bit is set when the synchronization of the CTRLA.SWRST register bit between clock domains is started.

## 16.8.3 Generator Control

GENCTRLn controls the settings of Generic Generator n (n=0..8). The reset value is 0x00000106 for Generator n=0, else 0x00000000

Name:

GENCTRL0, GENCTRL1, GENCTRL2, GENCTRL3, GENCTRL4, GENCTRL5, GENCTRL6, GENCTRL7, GENCTRL8

Offset:

0x20 + n\*0x04 [n=0..8]

Reset:

0x00000106

Property: PAC Write-Protection, Write-Synchronized

| Offset | Name         | Bit Pos. |  |   |           |           |        |         |

|--------|--------------|----------|--|---|-----------|-----------|--------|---------|

| 0x2C   | DPLLSYNCBUSY | 7:0      |  |   | DPLLPRESC | DPLLRATIO | ENABLE |         |

| 0x2D   |              |          |  |   |           |           |        |         |

|        | Reserved     |          |  |   |           |           |        |         |

| 0x2F   |              |          |  |   |           |           |        |         |

| 0x30   | DPLLSTATUS   | 7:0      |  |   |           |           | CLKRDY | LOCK    |

| 0x31   |              |          |  |   |           |           |        |         |

|        | Reserved     |          |  |   |           |           |        |         |

| 0x37   |              |          |  |   |           |           |        |         |

| 0x38   |              | 7:0      |  |   | FCAI      | _[5:0]    |        |         |

| 0x39   |              | 15:8     |  |   |           |           | FRANC  | GE[1:0] |

| 0x3A   | CAL48M       | 23:16    |  | - | TCAI      | _[5:0]    |        |         |

| 0x3B   |              | 31:24    |  |   |           |           |        |         |

# 20.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Write-protection is denoted by the "PAC Write-Protection" property in each individual register description. Refer to the Register Access Protection section and the PAC - Peripheral Access Controller chapter for details.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" or "Write.Synchronized" property in each individual register description. Refer to the Synchronization section for details.

# 20.8.1 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x00 [ID-00001eee]Reset:0x00000000Property:PAC Write-Protection

When the Run in Standby bit in the VREG register (VREG.RUNSTDBY) is written to '1', VDDCORE is supplied by the main voltage regulator. The VDDCORE level is set to the active mode voltage level.

**Related Links**

Sleep Mode Controller

## 22.6.2 Voltage Reference System Operation

The reference voltages are generated by a functional block DETREF inside of the SUPC. DETREF is providing a fixed-voltage source, BANDGAP=1V, and a variable voltage, INTREF.

#### 22.6.2.1 Initialization

The voltage reference output and the temperature sensor are disabled after any Reset.

#### 22.6.2.2 Enabling, Disabling, and Resetting

The voltage reference output is enabled/disabled by setting/clearing the Voltage Reference Output Enable bit in the Voltage Reference register (VREF.VREFOE).

The temperature sensor is enabled/disabled by setting/clearing the Temperature Sensor Enable bit in the Voltage Reference register (VREF.TSEN).

**Note:** When VREF.ONDEMAND=0, it is not recommended to enable both voltage reference output and temperature sensor at the same time - only the voltage reference output will be present at both ADC inputs.

#### 22.6.2.3 Selecting a Voltage Reference

The Voltage Reference Selection bit field in the VREF register (VREF.SEL) selects the voltage of INTREF to be applied to analog modules, e.g. the ADC.

#### 22.6.2.4 Sleep Mode Operation

The Voltage Reference output and the Temperature Sensor output behavior during sleep mode can be configured using the Run in Standby bit and the On Demand bit in the Voltage Reference register (VREF.RUNSTDBY, VREF.ONDEMAND), see the following table:

#### Table 22-1. VREF Sleep Mode Operation

| VREF.ONDEMAND | VREF.RUNSTDBY | Voltage Reference Sleep behavior                                                         |

|---------------|---------------|------------------------------------------------------------------------------------------|

| -             | -             | Disable                                                                                  |

| 0             | 0             | Always run in all sleep modes except standby sleep mode                                  |

| 0             | 1             | Always run in all sleep modes including standby sleep mode                               |

| 1             | 0             | Only run if requested by the ADC, in all sleep modes <i>except</i> standby sleep mode    |

| 1             | 1             | Only run if requested by the ADC, in all sleep modes <i>including</i> standby sleep mode |

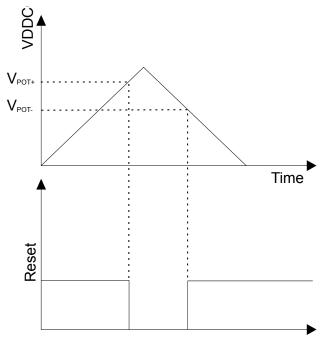

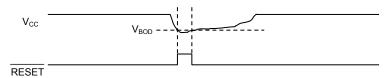

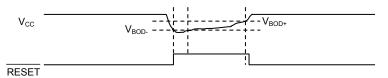

# 22.6.3 Brown-Out Detectors

#### 22.6.3.1 Initialization

Before a Brown-Out Detector (BODVDD) is enabled, it must be configured, as outlined by the following:

- Set the BOD threshold level (BODVDD.LEVEL)

- Set the configuration in active, standby (BODVDD.ACTCDG, BODVDD.STDBYCFG)

- Set the prescaling value if the BOD will run in sampling mode (BODVDD.PSEL)

- Set the action and hysteresis (BODVDD.ACTION and BODVDD.HYST)

| Bit    | 31  | 30  | 29  | 28   | 27      | 26  | 25  | 24  |

|--------|-----|-----|-----|------|---------|-----|-----|-----|

|        |     |     |     | COMP | [31:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 23  | 22  | 21  | 20   | 19      | 18  | 17  | 16  |

|        |     |     |     | COMP | [23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 15  | 14  | 13  | 12   | 11      | 10  | 9   | 8   |

|        |     |     |     | COMF | P[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

|        |     |     |     |      |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4    | 3       | 2   | 1   | 0   |

|        |     |     |     | COM  | P[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0       | 0   | 0   | 0   |

# Bits 31:0 – COMP[31:0]: Compare Value

The 32-bit value of COMP0 is continuously compared with the 32-bit COUNT value. When a match occurs, the Compare 0 interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.CMP0) is set on the next counter cycle, and the counter value is cleared if CTRLA.MATCHCLR is '1'.

| Bit    | 31           | 30   | 29      | 28  | 27      | 26 | 25       | 24 |  |  |  |

|--------|--------------|------|---------|-----|---------|----|----------|----|--|--|--|

|        | RWWEEP[11:4] |      |         |     |         |    |          |    |  |  |  |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |  |  |  |

| Reset  | 0            | 0    | 0       | 0   | 0       | 0  | 0        | 0  |  |  |  |

|        |              |      |         |     |         |    |          |    |  |  |  |

| Bit    | 23           | 22   | 21      | 20  | 19      | 18 | 17       | 16 |  |  |  |

|        |              | RWWE | EP[3:0] |     |         |    | PSZ[2:0] |    |  |  |  |

| Access | R            | R    | R       | R   |         | R  | R        | R  |  |  |  |

| Reset  | 0            | 0    | 0       | 0   |         | x  | х        | x  |  |  |  |

|        |              |      |         |     |         |    |          |    |  |  |  |

| Bit    | 15           | 14   | 13      | 12  | 11      | 10 | 9        | 8  |  |  |  |

|        |              |      |         | NVM | P[15:8] |    |          |    |  |  |  |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |  |  |  |

| Reset  | x            | x    | x       | x   | х       | х  | х        | х  |  |  |  |

|        |              |      |         |     |         |    |          |    |  |  |  |

| Bit    | 7            | 6    | 5       | 4   | 3       | 2  | 1        | 0  |  |  |  |

|        |              |      |         | NVM | P[7:0]  |    |          |    |  |  |  |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |  |  |  |

| Reset  | x            | x    | x       | x   | х       | x  | x        | x  |  |  |  |

#### Bits 31:20 – RWWEEP[11:0]: Read While Write EEPROM emulation area Pages

Indicates the number of pages in the RWW EEPROM emulation address space.

## Bits 18:16 – PSZ[2:0]: Page Size

Indicates the page size. Not all devices of the device families will provide all the page sizes indicated in the table.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | 8    | 8 bytes     |

| 0x1   | 16   | 16 bytes    |

| 0x2   | 32   | 32 bytes    |

| 0x3   | 64   | 64 bytes    |

| 0x4   | 128  | 128 bytes   |

| 0x5   | 256  | 256 bytes   |

| 0x6   | 512  | 512 bytes   |

| 0x7   | 1024 | 1024 bytes  |

#### Bits 15:0 – NVMP[15:0]: NVM Pages

Indicates the number of pages in the NVM main address space.

#### 27.8.4 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x0C [ID-0000b2c]Reset:0x00Property:PAC Write-Protection

# SAM C20/C21

| Offset | Name    | Bit Pos. |      |      |      |      |          |       |          |      |  |

|--------|---------|----------|------|------|------|------|----------|-------|----------|------|--|

| 0x17   |         | 31:24    |      |      |      |      | EVD11    | EVD10 | EVD9     | EVD9 |  |

| 0x18   |         | 7:0      | OVR7 | OVR6 | OVR5 | OVR4 | OVR3     | OVR2  | OVR1     | OVR0 |  |

| 0x19   | INTFLAG | 15:8     |      |      |      |      | OVR11    | OVR10 | OVR9     | OVR8 |  |

| 0x1A   |         | 23:16    | EVD7 | EVD6 | EVD5 | EVD4 | EVD3     | EVD2  | EVD1     | EVD0 |  |

| 0x1B   |         | 31:24    |      |      |      |      | EVD11    | EVD10 | EVD9     | EVD9 |  |

| 0x1C   |         | 7:0      |      |      |      | CHAN | NEL[7:0] |       |          |      |  |

| 0x1D   |         | 15:8     |      |      |      |      |          | CHANN | EL[11:8] |      |  |

| 0x1E   | SWEVT   | 23:16    |      |      |      |      |          |       |          |      |  |

| 0x1F   |         | 31:24    |      |      |      |      |          |       |          |      |  |

# 29.7.2 CHANNELn

| Offset           | Name      | Bit<br>Pos. |          |            |  |  |      |         |      |                |  |  |

|------------------|-----------|-------------|----------|------------|--|--|------|---------|------|----------------|--|--|

| 0x20 +<br>0x4*n  |           | 7:0         |          | EVGEN[7:0] |  |  |      |         |      |                |  |  |

| 0x4 11<br>0x21 + |           |             |          |            |  |  |      |         |      |                |  |  |

| 0x4*n            | CHANNELn  | 15:8        | ONDEMAND | RUNSTDBY   |  |  | EDGS | EL[1:0] | PATH | <b>I</b> [1:0] |  |  |

| 0x22 +           | CHANNEELI | 23:16       |          |            |  |  |      |         |      |                |  |  |

| 0x4*n            |           | 23.10       |          |            |  |  |      |         |      |                |  |  |

| 0x23 +           | 31:24     | 31.24       |          |            |  |  |      |         |      |                |  |  |

| 0x4*n            |           |             |          |            |  |  |      |         |      |                |  |  |

# 29.7.3 USERm

| Offset          | Name  | Bit<br>Pos. |  |       |          |  |  |

|-----------------|-------|-------------|--|-------|----------|--|--|

| 0x80 +<br>0x4*m | USERm | 7:0         |  | CHANN | IEL[7:0] |  |  |

| 0x81 +<br>0x4*m |       | 15:8        |  |       |          |  |  |

| 0x82 +<br>0x4*m |       | 23:16       |  |       |          |  |  |

| 0x83 +<br>0x4*m |       | 31:24       |  |       |          |  |  |

# 29.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Refer to Register Access Protection and PAC - Peripheral Access Controller.

## **Related Links**

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                            |

| 1     | The receiver is enabled or will be enabled when the USART is enabled. |

#### Bit 16 – TXEN: Transmitter Enable

Writing '0' to this bit will disable the USART transmitter. Disabling the transmitter will not become effective until ongoing and pending transmissions are completed.

Writing '1' to CTRLB.TXEN when the USART is disabled will set CTRLB.TXEN immediately. When the USART is enabled, CTRLB.TXEN will be cleared, and SYNCBUSY.CTRLB will be set and remain set until the transmitter is enabled. When the transmitter is enabled, CTRLB.TXEN will read back as '1'.

Writing '1' to CTRLB.TXEN when the USART is enabled will set SYNCBUSY.CTRLB, which will remain set until the transmitter is enabled, and CTRLB.TXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The transmitter is disabled or being enabled.                            |

| 1     | The transmitter is enabled or will be enabled when the USART is enabled. |

#### Bit 13 - PMODE: Parity Mode

This bit selects the type of parity used when parity is enabled (CTRLA.FORM is '1'). The transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The receiver will generate a parity value for the incoming data and parity bit, compare it to the parity mode and, if a mismatch is detected, STATUS.PERR will be set.

This bit is not synchronized.

| Value | Description  |

|-------|--------------|

| 0     | Even parity. |

| 1     | Odd parity.  |

# Bit 10 – ENC: Encoding Format

This bit selects the data encoding format.

This bit is not synchronized.

| Value | Description           |

|-------|-----------------------|

| 0     | Data is not encoded.  |

| 1     | Data is IrDA encoded. |

# **Bit 9 – SFDE: Start of Frame Detection Enable**

This bit controls whether the start-of-frame detector will wake up the device when a start bit is detected on the RxD line.

This bit is not synchronized.

| SFDE | INTENSET.RXS | INTENSET.RXC | Description                                                                     |

|------|--------------|--------------|---------------------------------------------------------------------------------|

| 0    | x            | Х            | Start-of-frame detection disabled.                                              |

| 1    | 0            | 0            | Reserved                                                                        |

| 1    | 0            | 1            | Start-of-frame detection enabled. RXC wakes up the device from all sleep modes. |

# 33.10 Register Description - I<sup>2</sup>C Master

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

# 33.10.1 Control A