#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g18a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

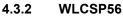

- DIGITAL PIN

- ANALOG PIN

- OSCILLATOR

- GROUND

- INPUT SUPPLY

- REGULATED OUTPUT SUPPLY

- RESET PIN

cleared or locked at the user discretion. A set of Interrupt Flag and Status registers informs the user on the status of the violation in the peripherals. In addition, slaves bus errors can be also reported in the cases where reserved area is accessed by the application.

# 11.5.2 Basic Operation

#### 11.5.2.1 Initialization

After reset, the PAC is enabled.

# 11.5.2.2 Initialization, Enabling and Resetting

The PAC is always enabled after reset.

Only a hardware reset will reset the PAC module.

#### 11.5.2.3 Operations

The PAC module allows the user to set, clear or lock the write protection status of all peripherals on all Peripheral Bridges.

If a peripheral register violation occurs, the Peripheral Interrupt Flag n registers (INTFLAGn) are updated to inform the user on the status of the violation in the peripherals connected to the Peripheral Bridge n (n = A,B,C ...). The corresponding Peripheral Write Control Status n register (STATUSn) gives the state of the write protection for all peripherals connected to the corresponding Peripheral Bridge n. Refer to the Peripheral Access Errors for details.

The PAC module also report the errors occurring at slave bus level when an access to reserved area is detected. AHB Slave Bus Interrupt Flag register (INTFLAGAHB) informs the user on the status of the violation in the corresponding slave. Refer to the AHB Slave Bus Errors for details.

#### 11.5.2.4 Peripheral Access Errors

The following events will generate a Peripheral Access Error:

- Protected write: To avoid unexpected writes to a peripheral's registers, each peripheral can be write

protected. Only the registers denoted as "PAC Write-Protection" in the module's datasheet can be

protected. If a peripheral is not write protected, write data accesses are performed normally. If a

peripheral is write protected and if a write access is attempted, data will not be written and

peripheral returns an access error. The corresponding interrupt flag bit in the INTFLAGn register

will be set.

- Illegal access: Access to an unimplemented register within the module.

- Synchronized write error: For write-synchronized registers an error will be reported if the register is written while a synchronization is ongoing.

When any of the INTFLAGn registers bit are set, an interrupt will be requested if the PAC interrupt enable bit is set.

#### 11.5.2.5 Write Access Protection Management

Peripheral access control can be enabled or disabled by writing to the WRCTRL register.

The data written to the WRCTRL register is composed of two fields; WRCTRL.PERID and WRCTRL.KEY. The WRCTRL.PERID is an unique identifier corresponding to a peripheral. The WRCTRL.KEY is a key value that defines the operation to be done on the control access bit. These operations can be "clear protection", "set protection" and "set and lock protection bit".

The "clear protection" operation will remove the write access protection for the peripheral selected by WRCTRL.PERID. Write accesses are allowed for the registers in this peripheral.

Frequencies must never exceed the specified maximum frequency for each clock domain.

| Value  | Name   | Description   |

|--------|--------|---------------|

| 0x01   | DIV1   | Divide by 1   |

| 0x02   | DIV2   | Divide by 2   |

| 0x04   | DIV4   | Divide by 4   |

| 0x08   | DIV8   | Divide by 8   |

| 0x10   | DIV16  | Divide by 16  |

| 0x20   | DIV32  | Divide by 32  |

| 0x40   | DIV64  | Divide by 64  |

| 0x80   | DIV128 | Divide by 128 |

| others | -      | Reserved      |

# 17.8.6 AHB Mask

**Note:** This register is only available for SAMC2x "N" series devices.

Name:AHBMASKOffset:0x10 [ID-00001086]Reset:0x000003CFFProperty:PAC Write-Protection

| Bit    | 31   | 30    | 29      | 28        | 27  | 26   | 25   | 24   |

|--------|------|-------|---------|-----------|-----|------|------|------|

|        |      |       |         |           |     |      |      |      |

| Access |      |       | R       | R         | R   | R    | R    | R    |

| Reset  |      |       | 0       | 0         | 0   | 0    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 23   | 22    | 21      | 20        | 19  | 18   | 17   | 16   |

|        |      |       |         |           |     |      |      |      |

| Access | R    | R     | R       | R         | R   | R    | R    | R    |

| Reset  | 0    | 0     | 0       | 0         | 0   | 0    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 15   | 14    | 13      | 12        | 11  | 10   | 9    | 8    |

|        |      |       |         |           |     | PAC  | CAN1 | CAN0 |

| Access | R    | R     | R       | R         | R   | R/W  | R/W  | R/W  |

| Reset  | 0    | 0     | 0       | 0         | 1   | 1    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 7    | 6     | 5       | 4         | 3   | 2    | 1    | 0    |

|        | DMAC | HSRAM | NVMCTRL | HMATRIXHS | DSU | APBC | APBB | APBA |

| Access | R/W  | R/W   | R/W     | R/W       | R/W | R/W  | R/W  | R/W  |

| Reset  | 1    | 1     | 1       | 1         | 1   | 1    | 1    | 1    |

# Bit 13 – APBD: APBD AHB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The AHB clock for the APBD is stopped. |

| 1     | The AHB clock for the APBD is enabled. |

# Bit 12 – DIVAS: DIVAS AHB Clock Enable

**CFDPRESC** Name: Offset: 0x12 **Reset:** 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1             | 0   |

|--------|---|---|---|---|---|-----|---------------|-----|

|        |   |   |   |   |   |     | CFDPRESC[2:0] |     |

| Access |   |   |   |   |   | R/W | R/W           | R/W |

| Reset  |   |   |   |   |   | 0   | 0             | 0   |

# Bits 2:0 – CFDPRESC[2:0]: Clock Failure Detector Prescaler

These bits select the prescaler for the clock failure detector.

The OSC48M oscillator is used to clock the CFD prescaler. The CFD safe clock frequency is the OSC48M frequency divided by 2<sup>^</sup>CFDPRESC.

#### 20.8.7 Event Control

**EVCTRL** Name: Offset: 0x13 Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | CFDEO |

| Access |   |   |   |   |   |   |   | R/W   |

| Reset  |   |   |   |   |   |   |   | 0     |

Reset

#### Bit 0 – CFDEO: Clock Failure Detector Event Output Enable

This bit indicates whether the Clock Failure detector event output is enabled or not and an output event will be generated when the Clock Failure detector detects a clock failure

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Clock Failure detector event output is disabled and no event will be generated. |

| 1     | Clock Failure detector event output is enabled and an event will be generated.  |

#### 20.8.8 48MHz Internal Oscillator (OSC48M) Control

Name: OSC48MCTRL Offset: 0x14 [ID-00001eee] **Reset:** 0x82 Property: PAC Write-Protection

| Bit    | 7        | 6        | 5 | 4 | 3 | 2 | 1      | 0 |

|--------|----------|----------|---|---|---|---|--------|---|

|        | ONDEMAND | RUNSTDBY |   |   |   |   | ENABLE |   |

| Access | R/W      | R/W      |   |   |   |   | R/W    |   |

| Reset  | 1        | 0        |   |   |   |   | 1      |   |

# Bit 7 – ONDEMAND: On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                                                                                                           |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock source. The oscillator is disabled if no peripheral is requesting the clock source. |

# Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the OSC48M behaves during standby sleep mode.

| Value | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OSC48M is disabled in standby sleep mode if no peripheral requests the clock.                                                                                          |

| 1     | The OSC48M is not stopped in standby sleep mode. If ONDEMAND=1, the OSC48M will be running when a peripheral is requesting the clock. If ONDEMAND=0, the clock source will |

|       | always be running in standby sleep mode.                                                                                                                                   |

# Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

# 20.8.9 OSC48M Divider

| Name:       | OSC48MDIV          |  |

|-------------|--------------------|--|

| Offset:     | 0x15 [ID-00001eee] |  |

| Reset:      | 0x0B               |  |

| Property: - |                    |  |

| Bit    | 7 | 6 | 5 | 4 | 3   | 2   | 1     | 0   |

|--------|---|---|---|---|-----|-----|-------|-----|

|        |   |   |   |   |     | DIV | [3:0] |     |

| Access |   |   |   |   | R/W | R/W | R/W   | R/W |

| Reset  |   |   |   |   | 1   | 0   | 1     | 1   |

# Bits 3:0 – DIV[3:0]: Oscillator Divider Selection

These bits control the oscillator frequency range by adjusting the division ratio. The oscillator frequency is 48MHz divided by DIV+1.

The BODVDD register is Enable-Protected, meaning that they can only be written when the BOD is disabled (BODVDD.ENABLE=0 and SYNCBUSY.BODVDDEN=0). As long as the Enable bit is '1', any writes to Enable-Protected registers will be discarded, and an APB error will be generated. The Enable bits are not Enable-Protected.

# 22.6.3.2 Enabling, Disabling, and Resetting

After power or user reset, the BODVDD and BODCORE register values are loaded from the NVM User Row.

The BODVDD is enabled by writing a '1' to the Enable bit in the BOD control register (BODVDD.ENABLE). The BOD is disabled by writing a '0' to the BODVDD.ENABLE.

# **Related Links**

NVM User Row Mapping

# 22.6.3.3 VDD Brown-Out Detector (BODVDD)

The VDD Brown-Out Detector (BODVDD) is able to monitor the VDD supply and compares the voltage with the brown-out threshold level set in the BODVDD Level field (BODVDD.LEVEL) in the BODVDD register.

When VDD crosses below the brown-out threshold level, the BODVDD can generate either an interrupt or a Reset, depending on the BODVDD Action bit field (BODVDD.ACTION).

The BODVDD detection status can be read from the BODVDD Detection bit in the Status register (STATUS.BODVDDDET).

At start-up or at Power-On Reset (POR), the BODVDD register values are loaded from the NVM User Row.

# **Related Links**

NVM User Row Mapping Brown Out Detectors Characteristics

#### 22.6.3.4 VDDCORE Brown-Out Detector (BODCORE)

The BODCORE is calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration must not be changed to assure the correct behavior of the BODCORE. The BODCORE generates a reset when VDDCORE crosses below the preset brown-out level. The BODCORE is always disabled in standby sleep mode.

#### **Related Links**

NVM User Row Mapping

#### 22.6.3.5 Continuous Mode

Continuous mode is the default mode for BODVDD.

The BODVDD is continuously monitoring the VDD supply voltage if it is enabled (BODVDD.ENABLE=1) and if the BODVDD Configuration bit in the BODVDD register is cleared (BODVDD.ACTCFG=0 for active mode, BODVDD.STDBYCFG=0 for standby mode).

#### 22.6.3.6 Sampling Mode

The Sampling Mode is a low-power mode where the BODVDD is being repeatedly enabled on a sampling clock's ticks. The BODVDD will monitor the supply voltage for a short period of time and then go to a low-power disabled state until the next sampling clock tick.

Sampling mode is enabled in Active mode for BODVDD by writing the ACTCFG bit (BODVDD.ACTCFG=1). Sampling mode is enabled in Standby mode by writing to the STDBYCFG bit

All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to the Nested Vector Interrupt Controller for details. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated. Refer to the Nested Vector Interrupt Controller for details.

# **Related Links**

Nested Vector Interrupt Controller

# 24.6.5 Events

The RTC can generate the following output events:

- Overflow (OVF): Generated when the counter has reached its top value and wrapped to zero.

- Compare (CMPn): Indicates a match between the counter value and the compare register.

- Alarm (ALARM): Indicates a match between the clock value and the alarm register.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to Periodic Intervals for details.

- Periodic Daily (PERD): Generated when the COUNT/CLOCK has incremented at a fixed period of time.

Setting the Event Output bit in the Event Control Register (EVCTRL.xxxEO=1) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the EVSYS - Event System for details on configuring the event system.

#### **Related Links**

EVSYS - Event System

# 24.6.6 Sleep Mode Operation

The RTC will continue to operate in any sleep mode where the source clock is active. The RTC *interrupts* can be used to wake up the device from a sleep mode. RTC *events* can trigger other operations in the system without exiting the sleep mode.

An interrupt request will be generated after the wake-up if the Interrupt Controller is configured accordingly. Otherwise the CPU will wake up directly, without triggering any interrupt. In this case, the CPU will continue executing right from the first instruction that followed the entry into sleep.

#### 24.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register, CTRLA.SWRST

- Enable bit in Control A register, CTRLA.ENABLE

The following registers are synchronized when written:

- Counter Value register, COUNT

- Clock Value register, CLOCK

- Counter Period register, PER

- Compare n Value registers, COMPn

- Alarm n Value registers, ALARMn

- Frequency Correction register, FREQCORR

Writing a '1' to this bit when both the DMAC and the CRC module are disabled (DMAENABLE and CRCENABLE are '0') resets all registers in the DMAC (except DBGCTRL) to their initial state. If either the DMAC or CRC module is enabled, the Reset request will be ignored and the DMAC will return an access error.

| Value | Description                          |  |

|-------|--------------------------------------|--|

| 0     | There is no Reset operation ongoing. |  |

| 1     | A Reset operation is ongoing.        |  |

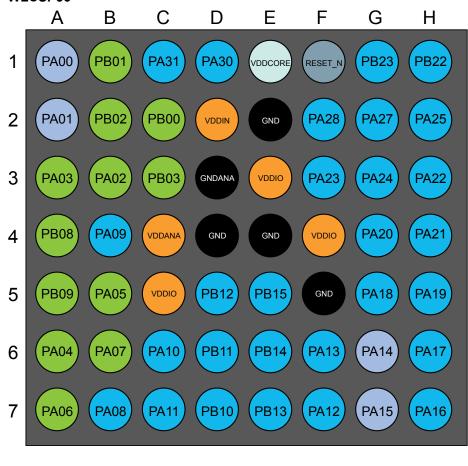

# 25.8.2 CRC Control

| Name:     | CRCCTRL                                |

|-----------|----------------------------------------|

| Offset:   | 0x02 [ID-00001ece]                     |

| Reset:    | 0x0000                                 |

| Property: | PAC Write-Protection, Enable-Protected |

# Bits 13:8 – CRCSRC[5:0]: CRC Input Source

These bits select the input source for generating the CRC, as shown in the table below. The selected source is locked until either the CRC generation is completed or the CRC module is disabled. This means the CRCSRC cannot be modified when the CRC operation is ongoing. The lock is signaled by the CRCBUSY status bit. CRC generation complete is generated and signaled from the selected source when used with the DMA channel.

| Value         | Name  | Description    |

|---------------|-------|----------------|

| 0x00          | NOACT | No action      |

| 0x01          | IO    | I/O interface  |

| 0x02-0x1<br>F | -     | Reserved       |

| 0x20          | CHN   | DMA channel 0  |

| 0x21          | CHN   | DMA channel 1  |

| 0x22          | CHN   | DMA channel 2  |

| 0x23          | CHN   | DMA channel 3  |

| 0x24          | CHN   | DMA channel 4  |

| 0x25          | CHN   | DMA channel 5  |

| 0x26          | CHN   | DMA channel 6  |

| 0x27          | CHN   | DMA channel 7  |

| 0x28          | CHN   | DMA channel 8  |

| 0x29          | CHN   | DMA channel 9  |

| 0x2A          | CHN   | DMA channel 10 |

| Value | Description                                                   |  |

|-------|---------------------------------------------------------------|--|

| 0     | The PMUXn registers of the selected pins will not be updated. |  |

| 1     | The PMUXn registers of the selected pins will be updated.     |  |

# Bits 27:24 – PMUX[3:0]: Peripheral Multiplexing

These bits determine the new value written to the Peripheral Multiplexing register (PMUXn) for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPMUX bit is set.

These bits will always read as zero.

#### Bit 22 – DRVSTR: Output Driver Strength Selection

This bit determines the new value written to PINCFGy.DRVSTR for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 18 – PULLEN: Pull Enable

This bit determines the new value written to PINCFGy.PULLEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 17 – INEN: Input Enable

This bit determines the new value written to PINCFGy.INEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bit 16 – PMUXEN: Peripheral Multiplexer Enable

This bit determines the new value written to PINCFGy.PMUXEN for all pins selected by the WRCONFIG.PINMASK and WRCONFIG.HWSEL bits, when the WRCONFIG.WRPINCFG bit is set.

This bit will always read as zero.

#### Bits 15:0 – PINMASK[15:0]: Pin Mask for Multiple Pin Configuration

These bits select the pins to be configured within the half-word group selected by the WRCONFIG.HWSEL bit.

These bits will always read as zero.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | The configuration of the corresponding I/O pin in the half-word group will be left unchanged. |

| 1     | The configuration of the corresponding I/O pin in the half-word PORT group will be updated.   |

#### 28.9.12 Event Input Control

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

# 30. SERCOM – Serial Communication Interface

# 30.1 Overview

There are up to eight instances of the serial communication interface (SERCOM) peripheral.

A SERCOM can be configured to support a number of modes: I<sup>2</sup>C, SPI, and USART. When SERCOM is configured and enabled, all SERCOM resources will be dedicated to the selected mode.

The SERCOM serial engine consists of a transmitter and receiver, baud-rate generator and address matching functionality. It can use the internal generic clock or an external clock to operate in all sleep modes.

# **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

# 30.2 Features

- Interface for configuring into one of the following:

- Inter-Integrated Circuit (I<sup>2</sup>C) Two-wire Serial Interface

- System Management Bus (SMBus<sup>™</sup>) compatible

- Serial Peripheral Interface (SPI)

- Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

- Single transmit buffer and double receive buffer

- Baud-rate generator

- Address match/mask logic

- Operational in all Sleep modes with an external clock source

- Can be used with DMA

See the Related Links for full feature lists of the interface configurations.

# **Related Links**

SERCOM USART – SERCOM Universal Synchronous and Asynchronous Receiver and Transmitter SERCOM SPI – SERCOM Serial Peripheral Interface SERCOM I2C – SERCOM Inter-Integrated Circuit

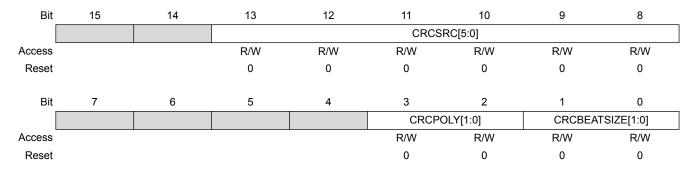

# 34.8.19 Interrupt Line Enable

# Bits 1:0 – EINTn: Enable Interrupt Line n [n = 1,0]

| Value | Description                    |  |

|-------|--------------------------------|--|

| 0     | CAN interrupt line n disabled. |  |

| 1     | CAN interrupt line n enabled.  |  |

# 34.8.20 Global Filter Configuration

This register is write-restricted and only writable if bit fields CCCR.CCE = 1 and CCCR.INIT = 1.

Name:GFCOffset:0x80 [ID-0000a4bb]Reset:0x00000000Property:Write-restricted

| Value | Description         |

|-------|---------------------|

| 0     | Tx FIFO operation.  |

| 1     | Tx Queue operation. |

#### Bits 29:24 – TFQS[5:0]: Transmit FIFO/Queue Size

| Value  | Description                                   |  |

|--------|-----------------------------------------------|--|

| 0      | No Tx FIFO/Queue.                             |  |

| 1 - 32 | Number of Tx Buffers used for Tx FIFO/Queue.  |  |

| >32    | Values greater than 32 are interpreted as 32. |  |

# Bits 21:16 – NDTB[5:0]: Number of Dedicated Transmit Buffers

| Value  | Description                                   |  |  |

|--------|-----------------------------------------------|--|--|

| 0      | No Tx FIFO/Queue.                             |  |  |

| 1 - 32 | Number of Tx Buffers used for Tx FIFO/Queue.  |  |  |

| >32    | Values greater than 32 are interpreted as 32. |  |  |

# Bits 15:0 – TBSA[15:0]: Tx Buffers Start Address

Start address of Tx Buffers section in Message RAM. When the CAN module addresses the Message RAM it addresses 32-bit words, not single bytes. The configurable start addresses are 32-bit word addresses, i.e. only bits 15 to 2 are evaluated, the two least significant bits are ignored. Bits 1 to 0 will always be read back as "00".

#### 34.8.36 Tx FIFO/Queue Status

**Note:** In case of mixed configurations where dedicated Tx Buffers are combined with a Tx FIFO or a Tx Queue, the Put and Get Indexes indicate the number of the Tx Buffer starting with the first dedicated Tx Buffers. Example: For a configuration of 12 dedicated Tx Buffers and a Tx FIFO of 20 Buffers a Put Index of 15 points to the fourth buffer of the Tx FIFO.

Name:TXFQSOffset:0xC4 [ID-0000a4bb]Reset:0x00000000Property:Read-only

These bits are not synchronized.

| Value | Name   | Description                                                                    |

|-------|--------|--------------------------------------------------------------------------------|

| 0x0   | GCLK   | Reload or reset the counter on next generic clock                              |

| 0x1   | PRESC  | Reload or reset the counter on next prescaler clock                            |

| 0x2   | RESYNC | Reload or reset the counter on next generic clock. Reset the prescaler counter |

| 0x3   | -      | Reserved                                                                       |

# Bits 3:2 – MODE[1:0]: Timer Counter Mode

These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

# Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 35.7.1.2 Control B Clear

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

| Bit    | 31      | 30       | 29       | 28     | 27       | 26       | 25       | 24       |

|--------|---------|----------|----------|--------|----------|----------|----------|----------|

|        |         |          |          |        | CMPx     | CMPx     | CMPx     | CMPx     |

| Access |         |          |          |        | R        | R        | R        | R        |

| Reset  |         |          |          |        | 0        | 0        | 0        | 0        |

|        |         |          |          |        |          |          |          |          |

| Bit    | 23      | 22       | 21       | 20     | 19       | 18       | 17       | 16       |

|        |         |          |          |        | CCBUFVx  | CCBUFVx  | CCBUFVx  | CCBUFVx  |

| Access |         |          |          |        | R/W      | R/W      | R/W      | R/W      |

| Reset  |         |          |          |        | 0        | 0        | 0        | 0        |

|        |         |          |          |        |          |          |          |          |

| Bit    | 15      | 14       | 13       | 12     | 11       | 10       | 9        | 8        |

|        | FAULTx  | FAULTx   | FAULTB   | FAULTA | FAULT1IN | FAULT0IN | FAULTBIN | FAULTAIN |

| Access | R/W     | R/W      | R/W      | R/W    | R        | R        | R        | R        |

| Reset  | 0       | 0        | 0        | 0      | 0        | 0        | 0        | 0        |

|        |         |          |          |        |          |          |          |          |

| Bit    | 7       | 6        | 5        | 4      | 3        | 2        | 1        | 0        |

|        | PERBUFV | WAVEBUFV | PATTBUFV | SLAVE  | DFS      | UFS      | IDX      | STOP     |

| Access | R/W     | R/W      | R/W      | R      | R/W      | R/W      | R        | R        |

| Reset  | 0       | 0        | 0        | 0      | 0        | 0        | 0        | 1        |

# Bits 27,26,25,24 – CMPx: Channel x Compare Value

This bit reflects the channel x output compare value.

| Value | Description                        |

|-------|------------------------------------|

| 0     | Channel compare output value is 0. |

| 1     | Channel compare output value is 1. |

# Bits 19,18,17,16 – CCBUFVx: Channel x Compare or Capture Buffer Valid

For a compare channel, this bit is set when a new value is written to the corresponding CCBUFx register. The bit is cleared either by writing a '1' to the corresponding location when CTRLB.LUPD is set, or automatically on an UPDATE condition.

For a capture channel, the bit is set when a valid capture value is stored in the CCBUFx register. The bit is automatically cleared when the CCx register is read.

#### Bits 15,14 – FAULTx: Non-recoverable Fault x State

This bit is set by hardware as soon as non-recoverable Fault x condition occurs.

This bit is cleared by writing a one to this bit and when the corresponding FAULTxIN status bit is low.

Once this bit is clear, the timer/counter will restart from the last COUNT value. To restart the timer/counter from BOTTOM, the timer/counter restart command must be executed before clearing the corresponding STATEx bit. For further details on timer/counter commands, refer to available commands description (CTRLBSET.CMD).

# Bit 13 – FAULTB: Recoverable Fault B State

This bit is set by hardware as soon as recoverable Fault B condition occurs.

This bit can be clear by hardware when Fault B action is resumed, or by writing a '1' to this bit when the corresponding FAULTBIN bit is low. If software halt command is enabled (FAULTB.HALT=SW), clearing this bit will release the timer/counter.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Reference buffer offset compensation is disabled. |

| 1     | Reference buffer offset compensation is enabled.  |

#### Bits 3:0 – REFSEL[3:0]: Reference Selection

These bits select the reference for the ADC.

| Value     | Name    | Description                         |

|-----------|---------|-------------------------------------|

| 0x0       | INTREF  | internal reference voltage          |

| x01       | INTVCC0 | 1/1.6 VDDANA                        |

| 0x2       | INTVCC1 | 1/2 VDDANA (only for VDDANA > 4.0V) |

| 0x3       | VREFA   | External reference                  |

| 0x4       | DAC     | DAC internal output                 |

| 0x5       | INTVCC2 | VDDANA                              |

| 0x6 - 0xF |         | Reserved                            |

# 38.8.4 Event Control

Name:EVCTRLOffset:0x03 [ID-0000120e]Reset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5        | 4        | 3        | 2        | 1       | 0       |

|--------|---|---|----------|----------|----------|----------|---------|---------|

|        |   |   | WINMONEO | RESRDYEO | STARTINV | FLUSHINV | STARTEI | FLUSHEI |

| Access |   |   | R/W      | R/W      | R/W      | R/W      | R/W     | R/W     |

| Reset  |   |   | 0        | 0        | 0        | 0        | 0       | 0       |

# Bit 5 – WINMONEO: Window Monitor Event Out

This bit indicates whether the Window Monitor event output is enabled or not and an output event will be generated when the window monitor detects something.

| Value | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| 0     | Window Monitor event output is disabled and an event will not be generated. |

| 1     | Window Monitor event output is enabled and an event will be generated.      |

#### Bit 4 – RESRDYEO: Result Ready Event Out

This bit indicates whether the Result Ready event output is enabled or not and an output event will be generated when the conversion result is available.

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | Result Ready event output is disabled and an event will not be generated. |

| 1     | Result Ready event output is enabled and an event will be generated.      |

# Bit 3 – STARTINV: Start Conversion Event Invert Enable

For the slave ADC, this bit has no effect when the SLAVEEN bit is set (CTRLA.SLAVEEN= 1).

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | Start event input source is not inverted. |

| 1     | Start event input source is inverted.     |

# Bit 2 – INPUTCTRL: Input Control Synchronization Busy

This bit is cleared when the synchronization of INPUTCTRL register between the clock domains is complete.

This bit is set when the synchronization of INPUTCTRL register between clock domains is started.

# Bit 1 – ENABLE: ENABLE Synchronization Busy

This bit is cleared when the synchronization of ENABLE register between the clock domains is complete.

This bit is set when the synchronization of ENABLE register between clock domains is started.

# Bit 0 – SWRST: SWRST Synchronization Busy

This bit is cleared when the synchronization of SWRST register between the clock domains is complete.

This bit is set when the synchronization of SWRST register between clock domains is started

# 38.8.20 Result

Name:

RESULT

Offset:

0x24 [ID-0000120e]

Reset:

0x0000

Property:

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9 | 8 |

|--------|----|----|----|-------|----------|----|---|---|

|        |    |    |    | RESUL | _T[15:8] |    |   |   |

| Access | R  | R  | R  | R     | R        | R  | R | R |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0 | 0 |

|        |    |    |    |       |          |    |   |   |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1 | 0 |

|        |    |    |    | RESU  | LT[7:0]  |    |   |   |

| Access | R  | R  | R  | R     | R        | R  | R | R |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0 | 0 |

# Bits 15:0 – RESULT[15:0]: Result Conversion Value

These bits will hold up to a 16-bit ADC conversion result, depending on the configuration.

In single conversion mode without averaging, the ADC conversion will produce a 12-bit result, which can be left- or right-shifted, depending on the setting of CTRLC.LEFTADJ.

If the result is left-adjusted (CTRLC.LEFTADJ), the high byte of the result will be in bit position [15:8], while the remaining 4 bits of the result will be placed in bit locations [7:4]. This can be used only if an 8-bit result is needed; i.e., one can read only the high byte of the entire 16-bit register.

If the result is not left-adjusted (CTRLC.LEFTADJ) and no oversampling is used, the result will be available in bit locations [11:0], and the result is then 12 bits long. If oversampling is used, the result will be located in bit locations [15:0], depending on the settings of the Average Control register.

#### 38.8.21 Sequence Control

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

# 43.8.2 Control B

| Name:     | CTRLB              |

|-----------|--------------------|

| Offset:   | 0x01 [ID-00001f13] |

| Reset:    | 0x00               |

| Property: | -                  |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | START |

| Access |   |   |   |   | - |   |   | W     |

| Reset  |   |   |   |   |   |   |   | 0     |

# Bit 0 – START: Start Measurement

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Writing a zero to this bit has no effect.      |

| 1     | Writing a one to this bit starts a measurement |

#### 43.8.3 Control C

| Name:    | CTRLC                                    |

|----------|------------------------------------------|

| Offset:  | 0x02 [ID-00001f13]                       |

| Reset:   | 0x00                                     |

| Property | : PAC Write-Protection, Enable-protected |

| Bit    | 7 | 6 | 5 | 4       | 3 | 2   | 1            | 0   |

|--------|---|---|---|---------|---|-----|--------------|-----|

|        |   |   |   | FREERUN |   |     | WINMODE[2:0] |     |

| Access |   |   |   | R/W     |   | R/W | R/W          | R/W |

| Reset  |   |   |   | 0       |   | 0   | 0            | 0   |

#### Bit 4 – FREERUN: Free Running Measurement

| Value | Description                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------|

| 0     | TSENS operates in single measurement mode.                                                                     |

| 1     | TSENS is in free running mode and a new measurement will be initiated when the previous measurement completes. |

# Bits 2:0 – WINMODE[2:0]: Window Monitor Mode

These bits enable and define the window monitor mode.

# 45. Electrical Characteristics 85°C (SAM C20/C21 E/G/J)

# **Related Links**

Electrical Characteristics 105°C (SAM C20/C21 E/G/J)

# 45.1 Disclaimer

All typical values are measured at Ta = 25°C unless otherwise specified. All minimum and maximum values are valid across operating temperature and voltage unless otherwise specified.

This chapter only contains characteristics specific for SAM C20/C21 E/G/J.

# 45.2 Absolute Maximum Ratings

Stresses beyond those listed in the below table may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Table 45-1. Absolute maximum ratings

| Symbol               | Parameter                                           | Min.     | Max.                  | Units |

|----------------------|-----------------------------------------------------|----------|-----------------------|-------|

| V <sub>DD</sub>      | Power supply voltage                                | 0        | 6.1                   | V     |

| I <sub>VDD</sub>     | Current into a V <sub>DD</sub> pin                  | -        | 92                    | mA    |

| I <sub>GND</sub>     | Current out of a GND pin                            | -        | 130                   | mA    |

| V <sub>PIN</sub>     | Pin voltage with respect to GND and $V_{\text{DD}}$ | GND-0.6V | V <sub>DD</sub> +0.6V | V     |

| T <sub>STORAGE</sub> | Storage temperature                                 | -60      | 150                   | °C    |

**Caution:** This device is sensitive to electrostatic discharges (ESD). Improper handling may lead to permanent performance degradation or malfunctioning.

Handle the device following best practice ESD protection rules: Be aware that the human body can accumulate charges large enough to impair functionality or destroy the device.

**Caution:** In debugger cold-plugging mode, NVM erase operations are not protected by the BODVDD and BODCORE. NVM erase operation at supply voltages below specified minimum can cause corruption of NVM areas that are mandatory for correct device behavior.

# **Related Links**

**GPIO Clusters**

# 45.3 General Operating Ratings

The device must operate within the ratings listed in the table below in order for all other electrical characteristics and typical characteristics of the device to be valid.

| Symbol | Parameter                  | Conditions           | Conditions |        |        | Units |

|--------|----------------------------|----------------------|------------|--------|--------|-------|

|        |                            |                      | VDD = 5.5V | +/-1.5 | +/-3.5 |       |

| DNL    | Differential non-linearity | VREF= Ext 2.0V       | VDD = 2.7V | +/-0.3 | +/-2.3 | LSB   |

|        |                            |                      | VDD = 5.5V | +/-0.4 | +/-2.2 |       |

|        | Gain error                 | VREF = VDDANA        | VDD = 2.7V | +/-0.2 | +/-2.1 |       |

|        |                            |                      | VDD = 5.5V | +/-0.2 | +/-2.1 |       |

|        |                            | VREF= 1.024V INT REF | VDD = 2.7V | +/-1.0 | +/-2.5 |       |

|        |                            |                      | VDD = 5.5V | +/-1.4 | +/-3.5 |       |

|        |                            | Ext. VREF            |            | +/-8   | +/-28  | mV    |

|        | Offset error               | Ext. VREF            |            | +/-4   | +/-26  | mV    |

1. These values are based on characterization. These values are not covered by test limits in production.

# 47.4.6 Analog Comparator Characteristics Table 47-15. Analog Comparator Characteristics

| Symbol                             | Parameters                                                              | Conditions                          | Min | Тур   | Мах    | Unit |

|------------------------------------|-------------------------------------------------------------------------|-------------------------------------|-----|-------|--------|------|

| PNIVR                              | Positive and Negative input range voltage                               |                                     | 0   | -     | VDDANA | V    |

| ICMR                               | Input common mode range                                                 |                                     | 0   | -     | VDDANA | V    |

| Off <sup>(1)(2)</sup>              | Offset                                                                  | Low power<br>COMPCTRLn.SPEED = 0x0  | -55 | -4/+2 | 51     | mV   |

|                                    |                                                                         | High speed<br>COMPCTRLn.SPEED = 0x3 | -22 | -2/+1 | 20     |      |

| V <sub>HYS</sub> <sup>(1)(3)</sup> | Hysteresis                                                              | High speed<br>COMPCTRLn.SPEED = 0x3 | 39  | 106   | 156    | mV   |

| T <sub>PD</sub> <sup>(1)</sup>     | Propagation Delay<br>Vcm=Vddana/2<br>Vin = ±100mV overdrive from<br>Vcm | Low power<br>COMPCTRLn.SPEED = 0x0  | -   | 149   | 268    | ns   |

|                                    |                                                                         | High speed<br>COMPCTRLn.SPEED =0x3  | -   | 41    | 73     |      |

| T <sub>START</sub> <sup>(1)</sup>  | Startup time                                                            | Low power<br>COMPCTRLn.SPEED = 0x0  | -   | 6.8   | 10.4   | μs   |

|                                    |                                                                         | High speed<br>COMPCTRLn.SPEED = 0x3 | -   | 2.2   | 3.7    |      |

| $V_{\text{SCALE}}{}^{(1)}$         | INL                                                                     |                                     | -   | 0.569 | -      | LSB  |

|                                    | DNL                                                                     |                                     | -   | 0.053 | -      |      |

# The Microchip Web Site

Microchip provides online support via our web site at http://www.microchip.com/. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Customer Change Notification Service**

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at http://www.microchip.com/. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support