Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20g18a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6. I/O Multiplexing and Considerations

# 6.1 Multiplexed Signals

Each pin is by default controlled by the PORT as a general purpose I/O and alternatively it can be assigned to one of the peripheral functions A, B, C, D, E, F, G, H, or I. To enable a peripheral function on a pin, the Peripheral Multiplexer Enable bit in the Pin Configuration register corresponding to that pin (PINCFGn.PMUXEN, n = 0.31) in the PORT must be written to one. The selection of peripheral function A to H is done by writing to the Peripheral Multiplexing Odd and Even bits in the Peripheral Multiplexing register (PMUXn.PMUXE/O) in the PORT.

| Pin      | I/O Pin      | Supply     | A                        |             | в       | •       |        | B(1)(2) | _                                       |      | с               | D                                | E          | F           | G                                        | н                        |             |

|----------|--------------|------------|--------------------------|-------------|---------|---------|--------|---------|-----------------------------------------|------|-----------------|----------------------------------|------------|-------------|------------------------------------------|--------------------------|-------------|

|          |              | Cappij     | EIC                      | REF         | ADC0    | ADC1    | SDADC  |         | РТС                                     | DAC  | SERCOM          | SERCOM-ALT                       | тс         | тсс         | СОМ                                      | AC/GCLK                  | CCL         |

| 1        | PA00         |            | EXTINT[0]                |             | ADOU    | ABOT    | ODADO  | 70      |                                         | DAG  |                 | SERCOM1/PAD[0]                   |            | 100         | 0011                                     | CMP[2]                   | UUL         |

| 2        |              |            | EXTINT[1]                |             |         |         |        |         |                                         |      |                 | SERCOM1/PAD[1]                   |            |             |                                          | CMP[3]                   |             |

| 3        | PC00         |            | EXTINT[8]                |             | AIN[8]  |         |        |         |                                         |      |                 | OEROOMIN AD[1]                   | 102/110[1] |             |                                          | Oldin [0]                |             |

| 4        |              |            | EXTINT[9]                |             | AIN[9]  |         |        |         |                                         |      |                 |                                  |            |             |                                          |                          |             |

| 5        | PC02         |            | EXTINT[10]               |             | AIN[10] | 1       |        |         |                                         |      |                 |                                  |            |             |                                          |                          |             |

| 6        | PC03         |            | EXTINT[11]               |             | AIN[11] |         |        |         |                                         |      | SERCOM7/PAD[0]  |                                  |            | TCC2/WO[0]  |                                          |                          |             |

| 7        | PA02         |            | EXTINT[2]                |             | AIN[0]  |         |        | AIN[4]  | Y[0]                                    | VOUT | OEROOMINI AD[0] |                                  |            | 1002/110[0] |                                          |                          |             |

| 8        | PA03         |            | EXTINT[2]                | ADC/VREFA   | AIN[1]  |         |        | 7414[4] | Y[1]                                    | 1001 |                 |                                  |            |             |                                          |                          |             |

| Ū        | 17100        | V D D A WA | Extintio                 | DAC/VREFB   | Andri   |         |        |         | .[.]                                    |      |                 |                                  |            |             |                                          |                          |             |

| 9        | PB04         | VDDANA     | EXTINT[4]                |             |         | AIN[6]  |        | AIN[5]  | Y[10]                                   |      |                 |                                  |            |             |                                          |                          |             |

| 10       | PB05         | VDDANA     | EXTINT[5]                |             |         | AIN[7]  |        | AIN[6]  | Y[11]                                   |      |                 |                                  |            |             |                                          |                          |             |

| 13       | PB06         | VDDIO      | EXTINT[6]                |             |         | AIN[8]  | INN[2] | AIN[7]  | Y[12]                                   |      | SERCOM7/PAD[1]  |                                  |            |             |                                          |                          | CCL2/IN[6]  |

| 14       | PB07         | VDDIO      | EXTINT[7]                |             |         | AIN[9]  | INP[2] |         | Y[13]                                   |      | SERCOM7/PAD[3]  | SERCOM7/PAD[2]                   |            |             |                                          |                          | CCL2/IN[7]  |

| 15       | PB08         | VDDIO      | EXTINT[8]                |             | AIN[2]  | AIN[4]  | INN[1] |         | Y[14]                                   |      | SERCOM7/PAD[2]  | SERCOM7/PAD[3]                   | TC4/WO[0]  |             |                                          |                          | CCL2/IN[8]  |

| 16       | PB09         | VDDANA     | EXTINT[9]                |             | AIN[3]  | AIN[5]  | INP[1] |         | Y[15]                                   |      |                 | SERCOM4/PAD[1]                   | TC4/WO[1]  |             |                                          |                          | CCL2/OUT[2] |

| 17       | PA04         | VDDANA     | EXTINT[4]                | SDADC/VREFB | AIN[4]  |         |        | AIN[0]  | Y[2]                                    |      |                 | SERCOM0/PAD[0]                   | TC0/WO[0]  |             |                                          |                          | CCL0/IN[0]  |

| 18       | PA05         | VDDANA     | EXTINT[5]                |             | AIN[5]  |         |        | AIN[1]  | Y[3]                                    |      |                 | SERCOM0/PAD[1]                   | TC0/WO[1]  |             |                                          |                          | CCL0/IN[1]  |

| 19       | PA06         | VDDANA     | EXTINT[6]                |             | AIN[6]  |         | INN[0] | AIN[2]  | Y[4]                                    |      |                 | SERCOM0/PAD[2]                   | TC1/WO[0]  |             |                                          |                          | CCL0/IN[2]  |

| 20       | PA07         | VDDANA     | EXTINT[7]                |             | AIN[7]  |         | INP[0] | AIN[3]  | Y[5]                                    |      |                 | SERCOM0/PAD[3]                   | TC1/WO[1]  |             |                                          |                          | CCL0/OUT[0] |

| 21       | PC05         | VDDANA     | EXTINT[13]               |             |         |         |        |         |                                         |      | SERCOM6/PAD[3]  |                                  |            | TCC2/WO[1]  |                                          |                          |             |

| 22       | PC06         | VDDANA     | EXTINT[14]               |             |         |         |        |         |                                         |      | SERCOM6/PAD[0]  |                                  |            |             |                                          |                          |             |

| 23       | PC07         | VDDANA     | EXTINT[15]               |             |         |         |        |         |                                         |      | SERCOM6/PAD[1]  |                                  |            |             |                                          |                          |             |

| 26       | PA08         | VDDIO      | NMI                      |             |         | AIN[10] |        |         | X[0]/Y[16]                              |      | SERCOM0/PAD[0]  | SERCOM2/PAD[0]                   | TC0/WO[0]  | TCC0/WO[0]  |                                          |                          | CCL1/IN[3]  |

| 27       | PA09         | VDDIO      | EXTINT[9]                |             |         | AIN[11] |        |         | X[1]/Y[17]                              |      | SERCOM0/PAD[1]  |                                  |            |             |                                          |                          | CCL1/IN[4]  |

| 28       | PA10         |            | EXTINT[10]               |             |         |         |        |         | X[2]/Y[18]                              |      |                 | SERCOM2/PAD[2]                   |            |             |                                          | GCLK_IO[4]               |             |

| 29       | PA11         | VDDIO      | EXTINT[11]               |             |         | -       |        |         | X[3]/Y[19]                              |      |                 | SERCOM2/PAD[3]                   |            |             |                                          |                          | CCL1/OUT[1] |

| 30       | PB10         |            | EXTINT[10]               |             |         |         |        |         | 1.1 1.1                                 |      |                 | SERCOM4/PAD[2]                   |            | TCC0_WO4    |                                          | GCLK_IO[4]               |             |

| 31       | PB11         | VDDIO      | EXTINT[11]               |             |         | -       |        |         |                                         |      |                 |                                  |            | TCC0_WO5    |                                          |                          | CCL1/OUT[1] |

| 32       | PB12         |            | EXTINT[12]               |             |         |         |        |         | X[12]/Y[28]                             |      | SERCOM4/PAD[0]  |                                  |            | TCC0_WO6    | CAN1/TX                                  | GCLK_IO[6]               |             |

| 33       | PB13         | VDDIO      | EXTINT[13]               |             |         |         |        |         | X[13]/Y[29]                             |      | SERCOM4/PAD[1]  |                                  | TC4/WO[1]  | _           | CAN1/RX                                  | GCLK_IO[7]               |             |

| 34       | PB14         |            | EXTINT[14]               |             |         |         |        |         | X[14]/Y[30]                             |      | SERCOM4/PAD[2]  |                                  | TC5/WO[0]  |             | CAN1/TX                                  | GCLK_IO[0]               |             |

| 35       | PB15         | VDDIO      | EXTINT[15]               |             |         |         |        |         | X[15]/Y[31]                             |      | SERCOM4/PAD[3]  |                                  | TC5/WO[1]  |             | CAN1/RX                                  |                          | CCL3/IN[10] |

| 38       | PC08         | VDDIO      | EXTINT[0]                |             |         |         |        |         | ,,(,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      | .,              | SERCOM7/PAD[0]                   | 100/110[1] |             | o, u i i i i i i i i i i i i i i i i i i | 0021(_10[1]              | 0020/11[10] |

| 39       | PC09         | VDDIO      | EXTINT[1]                |             |         | -       | -      |         |                                         |      | SERCOM6/PAD[1]  |                                  |            |             |                                          |                          |             |

| 40       | PC10         | VDDIO      | EXTINT[2]                |             |         |         |        |         |                                         |      | SERCOM6/PAD[2]  |                                  |            |             |                                          |                          |             |

| 40       | PC11         | VDDIO      | EXTINT[2]                |             |         |         |        |         |                                         |      |                 | SERCOM7/PAD[3]                   |            |             |                                          |                          |             |

| 42       | PC12         | VDDIO      | EXTINT[4]                |             |         |         |        |         |                                         |      | SERCOM7/PAD[0]  | 02.000111110[0]                  |            |             |                                          |                          |             |

| 42       | PC12<br>PC13 | VDDIO      | EXTINT[4]                |             |         |         |        |         |                                         |      | SERCOM7/PAD[1]  |                                  |            |             |                                          |                          |             |

| 43       | PC14         | VDDIO      | EXTINT[6]                |             |         |         |        |         |                                         |      | SERCOM7/PAD[1]  |                                  |            |             |                                          |                          |             |

| 44       | PC14<br>PC15 | VDDIO      | EXTINT[7]                |             |         |         |        |         |                                         |      | SERCOM7/PAD[2]  |                                  |            |             |                                          |                          |             |

| 45       | PA12         |            | EXTINT[12]               |             |         |         |        |         |                                         |      |                 | SERCOM4/PAD[0]                   | TC2/MO[0]  | TCC0 WOR    |                                          | CMP[0]                   |             |

| 40       | PA12<br>PA13 |            | EXTINT[12]<br>EXTINT[13] |             |         |         |        |         |                                         |      |                 | SERCOM4/PAD[0]                   |            | _           |                                          | CMP[0]<br>CMP[1]         |             |

| 47       | PA13<br>PA14 |            | EXTINT[13]<br>EXTINT[14] |             |         |         |        |         |                                         |      |                 |                                  |            | 1000_007    |                                          |                          |             |

| 48<br>49 | PA14<br>PA15 |            | EXTINT[14]<br>EXTINT[15] |             |         |         |        |         |                                         |      |                 | SERCOM4/PAD[2]<br>SERCOM4/PAD[3] |            |             |                                          | GCLK_IO[0]<br>GCLK_IO[1] |             |

| 49<br>52 | PA15<br>PA16 | VDDIO      | EXTINT[0]                |             |         |         |        |         | VIAINI201                               |      |                 |                                  |            | TOCIMUOIO   |                                          |                          |             |

|          | PA16<br>PA17 | VDDIO      |                          |             |         |         |        |         | X[4]/Y[20]                              |      |                 | SERCOM3/PAD[0]                   |            |             |                                          | GCLK_IO[2]               |             |

| 53       |              |            | EXTINT[1]                |             |         |         |        |         | X[5]/Y[21]                              |      | SERCOM1/PAD[1]  |                                  |            |             |                                          | GCLK_IO[3]               |             |

| 54       | PA18         | VDDIO      | EXTINT[2]                |             |         |         |        |         | X[6]/Y[22]                              |      |                 | SERCOM3/PAD[2]                   |            |             |                                          | CMP[0]                   | CCL0/IN[2]  |

| 55       | PA19         | VDDIO      | EXTINT[3]                |             |         |         |        |         | X[7]/Y[23]                              |      |                 | SERCOM3/PAD[3]                   | 1C3/WO[1]  | TCC1/WO[3]  |                                          | CMP[1]                   | CCL0/OUT[0] |

| 56       | PC16         | VDDIO      | EXTINT[8]                |             |         |         |        |         |                                         |      | SERCOM6/PAD[0]  |                                  |            |             |                                          |                          |             |

| 57       | PC17         | VDDIO      | EXTINT[9]                |             |         |         |        |         |                                         |      | SERCOM6/PAD[1]  |                                  |            |             |                                          |                          |             |

| 58       | PC18         | VDDIO      | EXTINT[10]               |             |         |         |        |         |                                         |      | SERCOM6/PAD[2]  |                                  |            |             |                                          |                          |             |

## Table 6-1. PORT Function Multiplexing for SAM C21 N

# SAM C20/C21

| Bit    | 31          | 30  | 29  | 28   | 27     | 26  | 25  | 24  |  |  |  |

|--------|-------------|-----|-----|------|--------|-----|-----|-----|--|--|--|

| [      | DATA[31:24] |     |     |      |        |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

|        |             |     |     |      |        |     |     |     |  |  |  |

| Bit    | 23          | 22  | 21  | 20   | 19     | 18  | 17  | 16  |  |  |  |

|        |             |     |     | DATA | 23:16] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

|        |             |     |     |      |        |     |     |     |  |  |  |

| Bit    | 15          | 14  | 13  | 12   | 11     | 10  | 9   | 8   |  |  |  |

| Γ      |             |     |     | DATA | [15:8] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

|        |             |     |     |      |        |     |     |     |  |  |  |

| Bit    | 7           | 6   | 5   | 4    | 3      | 2   | 1   | 0   |  |  |  |

| Γ      |             |     |     | DATA | \[7:0] |     |     |     |  |  |  |

| Access | R/W         | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |  |  |  |

| Reset  | 0           | 0   | 0   | 0    | 0      | 0   | 0   | 0   |  |  |  |

Bits 31:0 – DATA[31:0]: Data

Data register.

# 13.13.8 Debug Communication Channel 1

Name:

DCC1

Offset:

0x0014 [ID-00001c14]

Reset:

0x0000000

Property:

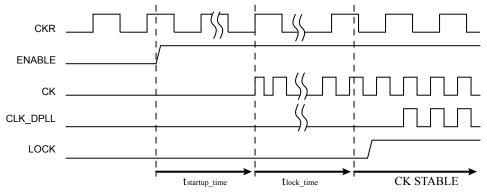

When the Wake Up Fast bit (DPLLCTRLB.WUF) is set, the wake up fast mode is activated. In this mode the clock gating cell is enabled at the end of the startup time. At this time the final frequency is not stable, as it is still during the acquisition period, but it allows to save several milliseconds. After first acquisition, the Lock Bypass bit (DPLLCTRLB.LBYPASS) indicates if the lock signal is discarded from the control of the clock gater (CG) generating the output clock CLK\_DPLL.

## Table 20-3. CLK\_DPLL Behavior from Startup to First Edge Detection

| WUF | LTIME CLK_DPLL Behavior |                                                                      |  |  |  |  |  |  |

|-----|-------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|

| 0   | 0                       | Normal Mode: First Edge when lock is asserted                        |  |  |  |  |  |  |

| 0   | Not Equal To Zero       | Lock Timer Timeout mode: First Edge when the timer down-counts to 0. |  |  |  |  |  |  |

| 1   | Х                       | Wake Up Fast Mode: First Edge when CK is active (startup time)       |  |  |  |  |  |  |

# Table 20-4. CLK\_DPLL Behavior after First Edge Detection

| LBYPASS | CLK_DPLL Behavior                                                     |

|---------|-----------------------------------------------------------------------|

| 0       | Normal Mode: the CLK_DPLL is turned off when lock signal is low.      |

| 1       | Lock Bypass Mode: the CLK_DPLL is always running, lock is irrelevant. |

# Figure 20-4. CK and CLK\_DPLL Output from DPLL Off Mode to Running Mode

## **Reference Clock Switching**

When a software operation requires reference clock switching, the recommended procedure is to turn the DPLL into the standby mode, modify the DPLLCTRLB.REFCLK to select the desired reference source, and activate the DPLL again.

## **Output Clock Prescaler**

The DPLL controller includes an output prescaler. This prescaler provides three selectable output clocks CK, CKDIV2 and CKDIV4. The Prescaler bit field in the DPLL Prescaler register (DPLLPRESC.PRESC) is used to select a new output clock prescaler. When the prescaler field is modified, the DPLLSYNCBUSY.DPLLPRESC bit is set. It will be cleared by hardware when the synchronization is over.

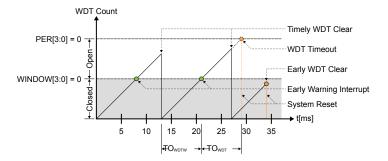

#### Figure 23-3. Window-Mode Operation

# 23.6.3 DMA Operation

Not applicable.

#### 23.6.4 Interrupts

The WDT has the following interrupt source:

- Early Warning (EW): Indicates that the counter is approaching the time-out condition.

- This interrupt is an asynchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the WDT is reset. See the INTFLAG register description for details on how to clear interrupt flags. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

Nested Vector Interrupt Controller Overview Interrupt Line Mapping PM – Power Manager Sleep Mode Controller

## 23.6.5 Events

Not applicable.

# 23.6.6 Sleep Mode Operation Related Links CTRLA

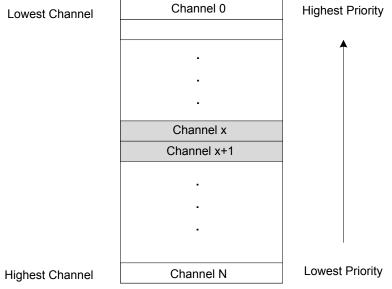

Each DMA channel supports a 4-level priority scheme. The priority level for a channel is configured by writing to the Channel Arbitration Level bit group in the Channel Control B register (CHCTRLB.LVL). As long as all priority levels are enabled, a channel with a higher priority level number will have priority over a channel with a lower priority level number. Each priority level x is enabled by setting the corresponding Priority Level x Enable bit in the Control register (CTRL.LVLENx=1).

Within each priority level the DMAC's arbiter can be configured to prioritize statically or dynamically:

*Static Arbitration* within a priority level is selected by writing a '0' to the Level x Round-Robin Scheduling Enable bit in the Priority Control 0 register (PRICTRL0.RRLVLENx).

When static arbitration is selected, the arbiter will prioritize a low channel number over a high channel number as shown in the figure below. When using the static arbitration there is a risk of high channel numbers never being granted access as the active channel. This can be avoided using a dynamic arbitration scheme.

*Dynamic Arbitration* within a priority level is selected by writing a '1' to **PRICTRLO.RRLVLEN**x.

The dynamic arbitration scheme in the DMAC is round-robin. With the round-robin scheme, the channel number of the last channel being granted access will have the lowest priority the next time the arbiter has to grant access to a channel within the same priority level, as shown in Figure 25-6. The channel number of the last channel being granted access as the active channel is stored in the Level x Channel Priority Number bit group in the Priority Control 0 register (PRICTRL0.LVLPRIx) for the corresponding priority level.

| Bit    | 31            | 30  | 29  | 28    | 27      | 26  | 25  | 24  |  |  |  |

|--------|---------------|-----|-----|-------|---------|-----|-----|-----|--|--|--|

|        | EXTINT[31:24] |     |     |       |         |     |     |     |  |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |  |  |

|        |               |     |     |       |         |     |     |     |  |  |  |

| Bit    | 23            | 22  | 21  | 20    | 19      | 18  | 17  | 16  |  |  |  |

|        |               |     |     | EXTIN | [23:16] |     |     |     |  |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |  |  |

|        |               |     |     |       |         |     |     |     |  |  |  |

| Bit    | 15            | 14  | 13  | 12    | 11      | 10  | 9   | 8   |  |  |  |

| [      |               |     |     | EXTIN | T[15:8] |     |     |     |  |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |  |  |

|        |               |     |     |       |         |     |     |     |  |  |  |

| Bit    | 7             | 6   | 5   | 4     | 3       | 2   | 1   | 0   |  |  |  |

|        |               |     |     | EXTIN | IT[7:0] |     |     |     |  |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |  |  |

#### Bits 31:0 – EXTINT[31:0]: External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

Writing a '1' to bit x will clear the External Interrupt Enable bit x, which disables the external interrupt EXTINTx.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

#### 26.8.7 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

Name:INTENSETOffset:0x10Reset:0x00000000Property:PAC Write-Protection

# SAM C20/C21

| Value | Name | Description                             |

|-------|------|-----------------------------------------|

| 0x2   | CLR  | Clear output register of pin on event.  |

| 0x3   | TGL  | Toggle output register of pin on event. |

# Table 28-5. PORT Event x Pin Identifier ( x = [3..0] )

| Value | Name  | Description                            |

|-------|-------|----------------------------------------|

| 0x0   | PIN0  | Event action to be executed on PIN 0.  |

| 0x1   | PIN1  | Event action to be executed on PIN 1.  |

|       |       |                                        |

| 0x31  | PIN31 | Event action to be executed on PIN 31. |

# 28.9.13 Peripheral Multiplexing n

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to 16 Peripheral Multiplexing registers in each group, one for every set of two subsequent I/O lines. The n denotes the number of the set of I/O lines.

Name:PMUXOffset:0x30 + n\*0x01 [n=0..15]Property:PAC Write-Protection

| Bit    | 7  | 6    | 5       | 4  | 3          | 2  | 1  | 0  |  |  |

|--------|----|------|---------|----|------------|----|----|----|--|--|

|        |    | PMUX | (O[3:0] |    | PMUXE[3:0] |    |    |    |  |  |

| Access | RW | RW   | RW      | RW | RW         | RW | RW | RW |  |  |

| Reset  | 0  | 0    | 0       | 0  | 0          | 0  | 0  | 0  |  |  |

## Bits 7:4 – PMUXO[3:0]: Peripheral Multiplexing for Odd-Numbered Pin

These bits select the peripheral function for odd-numbered pins  $(2^n + 1)$  of a PORT group, if the corresponding PINCFGy.PMUXEN bit is '1'.

Not all possible values for this selection may be valid. For more details, refer to the *I/O Multiplexing and Considerations*.

#### Sleep Mode Controller

## 29.6.4 Sleep Mode Operation

The EVSYS can generate interrupts to wake up the device from any sleep mode.

To be able to run in standby, the Run in Standby bit in the Channel register (CHANNELn.RUNSTDBY) must be set to '1'. When the Generic Clock On Demand bit in Channel register (CHANNELn.ONDEMAND) is set to '1' and the event generator is detected, the event channel will request its clock (GCLK\_EVSYS\_CHANNEL\_n). The event latency for a resynchronized channel path will increase by two GCLK\_EVSYS\_CHANNEL\_n clock (i.e., up to five GCLK\_EVSYS\_CHANNEL\_n clock cycles).

A channel will behave differently in different sleep modes regarding to CHANNELn.RUNSTDBY and CHANNELn.ONDEMAND, as shown in the table below:

| CHANNELn.ONDEMAN<br>D | CHANNELn.RUNSTDB<br>Y | Sleep Behavior                                                                                                                                                                                |  |  |  |  |

|-----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                     | 0                     | Only run in IDLE sleep mode if an event must be propagated. Disabled in STANDBY sleep mode.                                                                                                   |  |  |  |  |

| 0                     | 1                     | Always run in IDLE and STANDBY sleep modes.                                                                                                                                                   |  |  |  |  |

| 1                     | 0                     | Only run in IDLE sleep mode if an event must be<br>propagated. Disabled in STANDBY sleep mode.<br>Two GCLK_EVSYS_n latency added in RESYNC<br>path before the event is propagated internally. |  |  |  |  |

| 1                     | 1                     | Always run in IDLE and STANDBY sleep modes.<br>Two GCLK_EVSYS_n latency added in RESYNC<br>path before the event is propagated internally.                                                    |  |  |  |  |

## Table 29-1. Event Channel Sleep Behavior

# 29.7 Register Summary

## 29.7.1 Common Registers

| Offset   | Name     | Bit Pos. |         |         |         |         |          |          |         |         |

|----------|----------|----------|---------|---------|---------|---------|----------|----------|---------|---------|

| 0x00     | CTRLA    | 7:0      |         |         |         |         |          |          |         | SWRST   |

| 0x010x0B | Reserved |          |         |         |         |         |          |          |         |         |

| 0x0C     |          | 7:0      | USRRDY7 | USRRDY6 | USRRDY5 | USRRDY4 | USRRDY3  | USRRDY2  | USRRDY1 | USRRDY0 |

| 0x0D     | CHSTATUS | 15:8     |         |         |         |         | USRRDY11 | USRRDY10 | USRRDY9 | USRRDY8 |

| 0x0E     | CHSTATUS | 23:16    | CHBUSY7 | CHBUSY6 | CHBUSY5 | CHBUSY4 | CHBUSY3  | CHBUSY2  | CHBUSY1 | CHBUSY0 |

| 0x0F     |          | 31:24    |         |         |         |         | CHBUSY11 | CHBUSY10 | CHBUSY9 | CHBUSY8 |

| 0x10     |          | 7:0      | OVR7    | OVR6    | OVR5    | OVR4    | OVR3     | OVR2     | OVR1    | OVR0    |

| 0x11     |          | 15:8     |         |         |         |         | OVR11    | OVR10    | OVR9    | OVR8    |

| 0x12     | INTENCLR | 23:16    | EVD7    | EVD6    | EVD5    | EVD4    | EVD3     | EVD2     | EVD1    | EVD0    |

| 0x13     |          | 31:24    |         |         |         |         | EVD11    | EVD10    | EVD9    | EVD8    |

| 0x14     |          | 7:0      | OVR7    | OVR6    | OVR5    | OVR4    | OVR3     | OVR2     | OVR1    | OVR0    |

| 0x15     | INTENSET | 15:8     |         |         |         |         | OVR11    | OVR10    | OVR9    | OVR8    |

| 0x16     |          | 23:16    | EVD7    | EVD6    | EVD5    | EVD4    | EVD3     | EVD2     | EVD1    | EVD0    |

| Bit    | 15 | 14  | 13   | 12  | 11  | 10     | 9    | 8    |

|--------|----|-----|------|-----|-----|--------|------|------|

|        |    |     |      |     |     |        |      |      |

| Access |    |     |      |     |     |        |      |      |

| Reset  |    |     |      |     |     |        |      |      |

|        |    |     |      |     |     |        |      |      |

| Bit    | 7  | 6   | 5    | 4   | 3   | 2      | 1    | 0    |

|        |    | TXE | COLL | ISF | CTS | BUFOVF | FERR | PERR |

| Access |    | R/W | R/W  | R/W | R   | R/W    | R/W  | R/W  |

| Reset  |    | 0   | 0    | 0   | 0   | 0      | 0    | 0    |

# Bit 6 – TXE: Transmitter Empty

When CTRLA.FORM is set to LIN master mode, this bit is set when any ongoing transmission is complete and TxDATA is empty.

When CTRLA.FORM is not set to LIN master mode, this bit will always read back as zero.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

## **Bit 5 – COLL: Collision Detected**

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set when collision detection is enabled (CTRLB.COLDEN) and a collision is detected.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

#### Bit 4 – ISF: Inconsistent Sync Field

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set when the frame format is set to auto-baud (CTRLA.FORM) and a sync field not equal to 0x55 is received.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

## Bit 3 – CTS: Clear to Send

This bit indicates the current level of the CTS pin when flow control is enabled (CTRLA.TXPO).

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

#### Bit 2 – BUFOVF: Buffer Overflow

Reading this bit before reading the Data register will indicate the error status of the next character to be read.

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set when a buffer overflow condition is detected. A buffer overflow occurs when the receive buffer is full, there is a new character waiting in the receive shift register and a new start bit is detected.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

### • Master on Bus (MB)

Each interrupt source has its own interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) will be set when the interrupt condition is meet. Each interrupt can be individually enabled by writing '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request active until the interrupt flag is cleared, the interrupt is disabled or the I<sup>2</sup>C is reset. See INTFLAG register for details on how to clear interrupt flags.

The I<sup>2</sup>C has one common interrupt request line for all the interrupt sources. The value of INTFLAG indicates which interrupt is executed. Note that interrupts must be globally enabled for interrupt requests. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 33.6.4.3 Events

Not applicable.

## 33.6.5 Sleep Mode Operation I<sup>2</sup>C Master Operation

The generic clock (GCLK\_SERCOMx\_CORE) will continue to run in idle sleep mode. If the Run In Standby bit in the Control A register (CTRLA.RUNSTDBY) is '1', the GLK\_SERCOMx\_CORE will also run in standby sleep mode. Any interrupt can wake up the device.

If CTRLA.RUNSTDBY=0, the GLK\_SERCOMx\_CORE will be disabled after any ongoing transaction is finished. Any interrupt can wake up the device.

## I<sup>2</sup>C Slave Operation

Writing CTRLA.RUNSTDBY=1 will allow the Address Match interrupt to wake up the device.

When CTRLA.RUNSTDBY=0, all receptions will be dropped.

## 33.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Write to Bus State bits in the Status register (STATUS.BUSSTATE)

- Address bits in the Address register (ADDR.ADDR) when in master operation.

The following registers are synchronized when written:

• Data (DATA) when in master operation

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

#### **Related Links**

Register Synchronization

# 33.7 Register Summary - I2C Slave

| Offset | Name             | Bit Pos. |          |         |       |             |           |        |              |        |

|--------|------------------|----------|----------|---------|-------|-------------|-----------|--------|--------------|--------|

| 0x00   |                  | 7:0      | RUNSTDBY |         |       |             | MODE[2:0] |        | ENABLE       | SWRST  |

| 0x01   |                  | 15:8     |          |         |       |             |           |        |              |        |

| 0x02   | CTRLA            | 23:16    | SEXTTOEN |         | SDAHO | DLD[1:0]    |           |        |              | PINOUT |

| 0x03   |                  | 31:24    |          | LOWTOUT |       |             | SCLSM     |        | SPEE         | D[1:0] |

| 0x04   |                  | 7:0      |          |         |       |             |           |        |              |        |

| 0x05   | CTRLB            | 15:8     | AMOE     | DE[1:0] |       |             |           | AACKEN | GCMD         | SMEN   |

| 0x06   | CIRLB            | 23:16    |          |         |       |             |           | ACKACT | CME          | [1:0]  |

| 0x07   |                  | 31:24    |          |         |       |             |           |        |              |        |

| 0x08   |                  |          |          |         |       |             |           |        |              |        |

|        | Reserved         |          |          |         |       |             |           |        |              |        |

| 0x13   |                  |          |          |         |       |             |           |        |              |        |

| 0x14   | INTENCLR         | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x15   | Reserved         |          |          |         |       |             |           |        |              |        |

| 0x16   | INTENSET         | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x17   | Reserved         |          |          |         |       |             |           |        |              |        |

| 0x18   | INTFLAG          | 7:0      | ERROR    |         |       |             |           | DRDY   | AMATCH       | PREC   |

| 0x19   | Reserved         |          |          |         |       |             |           |        |              |        |

| 0x1A   | STATUS           | 7:0      | CLKHOLD  | LOWTOUT |       | SR          | DIR       | RXNACK | COLL         | BUSERR |

| 0x1B   | STATUS           | 15:8     |          |         |       |             | LENERR    | HS     | SEXTTOUT     |        |

| 0x1C   |                  | 7:0      |          |         |       |             |           |        | ENABLE       | SWRST  |

| 0x1D   | <b>EVNOPLIEV</b> | 15:8     |          |         |       |             |           |        |              |        |

| 0x1E   | SYNCBUSY         | 23:16    |          |         |       |             |           |        |              |        |

| 0x1F   |                  | 31:24    |          |         |       |             |           |        |              |        |

| 0x20   |                  |          |          |         |       |             |           |        |              |        |

|        | Reserved         |          |          |         |       |             |           |        |              |        |

| 0x23   |                  |          |          |         |       |             |           |        |              |        |

| 0x24   |                  | 7:0      |          |         |       | ADDR[6:0]   |           |        |              | GENCEN |

| 0x25   | ADDR             | 15:8     | TENBITEN |         |       |             |           |        | ADDR[9:7]    |        |

| 0x26   | AUUK             | 23:16    |          |         | ļ     | ADDRMASK[6: | 0]        |        |              |        |

| 0x27   |                  | 31:24    |          |         |       |             |           |        | ADDRMASK[9:7 | ]      |

| 0x28   |                  | 7:0      |          |         |       | DAT         | A[7:0]    |        |              |        |

| 0x29   | DATA             | 15:8     |          |         |       |             |           |        |              |        |

# 33.8 Register Description - I<sup>2</sup>C Slave

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

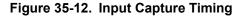

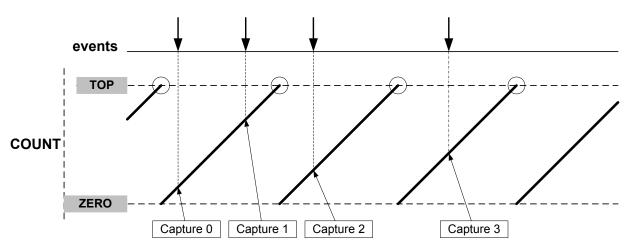

### **Event Capture Action**

The compare/capture channels can be used as input capture channels to capture events from the Event System or from the corresponding IO pin, and give them a timestamp. The following figure shows four capture events for one capture channel.

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

## Period and Pulse-Width (PPW) Capture Action

The TC can perform two input captures and restart the counter on one of the edges. This enables the TC to measure the pulse width and period and to characterize the frequency *f* and duty cycle of an input signal:

$$f = \frac{1}{T}$$

dutyCycle =  $\frac{t_p}{T}$

Name:STATUSOffset:0x0BReset:0x01Property:Read-Synchronized

| Bit    | 7 | 6 | 5 | 4       | 3       | 2 | 1     | 0    |

|--------|---|---|---|---------|---------|---|-------|------|

|        |   |   |   | CCBUFVx | PERBUFV |   | SLAVE | STOP |

| Access |   |   |   | R/W     | R/W     |   | R     | R    |

| Reset  |   |   |   | 0       | 0       |   | 0     | 1    |

## Bit 4 – CCBUFVx: Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

#### Bit 3 – PERBUFV: Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. The bit is cleared by writing '1' to the corresponding location when CTRLB.LUPD is set, or automatically cleared by hardware on UPDATE condition. This bit is available only in 8-bit mode and will always read zero in 16- and 32-bit modes.

#### Bit 1 – SLAVE: Slave Status Flag

This bit is only available in 32-bit mode on the slave TC (i.e., TC1 and/or TC3). The bit is set when the associated master TC (TC0 and TC2, respectively) is set to run in 32-bit mode.

#### Bit 0 – STOP: Stop Status Flag

This bit is set when the TC is disabled, on a Stop command, or on an overflow/underflow condition when the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT) is '1'.

| Value | Description         |

|-------|---------------------|

| 0     | Counter is running. |

| 1     | Counter is stopped. |

#### 35.7.1.9 Waveform Generation Control

Name:WAVEOffset:0x0CReset:0x00Property:PAC Write-Protection, Enable-Protected

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e. a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

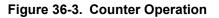

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. The COUNT value will always be ZERO or TOP, depending on direction set by CTRLBSET.DIR or CTRLBCLR.DIR, when starting the TCC, unless a different value has been written to it, or the TCC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed during normal operation. See also Figure 36-3.

# **Stop Command**

A stop command can be issued from software by using TCC Command bits in Control B Set register (CTRLBSET.CMD=0x2, STOP).

## Pause Event Action

A pause command can be issued when the stop event action is configured in the Input Event Action 1 bits in Event Control register (EVCTRL.EVACT1=0x3, STOP).

# **Re-Trigger Command and Event Action**

A re-trigger command can be issued from software by using TCC Command bits in Control B Set register (CTRLBSET.CMD=0x1, RETRIGGER), or from event when the re-trigger event action is configured in the Input Event 0/1 Action bits in Event Control register (EVCTRL.EVACTn=0x1, RETRIGGER).

When the command is detected during counting operation, the counter will be reloaded or cleared, depending on the counting direction (CTRLBSET.DIR or CTRLBCLR.DIR). The Re-Trigger bit in the Interrupt Flag Status and Clear register will be set (INTFLAG.TRG). It is also possible to generate an event by writing a '1' to the Re-Trigger Event Output Enable bit in the Event Control register (EVCTRL.TRGEO). If the re-trigger command is detected when the counter is stopped, the counter will resume counting operation from the value in COUNT.

## Note:

When a re-trigger event action is configured in the Event Action bits in the Event Control register (EVCTRL.EVACTn=0x1, RETRIGGER), enabling the counter will not start the counter. The counter will start on the next incoming event and restart on corresponding following event.

## **Start Event Action**

The start action can be selected in the Event Control register (EVCTRL.EVACT0=0x3, START) and can start the counting operation when previously stopped. The event has no effect if the counter is already

Name:PERBUFOffset:0x6C [ID-00002e48]Reset:0xFFFFFFFProperty:Write-Synchronized, Read-Synchronized

| Bit    | 31            | 30      | 29             | 28    | 27      | 26  | 25  | 24  |  |  |  |

|--------|---------------|---------|----------------|-------|---------|-----|-----|-----|--|--|--|

|        |               |         |                |       |         |     |     |     |  |  |  |

| Access |               |         |                |       |         |     |     |     |  |  |  |

| Reset  |               |         |                |       |         |     |     |     |  |  |  |

|        |               |         |                |       |         |     |     |     |  |  |  |

| Bit    | 23            | 22      | 21             | 20    | 19      | 18  | 17  | 16  |  |  |  |

|        | PERBUF[17:10] |         |                |       |         |     |     |     |  |  |  |

| Access | R/W           | R/W     | R/W            | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 1             | 1       | 1              | 1     | 1       | 1   | 1   | 1   |  |  |  |

|        |               |         |                |       |         |     |     |     |  |  |  |

| Bit    | 15            | 14      | 13             | 12    | 11      | 10  | 9   | 8   |  |  |  |

|        |               |         |                | PERBL | JF[9:2] |     |     |     |  |  |  |

| Access | R/W           | R/W     | R/W            | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 1             | 1       | 1              | 1     | 1       | 1   | 1   | 1   |  |  |  |

|        |               |         |                |       |         |     |     |     |  |  |  |

| Bit    | 7             | 6       | 5              | 4     | 3       | 2   | 1   | 0   |  |  |  |

|        | PERB          | UF[1:0] | DITHERBUF[5:0] |       |         |     |     |     |  |  |  |

| Access | R/W           | R/W     | R/W            | R/W   | R/W     | R/W | R/W | R/W |  |  |  |

| Reset  | 1             | 1       | 1              | 1     | 1       | 1   | 1   | 1   |  |  |  |

## Bits 23:6 – PERBUF[17:0]: Period Buffer Value

These bits hold the value of the period buffer register. The value is copied to PER register on UPDATE condition.

Note: When the TCC is configured as 16-bit timer/counter, the excess bits are read zero.

**Note:** This bit field occupies the MSB of the register, [23:m]. m is dependent on the Resolution bit in the Control A register (CTRLA.RESOLUTION):

| CTRLA.RESOLUTION | Bits [23:m]     |

|------------------|-----------------|

| 0x0 - NONE       | 23:0            |

| 0x1 - DITH4      | 23:4            |

| 0x2 - DITH5      | 23:5            |

| 0x3 - DITH6      | 23:6 (depicted) |

#### Bits 5:0 – DITHERBUF[5:0]: Dithering Buffer Cycle Number

These bits represent the PER.DITHER bits buffer. When the double buffering is enabled, the value of this bit field is copied to the PER.DITHER bits on an UPDATE condition.

**Note:** This bit field consists of the n LSB of the register. n is dependent on the value of the Resolution bits in the Control A register (CTRLA.RESOLUTION):

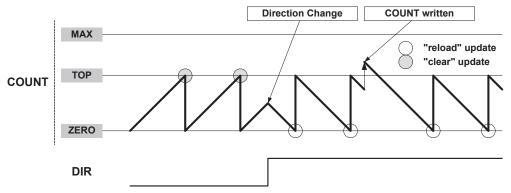

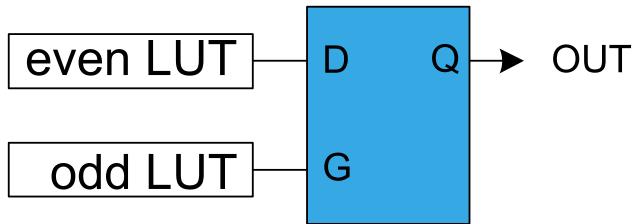

#### Figure 37-15. JK Flip Flop

When the even LUT is disabled (LUTCTRL0.ENABLE=0 / LUTCTRL2.ENABLE=0), the flip-flop is asynchronously cleared. The reset command (R) is kept enabled for one APB clock cycle. In all other cases, the flip-flop output (OUT) is refreshed on rising edge of the GCLK\_CCL, as shown in Table 37-3.

# Table 37-3. JK Characteristics

| R | J | κ | ουτ                    |

|---|---|---|------------------------|

| 1 | Х | Х | Clear                  |

| 0 | 0 | 0 | Hold state (no change) |

| 0 | 0 | 1 | Clear                  |

| 0 | 1 | 0 | Set                    |

| 0 | 1 | 1 | Toggle                 |

# Gated D-Latch (DLATCH)

When the DLATCH is selected, the D-input is driven by the even LUT output (LUT0 and LUT2), and the G-input is driven by the odd LUT output (LUT1 and LUT3), as shown in Figure 37-14.

## Figure 37-16. D-Latch

When the even LUT is disabled (LUTCTRL0.ENABLE=0 / LUTCTRL2.ENABLE=0), the latch output will be cleared. The G-input is forced enabled for one more APB clock cycle, and the D-input to zero. In all other cases, the latch output (OUT) is refreshed as shown in Table 37-4.

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Number of<br>Automatic Right<br>Shifts | Final Result<br>Precision | Automatic<br>Division Factor |

|-------------------------------------|-----------------------|----------------------------------------|---------------------------|------------------------------|

| 4                                   | 0x2                   | 0                                      | 14 bits                   | 0                            |

| 8                                   | 0x3                   | 0                                      | 15 bits                   | 0                            |

| 16                                  | 0x4                   | 0                                      | 16 bits                   | 0                            |

| 32                                  | 0x5                   | 1                                      | 16 bits                   | 2                            |

| 64                                  | 0x6                   | 2                                      | 16 bits                   | 4                            |

| 128                                 | 0x7                   | 3                                      | 16 bits                   | 8                            |

| 256                                 | 0x8                   | 4                                      | 16 bits                   | 16                           |

| 512                                 | 0x9                   | 5                                      | 16 bits                   | 32                           |

| 1024                                | 0xA                   | 6                                      | 16 bits                   | 64                           |

| Reserved                            | 0xB –0xF              |                                        | 12 bits                   | 0                            |

#### 38.6.2.10 Averaging

Averaging is a feature that increases the sample accuracy, at the cost of a reduced sampling rate. This feature is suitable when operating in noisy conditions.

Averaging is done by accumulating m samples, as described in Accumulation, and dividing the result by m. The averaged result is available in the RESULT register. The number of samples to be accumulated is specified by writing to AVGCTRL.SAMPLENUM as shown in Table 38-2.

The division is obtained by a combination of the automatic right shift described above, and an additional right shift that must be specified by writing to the Adjusting Result/Division Coefficient field in AVGCTRL (AVGCTRL.ADJRES), as described in Table 38-2.

**Note:** To perform the averaging of two or more samples, the Conversion Result Resolution field in the Control C register (CTRLC.RESSEL) must be set.

Averaging AVGCTRL.SAMPLENUM samples will reduce the un-averaged sampling rate by a factor

#### AVGCTRL.SAMPLENUM.

When the averaged result is available, the INTFLAG.RESRDY bit will be set.

#### Table 38-2. Averaging

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result<br>Precision | Number of<br>Automatic<br>Right<br>Shifts |    | AVGCTRL.ADJRES | Total<br>Number<br>of Right<br>Shifts | Final<br>Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|----|----------------|---------------------------------------|------------------------------|---------------------------------|

| 1                                   | 0x0                   | 12 bits                             | 0                                         | 1  | 0x0            |                                       | 12 bits                      | 0                               |

| 2                                   | 0x1                   | 13                                  | 0                                         | 2  | 0x1            | 1                                     | 12 bits                      | 0                               |

| 4                                   | 0x2                   | 14                                  | 0                                         | 4  | 0x2            | 2                                     | 12 bits                      | 0                               |

| 8                                   | 0x3                   | 15                                  | 0                                         | 8  | 0x3            | 3                                     | 12 bits                      | 0                               |

| 16                                  | 0x4                   | 16                                  | 0                                         | 16 | 0x4            | 4                                     | 12 bits                      | 0                               |

| 32                                  | 0x5                   | 17                                  | 1                                         | 16 | 0x4            | 5                                     | 12 bits                      | 2                               |

Register Synchronization

# 41.7 Register Summary

| Offset | Name     | Bit Pos. |       |          |        |       |          |         |         |          |

|--------|----------|----------|-------|----------|--------|-------|----------|---------|---------|----------|

| 0x00   | CTRLA    | 7:0      |       | RUNSTDBY |        |       |          |         | ENABLE  | SWRST    |

| 0x01   | CTRLB    | 7:0      | REFSE | EL[1:0]  | DITHER |       | VPD      | LEFTADJ | IOEN    | EOEN     |

| 0x02   | EVCTRL   | 7:0      |       |          |        |       |          | INVEI   | EMPTYEO | STARTEI  |

| 0x03   | Reserved |          |       |          |        |       |          |         |         |          |

| 0x04   | INTENCLR | 7:0      |       |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x05   | INTENSET | 7:0      |       |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x06   | INTFLAG  | 7:0      |       |          |        |       |          |         | EMPTY   | UNDERRUN |

| 0x07   | STATUS   | 7:0      |       |          |        |       |          |         |         | READY    |

| 0x08   | DATA     | 7:0      |       |          |        | DAT   | A[7:0]   |         |         |          |

| 0x09   | DATA     | 15:8     |       |          |        | DATA  | [15:8]   |         |         |          |

| 0x0A   |          |          |       |          |        |       |          |         |         |          |

|        | Reserved |          |       |          |        |       |          |         |         |          |

| 0x0B   |          |          |       |          |        |       |          |         |         |          |

| 0x0C   | DATABUF  | 7:0      |       |          |        | DATAB | UF[7:0]  |         |         |          |

| 0x0D   | DAIADOI  | 15:8     |       |          |        | DATAB | UF[15:8] |         |         |          |

| 0x0E   |          |          |       |          |        |       |          |         |         |          |

|        | Reserved |          |       |          |        |       |          |         |         |          |

| 0x0F   |          |          |       |          |        |       |          |         |         |          |

| 0x10   |          | 7:0      |       |          |        |       | DATABUF  | DATA    | ENABLE  | SWRST    |

| 0x11   | SYNCBUSY | 15:8     |       |          |        |       |          |         |         |          |

| 0x12   | 31102001 | 23:16    |       |          |        |       |          |         |         |          |

| 0x13   |          | 31:24    |       |          |        |       |          |         |         |          |

| 0x14   |          |          |       |          |        |       |          |         |         |          |

|        | Reserved |          |       |          |        |       |          |         |         |          |

| 0x17   |          |          |       |          |        |       |          |         |         |          |

| 0x18   | DBGCTRL  | 7:0      |       |          |        |       |          |         |         | DBGRUN   |

# 41.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

## 41.8.1 Control A

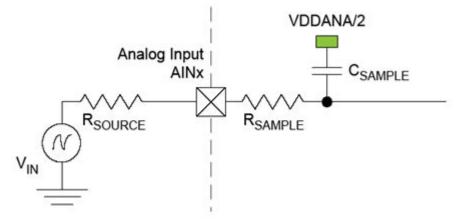

| Symbol  | Parameters                        | Conditions                    | Min        | Тур  | Мах        | Unit |

|---------|-----------------------------------|-------------------------------|------------|------|------------|------|

| Vcmin   | Input common mode voltage         | CTRLC.R2R=1                   | 0.2        | -    | VREF-0.2   | V    |

|         |                                   | CTRLC.R2R=0                   | VREF/2-0.2 | -    | VREF/2+0.2 | V    |

| CSAMPLE | Input sampling capacitance        |                               | -          | 1.6  | 4.5        | pF   |

| RSAMPLE | Input sampling on-resistance      | For a sampling rate at 1 Msps | -          | 1000 | 1715       | Ω    |

| Rref    | Reference input source resistance |                               | 0          | -    | 1000       | kΩ   |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

# Figure 45-4. ADC Analog Input AINx

The minimum sampling time  $t_{\text{samplehold}}$  for a given  $R_{\text{source}}$  can be found using this formula:

$t_{\text{samplehold}} \ge (R_{\text{sample}} + R_{\text{source}}) \times C_{\text{sample}} \times (n+2) \times \ln(2)$ For 12-bit accuracy:

$$t_{\text{samplehold}} \ge (R_{\text{sample}} + R_{\text{source}}) \times C_{\text{sample}} \times 9.7$$

where  $t_{\text{samplehold}} \ge \frac{1}{2 \times f_{\text{ADC}}}$ .

# Table 45-19. Differential Mode<sup>(1)</sup>

| Symbol              | Parameter                 | Cond            | Conditions                 |      |      | ent  | Unit |

|---------------------|---------------------------|-----------------|----------------------------|------|------|------|------|

|                     |                           |                 |                            | Min  | Тур  | Мах  |      |

| ENOB <sup>(2)</sup> | Effective Number of bits  | Fadc = 500 ksps | Vddana=5.0V<br>Vref=Vddana | 10.0 | 10.7 | 11   | bits |

|                     |                           |                 | Vddana=2.7V<br>Vref=2.0V   | 10.3 | 10.5 | 10.9 |      |

|                     |                           | Fadc = 1 Msps   | Vddana=5.0V<br>Vref=Vddana | 10.5 | 10.8 | 11.1 |      |

|                     |                           |                 | Vddana=2.7V<br>Vref=2.0V   | 9.9  | 10.0 | 10.6 |      |

| TUE                 | Total Unadjusted<br>Error | Fadc = 500 ksps | Vddana=5.0V<br>Vref=Vddana | -    | 7.8  | 17.0 | LSB  |