Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20j15a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Device select

# 13.11 Functional Description

## 13.11.1 Principle of Operation

The DSU provides memory services such as CRC32 or MBIST that require almost the same interface. Hence, the Address, Length and Data registers (ADDR, LENGTH, DATA) are shared. These shared registers must be configured first; then a command can be issued by writing the Control register. When a command is ongoing, other commands are discarded until the current operation is completed. Hence, the user must wait for the STATUSA.DONE bit to be set prior to issuing another one.

## 13.11.2 Basic Operation

## 13.11.2.1 Initialization

The module is enabled by enabling its clocks. For more details, refer to Clocks. The DSU registers can be PAC write-protected.

#### **Related Links**

PAC - Peripheral Access Controller

#### 13.11.2.2 Operation From a Debug Adapter

Debug adapters should access the DSU registers in the external address range 0x100 - 0x2000. If the device is protected by the NVMCTRL security bit, accessing the first 0x100 bytes causes the system to return an error. Refer to Intellectual Property Protection.

#### **Related Links**

NVMCTRL – Non-Volatile Memory Controller Security Bit

#### 13.11.2.3 Operation From the CPU

There are no restrictions when accessing DSU registers from the CPU. However, the user should access DSU registers in the internal address range (0x0 - 0x100) to avoid external security restrictions. Refer to Intellectual Property Protection.

## 13.11.3 32-bit Cyclic Redundancy Check CRC32

The DSU unit provides support for calculating a cyclic redundancy check (CRC32) value for a memory area (including Flash and AHB RAM).

When the CRC32 command is issued from:

- The internal range, the CRC32 can be operated at any memory location

- The external range, the CRC32 operation is restricted; DATA, ADDR, and LENGTH values are forced (see below)

# SAM C20/C21

| Access<br>Reset<br>Bit | t    | 22        |             |    |    |           |             |    |

|------------------------|------|-----------|-------------|----|----|-----------|-------------|----|

| Reset                  | t    | 22        |             |    |    |           |             |    |

|                        |      | 22        |             |    |    |           |             |    |

| Bit                    | t 23 | 22        |             |    |    |           |             |    |

| Bit                    | t 23 | 22        |             |    |    |           |             |    |

|                        |      | 22        | 21          | 20 | 19 | 18        | 17          | 16 |

|                        |      |           |             |    |    |           |             |    |

| Access                 | 3    |           |             |    | 1  |           |             |    |

| Reset                  | t    |           |             |    |    |           |             |    |

|                        |      |           |             |    |    |           |             |    |

| Bit                    | t 15 | 14        | 13          | 12 | 11 | 10        | 9           | 8  |

|                        |      |           |             |    |    |           |             |    |

| Access                 | s    |           |             |    | I  |           |             |    |

| Reset                  | t    |           |             |    |    |           |             |    |

|                        |      |           |             |    |    |           |             |    |

| Bit                    | t 7  | 6         | 5           | 4  | 3  | 2         | 1           | 0  |

|                        |      | FKBC      | C[3:0]      |    |    | JEPC      | C[3:0]      |    |

|                        | • R  | R         | R           | R  | R  | R         | R           | R  |

| Access                 | , ,, | 0         | 0           | 0  | 0  | 0         | 0           | 0  |

| Reset                  | t 7  | FKBC<br>R | C[3:0]<br>R | R  | R  | JEPC<br>R | C[3:0]<br>R |    |

# Bits 7:4 – FKBC[3:0]: 4KB Count

These bits will always return zero when read, indicating that this debug component occupies one 4KB block.

## Bits 3:0 – JEPCC[3:0]: JEP-106 Continuation Code

These bits will always return zero when read.

# 13.13.15 Peripheral Identification 0

Name:

PID0

Offset:

0x1FE0

Reset:

0x0000000

Property:

#### 16.6.5.2 Minimize Power Consumption in Standby

The following table identifies when a Clock Generator is off in Standby Mode, minimizing the power consumption:

| Request for Clock n present | GENCTRLn.RUNSTDB<br>Y | GENCTRLn.OE | Clock Generator n |

|-----------------------------|-----------------------|-------------|-------------------|

| yes                         | -                     | -           | active            |

| no                          | 1                     | 1           | active            |

| no                          | 1                     | 0           | OFF               |

| no                          | 0                     | 1           | OFF               |

| no                          | 0                     | 0           | OFF               |

#### Table 16-2. Clock Generator n Activity in Standby Mode

#### 16.6.5.3 Entering Standby Mode

There may occur a delay when the device is put into Standby, until the power is turned off. This delay is caused by running Clock Generators: if the Run in Standby bit in the Generator Control register (GENCTRLn.RUNSTDBY) is '0', GCLK must verify that the clock is turned of properly. The duration of this verification is frequency-dependent.

#### **Related Links**

PM – Power Manager

#### 16.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

An exception is the Channel Enable bit in the Peripheral Channel Control registers (PCHCTRLm.CHEN). When changing this bit, the bit value must be read-back to ensure the synchronization is complete and to assert glitch free internal operation. Note that changing the bit value under ongoing synchronization will *not* generate an error.

The following registers are synchronized when written:

- Generic Clock Generator Control register (GENCTRLn)

- Control A register (CTRLA)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

#### **Related Links**

CTRLA

**Register Synchronization**

PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45 Frequencies must never exceed the specified maximum frequency for each clock domain.

| Value  | Name   | Description   |

|--------|--------|---------------|

| 0x01   | DIV1   | Divide by 1   |

| 0x02   | DIV2   | Divide by 2   |

| 0x04   | DIV4   | Divide by 4   |

| 0x08   | DIV8   | Divide by 8   |

| 0x10   | DIV16  | Divide by 16  |

| 0x20   | DIV32  | Divide by 32  |

| 0x40   | DIV64  | Divide by 64  |

| 0x80   | DIV128 | Divide by 128 |

| others | -      | Reserved      |

## 17.8.6 AHB Mask

**Note:** This register is only available for SAMC2x "N" series devices.

Name:AHBMASKOffset:0x10 [ID-00001086]Reset:0x000003CFFProperty:PAC Write-Protection

| Bit    | 31   | 30    | 29      | 28        | 27  | 26   | 25   | 24   |

|--------|------|-------|---------|-----------|-----|------|------|------|

|        |      |       |         |           |     |      |      |      |

| Access |      |       | R       | R         | R   | R    | R    | R    |

| Reset  |      |       | 0       | 0         | 0   | 0    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 23   | 22    | 21      | 20        | 19  | 18   | 17   | 16   |

|        |      |       |         |           |     |      |      |      |

| Access | R    | R     | R       | R         | R   | R    | R    | R    |

| Reset  | 0    | 0     | 0       | 0         | 0   | 0    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 15   | 14    | 13      | 12        | 11  | 10   | 9    | 8    |

|        |      |       |         |           |     | PAC  | CAN1 | CAN0 |

| Access | R    | R     | R       | R         | R   | R/W  | R/W  | R/W  |

| Reset  | 0    | 0     | 0       | 0         | 1   | 1    | 0    | 0    |

|        |      |       |         |           |     |      |      |      |

| Bit    | 7    | 6     | 5       | 4         | 3   | 2    | 1    | 0    |

|        | DMAC | HSRAM | NVMCTRL | HMATRIXHS | DSU | APBC | APBB | APBA |

| Access | R/W  | R/W   | R/W     | R/W       | R/W | R/W  | R/W  | R/W  |

| Reset  | 1    | 1     | 1       | 1         | 1   | 1    | 1    | 1    |

# Bit 13 – APBD: APBD AHB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The AHB clock for the APBD is stopped. |

| 1     | The AHB clock for the APBD is enabled. |

#### Bit 12 – DIVAS: DIVAS AHB Clock Enable

#### 24.12.10 Alarm Value in Clock/Calendar mode (CTRLA.MODE=2)

The 32-bit value of ALARM is continuously compared with the 32-bit CLOCK value, based on the masking set by MASK.SEL. When a match occurs, the Alarm n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.ALARM) is set on the next counter cycle, and the counter is cleared if CTRLA.MATCHCLR is '1'.

Name: ALARM Offset: 0x20 Reset: 0x0000000 Property: PAC Write-Protection, Write-Synchronized

| Bit    | 31   | 30      | 29     | 28     | 27       | 26          | 25  | 24        |

|--------|------|---------|--------|--------|----------|-------------|-----|-----------|

|        |      |         | YEAF   | R[5:0] |          |             | MON | TH[3:2]   |

| Access | R/W  | R/W     | R/W    | R/W    | R/W      | R/W         | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0        | 0           | 0   | 0         |

|        |      |         |        |        |          |             |     |           |

| Bit    | 23   | 22      | 21     | 20     | 19       | 18          | 17  | 16        |

|        | MON  | FH[1:0] |        |        | DAY[4:0] |             |     | HOUR[4:4] |

| Access | R/W  | R/W     | R/W    | R/W    | R/W      | R/W         | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0        | 0           | 0   | 0         |

|        |      |         |        |        |          |             |     |           |

| Bit    | 15   | 14      | 13     | 12     | 11       | 10          | 9   | 8         |

|        |      | HOU     | R[3:0] |        |          | MINUTE[5:2] |     |           |

| Access | R/W  | R/W     | R/W    | R/W    | R/W      | R/W         | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0        | 0           | 0   | 0         |

|        |      |         |        |        |          |             |     |           |

| Bit    | 7    | 6       | 5      | 4      | 3        | 2           | 1   | 0         |

|        | MINU | TE[1:0] |        |        | SECO     | ND[5:0]     |     |           |

| Access | R/W  | R/W     | R/W    | R/W    | R/W      | R/W         | R/W | R/W       |

| Reset  | 0    | 0       | 0      | 0      | 0        | 0           | 0   | 0         |

#### Bits 31:26 - YEAR[5:0]: Year

The alarm year. Years are only matched if MASK.SEL is 6

#### Bits 25:22 - MONTH[3:0]: Month

The alarm month. Months are matched only if MASK.SEL is greater than 4.

#### Bits 21:17 – DAY[4:0]: Day

The alarm day. Days are matched only if MASK.SEL is greater than 3.

#### Bits 16:12 - HOUR[4:0]: Hour

The alarm hour. Hours are matched only if MASK.SEL is greater than 2.

#### Bits 11:6 - MINUTE[5:0]: Minute

The alarm minute. Minutes are matched only if MASK.SEL is greater than 1.

#### Bits 5:0 - SECOND[5:0]: Second

The alarm second. Seconds are matched only if MASK.SEL is greater than 0.

The following DMAC bit is enable-protected, meaning that it can only be written when both the DMAC and CRC are disabled (CTRL.DMAENABLE=0 and CTRL.CRCENABLE=0):

• Software Reset bit in Control register (CTRL.SWRST)

The following DMA channel register is enable-protected, meaning that it can only be written when the corresponding DMA channel is disabled (CHCTRLA.ENABLE=0):

Channel Control B (CHCTRLB) register, except the Command bit (CHCTRLB.CMD) and the Channel Arbitration Level bit (CHCTRLB.LVL)

The following DMA channel bit is enable-protected, meaning that it can only be written when the corresponding DMA channel is disabled:

• Channel Software Reset bit in Channel Control A register (CHCTRLA.SWRST)

The following CRC registers are enable-protected, meaning that they can only be written when the CRC is disabled (CTRL.CRCENABLE=0):

- CRC Control register (CRCCTRL)

- CRC Checksum register (CRCCHKSUM)

Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before the DMAC is enabled it must be configured, as outlined by the following steps:

- The SRAM address of where the descriptor memory section is located must be written to the Description Base Address (BASEADDR) register

- The SRAM address of where the write-back section should be located must be written to the Write-Back Memory Base Address (WRBADDR) register

- Priority level x of the arbiter can be enabled by setting the Priority Level x Enable bit in the Control register (CTRL.LVLENx=1)

Before a DMA channel is enabled, the DMA channel and the corresponding first transfer descriptor must be configured, as outlined by the following steps:

- DMA channel configurations

- The channel number of the DMA channel to configure must be written to the Channel ID (CHID) register

- Trigger action must be selected by writing the Trigger Action bit group in the Channel Control B register (CHCTRLB.TRIGACT)

- Trigger source must be selected by writing the Trigger Source bit group in the Channel Control B register (CHCTRLB.TRIGSRC)

- Transfer Descriptor

- The size of each access of the data transfer bus must be selected by writing the Beat Size bit group in the Block Transfer Control register (BTCTRL.BEATSIZE)

- The transfer descriptor must be made valid by writing a one to the Valid bit in the Block Transfer Control register (BTCTRL.VALID)

- Number of beats in the block transfer must be selected by writing the Block Transfer Count (BTCNT) register

- Source address for the block transfer must be selected by writing the Block Transfer Source Address (SRCADDR) register

- Destination address for the block transfer must be selected by writing the Block Transfer Destination Address (DSTADDR) register

Name: CHID Offset: 0x3F [ID-00001ece] Reset: 0x00 Property: -

| Bit    | 7 | 6 | 5 | 4 | 3   | 2    | 1    | 0   |

|--------|---|---|---|---|-----|------|------|-----|

|        |   |   |   |   |     | ID[; | 3:0] |     |

| Access |   |   |   |   | R/W | R/W  | R/W  | R/W |

| Reset  |   |   |   |   | 0   | 0    | 0    | 0   |

## Bits 3:0 – ID[3:0]: Channel ID

These bits define the channel number that will be affected by the channel registers (CH\*). Before reading or writing a channel register, the channel ID bit group must be written first.

## 25.8.18 Channel Control A

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

Name: CHCTRLA Offset: 0x40 [ID-00001ece] Reset: 0x00 Property: PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6        | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|----------|---|---|---|---|--------|-------|

|        |   | RUNSTDBY |   |   |   |   | ENABLE | SWRST |

| Access | R | R/W      | R | R | R | R | R/W    | R/W   |

| Reset  | 0 | 0        | 0 | 0 | 0 | 0 | 0      | 0     |

## Bit 6 – RUNSTDBY: Channel run in standby

This bit is used to keep the DMAC channel running in standby mode.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The DMAC channel is halted in standby.        |

| 1     | The DMAC channel continues to run in standby. |

## Bit 1 – ENABLE: Channel Enable

Writing a '0' to this bit during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

Writing a '1' to this bit will enable the DMA channel.

This bit is not enable-protected.

| Value | Description              |

|-------|--------------------------|

| 0     | DMA channel is disabled. |

| 1     | DMA channel is enabled.  |

## Bit 0 – SWRST: Channel Software Reset

Writing a '0' to this bit has no effect.

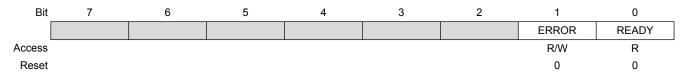

Name: INTFLAG Offset: 0x14 [ID-0000b2c] Reset: 0x00 Property: -

## Bit 1 – ERROR: Error

This flag is set on the occurrence of an NVME, LOCKE or PROGE error.

This bit can be cleared by writing a '1' to its bit location.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | No errors have been received since the last clear.    |

| 1     | At least one error has occurred since the last clear. |

## Bit 0 – READY: NVM Ready

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | The NVM controller is busy programming or erasing.   |

| 1     | The NVM controller is ready to accept a new command. |

# 27.8.7 Status

| Name:       | STATUS             |  |  |  |

|-------------|--------------------|--|--|--|

| Offset:     | 0x18 [ID-00000b2c] |  |  |  |

| Reset:      | 0x0X00             |  |  |  |

| Property: – |                    |  |  |  |

| Bit    | 15 | 14 | 13 | 12   | 11    | 10    | 9    | 8   |

|--------|----|----|----|------|-------|-------|------|-----|

|        |    |    |    |      |       |       |      | SB  |

| Access |    |    |    |      |       |       |      | R   |

| Reset  |    |    |    |      |       |       |      | x   |

|        |    |    |    |      |       |       |      |     |

| Bit    | 7  | 6  | 5  | 4    | 3     | 2     | 1    | 0   |

|        |    |    |    | NVME | LOCKE | PROGE | LOAD | PRM |

| Access |    |    |    | R/W  | R/W   | R/W   | R/W  | R   |

| Reset  |    |    |    | 0    | 0     | 0     | 0    | 0   |

|        |    |    |    | R/W  | R/W   | R/W   |      | R   |

#### Bit 8 – SB: Security Bit Status

| Value | Description                   |

|-------|-------------------------------|

| 0     | The Security bit is inactive. |

| 1     | The Security bit is active.   |

## Bit 4 – NVME: NVM Error

This bit can be cleared by writing a '1' to its bit location.

#### 29.6.2.9 The Overrun Channel n Interrupt

The Overrun Channel n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.OVRn) will be set, and the optional interrupt will be generated in the following cases:

- One or more event users on channel n is not ready when there is a new event.

- An event occurs when the previous event on channel m has not been handled by all event users connected to that channel.

The flag will only be set when using resynchronized paths. In the case of asynchronous path, the INTFLAG.OVRn is always read as zero.

#### 29.6.2.10 The Event Detected Channel n Interrupt

The Event Detected Channel n interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.EVDn) is set when an event coming from the event generator configured on channel n is detected.

The flag will only be set when using a resynchronized path. In the case of asynchronous path, the INTFLAG.EVDn is always zero.

#### 29.6.2.11 Channel Status

The Channel Status register (CHSTATUS) shows the status of the channels when using a synchronous or resynchronized path. There are two different status bits in CHSTATUS for each of the available channels:

- The CHSTATUS.CHBUSYn bit will be set when an event on the corresponding channel n has not been handled by all event users connected to that channel.

- The CHSTATUS.USRRDYn bit will be set when all event users connected to the corresponding channel are ready to handle incoming events on that channel.

#### 29.6.2.12 Software Event

A software event can be initiated on a channel by setting the Channel n bit in the Software Event register (SWEVT.CHANNELn) to '1'. Then the software event can be serviced as any event generator; i.e., when the bit is set to '1', an event will be generated on the respective channel.

#### 29.6.3 Interrupts

The EVSYS has the following interrupt sources:

- Overrun Channel n interrupt (OVRn): for details, refer to The Overrun Channel n Interrupt.

- Event Detected Channel n interrupt (EVDn): for details, refer to The Event Detected Channel n Interrupt.

These interrupts events are asynchronous wake-up sources. See *Sleep Mode Controller*. Each interrupt source has an interrupt flag which is in the Interrupt Flag Status and Clear (INTFLAG) register. The flag is set when the interrupt is issued. Each interrupt event can be individually enabled by setting a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by setting a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt event is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt event works until the interrupt flag is cleared, the interrupt is disabled, or the Event System is reset. See INTFLAG for details on how to clear interrupt flags.

All interrupt events from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to the *Nested Vector Interrupt Controller* for details. The event user must read the INTFLAG register to determine what the interrupt condition is.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

© 2017 Microchip Technology Inc.

| Bit    | 31   | 30      | 29    | 28 | 27 | 26  | 25          | 24  |

|--------|------|---------|-------|----|----|-----|-------------|-----|

| ا<br>م |      |         |       |    |    |     |             |     |

| Access |      |         |       |    |    |     |             |     |

| Reset  |      |         |       |    |    |     |             |     |

| Bit    | 23   | 22      | 21    | 20 | 19 | 18  | 17          | 16  |

|        |      |         |       |    |    |     | RXEN        |     |

| Access |      |         |       |    |    |     | R/W         |     |

| Reset  |      |         |       |    |    |     | 0           |     |

|        |      |         |       |    |    |     |             |     |

| Bit    | 15   | 14      | 13    | 12 | 11 | 10  | 9           | 8   |

|        | AMOD | DE[1:0] | MSSEN |    |    |     | SSDE        |     |

| Access | R/W  | R/W     | R/W   |    |    |     | R/W         |     |

| Reset  | 0    | 0       | 0     |    |    |     | 0           |     |

|        |      |         |       |    |    |     |             |     |

| Bit    | 7    | 6       | 5     | 4  | 3  | 2   | 1           | 0   |

|        |      | PLOADEN |       |    |    |     | CHSIZE[2:0] |     |

| Access |      | R/W     |       |    |    | R/W | R/W         | R/W |

| Reset  |      | 0       |       |    |    | 0   | 0           | 0   |

#### Bit 17 – RXEN: Receiver Enable

Writing '0' to this bit will disable the SPI receiver immediately. The receive buffer will be flushed, data from ongoing receptions will be lost and STATUS.BUFOVF will be cleared.

Writing '1' to CTRLB.RXEN when the SPI is disabled will set CTRLB.RXEN immediately. When the SPI is enabled, CTRLB.RXEN will be cleared, SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the SPI is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                         |

| 1     | The receiver is enabled or it will be enabled when SPI is enabled. |

#### Bits 15:14 – AMODE[1:0]: Address Mode

These bits set the slave addressing mode when the frame format (CTRLA.FORM) with address is used. They are unused in master mode.

| AMODE[1:0] | Name    | Description                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------|

| 0x0        | MASK    | ADDRMASK is used as a mask to the ADDR register                                                               |

| 0x1        | 2_ADDRS | The slave responds to the two unique addresses in ADDR and ADDRMASK                                           |

| 0x2        | RANGE   | The slave responds to the range of addresses between and including ADDR and ADDRMASK. ADDR is the upper limit |

| 0x3        | -       | Reserved                                                                                                      |

# Bit 13 – MSSEN: Master Slave Select Enable

This bit enables hardware slave select  $(\overline{SS})$  control.

Name:INTENCLROffset:0x14 [ID-00000e74]Reset:0x00Property:PAC Write-Protection

| Bit    | 7     | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|-------|---|---|---|-----|-----|-----|-----|

|        | ERROR |   |   |   | SSL | RXC | TXC | DRE |

| Access | R/W   |   |   |   | R/W | R/W | R/W | R/W |

| Reset  | 0     |   |   |   | 0   | 0   | 0   | 0   |

# Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

## Bit 3 – SSL: Slave Select Low Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Slave Select Low Interrupt Enable bit, which disables the Slave Select Low interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Slave Select Low interrupt is disabled. |

| 1     | Slave Select Low interrupt is enabled.  |

## **Bit 2 – RXC: Receive Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

## **Bit 1 – TXC: Transmit Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Transmit Complete Interrupt Enable bit, which disable the Transmit Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

## Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

# 33. SERCOM I<sup>2</sup>C – SERCOM Inter-Integrated Circuit

# 33.1 Overview

The inter-integrated circuit (I<sup>2</sup>C) interface is one of the available modes in the serial communication interface (SERCOM).

The I<sup>2</sup>C interface uses the SERCOM transmitter and receiver configured as shown in Figure 33-1. Labels in capital letters are registers accessible by the CPU, while lowercase labels are internal to the SERCOM.

A SERCOM instance can be configured to be either an I<sup>2</sup>C master or an I<sup>2</sup>C slave. Both master and slave have an interface containing a shift register, a transmit buffer and a receive buffer. In addition, the I<sup>2</sup>C master uses the SERCOM baud-rate generator, while the I<sup>2</sup>C slave uses the SERCOM address match logic.

## **Related Links**

SERCOM – Serial Communication Interface

# 33.2 Features

SERCOM I<sup>2</sup>C includes the following features:

- Master or slave operation

- Can be used with DMA

- Philips I<sup>2</sup>C compatible

- SMBus<sup>™</sup> compatible

- PMBus compatible

- Support of 100kHz and 400kHz, 1MHz and 3.4MHz I<sup>2</sup>C mode

- 4-Wire operation supported

- Physical interface includes:

- Slew-rate limited outputs

- Filtered inputs

- Slave operation:

- Operation in all sleep modes

- Wake-up on address match

- 7-bit and 10-bit Address match in hardware for:

- Unique address and/or 7-bit general call address

- Address range

- Two unique addresses can be used with DMA

#### **Related Links**

Features

| Bit    | 31      | 30   | 29           | 28    | 27       | 26      | 25       | 24     |

|--------|---------|------|--------------|-------|----------|---------|----------|--------|

|        |         |      |              |       |          | FILTER  | VAL[3:0] |        |

| Access |         |      |              |       | R/W      | R/W     | R/W      | R/W    |

| Reset  |         |      |              |       | 0        | 0       | 0        | 0      |

|        |         |      |              |       |          |         |          |        |

| Bit    | 23      | 22   | 21           | 20    | 19       | 18      | 17       | 16     |

|        |         |      |              | BLANK | VAL[7:0] |         |          |        |

| Access | R/W     | R/W  | R/W          | R/W   | R/W      | R/W     | R/W      | R/W    |

| Reset  | 0       | 0    | 0            | 0     | 0        | 0       | 0        | 0      |

|        |         |      |              |       |          |         |          |        |

| Bit    | 15      | 14   | 13           | 12    | 11       | 10      | 9        | 8      |

|        |         |      | CAPTURE[2:0] |       | CHSE     | EL[1:0] | HALT     | Г[1:0] |

| Access |         | R/W  | R/W          | R/W   | R/W      | R/W     | R/W      | R/W    |

| Reset  |         | 0    | 0            | 0     | 0        | 0       | 0        | 0      |

|        |         |      |              |       |          |         |          |        |

| Bit    | 7       | 6    | 5            | 4     | 3        | 2       | 1        | 0      |

|        | RESTART | BLAN | K[1:0]       | QUAL  | KEEP     |         | SRC      | [1:0]  |

| Access | R/W     | R/W  | R/W          | R/W   | R/W      |         | R/W      | R/W    |

| Reset  | 0       | 0    | 0            | 0     | 0        |         | 0        | 0      |

#### Bits 27:24 – FILTERVAL[3:0]: Recoverable Fault n Filter Value

These bits define the filter value applied on MCEx (x=0,1) event input line. The value must be set to zero when MCEx event is used as synchronous event.

#### Bits 23:16 – BLANKVAL[7:0]: Recoverable Fault n Blanking Value

These bits determine the duration of the blanking of the fault input source. Activation and edge selection of the blank filtering are done by the BLANK bits (FCTRLn.BLANK).

When enabled, the fault input source is internally disabled for BLANKVAL\* prescaled GCLK\_TCC periods after the detection of the waveform edge.

#### Bits 14:12 – CAPTURE[2:0]: Recoverable Fault n Capture Action

These bits select the capture and Fault n interrupt/event conditions.

Table 36-8. Fault n Capture Action

| Value | Name    | Description                                                                                                                                                                                                                            |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0   | DISABLE | Capture on valid recoverable Fault n is disabled                                                                                                                                                                                       |

| 0x1   | CAPT    | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0].<br>INTFLAG.FAULTn flag rises on each new captured value.                                                                       |

| 0x2   | CAPTMIN | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0], if COUNT value is lower than the last stored capture value (CC).<br>INTFLAG.FAULTn flag rises on each local minimum detection. |

| 0x3   | CAPTMAX | On rising edge of a valid recoverable Fault n, capture counter value on channel selected by CHSEL[1:0], if COUNT value is higher than the last stored capture value (CC).                                                              |

#### Bit 12 – FAULTA: Recoverable Fault A State

This bit is set by hardware as soon as recoverable Fault A condition occurs.

This bit can be clear by hardware when Fault A action is resumed, or by writing a '1' to this bit when the corresponding FAULTAIN bit is low. If software halt command is enabled (FAULTA.HALT=SW), clearing this bit will release the timer/counter.

#### Bit 11 – FAULT1IN: Non-Recoverable Fault 1 Input

This bit is set while an active Non-Recoverable Fault 1 input is present.

#### Bit 10 – FAULTOIN: Non-Recoverable Fault 0 Input

This bit is set while an active Non-Recoverable Fault 0 input is present.

#### Bit 9 – FAULTBIN: Recoverable Fault B Input

This bit is set while an active Recoverable Fault B input is present.

#### Bit 8 – FAULTAIN: Recoverable Fault A Input

This bit is set while an active Recoverable Fault A input is present.

#### Bit 7 – PERBUFV: Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. This bit is automatically cleared by hardware on UPDATE condition when CTRLB.LUPD is set, or by writing a '1' to this bit.

#### Bit 6 – WAVEBUFV: Waveform Control Buffer Valid

This bit is set when a new value is written to the WAVEBUF register. This bit is automatically cleared by hardware on UPDATE condition when CTRLB.LUPD is set, or by writing a '1' to this bit.

#### Bit 5 – PATTBUFV: Pattern Generator Value Buffer Valid

This bit is set when a new value is written to the PATTBUF register. This bit is automatically cleared by hardware on UPDATE condition when CTRLB.LUPD is set, or by writing a '1' to this bit.

#### Bit 4 – SLAVE: Slave

This bit is set when TCC is set in Slave mode. This bit follows the CTRLA.MSYNC bit state.

#### Bit 3 – DFS: Debug Fault State

This bit is set by hardware in debug mode when DDBGCTRL.FDDBD bit is set. The bit is cleared by writing a '1' to this bit and when the TCC is not in debug mode.

When the bit is set, the counter is halted and the waveforms state depend on DRVCTRL.NRE and DRVCTRL.NRV registers.

#### Bit 2 – UFS: Non-recoverable Update Fault State

This bit is set by hardware when the RAMP index changes and the Lock Update bit is set (CTRLBSET.LUPD). The bit is cleared by writing a one to this bit.

When the bit is set, the waveforms state depend on DRVCTRL.NRE and DRVCTRL.NRV registers.

#### Bit 1 – IDX: Ramp Index

In RAMP2 and RAMP2A operation, the bit is cleared during the cycle A and set during the cycle B. In RAMP1 operation, the bit always reads zero. For details on ramp operations, refer to Ramp Operations.

# 37.7 Register Summary

| Offset | Name     | Bit Pos. |            |             |         |         |                     |             |             |       |  |

|--------|----------|----------|------------|-------------|---------|---------|---------------------|-------------|-------------|-------|--|

| 0x00   | CTRL     | 7:0      |            | RUNSTDBY    |         |         |                     |             | ENABLE      | SWRST |  |

| 0x01   |          |          |            |             |         |         |                     |             |             |       |  |

|        | Reserved |          |            |             |         |         |                     |             |             |       |  |

| 0x03   |          |          |            |             |         |         |                     |             |             |       |  |

| 0x04   | SEQCTRL0 | 7:0      |            |             |         |         |                     | SEQS        | EL[3:0]     |       |  |

| 0x05   | SEQCTRL1 | 7:0      |            |             |         |         |                     | SEQS        | EL[3:0]     |       |  |

| 0x06   |          |          |            |             |         |         |                     |             |             |       |  |

|        | Reserved |          |            |             |         |         |                     |             |             |       |  |

| 0x07   |          |          |            |             |         |         |                     |             |             |       |  |

| 0x08   |          | 7:0      | EDGESEL    |             | FILTS   | EL[1:0] |                     |             | ENABLE      |       |  |

| 0x09   | LUTCTRL0 |          |            | INSELx[3:0] |         |         |                     | INSEL       | INSELx[3:0] |       |  |

| 0x0A   | LUTCINEU | 23:16    |            | LUTEO       | LUTEI   | INVEI   |                     | INSEL       | _x[3:0]     |       |  |

| 0x0B   |          | 31:24    |            | TRUTH[7:0]  |         |         |                     |             |             |       |  |

| 0x0C   |          | 7:0      | EDGESEL    |             | FILTS   | EL[1:0] |                     |             | ENABLE      |       |  |

| 0x0D   | LUTCTRL1 | 15:8     |            | INSEL       | _x[3:0] |         | INSELx[3:0]         |             |             |       |  |

| 0x0E   | LUTCIKET | 23:16    |            | LUTEO       | LUTEI   | INVEI   |                     | INSELx[3:0] |             |       |  |

| 0x0F   |          | 31:24    |            |             |         | TRUT    | <sup>-</sup> H[7:0] |             |             |       |  |

| 0x10   |          | 7:0      | EDGESEL    |             | FILTS   | EL[1:0] |                     |             | ENABLE      |       |  |

| 0x11   | LUTCTRL2 | 15:8     |            | INSEL       | _x[3:0] |         | INSELx[3:0]         |             |             |       |  |

| 0x12   | LUTCIRLZ | 23:16    |            | LUTEO       | LUTEI   | INVEI   |                     | INSEL       | _x[3:0]     |       |  |

| 0x13   |          | 31:24    | TRUTH[7:0] |             |         |         |                     |             |             |       |  |

| 0x14   |          | 7:0      | EDGESEL    |             | FILTS   | EL[1:0] |                     |             | ENABLE      |       |  |

| 0x15   | LUTCTRL3 | 15:8     |            | INSEL       | _x[3:0] |         |                     | INSEL       | _x[3:0]     |       |  |

| 0x16   | LUIUIRLJ | 23:16    |            | LUTEO       | LUTEI   | INVEI   |                     | INSEL       | _x[3:0]     |       |  |

| 0x17   |          | 31:24    |            |             |         | TRUT    | H[7:0]              |             |             |       |  |

# 37.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

# 37.8.1 Control

# 38. ADC – Analog-to-Digital Converter

# 38.1 Overview

The Analog-to-Digital Converter (ADC) converts analog signals to digital values. The ADC has up to 12bit resolution, and is capable of a sampling rate of up to 1MSPS. The input selection is flexible, and both differential and single-ended measurements can be performed. In addition, several internal signal inputs are available. The ADC can provide both signed and unsigned results.

ADC measurements can be started by either application software or an incoming event from another peripheral in the device. ADC measurements can be started with predictable timing, and without software intervention.

Both internal and external reference voltages can be used.

An integrated temperature sensor is available for use with the ADC. The bandgap voltage as well as the scaled I/O and core voltages can also be measured by the ADC.

The ADC has a compare function for accurate monitoring of user-defined thresholds, with minimum software intervention required.

The ADC can be configured for 8-, 10- or 12-bit results. ADC conversion results are provided left- or rightadjusted, which eases calculation when the result is represented as a signed value. It is possible to use DMA to move ADC results directly to memory or peripherals when conversions are done.

The SAM C20/C21 has two ADC instances, ADC0 and ADC1. The two inputs can be sampled simultaneously, as each ADC includes sample and hold circuits.

**Note:** When the Peripheral Touch Controller (PTC) is enabled, ADC0 is serving the PTC exclusively. In this case, ADC0 cannot be used by the user application.

# 38.2 Features

- Two Analog to Digital Converters (ADC) ADC0 and ADC1

- 8-, 10- or 12-bit resolution

- Up to 1,000,000 samples per second (1MSPS)

- Differential and single-ended inputs

- Up to 12 analog inputs per ADC (20 unique channels total)

16 positive and 7 negative, including internal and external

- Internal inputs:

- Bandgap voltage

- Scaled core supply

- Scaled I/O supply

- DAC

- Single, continuous and sequencing options

- Windowing monitor with selectable channel

- Conversion range: V<sub>ref</sub> = [2.0V to VDD<sub>ANA</sub>]

- Built-in internal reference and external reference options

- Event-triggered conversion for accurate timing (one event input)

- Optional DMA transfer of conversion settings or result

| Bit    | 7        | 6 | 5      | 4        | 3 | 2 | 1    | 0       |

|--------|----------|---|--------|----------|---|---|------|---------|

|        | ONREFBUF |   | REFRAN | IGE[1:0] |   |   | REFS | EL[1:0] |

| Access | R/W      |   | R/W    | R/W      |   |   | R/W  | R/W     |

| Reset  | 0        |   | 0      | 0        |   |   | 0    | 0       |

## Bit 7 – ONREFBUF: Reference Buffer On

Turning on the buffer increases the impedance seen on the external reference, so that the current load reduces from  $5\mu$ A to  $0.10\mu$ A. This needs to be matched with whatever type of reference circuit is used.

| Value | Description          |

|-------|----------------------|

| 0     | Reference Buffer Off |

| 1     | Reference Buffer On  |

#### Bits 5:4 – REFRANGE[1:0]: Reference Range

| REFRANGE[1:0] | Reference Voltage  |

|---------------|--------------------|

| 0x0           | Vref < 1.4V        |

| 0x1           | 1.4V < Vref < 2.4V |

| 0x2           | 2.4 < Vref < 3.6V  |

| 0x3           | Vref > 3.6V        |

## Bits 1:0 – REFSEL[1:0]: Reference Selection

These bits select the reference for the ADC.

**Note:** The reference buffer should be enabled (ONREFBUF=1) when using the internal bandgap or DAC output as reference.

| Value | Name             | Description                     |

|-------|------------------|---------------------------------|

| 0x0   | Internal bandgap | Internal 1.024V, 2.048V, 4.096V |

| 0x1   | VREFB pin        | External 1-5.5V                 |

| 0x2   | DAC output       | Internal 1-5.5V                 |

| 0x3   | VDDANA           | Supply 2.7-5.5V                 |

# 39.8.3 Control B

Name:CTRLBOffset:0x02 [ID-0000243d]Reset:0x0000Property:PAC Write-Protection, Enable-Protected

#### Bit 1 – OVERRUN: Overrun

This flag is cleared by writing a one to the flag.

This flag is set if RESULT is written before the previous value has been read by CPU, and an interrupt request will be generated if INTENCLR/SET.OVERRUN is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Overrun interrupt flag.

#### Bit 0 – RESRDY: Result Ready

This flag is cleared by writing a one to the flag or by reading the RESULT register.

This flag is set when the conversion result is available, and an interrupt will be generated if INTENCLR/ SET.RESRDY is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the Result Ready interrupt flag.

## 39.8.8 Sequence Status

Name:

SEQSTATUS

Offset:

0x08 [ID-0000243d]

Reset:

0x00

Property:

| Bit    | 7       | 6 | 5 | 4 | 3 | 2     | 1        | 0 |

|--------|---------|---|---|---|---|-------|----------|---|

| ſ      | SEQBUSY |   |   |   |   | SEQST | ATE[3:0] |   |

| Access | R       |   |   |   | R | R     | R        | R |

| Reset  | 0       |   |   |   | 0 | 0     | 0        | 0 |

#### Bit 7 – SEQBUSY: Sequence busy

This bit is set when the sequence start.

This bit is clear when the last conversion in a sequence is done.

#### Bits 3:0 - SEQSTATE[3:0]: Sequence State

This bit field is the pointer of sequence. This value identifies the last conversion done in the sequence.

## 39.8.9 Input Control

Name:INPUTCTRLOffset:0x09 [ID-0000243d]Reset:0x00Property:PAC Write-Protection, Write-Synchronized

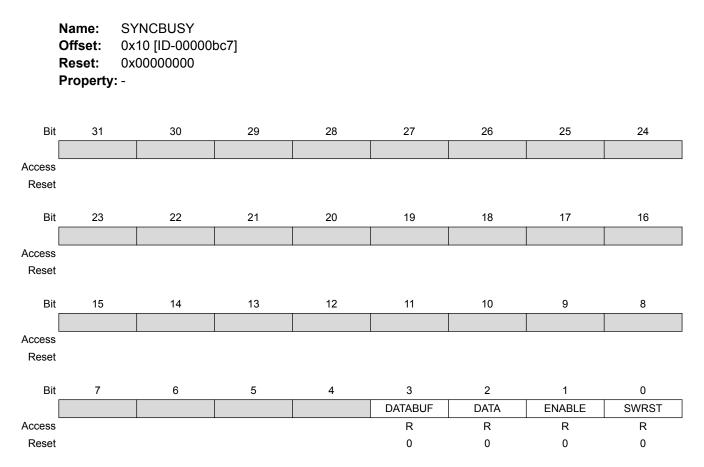

## 41.8.10 Synchronization Busy

## Bit 3 – DATABUF: Data Buffer DAC0

This bit is set when DATABUF register is written.

This bit is cleared when DATABUF synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

## Bit 2 – DATA: Data

This bit is set when DATA register is written.

This bit is cleared when DATA synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

# Bit 1 – ENABLE: DAC Enable Status

This bit is set when CTRLA.ENABLE bit is written.

This bit is cleared when CTRLA.ENABLE synchronization is completed.

# 48. Packaging Information

Table 48-1. Thermal Resistance Data

# 48.1 Thermal Considerations

## 48.1.1 Thermal Resistance Data

The following table summarizes the thermal resistance data depending on the package.

| Package Type  | θ <sub>JA</sub> | θ <sub>JC</sub> |

|---------------|-----------------|-----------------|

| 32-pin TQFP   | 63.1°C/W        | 14.3°C/W        |

| 48-pin TQFP   | 62.7°C/W        | 11.6°C/W        |

| 64-pin TQFP   | 56.3°C/W        | 11.1°C/W        |

| 100-pin TQFP  | 55.0°C/W        | 11.1°C/W        |

| 32-pin QFN    | 40.5°C/W        | 16.0°C/W        |

| 48-pin QFN    | 30.9°C/W        | 10.4°C/W        |

| 64-pin QFN    | 31.4°C/W        | 10.2°C/W        |

| 56-ball WLCSP | 37.5°C/W        | 5.48°C/W        |

#### 48.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- $\theta_{JA}$  = Package thermal resistance, Junction-to-ambient (°C/W), see Thermal Resistance Data

- $\theta_{JC}$  = Package thermal resistance, Junction-to-case thermal resistance (°C/W), see Thermal Resistance Data

- θ<sub>HEATSINK</sub> = Thermal resistance (°C/W) specification of the external cooling device

- P<sub>D</sub> = Device power consumption (W)

- T<sub>A</sub> = Ambient temperature (°C)

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

# 48.2 Package Drawings

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a>.