Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20j17a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

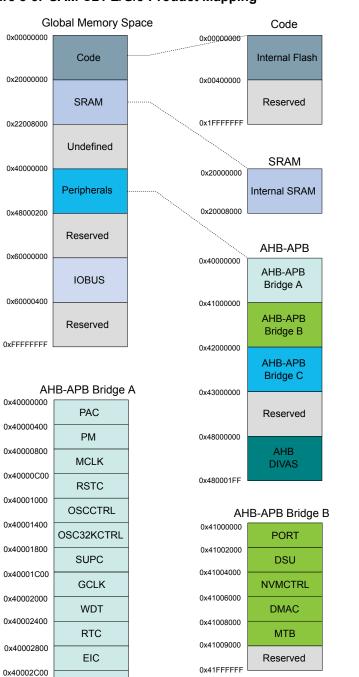

## Figure 8-3. SAM C21 E/G/J Product Mapping

| AHB-APB Bridge C         |          |  |  |  |

|--------------------------|----------|--|--|--|

| 0x42000000               | EVSYS    |  |  |  |

| 0x42000400               | SERCOM0  |  |  |  |

| 0x42000800               | SERCOM1  |  |  |  |

| 0x42000C00               | SERCOM2  |  |  |  |

| 0x42001000               | SERCOM3  |  |  |  |

| 0x42001400               | SERCOM4  |  |  |  |

| 0x42001800               | SERCOM5  |  |  |  |

| 0x42001C00               | CAN0     |  |  |  |

| 0x42002000               | CAN1     |  |  |  |

| 0x42002400               | TCC0     |  |  |  |

| 0x42002800               | TCC1     |  |  |  |

| 0x42002C00               | TCC2     |  |  |  |

| 0x42003000               | TC0      |  |  |  |

| 0x42003400               | TC1      |  |  |  |

| 0x42003800               | TC2      |  |  |  |

| 0x42003C00               | TC3      |  |  |  |

| 0x42004000               | TC4      |  |  |  |

| 0x42004400               | ADC0     |  |  |  |

| 0x42004800               | ADC1     |  |  |  |

| 0x42004C00               | SDADC    |  |  |  |

| 0x42005000               | AC       |  |  |  |

| 0x42005400               | DAC      |  |  |  |

| 0x42005800               | PTC      |  |  |  |

| 0x42005C00               | CCL      |  |  |  |

| 0x42006000<br>0x42FFFFFF | Reserved |  |  |  |

|                          |          |  |  |  |

0x40003000

0x40003400

0x40FFFFFF

FREQM

**TSENS**

Reserved

| AMOD[1:0] | Short name | External range restrictions                                                                                                                 |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0         | ARRAY      | CRC32 is restricted to the full Flash array area (EEPROM emulation area not included) DATA forced to 0xFFFFFFF before calculation (no seed) |

| 1         | EEPROM     | CRC32 of the whole EEPROM emulation area DATA forced to 0xFFFFFFF before calculation (no seed)                                              |

| 2-3       | Reserved   |                                                                                                                                             |

Table 13-3. AMOD Bit Descriptions when Operating CRC32

The algorithm employed is the industry standard CRC32 algorithm using the generator polynomial 0xEDB88320 (reversed representation).

#### 13.11.3.1 Starting CRC32 Calculation

CRC32 calculation for a memory range is started after writing the start address into the Address register (ADDR) and the size of the memory range into the Length register (LENGTH). Both must be word-aligned.

The initial value used for the CRC32 calculation must be written to the Data register (DATA). This value will usually be 0xFFFFFFF, but can be, for example, the result of a previous CRC32 calculation if generating a common CRC32 of separate memory blocks.

Once completed, the calculated CRC32 value can be read out of the Data register. The read value must be complemented to match standard CRC32 implementations or kept non-inverted if used as starting point for subsequent CRC32 calculations.

If the device is in protected state by the NVMCTRL security bit, it is only possible to calculate the CRC32 of the whole flash array when operated from the external address space. In most cases, this area will be the entire onboard non-volatile memory. The Address, Length and Data registers will be forced to predefined values once the CRC32 operation is started, and values written by the user are ignored. This allows the user to verify the contents of a protected device.

The actual test is started by writing a '1' in the 32-bit Cyclic Redundancy Check bit of the Control register (CTRL.CRC). A running CRC32 operation can be canceled by resetting the module (writing '1' to CTRL.SWRST).

#### Related Links

NVMCTRL – Non-Volatile Memory Controller Security Bit

## 13.11.3.2 Interpreting the Results

The user should monitor the Status A register. When the operation is completed, STATUSA.DONE is set. Then the Bus Error bit of the Status A register (STATUSA.BERR) must be read to ensure that no bus error occurred.

#### 13.11.4 Debug Communication Channels

The Debug Communication Channels (DCCO and DCC1) consist of a pair of registers with associated handshake logic, accessible by both CPU and debugger even if the device is protected by the NVMCTRL security bit. The registers can be used to exchange data between the CPU and the debugger, during run time as well as in debug mode. This enables the user to build a custom debug protocol using only these registers.

| CPU Clock Domain  |               |  |  |  |  |

|-------------------|---------------|--|--|--|--|

| Peripheral Clock  | Default State |  |  |  |  |

| CLK_ADC1_APB      | Disabled      |  |  |  |  |

| CLK_BRIDGE_A_AHB  | Enabled       |  |  |  |  |

| CLK_BRIDGE_B_AHB  | Enabled       |  |  |  |  |

| CLK_BRIDGE_C_AHB  | Enabled       |  |  |  |  |

| CLK_BRIDGE_D_AHB  | Enabled       |  |  |  |  |

| CLK_CAN0_AHB      | Disabled      |  |  |  |  |

| CLK_CAN1_AHB      | Disabled      |  |  |  |  |

| CLK_CCL_APB       | Disabled      |  |  |  |  |

| CLK_DAC_APB       | Disabled      |  |  |  |  |

| CLK_DIVAS_AHB     | Enabled       |  |  |  |  |

| CLK_DMAC_AHB      | Enabled       |  |  |  |  |

| CLK_DMAC_APB      | Enabled       |  |  |  |  |

| CLK_DSU_AHB       | Enabled       |  |  |  |  |

| CLK_DSU_APB       | Enabled       |  |  |  |  |

| CLK_EIC_APB       | Enabled       |  |  |  |  |

| CLK_EVSYS_APB     | Disabled      |  |  |  |  |

| CLK_FREQM_APB     | Enabled       |  |  |  |  |

| CLK_GCLK_AHB      | Enabled       |  |  |  |  |

| CLK_HAMATRIX_APB  | Disabled      |  |  |  |  |

| CLK_MCLK_APB      | Enabled       |  |  |  |  |

| CLK_MTB_APB       | Enabled       |  |  |  |  |

| CLK_NVMCTRL_AHB   | Enabled       |  |  |  |  |

| CLK_NVMCTRL_APB   | Enabled       |  |  |  |  |

| CLK_OSCCTRL_APB   | Enabled       |  |  |  |  |

| CLK_OSC32CTRL_APB | Enabled       |  |  |  |  |

| CLK_PAC_AHB       | Enabled       |  |  |  |  |

| CLK_PAC_APB       | Enabled       |  |  |  |  |

| CLK_PORT_APB      | Enabled       |  |  |  |  |

| CLK_PTC_APB       | Disabled      |  |  |  |  |

| CLK_SDADC_APB     | Disabled      |  |  |  |  |

| CLK_SERCOM0_APB   | Disabled      |  |  |  |  |

#### Bit 8 – DPLLLCKR: DPLL Lock Rise Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the DPLL Lock Rise Interrupt Enable bit, which enables the DPLL Lock Rise interrupt.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Rise interrupt is disabled.                                                |

| 1     | The DPLL Lock Rise interrupt is enabled, and an interrupt request will be generated when |

|       | the DPLL Lock Rise Interrupt flag is set.                                                |

## Bit 4 – OSC48MRDY: OSC48M Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the OSC48M Ready Interrupt Enable bit, which enables the OSC48M Ready interrupt.

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OSC48M Ready interrupt is disabled.                                                                                        |

| 1     | The OSC48M Ready interrupt is enabled, and an interrupt request will be generated when the OSC48M Ready Interrupt flag is set. |

## Bit 1 – CLKFAIL: XOSC Clock Failure Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the XOSC Clock Failure Interrupt Enable bit, which enables the XOSC Clock Failure Interrupt.

| Value | Description                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC Clock Failure Interrupt is disabled.                                                                                              |

| 1     | The XOSC Clock Failure Interrupt is enabled, and an interrupt request will be generated when the XOSC Clock Failure Interrupt flag is set. |

## Bit 0 – XOSCRDY: XOSC Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the XOSC Ready Interrupt Enable bit, which enables the XOSC Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC Ready interrupt is disabled.                                                                                      |

| 1     | The XOSC Ready interrupt is enabled, and an interrupt request will be generated when the XOSC Ready Interrupt flag is set. |

#### 20.8.3 Interrupt Flag Status and Clear

Name:

INTFLAG

Offset:

0x08 [ID-00001eee]

Reset:

0x00000000

Property:

Name:SYNCBUSYOffset:0x04Reset:0x0000000Property:-

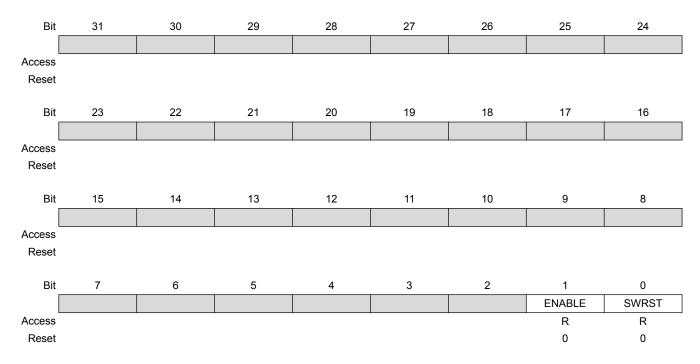

## Bit 1 – ENABLE: Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

## Bit 0 – SWRST: Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

## 26.8.5 Event Control

Name:EVCTRLOffset:0x08Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   |

|--------|------|------|------|------|------|------|------|------|

|        |      |      |      |      | EVDn | EVDn | EVDn | EVDn |

| Access |      |      |      |      | R/W  | R/W  | R/W  | R/W  |

| Reset  |      |      |      |      | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|        | EVDn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|        |      |      |      |      | OVRn | OVRn | OVRn | OVRn |

| Access |      |      |      |      | R/W  | R/W  | R/W  | R/W  |

| Reset  |      |      |      |      | 0    | 0    | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | OVRn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Bits 27:16 – EVDn: Event Detected Channel n Interrupt Enable [n = 11..0]

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Event Detected Channel n Interrupt Enable bit, which enables the Event Detected Channel n interrupt.

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | The Event Detected Channel n interrupt is disabled. |

| 1     | The Event Detected Channel n interrupt is enabled.  |

## Bits 11:0 – OVRn: Overrun Channel n Interrupt Enable [n = 11..0]

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Overrun Channel n Interrupt Enable bit, which disables the Overrun Channel n interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Overrun Channel n interrupt is disabled. |

| 1     | The Overrun Channel n interrupt is enabled.  |

## **Related Links**

PAC - Peripheral Access Controller

## 29.8.5 Interrupt Flag Status and Clear

Name:

INTFLAG

Offset:

0x18 [ID-0000120d]

Reset:

0x00000000

Property:

–

# SAM C20/C21

| Value     | Channel Number             |

|-----------|----------------------------|

| 0x00      | No channel output selected |

| 0x01      | 0                          |

| 0x02      | 1                          |

| 0x03      | 2                          |

| 0x04      | 3                          |

| 0x05      | 4                          |

| 0x06      | 5                          |

| 0x07      | 6                          |

| 0x08      | 7                          |

| 0x09      | 8                          |

| 0x0A      | 9                          |

| 0x0B      | 10                         |

| 0x0C      | 11                         |

| 0x0D-0xFF | Reserved                   |

## Table 29-3. User Multiplexer Number

| USERm | User Multiplexer       | Description        | Path Type                                                            |

|-------|------------------------|--------------------|----------------------------------------------------------------------|

| m = 0 | TSENS<br>STARTReserved | Start measurement- | Asynchronous,<br>synchronous, and<br>resynchronized<br>pathsReserved |

| m = 1 | PORT EV0               | Event 0            | Asynchronous path only                                               |

| m = 2 | PORT EV1               | Event 1            | Asynchronous path only                                               |

| m = 3 | PORT EV2               | Event 2            | Asynchronous path only                                               |

| m = 4 | PORT EV3               | Event 3            | Asynchronous path only                                               |

| m = 5 | DMAC CH0               | Channel 0          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 6 | DMAC CH1               | Channel 1          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 7 | DMAC CH2               | Channel 2          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 8 | DMAC CH3               | Channel 3          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

#### 31.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

#### 31.5.9 Analog Connections

Not applicable.

## 31.6 Functional Description

#### 31.6.1 Principle of Operation

The USART uses the following lines for data transfer:

- RxD for receiving

- TxD for transmitting

- XCK for the transmission clock in synchronous operation

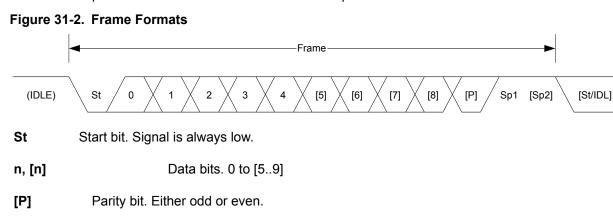

USART data transfer is frame based. A serial frame consists of:

- 1 start bit

- From 5 to 9 data bits (MSB or LSB first)

- No, even or odd parity bit

- 1 or 2 stop bits

A frame starts with the start bit followed by one character of data bits. If enabled, the parity bit is inserted after the data bits and before the first stop bit. After the stop bit(s) of a frame, either the next frame can follow immediately, or the communication line can return to the idle (high) state. The figure below illustrates the possible frame formats. Brackets denote optional bits.

Name:INTENCLROffset:0x14 [ID-00000e74]Reset:0x00Property:PAC Write-Protection

| Bit    | 7     | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|-------|---|---|---|-----|-----|-----|-----|

|        | ERROR |   |   |   | SSL | RXC | TXC | DRE |

| Access | R/W   |   |   |   | R/W | R/W | R/W | R/W |

| Reset  | 0     |   |   |   | 0   | 0   | 0   | 0   |

## Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

## Bit 3 – SSL: Slave Select Low Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Slave Select Low Interrupt Enable bit, which disables the Slave Select Low interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Slave Select Low interrupt is disabled. |

| 1     | Slave Select Low interrupt is enabled.  |

## **Bit 2 – RXC: Receive Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

## **Bit 1 – TXC: Transmit Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Transmit Complete Interrupt Enable bit, which disable the Transmit Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

## Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | SWRST synchronization is not busy. |

| 1     | SWRST synchronization is busy.     |

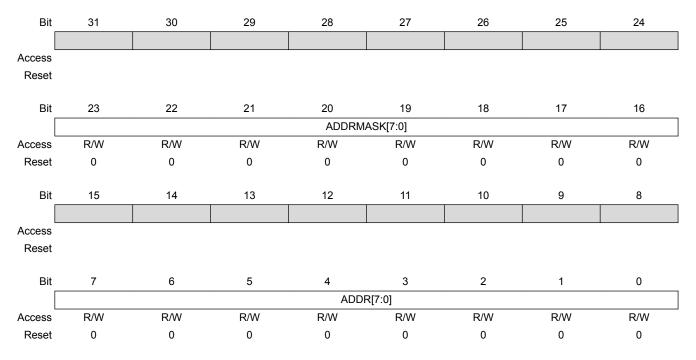

#### 32.8.9 Address

Name:ADDROffset:0x24 [ID-0000e74]Reset:0x0000000Property:PAC Write-Protection, Enable-Protected

#### Bits 23:16 – ADDRMASK[7:0]: Address Mask

These bits hold the address mask when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

#### Bits 7:0 - ADDR[7:0]: Address

These bits hold the address when the transaction format with address is used (CTRLA.FORM, CTRLB.AMODE).

## 32.8.10 Data

Name:

DATA

Offset:

0x28 [ID-00000e74]

Reset:

0x0000

Property:

–

To leave low power mode, CLK\_CANx\_APB and GCLK\_CANx must be active before writing CCCR.CSR to '0'. The CAN will acknowledge this by resetting CCCR.CSA = 0. Afterwards, the application can restart CAN communication by resetting bit CCCR.INIT.

## 34.6.10 Synchronization

Due to the asynchronicity between the main clock domain (CLK\_CAN\_APB) and the peripheral clock domain (GCLK\_CAN) some registers are synchronized when written. When a write-synchronized register is written, the read back value will not be updated until the register has completed synchronization.

The following bits and registers are write-synchronized:

I Initialization bit in CC Control register (CCCR.INIT)

- Drive Control register (DRVCTRL)

- Wave register (WAVE)

- Event Control register (EVCTRL)

Enable-protected bits in the CTRLA register can be written at the same time as CTRLA.ENABLE is written to '1', but not at the same time as CTRLA.ENABLE is written to '0'. Enable-protection is denoted by the "Enable-Protected" property in the register description.

Before enabling the TC, the peripheral must be configured by the following steps:

- 1. Enable the TC bus clock (CLK\_TCx\_APB).

- 2. Select 8-, 16- or 32-bit counter mode via the TC Mode bit group in the Control A register (CTRLA.MODE). The default mode is 16-bit.

- 3. Select one wave generation operation in the Waveform Generation Operation bit group in the WAVE register (WAVE.WAVEGEN).

- 4. If desired, the GCLK\_TCx clock can be prescaled via the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

- If the prescaler is used, select a prescaler synchronization operation via the Prescaler and Counter Synchronization bit group in the Control A register (CTRLA.PRESYNC).

- 5. If desired, select one-shot operation by writing a '1' to the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT).

- 6. If desired, configure the counting direction 'down' (starting from the TOP value) by writing a '1' to the Counter Direction bit in the Control B register (CTRLBSET.DIR).

- 7. For capture operation, enable the individual channels to capture in the Capture Channel x Enable bit group in the Control A register (CTRLA.CAPTEN).

- 8. If desired, enable inversion of the waveform output or IO pin input signal for individual channels via the Invert Enable bit group in the Drive Control register (DRVCTRL.INVEN).

#### 35.6.2.2 Enabling, Disabling, and Resetting

The TC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The TC is disbled by writing a zero to CTRLA.ENABLE.

The TC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the TC, except DBGCTRL, will be reset to their initial state. Refer to the CTRLA register for details.

The TC should be disabled before the TC is reset in order to avoid undefined behavior.

#### 35.6.2.3 Prescaler Selection

The GCLK\_TCx is fed into the internal prescaler.

The prescaler consists of a counter that counts up to the selected prescaler value, whereupon the output of the prescaler toggles.

If the prescaler value is higher than one, the counter update condition can be optionally executed on the next GCLK\_TCx clock pulse or the next prescaled clock pulse. For further details, refer to Prescaler (CTRLA.PRESCALER) and Counter Synchronization (CTRLA.PRESYNC) description.

Prescaler outputs from 1 to 1/1024 are available. For a complete list of available prescaler outputs, see the register description for the Prescaler bit group in the Control A register (CTRLA.PRESCALER).

**Note:** When counting events, the prescaler is bypassed.

The joint stream of prescaler ticks and event action ticks is called CLK\_TC\_CNT.

# SAM C20/C21

| Offset | Name   | Bit Pos. |               |

|--------|--------|----------|---------------|

| 0x2F   |        | 31:24    | PERBUF[31:24] |

| 0x30   |        | 7:0      | CCBUF[7:0]    |

| 0x31   | CCBUF0 | 15:8     | CCBUF[15:8]   |

| 0x32   |        | 23:16    | CCBUF[23:16]  |

| 0x33   |        | 31:24    | CCBUF[31:24]  |

| 0x34   |        | 7:0      | CCBUF[7:0]    |

| 0x35   | CCBUF1 | 15:8     | CCBUF[15:8]   |

| 0x36   |        | 23:16    | CCBUF[23:16]  |

| 0x37   |        | 31:24    | CCBUF[31:24]  |

#### 35.7.3.1 Control A

Name:CTRLAOffset:0x00Reset:0x00000000Property:PAC Write-Protection, Write-Synchronized, Enable-Protected

| Bit    | 31       | 30       | 29     | 28             | 27    | 26     | 25             | 24      |

|--------|----------|----------|--------|----------------|-------|--------|----------------|---------|

|        |          |          |        | CAPTMODE1[1:0] |       |        | CAPTMODE0[1:0] |         |

| Access |          |          |        | R/W            | R/W   |        | R/W            | R/W     |

| Reset  |          |          |        | 0              | 0     |        | 0              | 0       |

|        |          |          |        |                |       |        |                |         |

| Bit    | 23       | 22       | 21     | 20             | 19    | 18     | 17             | 16      |

|        |          |          | COPEN1 | COPEN0         |       |        | CAPTEN1        | CAPTEN0 |

| Access |          |          | R/W    | R/W            |       |        | R/W            | R/W     |

| Reset  |          |          | 0      | 0              |       |        | 0              | 0       |

|        |          |          |        |                |       |        |                |         |

| Bit    | 15       | 14       | 13     | 12             | 11    | 10     | 9              | 8       |

|        |          |          |        |                | ALOCK | F      | PRESCALER[2:0] |         |

| Access |          |          |        |                | R/W   | R/W    | R/W            | R/W     |

| Reset  |          |          |        |                | 0     | 0      | 0              | 0       |

|        |          |          |        |                |       |        |                |         |

| Bit    | 7        | 6        | 5      | 4              | 3     | 2      | 1              | 0       |

|        | ONDEMAND | RUNSTDBY | PRESCS | YNC[1:0]       | MOD   | E[1:0] | ENABLE         | SWRST   |

| Access | R/W      | R/W      | R/W    | R/W            | R/W   | R/W    | R/W            | W       |

| Reset  | 0        | 0        | 0      | 0              | 0     | 0      | 0              | 0       |

Bits 28:27 – CAPTMODE1[1:0]: Capture mode Channel 1

These bits select the channel 1 capture mode.

| Value | Name    | Description     |

|-------|---------|-----------------|

| 0x0   | DEFAULT | Default capture |

| 0x1   | CAPTMIN | Minimum capture |

| 0x2   | CAPTMAX | Maximum capture |

| 0x3   |         | Reserved        |

## Bits 25:24 – CAPTMODE0[1:0]: Capture mode Channel 0

These bits select the channel 0 capture mode.

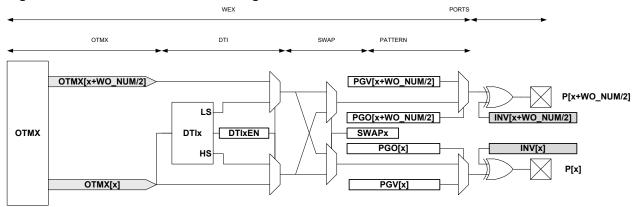

#### Figure 36-33. Waveform Extension Stage Details

**The output matrix (OTMX)** unit distributes compare channels, according to the selectable configurations in Table 36-4.

| Table 36-4 | Output Matrix | <b>Channel Pin</b> | Routing | Configuration |

|------------|---------------|--------------------|---------|---------------|

|------------|---------------|--------------------|---------|---------------|

| Value |     |     |     | ΟΤΝ | IX[x] |     |     |     |

|-------|-----|-----|-----|-----|-------|-----|-----|-----|

| 0x0   | CC3 | CC2 | CC1 | CC0 | CC3   | CC2 | CC1 | CC0 |

| 0x1   | CC1 | CC0 | CC1 | CC0 | CC1   | CC0 | CC1 | CC0 |

| 0x2   | CC0 | CC0 | CC0 | CC0 | CC0   | CC0 | CC0 | CC0 |

| 0x3   | CC1 | CC1 | CC1 | CC1 | CC1   | CC1 | CC1 | CC0 |

Notes on Table 36-4:

- Configuration 0x0 is the default configuration. The channel location is the default one, and channels are distributed on outputs modulo the number of channels. Channel 0 is routed to the Output matrix output OTMX[0], and Channel 1 to OTMX[1]. If there are more outputs than channels, then channel 0 is duplicated to the Output matrix output OTMX[CC\_NUM], channel 1 to OTMX[CC\_NUM+1] and so on.

- Configuration 0x1 distributes the channels on output modulo half the number of channels. This

assigns twice the number of output locations to the lower channels than the default configuration.

This can be used, for example, to control the four transistors of a full bridge using only two compare

channels.

Using pattern generation, some of these four outputs can be overwritten by a constant level, enabling flexible drive of a full bridge in all quadrant configurations.

- Configuration 0x2 distributes compare channel 0 (CC0) to all port pins. With pattern generation, this configuration can control a stepper motor.

- Configuration 0x3 distributes the compare channel CC0 to the first output, and the channel CC1 to all other outputs. Together with pattern generation and the fault extension, this configuration can control up to seven LED strings, with a boost stage.

| Value | ОТМХ[3] | ОТМХ[2] | ОТМХ[1] | ОТМХ[0] |

|-------|---------|---------|---------|---------|

| 0x0   | CC3     | CC2     | CC1     | CC0     |

| 0x1   | CC1     | CC0     | CC1     | CC0     |

## Table 36-5. Example: four compare channels on four outputs

#### Analog-to-Digital Converter (ADC) Characteristics

## 38.6.2.6 ADC Resolution

The ADC supports 8-bit, 10-bit or 12-bit resolution. Resolution can be changed by writing the Resolution bit group in the Control C register (CTRLC.RESSEL). By default, the ADC resolution is set to 12 bits. The resolution affects the propagation delay, see also Conversion Timing and Sampling Rate.

#### 38.6.2.7 Differential and Single-Ended Conversions

The ADC has two conversion options: differential and single-ended:

If the positive input is always positive, the single-ended conversion should be used in order to have full 12-bit resolution in the conversion.

If the positive input may go below the negative input, the differential mode should be used in order to get correct results.

The differential mode is enabled by setting DIFFMODE bit in the Control C register (CTRLC.DIFFMODE). Both conversion types could be run in single mode or in free-running mode. When the free-running mode is selected, an ADC input will continuously sample the input and performs a new conversion. The INTFLAG.RESRDY bit will be set at the end of each conversion.

#### 38.6.2.8 Conversion Timing and Sampling Rate

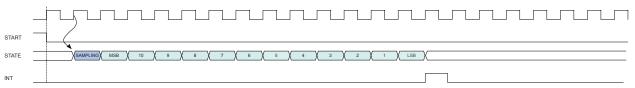

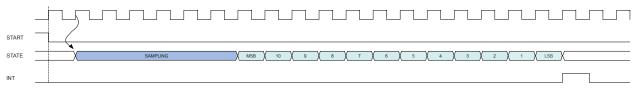

The following figure shows the ADC timing for one single conversion. A conversion starts after the software or event start are synchronized with the GCLK\_ADCx clock. The input channel is sampled in the first half CLK\_ADCx period.

#### Figure 38-3. ADC Timing for One Conversion in 12-bit Resolution

The sampling time can be increased by using the Sampling Time Length bit group in the Sampling Time Control register (SAMPCTRL.SAMPLEN). As example, the next figure is showing the timing conversion with sampling time increased to six CLK\_ADC cycles.

#### Figure 38-4. ADC Timing for One Conversion with Increased Sampling Time, 12-bit

The ADC provides also offset compensation, see the following figure. The offset compensation is enabled by the Offset Compensation bit in the Sampling Control register (SAMPCTRL.OFFCOMP).

Note: If offset compensation is used, the sampling time must be set to one cycle of CLK\_ADCx.

In free running mode, the sampling rate R<sub>S</sub> is calculated by

$R_{S} = f_{CLK\_ADC} / (n_{SAMPLING} + n_{OFFCOMP} + n_{DATA})$

Here,  $n_{SAMPLING}$  is the sampling duration in CLK\_ADC cycles,  $n_{OFFCOMP}$  is the offset compensation duration in clock cycles, and  $n_{DATA}$  is the bit resolution.  $f_{CLK\_ADC}$  is the ADC clock frequency from the internal prescaler:  $f_{CLK\_ADC} = f_{GCLK\_ADC} / 2^{(1 + CTRLB.PRESCALER)}$

| Value     | Name    | Description                      |

|-----------|---------|----------------------------------|

| 0x0       | DISABLE | No window mode (default)         |

| 0x1       | ABOVE   | RESULT > WINLT                   |

| 0x2       | BELOW   | RESULT < WINUT                   |

| 0x3       | INSIDE  | WINLT < RESULT < WINUT           |

| 0x4       | OUTSIDE | WINUT < RESULT or RESULT < WINLT |

| 0x5 - 0x7 |         | Reserved                         |

## 39.8.12 Window Monitor Lower Threshold

- Name: WINLT

- Offset: 0x0C [ID-0000243d]

- **Reset:** 0x0000000

- Property: PAC Write-Protection, Write-Synchronized

| Bit    | 31  | 30  | 29  | 28    | 27      | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|---------|-----|-----|-----|

|        |     |     |     |       |         |     |     |     |

| Access |     |     |     |       |         |     |     |     |

| Reset  |     |     |     |       |         |     |     |     |

|        |     |     |     |       |         |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19      | 18  | 17  | 16  |

|        |     |     |     | WINLT | [23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |     |     |       |         |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11      | 10  | 9   | 8   |

|        |     |     |     | WINL  | [15:8]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

|        |     |     |     |       |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3       | 2   | 1   | 0   |

|        |     |     |     | WINL  | T[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0       | 0   | 0   | 0   |

## Bits 23:0 – WINLT[23:0]: Window Lower Threshold

If the window monitor is enabled, these bits define the lower threshold value.

## 39.8.13 Window Monitor Upper Threshold

Name:WINUTOffset:0x10 [ID-0000243d]Reset:0x0000000Property:PAC Write-Protection, Write-Synchronized

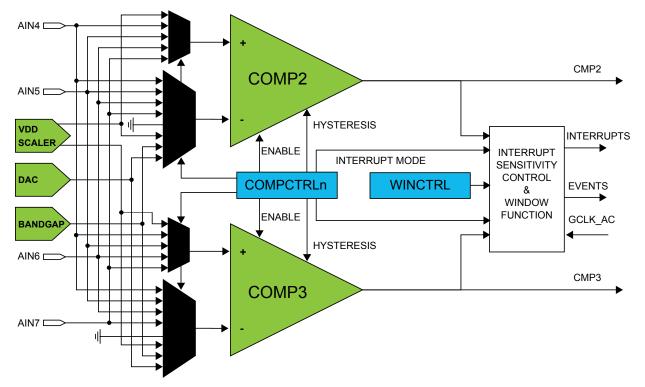

Figure 40-2. Analog Comparator Block Diagram (Second Pair)

# 40.4 Signal Description

| Signal  | Description    | Туре               |

|---------|----------------|--------------------|

| AIN[70] | Analog input   | Comparator inputs  |

| CMP[20] | Digital output | Comparator outputs |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

#### **Related Links**

I/O Multiplexing and Considerations

## 40.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 40.5.1 I/O Lines

Using the AC's I/O lines requires the I/O pins to be configured. Refer to *PORT - I/O Pin Controller* for details.

#### **Related Links**

PORT: IO Pin Controller

#### Bit 0 – SWRST: Software Reset Busy

This bit is cleared when the synchronization of CTRLA.SWRST is complete.

This bit is set when the synchronization of CTRLA.SWRST is started.

## 43.8.10 Value

Name:

VALUE

Offset:

0x0C [ID-00001f13]

Reset:

0x0000

Property:

| Bit    | 31         | 30 | 29 | 28    | 27      | 26 | 25 | 24 |

|--------|------------|----|----|-------|---------|----|----|----|

|        |            |    |    |       |         |    |    |    |

| Access |            |    |    |       |         |    |    |    |

| Reset  |            |    |    |       |         |    |    |    |

|        |            |    |    |       |         |    |    |    |

| Bit    | 23         | 22 | 21 | 20    | 19      | 18 | 17 | 16 |

|        |            |    |    | VALUE | [23:16] |    |    |    |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |            |    |    |       |         |    |    |    |

| Bit    | 15         | 14 | 13 | 12    | 11      | 10 | 9  | 8  |

|        |            |    |    | VALUE | E[15:8] |    |    |    |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |            |    |    |       |         |    |    |    |

| Bit    | 7          | 6  | 5  | 4     | 3       | 2  | 1  | 0  |

|        | VALUE[7:0] |    |    |       |         |    |    |    |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |

|        |            |    |    |       |         |    |    |    |

## Bits 23:0 – VALUE[23:0]: Measurement Value

Result from measurement. This VALUE is in two's complement format.

**Example:** If the TSENS GAIN and OFFSET registers are setup with values stored in the NVM Temperature Calibration Area (Refer to Table 9-7), the TSENS resolution is set at 100 which will result in the following values

| Temperature | VALUE            |

|-------------|------------------|

| T = 25°C    | 2500 = 0x09C4    |

| T = -25°C   | -2500 = 0xFFF63C |

## 43.8.11 Window Monitor Lower Threshold

# SAM C20/C21

| Symbol Parameter    |                              | Conditions                             | Conditions                                   |      |        | Measurement |    |  |  |

|---------------------|------------------------------|----------------------------------------|----------------------------------------------|------|--------|-------------|----|--|--|

|                     |                              |                                        |                                              |      |        | Мах         |    |  |  |

|                     |                              | Fadc = 1 Msps - R2R disabled with gain | Vddana=2.7V Vref=2.0V                        | -    | +/-0.3 | +/-0.8      |    |  |  |

|                     |                              | compensation                           | Vddana=5.0V<br>Vref=Vddana/2                 | -    | +/-0.1 | +/-0.5      |    |  |  |

| Offset Offset Error | Fadc = 1 Msps - R2R disabled | Vddana=5.0V Vref=Vddana                | -                                            | +/-7 | +/-63  | mV          |    |  |  |

|                     |                              | Vddana=2.7V Vref=2.0V                  | -                                            | +/-7 | +/-64  |             |    |  |  |

| SFDR                |                              | Spurious Free Dynamic Range            | Fs = 1Msps / Fin = 14                        | 57   | 66     | 73          | dB |  |  |

| SINAD(1)            |                              | Signal to Noise and Distortion ratio   | kHz / Full range Input<br>signal Vddana=5.0V | 54   | 59     | 62          |    |  |  |

| SNR at -3 db<br>FS  |                              | Signal to Noise ratio                  | Vref=Vddana                                  | 57   | 60     | 62          |    |  |  |

| THD                 |                              | Total Harmonic Distortion              |                                              | -71  | -64    | -56         |    |  |  |

|                     |                              | Noise RMS                              | External Reference voltage                   | -    | 0.6    | 1.9         | mV |  |  |

1. Referred to Full Scale.

## 47.4.4 Sigma-Delta Analog-to-Digital Converter (SDADC) Characteristics

## Table 47-8. Operating Conditions<sup>(1)</sup>

| Symbol       | Parameters                    | Conditions                        | Min                          | Тур                | Max   | Unit   |

|--------------|-------------------------------|-----------------------------------|------------------------------|--------------------|-------|--------|

| Res          | Resolution                    | Differential mode                 | -                            | 16                 | -     | bits   |

|              |                               | Single-Ended mode                 | -                            | 15                 | -     |        |

| CLK_SDADC    | Sampling Clock Speed          | Chopper OFF (ANACTRL.ONCHOP = 0)  | 1                            | -                  | 6     | MHz    |

|              |                               | Chopper ON (ANACTRL.ONCHOP = 1)   | 1                            | -                  | 3     |        |

| CLK_SDADC_FS | Conversion rate               |                                   | CL                           | K_SDADC            | :/4   |        |

| fs           | Output Data Rate              | Free running mode                 | CLK_S                        | CLK_SDADC_FS / OSR |       |        |

|              |                               | Single conversion mode SKPCNT = N | (CLK_SDADC_FS / OSR) x (N+1) |                    |       |        |

| OSR          | Oversampling ratio            | Differential mode                 | 64                           | 256                | 1024  | Cycles |

|              | Input Conversion range        | Differential mode                 | - VREF                       | -                  | VREF  | V      |

|              |                               | Gaincorr = 0x1                    |                              |                    |       |        |

|              |                               | Single-Ended mode                 | 0                            | -                  | VREF  |        |

|              |                               | Gaincorr = 0x1                    |                              |                    |       |        |

| Vref         | Reference Voltage range       |                                   | 1                            | -                  | 5.5   | V      |

| Vcom         | Common mode voltage           | Differential mode                 | 0                            | -                  | AVDD  | V      |

| Cin          | Input capacitance             |                                   | 0.425                        | 0.5                | 0.575 | pF     |

| Zin          | Input impedance               | Differential mode                 | 1/(Cin x CLK_SDADC_FS)       |                    | kΩ    |        |

|              |                               | Single-Ended mode                 | 1/(Cin x CLK_SDADC_FS x 2)   |                    |       |        |

|              | Input anti-alias filter       | Rext                              | -                            | 1.0                | -     | kΩ     |

|              | recommendation <sup>(2)</sup> | Cext                              | 3.3                          | -                  | 10    | nF     |

1. These are based on simulation. These values are not covered by test or characterization.

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC               | ASIA/PACIFIC            | EUROPE                                      |

|---------------------------|----------------------------|-------------------------|---------------------------------------------|

| Corporate Office          | Asia Pacific Office        | China - Xiamen          | Austria - Wels                              |

| 2355 West Chandler Blvd.  | Suites 3707-14, 37th Floor | Tel: 86-592-2388138     | Tel: 43-7242-2244-39                        |

| Chandler, AZ 85224-6199   | Tower 6, The Gateway       | Fax: 86-592-2388130     | Fax: 43-7242-2244-393                       |

| Tel: 480-792-7200         | Harbour City, Kowloon      | China - Zhuhai          | Denmark - Copenhagen                        |

| Fax: 480-792-7277         | Hong Kong                  | Tel: 86-756-3210040     | Tel: 45-4450-2828                           |

| Technical Support:        | Tel: 852-2943-5100         | Fax: 86-756-3210049     | Fax: 45-4485-2829                           |

| http://www.microchip.com/ | Fax: 852-2401-3431         | India - Bangalore       | Finland - Espoo                             |

| support                   | Australia - Sydney         | Tel: 91-80-3090-4444    | Tel: 358-9-4520-820                         |

| Web Address:              | Tel: 61-2-9868-6733        | Fax: 91-80-3090-4123    | France - Paris                              |

| www.microchip.com         | Fax: 61-2-9868-6755        | India - New Delhi       | Tel: 33-1-69-53-63-20                       |

| Atlanta                   | China - Beijing            | Tel: 91-11-4160-8631    | Fax: 33-1-69-30-90-79                       |

| Duluth, GA                | Tel: 86-10-8569-7000       | Fax: 91-11-4160-8632    | France - Saint Cloud                        |

| Tel: 678-957-9614         | Fax: 86-10-8528-2104       | India - Pune            | Tel: 33-1-30-60-70-00                       |

| Fax: 678-957-1455         | China - Chengdu            | Tel: 91-20-3019-1500    | Germany - Garching                          |

| Austin, TX                | Tel: 86-28-8665-5511       | Japan - Osaka           | Tel: 49-8931-9700                           |

| Tel: 512-257-3370         | Fax: 86-28-8665-7889       | Tel: 81-6-6152-7160     | Germany - Haan                              |

| Boston                    | China - Chongqing          | Fax: 81-6-6152-9310     | Tel: 49-2129-3766400                        |

| Westborough, MA           | Tel: 86-23-8980-9588       | Japan - Tokyo           | Germany - Heilbronn                         |

| Tel: 774-760-0087         | Fax: 86-23-8980-9500       | Tel: 81-3-6880- 3770    | Tel: 49-7131-67-3636                        |

| Fax: 774-760-0088         | China - Dongguan           | Fax: 81-3-6880-3771     | Germany - Karlsruhe                         |

| Chicago                   | Tel: 86-769-8702-9880      | Korea - Daegu           | Tel: 49-721-625370                          |

| Itasca, IL                | China - Guangzhou          | Tel: 82-53-744-4301     | Germany - Munich                            |

| Tel: 630-285-0071         | Tel: 86-20-8755-8029       | Fax: 82-53-744-4302     | Tel: 49-89-627-144-0                        |

| Fax: 630-285-0075         | China - Hangzhou           | Korea - Seoul           | Fax: 49-89-627-144-44                       |

| Dallas                    | Tel: 86-571-8792-8115      | Tel: 82-2-554-7200      | Germany - Rosenheim                         |

| Addison, TX               | Fax: 86-571-8792-8116      | Fax: 82-2-558-5932 or   | Tel: 49-8031-354-560                        |

| Tel: 972-818-7423         | China - Hong Kong SAR      | 82-2-558-5934           | Israel - Ra'anana                           |

| Fax: 972-818-2924         | Tel: 852-2943-5100         | Malaysia - Kuala Lumpur | Tel: 972-9-744-7705                         |

| Detroit                   | Fax: 852-2401-3431         | Tel: 60-3-6201-9857     | Italy - Milan                               |

| Novi, MI                  | China - Nanjing            | Fax: 60-3-6201-9859     | Tel: 39-0331-742611                         |

| Tel: 248-848-4000         | Tel: 86-25-8473-2460       | Malaysia - Penang       | Fax: 39-0331-466781                         |

| Houston, TX               | Fax: 86-25-8473-2470       | Tel: 60-4-227-8870      | Italy - Padova                              |

| Tel: 281-894-5983         | China - Qingdao            | Fax: 60-4-227-4068      | Tel: 39-049-7625286                         |

| Indianapolis              | Tel: 86-532-8502-7355      | Philippines - Manila    | Netherlands - Drunen                        |

| Noblesville, IN           | Fax: 86-532-8502-7205      | Tel: 63-2-634-9065      | Tel: 31-416-690399                          |

| Tel: 317-773-8323         | China - Shanghai           | Fax: 63-2-634-9069      | Fax: 31-416-690340                          |

| Fax: 317-773-5453         | Tel: 86-21-3326-8000       | Singapore               | Norway - Trondheim                          |

| Tel: 317-536-2380         | Fax: 86-21-3326-8021       | Tel: 65-6334-8870       | Tel: 47-7289-7561                           |

| Los Angeles               | China - Shenyang           | Fax: 65-6334-8850       | Poland - Warsaw                             |

| Mission Viejo, CA         | Tel: 86-24-2334-2829       | Taiwan - Hsin Chu       | Tel: 48-22-3325737                          |

| Tel: 949-462-9523         | Fax: 86-24-2334-2393       | Tel: 886-3-5778-366     | Romania - Bucharest                         |

| Fax: 949-462-9608         | China - Shenzhen           | Fax: 886-3-5770-955     | Tel: 40-21-407-87-50                        |

| Tel: 951-273-7800         | Tel: 86-755-8864-2200      | Taiwan - Kaohsiung      | Spain - Madrid                              |

| Raleigh, NC               | Fax: 86-755-8203-1760      | Tel: 886-7-213-7830     | Tel: 34-91-708-08-90                        |

| Tel: 919-844-7510         | China - Wuhan              | Taiwan - Taipei         | Fax: 34-91-708-08-91                        |

|                           | Tel: 86-27-5980-5300       | Tel: 886-2-2508-8600    |                                             |

| New York, NY              | Fax: 86-27-5980-5300       | Fax: 886-2-2508-8600    | Sweden - Gothenberg<br>Tel: 46-31-704-60-40 |

| Tel: 631-435-6000         | China - Xian               |                         | Sweden - Stockholm                          |

| San Jose, CA              |                            | Thailand - Bangkok      |                                             |

| Tel: 408-735-9110         | Tel: 86-29-8833-7252       | Tel: 66-2-694-1351      | Tel: 46-8-5090-4654                         |

| Tel: 408-436-4270         | Fax: 86-29-8833-7256       | Fax: 66-2-694-1350      | UK - Wokingham                              |

| Canada - Toronto          |                            |                         | Tel: 44-118-921-5800                        |

| Tel: 905-695-1980         |                            |                         | Fax: 44-118-921-5820                        |

| Fax: 905-695-2078         |                            |                         |                                             |