Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20j17a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

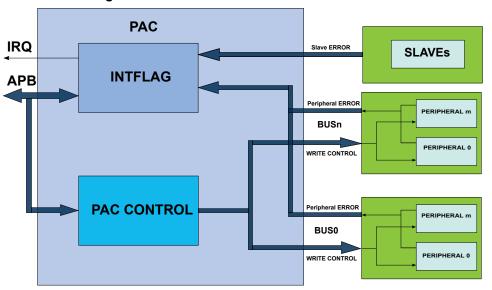

# 11. PAC - Peripheral Access Controller

# 11.1 Overview

The Peripheral Access Controller provides an interface for the locking and unlocking of peripheral registers within the device. It reports all violations that could happen when accessing a peripheral: write protected access, illegal access, enable protected access, access when clock synchronization or software reset is on-going. These errors are reported in a unique interrupt flag for a peripheral. The PAC module also reports errors occurring at the slave bus level, when an access to a non-existing address is detected.

# 11.2 Features

• Manages write protection access and reports access errors for the peripheral modules or bridges.

# 11.3 Block Diagram

# Figure 11-1. PAC Block Diagram

# **11.4 Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 11.4.1 IO Lines

Not applicable.

# 11.4.2 Power Management

The PAC can continue to operate in any Sleep mode where the selected source clock is running. The PAC interrupts can be used to wake up the device from Sleep modes. The events can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

# SAM C20/C21

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | B Clock             | AP    | B Clock             | Generic<br>Clock         | PAC   |                  |                                    | Events                                        | DMA                        |                  |

|---------------------|-----------------|-------------|-------|---------------------|-------|---------------------|--------------------------|-------|------------------|------------------------------------|-----------------------------------------------|----------------------------|------------------|

|                     |                 |             | Index | Enabled<br>at Reset | Index | Enabled<br>at Reset | Index                    | Index | Prot at<br>Reset | User                               | Generator                                     | Index                      | Sleep<br>Walking |

|                     |                 |             |       |                     |       |                     |                          |       |                  | 45: STOP                           |                                               |                            |                  |

| AHB-APB<br>Bridge C | 0x42000000      |             | 2     | Y                   |       |                     |                          |       |                  |                                    |                                               |                            | N/A              |

| EVSYS               | 0x42000000      | 8           |       |                     | 0     | N                   | 6-17: one per<br>CHANNEL | 0     | N                |                                    |                                               |                            | Y                |

| SERCOM0             | 0x42000400      | 9           |       |                     | 1     | N                   | 19: CORE<br>18: SLOW     | 1     | N                |                                    |                                               | 2: RX<br>3: TX             | Y                |

| SERCOM1             | 0x42000800      | 10          |       |                     | 2     | N                   | 20: CORE<br>18: SLOW     | 2     | N                |                                    |                                               | 4: RX<br>5: TX             | Y                |

| SERCOM2             | 0x42000C00      | 11          |       |                     | 3     | N                   | 21: CORE<br>18: SLOW     | 3     | N                |                                    |                                               | 6: RX<br>7: TX             | Y                |

| SERCOM3             | 0x42001000      | 12          |       |                     | 4     | N                   | 22: CORE<br>18: SLOW     | 4     | N                |                                    |                                               | 8: RX<br>9: TX             | Y                |

| SERCOM4             | 0x42001400      | 13          |       |                     | 5     | N                   | 23: CORE<br>18: SLOW     | 5     | N                |                                    |                                               | 10: RX<br>11: TX           | Y                |

| SERCOM5             | 0x42001800      | 14          |       |                     | 6     | N                   | 25: CORE<br>24: SLOW     | 6     | N                |                                    |                                               | 12: RX<br>13: TX           | Y                |

| CAN0                | 0x42001C00      | 15          | 8     | N                   |       |                     | 26                       |       |                  |                                    |                                               | 14: DEBUG                  | N/A              |

| CAN1                | 0x42002000      | 16          | 9     | N                   |       |                     | 27                       |       |                  |                                    |                                               | 15: DEBUG                  | N/A              |

| TCC0                | 0x42002400      | 17          |       |                     | 9     | N                   | 28                       | 9     | N                | 9-10: EV0-1<br>11-14:<br>MC0-3     | 34: OVF<br>35: TRG<br>36: CNT<br>37-40: MC0-3 | 16: OVF<br>17-20:<br>MC0-3 | Y                |

| TCC1                | 0x42002800      | 18          |       |                     | 10    | N                   | 28                       | 10    | N                | 15-16:<br>EV0-1<br>17-18:<br>MC0-1 | 41: OVF<br>42: TRG<br>43: CNT<br>44-45: MC0-1 | 21: OVF<br>22-23:<br>MC0-1 | Y                |

| TCC2                | 0x42002C00      | 19          |       |                     | 11    | N                   | 29                       | 11    | N                | 19-20:<br>EV0-1<br>21-22:<br>MC0-1 | 46: OVF<br>47: TRG<br>48: CNT<br>49-50: MC0-1 | 24: OVF<br>25-26:<br>MC0-1 | Y                |

| TCO                 | 0x42003000      | 20          |       |                     | 12    | N                   | 30                       | 12    | N                | 23: EVU                            | 51: OVF<br>52-53: MC0-1                       | 27: OVF<br>28-29:<br>MC0-1 | Y                |

| TC1                 | 0x42003400      | 21          |       |                     | 13    | N                   | 30                       | 13    | N                | 24: EVU                            | 54: OVF<br>55-56: MC0-1                       | 30: OVF<br>21-32:<br>MC0-1 | Y                |

| TC2                 | 0x42003800      | 22          |       |                     | 14    | N                   | 31                       | 14    | N                | 25: EVU                            | 57: OVF<br>58-59: MC0-1                       | 33: OVF<br>23-35:<br>MC0-1 | Y                |

| ТСЗ                 | 0x42003C00      | 23          |       |                     | 15    | N                   | 31                       | 15    | N                | 26: EVU                            | 60: OVF<br>61-62: MC0-1                       | 36: OVF<br>37-38:<br>MC0-1 | Y                |

| TC4                 | 0x42004000      | 24          |       |                     | 16    | N                   | 32                       | 16    | N                | 27: EVU                            | 63: OVF<br>64-65: MC0-1                       | 39: OVF<br>40-41:<br>MC0-1 | Y                |

| ADC0                | 0x42004400      | 25          |       |                     | 17    | N                   | 33                       | 17    | N                | 28: START<br>29: SYNC              | 66: RESRDY<br>67: WINMON                      | 42:<br>RESRDY              | Y                |

| ADC1                | 0x42004800      | 26          |       |                     | 18    | N                   | 34                       | 18    | N                | 30: START<br>31: SYNC              | 68: RESRDY<br>69: WINMON                      | 43:<br>RESRDY              | Y                |

| SDADC               | 0x42004C00      | 29          |       |                     | 19    | N                   | 35                       | 19    | N                | 32: START<br>33: FLUSH             | 70: RESRDY<br>71: WINMON                      | 44:<br>RESRDY              | Y                |

| AC                  | 0x42005000      | 27          |       |                     | 20    | N                   | 34                       | 20    | N                | 34-37:<br>SOC0-3                   | 72-75: COMP0-3<br>76-77: WIN0-1               |                            | Y                |

|        | 1        |          |       |          |        |            |       |              |       |

|--------|----------|----------|-------|----------|--------|------------|-------|--------------|-------|

| Offset | Name     | Bit Pos. |       |          |        |            |       |              |       |

|        |          |          |       |          |        |            |       |              |       |

| 0x1FCB |          |          |       |          |        |            |       |              |       |

| 0x1FCC | -        | 7:0      |       |          |        |            |       |              | SMEMP |

| 0x1FCD | MEMTYPE  | 15:8     |       |          |        |            |       |              |       |

| 0x1FCE |          | 23:16    |       |          |        |            |       |              |       |

| 0x1FCF |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FD0 | -        | 7:0      | FKB   | C[3:0]   |        |            | JEPC  | C[3:0]       |       |

| 0x1FD1 | PID4     | 15:8     |       |          |        |            |       |              |       |

| 0x1FD2 |          | 23:16    |       |          |        |            |       |              |       |

| 0x1FD3 |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FD4 |          |          |       |          |        |            |       |              |       |

|        | Reserved |          |       |          |        |            |       |              |       |

| 0x1FDF |          |          |       |          |        |            |       |              |       |

| 0x1FE0 |          | 7:0      |       |          | PARTI  | NBL[7:0]   |       |              |       |

| 0x1FE1 | PID0     | 15:8     |       |          |        |            |       |              |       |

| 0x1FE2 | 1100     | 23:16    |       |          |        |            |       |              |       |

| 0x1FE3 |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FE4 |          | 7:0      | JEPID | OCL[3:0] |        |            | PARTN | BH[3:0]      |       |

| 0x1FE5 | PID1     | 15:8     |       |          |        |            |       |              |       |

| 0x1FE6 | PIDT     | 23:16    |       |          |        |            |       |              |       |

| 0x1FE7 |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FE8 |          | 7:0      | REVIS | ION[3:0] |        | JEPU       |       | JEPIDCH[2:0] |       |

| 0x1FE9 | PID2     | 15:8     |       |          |        |            |       |              |       |

| 0x1FEA | PID2     | 23:16    |       |          |        |            |       |              |       |

| 0x1FEB |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FEC |          | 7:0      | REVA  | ND[3:0]  |        |            | CUSM  | OD[3:0]      |       |

| 0x1FED | DIDA     | 15:8     |       |          |        |            |       |              |       |

| 0x1FEE | PID3     | 23:16    |       |          |        |            |       |              |       |

| 0x1FEF |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FF0 |          | 7:0      |       |          | PREAME | BLEB0[7:0] |       |              |       |

| 0x1FF1 |          | 15:8     |       |          |        |            |       |              |       |

| 0x1FF2 | CID0     | 23:16    |       |          |        |            |       |              |       |

| 0x1FF3 |          | 31:24    |       |          |        |            |       |              |       |

| 0x1FF4 |          | 7:0      | CCLA  | .SS[3:0] |        |            | PREAM | BLE[3:0]     |       |

| 0x1FF5 |          | 15:8     |       |          |        |            |       |              |       |

| 0x1FF6 | CID1     | 23:16    |       |          |        |            |       |              |       |

| 0x1FF7 | -        | 31:24    |       |          |        |            |       |              |       |

| 0x1FF8 |          | 7:0      |       |          | PREAME | BLEB2[7:0] |       |              |       |

| 0x1FF9 |          | 15:8     |       |          |        |            |       |              |       |

| 0x1FFA | CID2     | 23:16    |       |          |        |            |       |              |       |

| 0x1FFB | -        | 31:24    |       |          |        |            |       |              |       |

| 0x1FFC |          | 7:0      |       |          | PREAME | 3LEB3[7:0] |       |              |       |

| 0x1FFD |          | 15:8     |       |          |        |            |       |              |       |

| 0x1FFE | CID3     | 23:16    |       |          |        |            |       |              |       |

| 0x1FFF | -        | 31:24    |       |          |        |            |       |              |       |

|        |          | 5        |       |          |        |            |       |              |       |

REGA, REGB are 8-bit core registers. REGC is 16-bit core register.

| Offset | Register |

|--------|----------|

| 0x00   | REGA     |

| 0x01   | REGB     |

| 0x02   | REGC     |

| 0x03   | REGC     |

Since synchronization is per register, user can write REGA (8-bit access) then immediately write REGB (8-bit access) without error.

User can write REGC (16-bit access) without affecting REGA or REGB. But if user writes REGC in two consecutive 8-bit accesses, second write will be discarded and generate an error.

When user makes a 32-bit access to offset 0x00, all registers are written but REGA, REGB, REGC can be updated at a different time because of independent write synchronization

#### 15.3.3 General Read-Synchronization

Before any read of a core register, the user must check that the related bit in SYNCBUSY register is cleared.

Read access to core register is always immediate but the return value is reliable only if a synchronization of this core register is not going.

# 15.3.4 Completion of Synchronization

The user can either poll SYNCBUSY register or use the Synchronization Ready interrupt (if available) to check when the synchronization is complete.

# 15.3.5 Enable Write-Synchronization

Writing to the Enable bit in the Control register (CTRL.ENABLE) will also trigger write-synchronization and set SYNCBUSY.ENABLE. CTRL.ENABLE will read its new value immediately after being written. The Synchronisation Ready interrupt (if available) cannot be used for Enable write-synchronization.

# 15.3.6 Software Reset Write-Synchronization

Writing a one to the Software Reset bit in CTRL (CTRL.SWRST) will also trigger write-synchronization and set SYNCBUSY.SWRST. When writing a one to the CTRL.SWRST bit it will immediately read as one. CTRL.SWRST and SYNCBUSY.SWRST will be cleared by hardware when the peripheral has been reset. Writing a zero to the CTRL.SWRST bit has no effect. The Synchronisation Ready interrupt (if available) cannot be used for Software Reset write-synchronization.

# 15.3.7 Synchronization Delay

The synchronization will delay the write or read access duration by a delay D, given by the equation:

$5 \cdot P_{\text{GCLK}} + 2 \cdot P_{\text{APB}} < D < 6 \cdot P_{\text{GCLK}} + 3 \cdot P_{\text{APB}}$

Where  $P_{\text{GCLK}}$  is the period of the generic clock and  $P_{\text{APB}}$  is the period of the peripheral bus clock. A normal peripheral bus register access duration is  $2 \cdot P_{\text{APB}}$ .

# Table 16-7. Generator Selection

| Value     | Description               |

|-----------|---------------------------|

| 0x0       | Generic Clock Generator 0 |

| 0x1       | Generic Clock Generator 1 |

| 0x2       | Generic Clock Generator 2 |

| 0x3       | Generic Clock Generator 3 |

| 0x4       | Generic Clock Generator 4 |

| 0x5       | Generic Clock Generator 5 |

| 0x6       | Generic Clock Generator 6 |

| 0x7       | Generic Clock Generator 7 |

| 0x8       | Generic Clock Generator 8 |

| 0x9 - 0xF | Reserved                  |

# Table 16-8. Reset Value after a User Reset or a Power Reset

| Reset       | PCHCTRLm.GEN              | PCHCTRLm.CHEN             | PCHCTRLm.WRTLOCK |

|-------------|---------------------------|---------------------------|------------------|

| Power Reset | 0x0                       | 0x0                       | 0x0              |

| User Reset  | If WRTLOCK = 0<br>: 0x0   | If WRTLOCK = 0<br>: 0x0   | No change        |

|             | If WRTLOCK = 1: no change | If WRTLOCK = 1: no change |                  |

A Power Reset will reset all the PCHCTRLm registers.

A User Reset will reset a PCHCTRL if WRTLOCK=0, or else, the content of that PCHCTRL remains unchanged.

PCHCTRL register Reset values are shown in the table PCHCTRLm Mapping.

# Table 16-9. PCHCTRLm Mapping

| index(m) | Name                 | Description                                            |

|----------|----------------------|--------------------------------------------------------|

| 0        | GCLK_DPLL            | FDPLL96M input clock source for reference              |

| 1        | GCLK_DPLL_32K        | FDPLL96M 32kHz clock for FDPLL96M internal clock timer |

| 2        | GCLK_EIC             | EIC                                                    |

| 3        | GCLK_FREQM_MSR       | FREQM Measure                                          |

| 4        | GCLK_FREQM_REF       | FREQM Reference                                        |

| 5        | GCLK_TSENS           | TSENS                                                  |

| 6        | GCLK_EVSYS_CHANNEL_0 | EVSYS_CHANNEL_0                                        |

| 7        | GCLK_EVSYS_CHANNEL_1 | EVSYS_CHANNEL_1                                        |

| 8        | GCLK_EVSYS_CHANNEL_2 | EVSYS_CHANNEL_2                                        |

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28 | 27 | 26      | 25        | 24         |

|--------|----|----|----|----|----|---------|-----------|------------|

| ſ      |    |    |    |    |    |         |           |            |

| Access |    |    |    |    |    |         |           |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18      | 17        | 16         |

|        |    |    |    |    |    |         |           |            |

| Access |    | •  |    |    |    |         | •         |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10      | 9         | 8          |

|        |    |    |    |    |    |         |           |            |

| Access |    | •  |    |    |    |         | •         |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2       | 1         | 0          |

| ſ      |    |    |    |    |    | CLKFAIL | OSC32KRDY | XOSC32KRDY |

| Access |    |    |    |    |    | R/W     | R/W       | R/W        |

| Reset  |    |    |    |    |    | 0       | 0         | 0          |

#### Bit 2 – CLKFAIL: XOSC32K Clock Failure Detection

This flag is cleared by writing a '1' to it.

This flag is set on a zero-to-one transition of the XOSC32K Clock Failure Detection bit in the Status register (STATUS.CLKFAIL) and will generate an interrupt request if INTENSET.CLKFAIL is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Clock Failure Detection flag.

#### Bit 1 – OSC32KRDY: OSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the OSC32K Ready bit in the Status register (STATUS.OSC32KRDY), and will generate an interrupt request if INTENSET.OSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the OSC32K Ready interrupt flag.

#### Bit 0 – XOSC32KRDY: XOSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the XOSC32K Ready bit in the Status register (STATUS.XOSC32KRDY), and will generate an interrupt request if INTENSET.XOSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the XOSC32K Ready interrupt flag.

#### 21.8.4 Status

# 25. DMAC – Direct Memory Access Controller

# 25.1 Overview

The Direct Memory Access Controller (DMAC) contains both a Direct Memory Access engine and a Cyclic Redundancy Check (CRC) engine. The DMAC can transfer data between memories and peripherals, and thus off-load these tasks from the CPU. It enables high data transfer rates with minimum CPU intervention, and frees up CPU time. With access to all peripherals, the DMAC can handle automatic transfer of data between communication modules.

The DMA part of the DMAC has several DMA channels which all can receive different types of transfer triggers to generate transfer requests from the DMA channels to the arbiter, see also the Block Diagram. The arbiter will grant one DMA channel at a time to act as the active channel. When an active channel has been granted, the fetch engine of the DMAC will fetch a transfer descriptor from the SRAM and store it in the internal memory of the active channel, which will execute the data transmission.

An ongoing data transfer of an active channel can be interrupted by a higher prioritized DMA channel. The DMAC will write back the updated transfer descriptor from the internal memory of the active channel to SRAM, and grant the higher prioritized channel to start transfer as the new active channel. Once a DMA channel is done with its transfer, interrupts and events can be generated optionally.

The DMAC has four bus interfaces:

- The data transfer bus is used for performing the actual DMA transfer.

- The AHB/APB Bridge bus is used when writing and reading the I/O registers of the DMAC.

- The *descriptor fetch bus* is used by the fetch engine to fetch transfer descriptors before data transfer can be started or continued.

- The write-back bus is used to write the transfer descriptor back to SRAM.

All buses are AHB master interfaces but the AHB/APB Bridge bus, which is an APB slave interface.

The CRC engine can be used by software to detect an accidental error in the transferred data and to take corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

# 25.2 Features

- Data transfer from:

- Peripheral to peripheral

- Peripheral to memory

- Memory to peripheral

- Memory to memory

- Transfer trigger sources

- Software

- Events from Event System

- Dedicated requests from peripherals

- SRAM based transfer descriptors

- Single transfer using one descriptor

- Multi-buffer or circular buffer modes by linking multiple descriptors

- Up to 12 channels

This bus clock (CLK\_DMAC\_APB) is always synchronous to the module clock (CLK\_DMAC\_AHB), but can be divided by a prescaler and may run even when the module clock is turned off.

#### **Related Links**

Peripheral Clock Masking

#### 25.5.4 DMA

Not applicable.

#### 25.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the DMAC interrupt requires the interrupt controller to be configured first.

## **Related Links**

Nested Vector Interrupt Controller

# 25.5.6 Events

The events are connected to the event system.

#### **Related Links**

EVSYS – Event System

#### 25.5.7 Debug Operation

When the CPU is halted in debug mode the DMAC will halt normal operation. The DMAC can be forced to continue operation during debugging. Refer to DBGCTRL for details.

#### 25.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Interrupt Pending register (INTPEND)

- Channel ID register (CHID)

- Channel Interrupt Flag Status and Clear register (CHINTFLAG)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

#### 25.5.9 Analog Connections

Not applicable.

# 25.6 Functional Description

#### 25.6.1 Principle of Operation

The DMAC consists of a DMA module and a CRC module.

#### 25.6.1.1 DMA

The DMAC can transfer data between memories and peripherals without interaction from the CPU. The data transferred by the DMAC are called transactions, and these transactions can be split into smaller data transfers. Figure 'DMA Transfer Sizes' shows the relationship between the different transfer sizes:

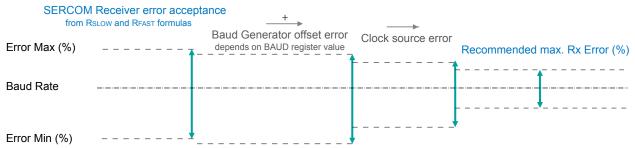

The following equations calculate the ratio of the incoming data rate and internal receiver baud rate:

$$R_{\text{SLOW}} = \frac{(D+1)S}{S-1+D\cdot S+S_F}$$

,  $R_{\text{FAST}} = \frac{(D+2)S}{(D+1)S+S_M}$

- R<sub>SLOW</sub> is the ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate

- *R*<sub>FAST</sub> is the ratio of the fastest incoming data rate that can be accepted in relation to the receiver baud rate

- *D* is the sum of character size and parity size (D = 5 to 10 bits)

- S is the number of samples per bit (S = 16, 8 or 3)

- $S_F$  is the first sample number used for majority voting ( $S_F = 7, 3, \text{ or } 2$ ) when CTRLA.SAMPA=0.

- $S_M$  is the middle sample number used for majority voting ( $S_M$  = 8, 4, or 2) when CTRLA.SAMPA=0.

The recommended maximum Rx Error assumes that the receiver and transmitter equally divide the maximum total error. Its connection to the SERCOM Receiver error acceptance is depicted in this figure:

#### Figure 31-5. USART Rx Error Calculation

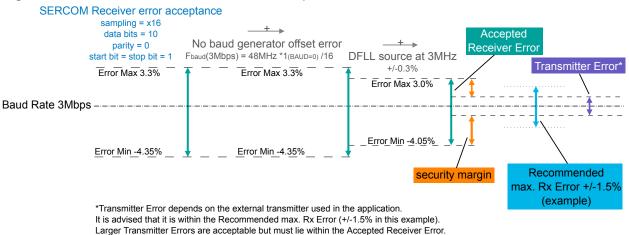

The recommendation values in the table above accommodate errors of the clock source and the baud generator. The following figure gives an example for a baud rate of 3Mbps:

#### Figure 31-6. USART Rx Error Calculation Example

#### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

#### 31.6.3 Additional Features

#### 31.6.3.1 Parity

Even or odd parity can be selected for error checking by writing 0x1 to the Frame Format bit field in the Control A register (CTRLA.FORM).

# 31.7 Register Summary

| Offset   | Name     | Bit Pos. |          |              |       |        |           |         |             |           |

|----------|----------|----------|----------|--------------|-------|--------|-----------|---------|-------------|-----------|

| 0x00     |          | 7:0      | RUNSTDBY |              |       |        | MODE[2:0] |         | ENABLE      | SWRST     |

| 0x01     |          | 15:8     |          | SAMPR[2:0]   | 1     |        |           |         |             | IBON      |

| 0x02     | CTRLA    | 23:16    | SAMF     | PA[1:0] RXPC |       | O[1:0] |           |         | TXP         | D[1:0]    |

| 0x03     |          | 31:24    |          | DORD         | CPOL  | CMODE  |           | FOR     | M[3:0]      |           |

| 0x04     |          | 7:0      |          | SBMODE       |       |        |           |         | CHSIZE[2:0] |           |

| 0x05     | CTRLB    | 15:8     |          |              | PMODE |        |           | ENC     | SFDE        | COLDEN    |

| 0x06     | CIRLB    | 23:16    |          |              |       |        |           |         | RXEN        | TXEN      |

| 0x07     |          | 31:24    |          |              |       |        |           |         | LINC        | 1D[1:0]   |

| 0x08     |          | 7:0      |          |              |       |        |           |         | GTIME[2:0]  |           |

| 0x09     |          | 15:8     |          |              |       |        | HDRD      | LY[1:0] | BRKL        | EN[1:0]   |

| 0x0A     | CTRLC    | 23:16    |          |              |       |        |           |         |             |           |

| 0x0B     |          | 31:24    |          |              |       |        |           |         |             |           |

| 0x0C     | DALID    | 7:0      |          |              | 1     | BAU    | D[7:0]    | 1       |             | 1         |

| 0x0D     | BAUD     | 15:8     |          |              |       | BAUE   | 0[15:8]   |         |             |           |

| 0x0E     | RXPL     | 7:0      |          |              |       | RXP    | L[7:0]    |         |             |           |

| 0x0F     |          |          |          |              |       |        |           |         |             |           |

| <br>0x13 | Reserved |          |          |              |       |        |           |         |             |           |

| 0x14     | INTENCLR | 7:0      | ERROR    |              | RXBRK | CTSIC  | RXS       | RXC     | TXC         | DRE       |

| 0x15     | Reserved |          |          |              |       |        |           |         |             |           |

| 0x16     | INTENSET | 7:0      | ERROR    |              | RXBRK | CTSIC  | RXS       | RXC     | TXC         | DRE       |

| 0x17     | Reserved |          |          |              |       |        |           |         |             |           |

| 0x18     | INTFLAG  | 7:0      | ERROR    |              | RXBRK | CTSIC  | RXS       | RXC     | TXC         | DRE       |

| 0x19     | Reserved |          |          |              |       |        |           |         |             |           |

| 0x1A     | 0747110  | 7:0      |          | TXE          | COLL  | ISF    | CTS       | BUFOVF  | FERR        | PERR      |

| 0x1B     | STATUS   | 15:8     |          |              |       |        |           |         |             |           |

| 0x1C     |          | 7:0      |          |              |       |        |           | CTRLB   | ENABLE      | SWRST     |

| 0x1D     | OVNODUOV | 15:8     |          |              |       |        |           |         |             |           |

| 0x1E     | SYNCBUSY | 23:16    |          |              |       |        |           |         |             |           |

| 0x1F     |          | 31:24    |          |              |       |        |           |         |             |           |

| 0x20     |          |          |          |              |       |        |           |         |             |           |

|          | Reserved |          |          |              |       |        |           |         |             |           |

| 0x27     |          |          |          |              |       |        |           |         |             |           |

| 0x28     | DATA     | 7:0      |          |              |       | DAT    | A[7:0]    |         |             |           |

| 0x29     | DATA     | 15:8     |          |              |       |        |           |         |             | DATA[8:8] |

| 0x2A     |          |          |          |              |       |        |           |         |             |           |

| <br>0x2F | Reserved |          |          |              |       |        |           |         |             |           |

| 0x30     | DBGCTRL  | 7:0      |          |              |       |        |           |         |             | DBGSTOP   |

# 31.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

#### **Bit 1 – TXC: Transmit Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Transmit Complete Interrupt Enable bit, which enables the Transmit Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

#### Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Register Empty Interrupt Enable bit, which enables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

## 31.8.8 Interrupt Flag Status and Clear

| Name:            | INTFLAG            |

|------------------|--------------------|

| Offset:          | 0x18 [ID-00000fa7] |

| Reset:           | 0x00               |

| <b>Property:</b> | -                  |

| Bit    | 7     | 6 | 5     | 4     | 3   | 2   | 1   | 0   |

|--------|-------|---|-------|-------|-----|-----|-----|-----|

|        | ERROR |   | RXBRK | CTSIC | RXS | RXC | TXC | DRE |

| Access | R/W   | • | R/W   | R/W   | R/W | R   | R/W | R   |

| Reset  | 0     |   | 0     | 0     | 0   | 0   | 0   | 0   |

#### Bit 7 – ERROR: Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. Errors that will set this flag are COLL, ISF, BUFOVF, FERR, and PERR.Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 5 – RXBRK: Receive Break

This flag is cleared by writing '1' to it.

This flag is set when auto-baud is enabled (CTRLA.FORM) and a break character is received.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

## 33.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

PM - Power Manager

## 33.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Main Clock Controller. Refer to *Peripheral Clock Masking* for details and default status of this clock.

Two generic clocks are used by SERCOM, GCLK\_SERCOMx\_CORE and GCLK\_SERCOM\_SLOW. The core clock (GCLK\_SERCOMx\_CORE) can clock the I<sup>2</sup>C when working as a master. The slow clock (GCLK\_SERCOM\_SLOW) is required only for certain functions, e.g. SMBus timing. These two clocks must be configured and enabled in the Generic Clock Controller (GCLK) before using the I<sup>2</sup>C.

These generic clocks are asynchronous to the bus clock (CLK\_SERCOMx\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

GCLK - Generic Clock Controller Peripheral Clock Masking PM – Power Manager

## 33.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

DMAC - Direct Memory Access Controller

# 33.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 33.5.6 Events

Not applicable.

# 33.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 33.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

| Bit    | 31        | 30  | 29  | 28   | 27      | 26          | 25  | 24  |  |

|--------|-----------|-----|-----|------|---------|-------------|-----|-----|--|

|        |           |     |     |      |         | EIDM[28:24] |     |     |  |

| Access |           |     |     | R/W  | R/W     | R/W         | R/W | R/W |  |

| Reset  |           |     |     | 1    | 1       | 1           | 1   | 1   |  |

|        |           |     |     |      |         |             |     |     |  |

| Bit    | 23        | 22  | 21  | 20   | 19      | 18          | 17  | 16  |  |

|        |           |     |     | EIDM | [23:16] |             |     |     |  |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W         | R/W | R/W |  |

| Reset  | 1         | 1   | 1   | 1    | 1       | 1           | 1   | 1   |  |

|        |           |     |     |      |         |             |     |     |  |

| Bit    | 15        | 14  | 13  | 12   | 11      | 10          | 9   | 8   |  |

|        |           |     |     | EIDM | I[15:8] |             |     |     |  |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W         | R/W | R/W |  |

| Reset  | 1         | 1   | 1   | 1    | 1       | 1           | 1   | 1   |  |

|        |           |     |     |      |         |             |     |     |  |

| Bit    | 7         | 6   | 5   | 4    | 3       | 2           | 1   | 0   |  |

|        | EIDM[7:0] |     |     |      |         |             |     |     |  |

| Access | R/W       | R/W | R/W | R/W  | R/W     | R/W         | R/W | R/W |  |

| Reset  | 1         | 1   | 1   | 1    | 1       | 1           | 1   | 1   |  |

#### Bits 28:0 – EIDM[28:0]: Extended ID Mask

For acceptance filtering of extended frames the Extended ID AND Mask is ANDed with the Message ID of a received frame. Intended for masking of 29-bit IDs in SAE J1939. With the reset value of all bits set to one the mask is not active.

#### 34.8.24 High Priority Message Status

This register is updated every time a Message ID filter element configured to generate a priority event matches. This can be used to monitor the status of incoming high priority messages and to enable fast access to these messages.

Name:HPMSOffset:0x94 [ID-0000a4bb]Reset:0x00000000Property:Read-only

# Table 34-15. Extended Message ID Filter Element

|    | 31   | 3           | 29 | 28          | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15       | 14    | 13   | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|------|-------------|----|-------------|----|----|----|----|----|----|----|----|----|----|----|----|----------|-------|------|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |      | 0           |    |             |    |    |    |    |    |    |    |    |    |    |    |    |          |       |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

| F0 | E    | FEC         |    | EFID1[28:0] |    |    |    |    |    |    |    |    |    |    |    |    |          |       |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    | [2   | 2:0]        |    |             |    |    |    |    |    |    |    |    |    |    |    |    | <u> </u> |       | 0.0] |    |    |    |   |   |   |   |   |   |   |   |   |   |

| F1 | EF   | EFID2[28:0] |    |             |    |    |    |    |    |    |    |    |    |    |    |    |          |       |      |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    | [1:0 | )]          |    |             |    |    |    |    |    |    |    |    |    |    |    |    | CEL      | טצנצי | 0.0] |    |    |    |   |   |   |   |   |   |   |   |   |   |

F0 Bits 31:29 - EFEC[2:0]: Extended Filter Element Configuration

All enabled filter elements are used for acceptance filtering of extended frames. Acceptance filtering stops at the first matching enabled filter element or when the end of the filter list is reached. If EFEC = "100", "101", or "110" a match sets interrupt flag IR.HPM and, if enabled, an interrupt is generated. In this case register HPMS is updated with the status of the priority match.

Table 34-16. Extended Filter Element Configuration

| Value | Name     | Description                                                                  |

|-------|----------|------------------------------------------------------------------------------|

| 0x0   | DISABLE  | Disable filter element.                                                      |

| 0x1   | STF0M    | Store in Rx FIFO 0 if filter matches.                                        |

| 0x2   | STF1M    | Store in Rx FIFO 1 if filter matches.                                        |

| 0x3   | REJECT   | Reject ID if filter matches.                                                 |

| 0x4   | PRIORITY | Set priority if filter matches.                                              |

| 0x5   | PRIF0M   | Set priority and store in FIFO 0 if filter matches.                          |

| 0x6   | PRIF1M   | Set priority and store in FIFO 1 if filter matches.                          |

| 0x7   | STRXBUF  | Store into Rx Buffer or as debug message, configuration of EFT[1:0] ignored. |

• F0 Bits 28:0 - EFID1[28:0]: Extended Filter ID 1

First ID of extended ID filter element.

When filtering for Rx Buffers or for debug messages this field defines the ID of a extended mesage to be stored. The received identifiers must match exactly, only XIDAM masking mechanism is used.

F1 Bits 31:30 - EFT[1:0]: Extended Filter Type

This field defines the extended filter type.

Table 34-17. Extended Filter Type

| Value            | Name                                             | Description                                                                |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 0x0              | RANGEM                                           | Range filter from EFID1 to EFID2 (EFID2 >= EFID1).                         |  |  |  |  |  |  |  |  |

| 0x1              | DUAL                                             | Dual ID filter for EFID1 or EFID2.                                         |  |  |  |  |  |  |  |  |

| 0x2              | CLASSIC                                          | Classic filter: EFID1 = filter, EFID2 = mask.                              |  |  |  |  |  |  |  |  |

| 0x3              | RANGE                                            | Range filter from EFID1 to EFID2 (EFID2 >= EFID1), XIDAM mask not applied. |  |  |  |  |  |  |  |  |

| • F <sup>*</sup> | E1 Bits 28:0 - EEID2[28:0]: Extended Eilter ID 2 |                                                                            |  |  |  |  |  |  |  |  |

F1 Bits 28:0 - EFID2[28:0]: Extended Filter ID 2

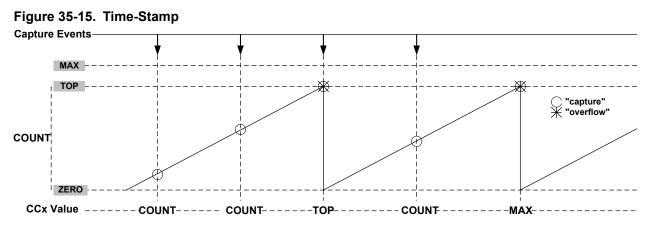

#### 35.6.3.3 Minimum Capture

The minimum capture is enabled by writing the CAPTMIN mode in the Channel n Capture Mode bits in the Control A register (CTRLA.CAPTMODEn = CAPTMIN).

#### CCx Content:

In CAPTMIN operations, CCx keeps the Minimum captured values. Before enabling this mode of capture, the user must initialize the corresponding CCx register value to a value different from zero. If the CCx register initial value is zero, no captures will be performed using the corresponding channel.

#### MCx Behaviour:

In CAPTMIN operation, capture is performed only when on capture event time, the counter value is lower than the last captured value. The MCx interrupt flag is set only when on capture event time, the counter value is upper or equal to the value captured on the previous event. So interrupt flag is set when a new absolute local Minimum value has been detected.

#### 35.6.3.4 Maximum Capture

The maximum capture is enabled by writing the CAPTMAX mode in the Channel n Capture Mode bits in the Control A register (CTRLA.CAPTMODEn = CAPTMAX).

#### CCx Content:

In CAPTMAX operations, CCx keeps the Maximum captured values. Before enabling this mode of capture, the user must initialize the corresponding CCx register value to a value different from TOP. If the CCx register initial value is TOP, no captures will be performed using the corresponding channel.

#### MCx Behaviour:

In CAPTMAX operation, capture is performed only when on capture event time, the counter value is upper than the last captured value. The MCx interrupt flag is set only when on capture event time, the counter value is lower or equal to the value captured on the previous event. So interrupt flag is set when a new absolute local Maximum value has been detected.

This bit is set when the synchronization of CCx between clock domains is started.

This bit is also set when the CCBUFx is written, and cleared on update condition. The bit is automatically cleared when the STATUS.CCBUFx bit is cleared.

#### Bit 5 – PER: PER Synchronization Busy

This bit is cleared when the synchronization of PER between the clock domains is complete.

This bit is set when the synchronization of PER between clock domains is started.

This bit is also set when the PER is written, and cleared on update condition. The bit is automatically cleared when the STATUS.PERBUF bit is cleared.

#### **Bit 4 – COUNT: COUNT Synchronization Busy**

This bit is cleared when the synchronization of COUNT between the clock domains is complete.

This bit is set when the synchronization of COUNT between clock domains is started.

#### Bit 3 – STATUS: STATUS Synchronization Busy

This bit is cleared when the synchronization of STATUS between the clock domains is complete.

This bit is set when a '1' is written to the Capture Channel Buffer Valid status flags (STATUS.CCBUFVx) and the synchronization of STATUS between clock domains is started.

#### Bit 2 – CTRLB: CTRLB Synchronization Busy

This bit is cleared when the synchronization of CTRLB between the clock domains is complete.

This bit is set when the synchronization of CTRLB between clock domains is started.

#### Bit 1 – ENABLE: ENABLE Synchronization Busy

This bit is cleared when the synchronization of ENABLE bit between the clock domains is complete.

This bit is set when the synchronization of ENABLE bit between clock domains is started.

#### Bit 0 – SWRST: SWRST Synchronization Busy

This bit is cleared when the synchronization of SWRST bit between the clock domains is complete.

This bit is set when the synchronization of SWRST bit between clock domains is started.

#### 35.7.2.13 Counter Value, 16-bit Mode

**Note:** Prior to any read access, this register must be synchronized by user by writing the according TC Command value to the Control B Set register (CTRLBSET.CMD=READSYNC).

Name:COUNTOffset:0x14Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

## Bit 10 – CNTEO: Timer/Counter Event Output Enable

This bit is used to enable the counter cycle event. When enabled, an event will be generated on begin or end of counter cycle depending of CNTSEL[1:0] settings.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | Counter cycle output event is disabled and will not be generated.                        |

| 1     | Counter cycle output event is enabled and will be generated depend of CNTSEL[1:0] value. |

# Bit 9 – TRGEO: Retrigger Event Output Enable

This bit is used to enable the counter retrigger event. When enabled, an event will be generated when the counter retriggers operation.

| N | /alue | Description                                                                           |

|---|-------|---------------------------------------------------------------------------------------|

| C | )     | Counter retrigger event is disabled and will not be generated.                        |

| 1 |       | Counter retrigger event is enabled and will be generated for every counter retrigger. |

# Bit 8 – OVFEO: Overflow/Underflow Event Output Enable

This bit is used to enable the overflow/underflow event. When enabled an event will be generated when the counter reaches the TOP or the ZERO value.

| Value | Description                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------|

| 0     | Overflow/underflow counter event is disabled and will not be generated.                                 |

| 1     | Overflow/underflow counter event is enabled and will be generated for every counter overflow/underflow. |

#### Bits 7:6 – CNTSEL[1:0]: Timer/Counter Interrupt and Event Output Selection

These bits define on which part of the counter cycle the counter event output is generated.

| Value | Name     | Description                                                                                     |

|-------|----------|-------------------------------------------------------------------------------------------------|

| 0x0   | BEGIN    | An interrupt/event is generated at begin of each counter cycle                                  |

| 0x1   | END      | An interrupt/event is generated at end of each counter cycle                                    |

| 0x2   | BETWEEN  | An interrupt/event is generated between each counter cycle.                                     |

| 0x3   | BOUNDARY | An interrupt/event is generated at begin of first counter cycle, and end of last counter cycle. |

#### Bits 5:3 – EVACT1[2:0]: Timer/Counter Event Input 1 Action

These bits define the action the TCC will perform on TCE1 event input.

| Value | Name         | Description                                 |

|-------|--------------|---------------------------------------------|

| 0x0   | OFF          | Event action disabled.                      |

| 0x1   | RETRIGGER    | Start restart or re-trigger TC on event     |

| 0x2   | DIR (asynch) | Direction control                           |

| 0x3   | STOP         | Stop TC on event                            |

| 0x4   | DEC          | Decrement TC on event                       |

| 0x5   | PPW          | Period captured into CC0 Pulse Width on CC1 |

| 0x6   | PWP          | Period captured into CC1 Pulse Width on CC0 |

| 0x7   | FAULT        | Non-recoverable Fault                       |

# Bits 2:0 – EVACT0[2:0]: Timer/Counter Event Input 0 Action

These bits define the action the TCC will perform on TCE0 event input 0.

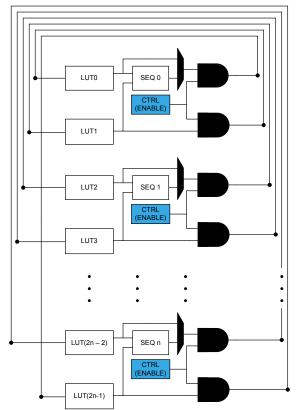

IN[2N][i] = SEQ[N]

IN[2N+1][i] = SEQ[N]

With *N* representing the sequencer number and i=0,1,2 representing the LUT input index.

For details, refer to Sequential Logic.

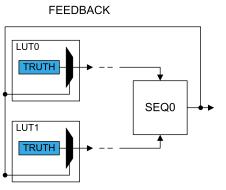

Figure 37-4. Feedback Input Selection

# Linked LUT (LINK)

When selected (LUTCTRLx.INSELy=LINK), the subsequent LUT output is used as the LUT input (e.g., LUT2 is the input for LUT1), as shown in this figure:

# Figure 37-5. Linked LUT Input Selection

## Bit 0 – SWRST: Software Reset Busy

This bit is cleared when the synchronization of CTRLA.SWRST is complete.

This bit is set when the synchronization of CTRLA.SWRST is started.

# 43.8.10 Value

Name:

VALUE

Offset:

0x0C [ID-00001f13]

Reset:

0x0000

Property:

| Bit    | 31         | 30 | 29 | 28    | 27      | 26 | 25 | 24 |  |  |

|--------|------------|----|----|-------|---------|----|----|----|--|--|

|        |            |    |    |       |         |    |    |    |  |  |

| Access |            |    |    |       |         |    |    |    |  |  |

| Reset  |            |    |    |       |         |    |    |    |  |  |

|        |            |    |    |       |         |    |    |    |  |  |

| Bit    | 23         | 22 | 21 | 20    | 19      | 18 | 17 | 16 |  |  |

|        |            |    |    | VALUE | [23:16] |    |    |    |  |  |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |  |  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |  |

|        |            |    |    |       |         |    |    |    |  |  |

| Bit    | 15         | 14 | 13 | 12    | 11      | 10 | 9  | 8  |  |  |

|        |            |    |    | VALUE | E[15:8] |    |    |    |  |  |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |  |  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |  |

|        |            |    |    |       |         |    |    |    |  |  |

| Bit    | 7          | 6  | 5  | 4     | 3       | 2  | 1  | 0  |  |  |

|        | VALUE[7:0] |    |    |       |         |    |    |    |  |  |

| Access | R          | R  | R  | R     | R       | R  | R  | R  |  |  |

| Reset  | 0          | 0  | 0  | 0     | 0       | 0  | 0  | 0  |  |  |

|        |            |    |    |       |         |    |    |    |  |  |

# Bits 23:0 – VALUE[23:0]: Measurement Value

Result from measurement. This VALUE is in two's complement format.

**Example:** If the TSENS GAIN and OFFSET registers are setup with values stored in the NVM Temperature Calibration Area (Refer to Table 9-7), the TSENS resolution is set at 100 which will result in the following values

| Temperature | VALUE            |

|-------------|------------------|

| T = 25°C    | 2500 = 0x09C4    |

| T = -25°C   | -2500 = 0xFFF63C |

# 43.8.11 Window Monitor Lower Threshold

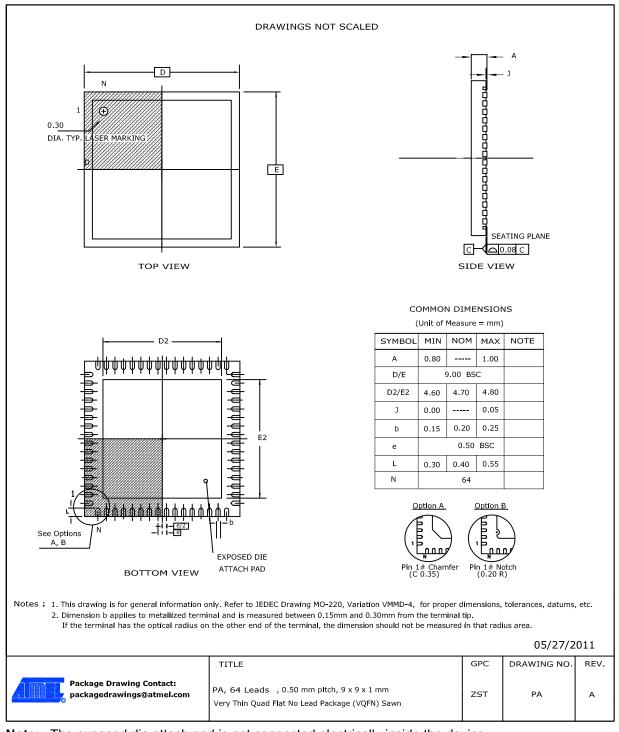

#### 48.2.3 64 pin QFN

**Note:** The exposed die attach pad is not connected electrically inside the device.

#### Table 48-8. Device and Package Maximum Weight

200

mg

# Table 48-9. Package Charateristics

MSL3