#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20j18a-mnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

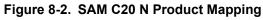

#### AHB-APB Bridge C 0x42000000 EVSYS 0x42000400 SERCOM0 0x42000800 SERCOM1 0x42000C00 SERCOM2 0x42001000 SERCOM3 0x42001400 SERCOM4 0x42001800 SERCOM5 0x42001C00 Reserved 0x42002000 Reserved 0x42002400 TCC0 0x42002800 TCC1 0x42002C00 TCC2 0x42003000 TC0 0x42003400 TC1 0x42003800 TC2 0x42003C00 TC3 0x42004000 TC4 0x42004400 ADC0 0x42004800 Reserved 0x42004C00 Reserved 0x42005000 AC 0x42005400 Reserved 0x42005800 PTC 0x42005C00 CCL 0x42006000 Reserved 0x42FFFFFF

# AHB-APB Bridge D

| 0                        | 0        |

|--------------------------|----------|

| 0x43000000<br>0x43000400 | SERCOM6  |

|                          | SERCOM7  |

| 0x43000800               | TC5      |

| 0x43000C00               | TC6      |

|                          | TC7      |

| 0x43001400               | Reserved |

| 0x43001800               |          |

| 0x40000000 | PAC        |

|------------|------------|

| 0x40000400 | PM         |

| 0x40000800 | MCLK       |

| 0x40000C00 | RSTC       |

| 0x40001000 | OSCCTRL    |

| 0x40001400 | OSC32KCTRL |

| 0x40001800 | SUPC       |

| 0x40001C00 | GCLK       |

| 0x40002000 | WDT        |

| 0x40002400 | RTC        |

| 0x40002800 | EIC        |

| 0x40002C00 | FREQM      |

| 0x40003000 | TSENS      |

| 0x40003400 |            |

| 0x40FFFFFF | Reserved   |

AHB-APB

Bridge D

AHB

DIVAS

AHB-APB Bridge B

PORT

DSU

NVMCTRL

DMAC

MTB

Reserved

0x48000000

0x480001FF

0x41000000

0x41002000

0x41004000

0x41006000

0x41008000

0x41009000

0x41FFFFFF

#### PM – Power Manager

#### 11.4.3 Clocks

The PAC bus clock (CLK\_PAC\_APB) can be enabled and disabled in the Main Clock module. The default state of CLK\_PAC\_APB can be found in the related links.

#### Related Links

MCLK – Main Clock Peripheral Clock Masking

#### 11.4.4 DMA

Not applicable.

#### 11.4.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the PAC interrupt requires the Interrupt Controller to be configured first.

#### Table 11-1. Interrupt Lines

| Instances | NVIC Line |

|-----------|-----------|

| PAC       | PACERR    |

#### **Related Links**

Nested Vector Interrupt Controller

### 11.4.6 Events

The events are connected to the Event System, which may need configuration.

#### Related Links

EVSYS – Event System

#### 11.4.7 Debug Operation

When the CPU is halted in debug mode, write protection of all peripherals is disabled and the PAC continues normal operation.

#### 11.4.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Write Control (WRCTRL) register

- AHB Slave Bus Interrupt Flag Status and Clear (INTFLAGAHB) register

- Peripheral Interrupt Flag Status and Clear n (INTFLAG A/B/C...) registers

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

# 11.5 Functional Description

### 11.5.1 Principle of Operation

The Peripheral Access Control module allows the user to set a write protection on peripheral modules and generate an interrupt in case of a peripheral access violation. The peripheral's protection can be set,

| Access<br>Reset<br>Bit | t    | 22        |             |    |    |           |             |    |

|------------------------|------|-----------|-------------|----|----|-----------|-------------|----|

| Reset                  | t    | 22        |             |    |    |           |             |    |

|                        |      | 22        |             |    |    |           |             |    |

| Bit                    | t 23 | 22        |             |    |    |           |             |    |

| Bit                    | t 23 | 22        |             |    |    |           |             |    |

|                        |      | 22        | 21          | 20 | 19 | 18        | 17          | 16 |

|                        |      |           |             |    |    |           |             |    |

| Access                 | 3    |           |             |    | 1  |           |             |    |

| Reset                  | t    |           |             |    |    |           |             |    |

|                        |      |           |             |    |    |           |             |    |

| Bit                    | t 15 | 14        | 13          | 12 | 11 | 10        | 9           | 8  |

|                        |      |           |             |    |    |           |             |    |

| Access                 | s    |           |             |    | I  |           |             |    |

| Reset                  | t    |           |             |    |    |           |             |    |

|                        |      |           |             |    |    |           |             |    |

| Bit                    | t 7  | 6         | 5           | 4  | 3  | 2         | 1           | 0  |

|                        |      | FKBC      | C[3:0]      |    |    | JEPC      | C[3:0]      |    |

|                        | s R  | R         | R           | R  | R  | R         | R           | R  |

| Access                 | , ,, | 0         | 0           | 0  | 0  | 0         | 0           | 0  |

| Reset                  | t 7  | FKBC<br>R | C[3:0]<br>R | R  | R  | JEPC<br>R | C[3:0]<br>R |    |

# Bits 7:4 – FKBC[3:0]: 4KB Count

These bits will always return zero when read, indicating that this debug component occupies one 4KB block.

#### Bits 3:0 – JEPCC[3:0]: JEP-106 Continuation Code

These bits will always return zero when read.

# 13.13.15 Peripheral Identification 0

Name:

PID0

Offset:

0x1FE0

Reset:

0x0000000

Property:

| Bit    | 31 | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----|----|----|--------|-----------|----|----|----|

|        |    |    |    |        |           |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |    |    |    |        |           |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |    |    |    |        |           |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

|        |    |    |    | PREAMB | LEB3[7:0] |    |    |    |

| Access | R  | R  | R  | R      | R         | R  | R  | R  |

| Reset  | 1  | 0  | 1  | 1      | 0         | 0  | 0  | 1  |

|        |    |    |    |        |           |    |    |    |

Bits 7:0 – PREAMBLEB3[7:0]: Preamble Byte 3

These bits will always return 0x000000B1 when read.

#### 17.5.2 Power Management

The MCLK will operate in all sleep modes if a synchronous clock is required in these modes.

#### **Related Links**

PM - Power Manager

#### 17.5.3 Clocks

The MCLK bus clock (CLK\_MCLK\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_MCLK\_APB can be found in the Peripheral Clock Masking section. If this clock is disabled, it can only be re-enabled by a reset.

The Generic Clock GCLK\_MAIN is required to generate the Main Clocks. GCLK\_MAIN is configured in the Generic Clock Controller, and can be re-configured by the user if needed.

#### **Related Links**

GCLK - Generic Clock Controller Peripheral Clock Masking

#### 17.5.3.1 Main Clock

The main clock GCLK\_MAIN is the common source for the synchronous clocks. This is fed into the common 8-bit prescaler that is used to generate synchronous clocks to the CPU, AHBx, and APBx modules.

### 17.5.3.2 CPU Clock

The CPU clock (CLK\_CPU) is routed to the CPU. Halting the CPU clock inhibits the CPU from executing instructions.

#### 17.5.3.3 APBx and AHBx Clock

The APBx clocks (CLK\_APBx) and the AHBx clocks (CLK\_AHBx) are the root clock source used by modules requiring a clock on the APBx and the AHBx bus. These clocks are always synchronous to the CPU clock, and can run even when the CPU clock is turned off in sleep mode. A clock gater is inserted after the common APB clock to gate any APBx clock of a module on APBx bus, as well as the AHBx clock.

#### 17.5.3.4 Clock Domains

The device has these synchronous clock domains:

• CPU synchronous clock domain (CPU Clock Domain). Frequency is f<sub>CPU</sub>.

See also the related links for the clock domain partitioning.

#### **Related Links**

Peripheral Clock Masking

### 17.5.4 DMA

Not applicable.

#### 17.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the MCLK interrupt requires the Interrupt Controller to be configured first.

#### 17.5.6 Events

Not applicable.

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0x6          | 64                                  | 3                              | 1953                                |

| 0x7          | 128                                 | 3                              | 3906                                |

| 0x8          | 256                                 | 3                              | 7813                                |

| 0x9          | 512                                 | 3                              | 15625                               |

| 0xA          | 1024                                | 3                              | 31250                               |

| 0xB          | 2048                                | 3                              | 62500µs                             |

| 0xC          | 4096                                | 3                              | 125000                              |

| 0xD          | 8192                                | 3                              | 250000                              |

| 0xE          | 16384                               | 3                              | 500000                              |

| 0xF          | 32768                               | 3                              | 1000000                             |

#### Note:

- 1. Actual startup time is 1 OSCULP32K cycle + 3 XOSC cycles.

- 2. The given time neglects the three XOSC cycles before OSCULP32K cycle.

#### **Bit 11 – AMPGC:** Automatic Amplitude Gain Control

**Note:** This bit must be set only after the XOSC has settled, indicated by the XOSC Ready flag in the Status register (STATUS.XOSCRDY).

| Value | Description                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The automatic amplitude gain control is disabled.                                                                                   |

| 1     | The automatic amplitude gain control is enabled. Amplitude gain will be automatically adjusted during Crystal Oscillator operation. |

#### Bits 10:8 – GAIN[2:0]: Oscillator Gain

These bits select the gain for the oscillator. The listed maximum frequencies are recommendations, and might vary based on capacitive load and crystal characteristics. Those bits must be properly configured even when the Automatic Amplitude Gain Control is active.

| Value   | Recommended Max Frequency [MHz] |

|---------|---------------------------------|

| 0x0     | 2                               |

| 0x1     | 4                               |

| 0x2     | 8                               |

| 0x3     | 16                              |

| 0x4     | 30                              |

| 0x5-0x7 | Reserved                        |

#### Bit 7 – ONDEMAND: On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled, depending on peripheral clock requests.

| Bit    | 7        | 6        | 5 | 4 | 3 | 2 | 1      | 0 |

|--------|----------|----------|---|---|---|---|--------|---|

|        | ONDEMAND | RUNSTDBY |   |   |   |   | ENABLE |   |

| Access | R/W      | R/W      |   |   |   |   | R/W    |   |

| Reset  | 1        | 0        |   |   |   |   | 1      |   |

#### Bit 7 – ONDEMAND: On Demand Control

The On Demand operation mode allows the oscillator to be enabled or disabled depending on peripheral clock requests.

If the ONDEMAND bit has been previously written to '1', the oscillator will only be running when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                                                                                                           |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock source. The oscillator is disabled if no peripheral is requesting the clock source. |

#### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the OSC48M behaves during standby sleep mode.

| Value | Description                                                                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OSC48M is disabled in standby sleep mode if no peripheral requests the clock.                                                                                          |

| 1     | The OSC48M is not stopped in standby sleep mode. If ONDEMAND=1, the OSC48M will be running when a peripheral is requesting the clock. If ONDEMAND=0, the clock source will |

|       | always be running in standby sleep mode.                                                                                                                                   |

#### Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

### 20.8.9 OSC48M Divider

| Name:     | OSC48MDIV          |

|-----------|--------------------|

| Offset:   | 0x15 [ID-00001eee] |

| Reset:    | 0x0B               |

| Property: | -                  |

| Bit    | 7 | 6 | 5 | 4 | 3   | 2   | 1     | 0   |

|--------|---|---|---|---|-----|-----|-------|-----|

|        |   |   |   |   |     | DIV | [3:0] |     |

| Access |   |   |   |   | R/W | R/W | R/W   | R/W |

| Reset  |   |   |   |   | 1   | 0   | 1     | 1   |

#### Bits 3:0 – DIV[3:0]: Oscillator Divider Selection

These bits control the oscillator frequency range by adjusting the division ratio. The oscillator frequency is 48MHz divided by DIV+1.

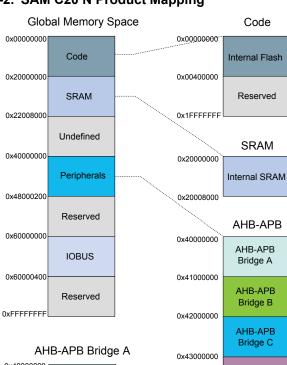

$\begin{array}{c} \text{OSC32KCTRL} \xrightarrow{\text{CLK}_{\text{RTC}} \text{OSC}} & \text{PRESCALER} & \xrightarrow{\text{CLK}_{\text{RTC}} \text{CN}} & \xrightarrow{\text{OX0000}} \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & & \\ & &$

Figure 24-2. RTC Block Diagram (Mode 1 — 16-Bit Counter)

Figure 24-3. RTC Block Diagram (Mode 2 — Clock/Calendar)

Related Links 32-Bit Counter (Mode 0) 16-Bit Counter (Mode 1) Clock/Calendar (Mode 2)

# 24.4 Signal Description

Not applicable.

# 24.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 24.5.1 I/O Lines

Not applicable.

# 24.5.2 Power Management

The RTC will continue to operate in any sleep mode where the selected source clock is running. The RTC interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes. Refer to the *Power Manager* for details on the different sleep modes.

The RTC will be reset only at power-on (POR) or by setting the Software Reset bit in the Control A register (CTRLA.SWRST=1).

#### **Related Links**

© 2017 Microchip Technology Inc.

descriptor. The benefit of having descriptor memory and write-back memory in the same section is that it requires less SRAM. In addition, the latency from fetching the first descriptor of a transaction to the first burst transfer is executed, is reduced.

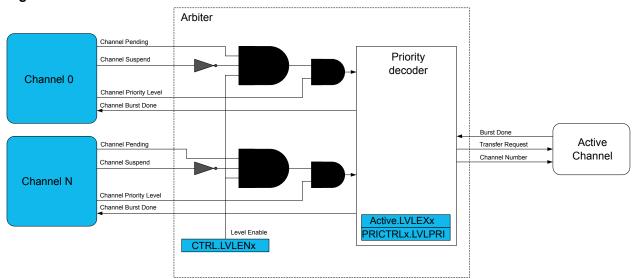

#### 25.6.2.4 Arbitration

If a DMA channel is enabled and not suspended when it receives a transfer trigger, it will send a transfer request to the arbiter. When the arbiter receives the transfer request it will include the DMA channel in the queue of channels having pending transfers, and the corresponding Pending Channel x bit in the Pending Channels registers (PENDCH.PENDCHx) will be set. Depending on the arbitration scheme, the arbiter will choose which DMA channel will be the next active channel. The active channel is the DMA channel being granted access to perform its next burst transfer. When the arbiter has granted a DMA channel access to the DMAC, the corresponding bit PENDCH.PENDCHx will be cleared. See also the following figure.

If the upcoming burst transfer is the first for the transfer request, the corresponding Busy Channel x bit in the Busy Channels register will be set (BUSYCH.BUSYCHx=1), and it will remain '1' for the subsequent granted burst transfers.

When the channel has performed its granted burst transfer(s) it will be either fed into the queue of channels with pending transfers, set to be waiting for a new transfer trigger, suspended, or disabled. This depends on the channel and block transfer configuration. If the DMA channel is fed into the queue of channels with pending transfers, the corresponding BUSYCH.BUSYCHx will remain '1'. If the DMA channel is set to wait for a new transfer trigger, suspended, or disabled, the corresponding BUSYCH.BUSYCHx will be cleared.

If a DMA channel is suspended while it has a pending transfer, it will be removed from the queue of pending channels, but the corresponding PENDCH.PENDCHx will remain set. When the same DMA channel is resumed, it will be added to the queue of pending channels again.

If a DMA channel gets disabled (CHCTRLA.ENABLE=0) while it has a pending transfer, it will be removed from the queue of pending channels, and the corresponding PENDCH.PENDCHx will be cleared.

# **Priority Levels**

When a channel level is pending or the channel is transferring data, the corresponding Level Executing bit is set in the Active Channel and Levels register (ACTIVE.LVLEXx).

| Offset | Name     | Bit Pos. |        |  |        |      |        |

|--------|----------|----------|--------|--|--------|------|--------|

| 0x5B   | PINCFG27 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5C   | PINCFG28 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5D   | PINCFG29 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5E   | PINCFG30 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5F   | PINCFG31 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

# 28.8 PORT Pin Groups and Register Repetition

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

# 28.9 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

#### 28.9.1 Data Direction

This register allows the user to configure one or more I/O pins as an input or output. This register can be manipulated without doing a read-modify-write operation by using the Data Direction Toggle (DIRTGL), Data Direction Clear (DIRCLR) and Data Direction Set (DIRSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

Name:DIROffset:0x00Reset:0x0000000Property:PAC Write-Protection

| Value     | Channel Number             |

|-----------|----------------------------|

| 0x00      | No channel output selected |

| 0x01      | 0                          |

| 0x02      | 1                          |

| 0x03      | 2                          |

| 0x04      | 3                          |

| 0x05      | 4                          |

| 0x06      | 5                          |

| 0x07      | 6                          |

| 0x08      | 7                          |

| 0x09      | 8                          |

| 0x0A      | 9                          |

| 0x0B      | 10                         |

| 0x0C      | 11                         |

| 0x0D-0xFF | Reserved                   |

# Table 29-3. User Multiplexer Number

| USERm | User Multiplexer       | Description        | Path Type                                                            |

|-------|------------------------|--------------------|----------------------------------------------------------------------|

| m = 0 | TSENS<br>STARTReserved | Start measurement- | Asynchronous,<br>synchronous, and<br>resynchronized<br>pathsReserved |

| m = 1 | PORT EV0               | Event 0            | Asynchronous path only                                               |

| m = 2 | PORT EV1               | Event 1            | Asynchronous path only                                               |

| m = 3 | PORT EV2               | Event 2            | Asynchronous path only                                               |

| m = 4 | PORT EV3               | Event 3            | Asynchronous path only                                               |

| m = 5 | DMAC CH0               | Channel 0          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 6 | DMAC CH1               | Channel 1          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 7 | DMAC CH2               | Channel 2          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

| m = 8 | DMAC CH3               | Channel 3          | Asynchronous,<br>synchronous, and<br>resynchronized paths            |

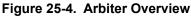

# 31.3 Block Diagram

Figure 31-1. USART Block Diagram

# 31.4 Signal Description

#### Table 31-1. SERCOM USART Signals

| Signal Name | Туре        | Description         |

|-------------|-------------|---------------------|

| PAD[3:0]    | Digital I/O | General SERCOM pins |

One signal can be mapped to one of several pins.

#### **Related Links**

I/O Multiplexing and Considerations

# 31.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 31.5.1 I/O Lines

Using the USART's I/O lines requires the I/O pins to be configured using the I/O Pin Controller (PORT).

When the SERCOM is used in USART mode, the SERCOM controls the direction and value of the I/O pins according to the table below. Both PORT control bits PINCFGn.PULLEN and PINCFGn.DRVSTR are still effective. If the receiver or transmitter is disabled, these pins can be used for other purposes.

#### Table 31-2. USART Pin Configuration

| Pin | Pin Configuration |

|-----|-------------------|

| TxD | Output            |

| RxD | Input             |

| ХСК | Output or input   |

The combined configuration of PORT and the Transmit Data Pinout and Receive Data Pinout bit fields in the Control A register (CTRLA.TXPO and CTRLA.RXPO, respectively) will define the physical position of the USART signals in Table 31-2.

data bit is shifted in. And the Receive Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set. The received data can be retrieved by reading DATA.

When the last character has been transmitted and there is no valid data in DATA, the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set. When the transaction is finished, the master must pull the  $\overline{SS}$  line high to notify the slave. If Master Slave Select Enable (CTRLB.MSSEN) is set to '0', the software must pull the  $\overline{SS}$  line high.

#### Slave

In slave mode (CTRLA.MODE=0x2), the SPI interface will remain inactive with the MISO line tri-stated as long as the  $\overline{SS}$  pin is pulled high. Software may update the contents of DATA at any time as long as the Data Register Empty flag in the Interrupt Status and Clear register (INTFLAG.DRE) is set.

When  $\overline{SS}$  is pulled low and SCK is running, the slave will sample and shift out data according to the transaction mode set. When the content of TxDATA has been loaded into the shift register, INTFLAG.DRE will be set, and new data can be written to DATA.

Similar to the master, the slave will receive one character for each character transmitted. A character will be transferred into the two-level receive buffer within the same clock cycle its last data bit is received. The received character can be retrieved from DATA when the Receive Complete interrupt flag (INTFLAG.RXC) is set.

When the master pulls the  $\overline{SS}$  line high, the transaction is done and the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set.

After DATA is written it takes up to three SCK clock cycles until the content of DATA is ready to be loaded into the shift register on the next character boundary. As a consequence, the first character transferred in a SPI transaction will not be the content of DATA. This can be avoided by using the preloading feature. Refer to Preloading of the Slave Shift Register.

When transmitting several characters in one SPI transaction, the data has to be written into DATA register with at least three SCK clock cycles left in the current character transmission. If this criteria is not met, the previously received character will be transmitted.

Once the DATA register is empty, it takes three CLK\_SERCOM\_APB cycles for INTFLAG.DRE to be set.

#### 32.6.2.7 Receiver Error Bit

The SPI receiver has one error bit: the Buffer Overflow bit (BUFOVF), which can be read from the Status register (STATUS). Once an error happens, the bit will stay set until it is cleared by writing '1' to it. The bit is also automatically cleared when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the immediate buffer overflow notification bit in the Control A register (CTRLA.IBON):

If CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA until the receiver complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) goes low.

If CTRLA.IBON=0, the buffer overflow condition travels with data through the receive FIFO. After the received data is read, STATUS.BUFOVF and INTFLAG.ERROR will be set along with INTFLAG.RXC, and RxDATA will be zero.

#### 32.6.3 Additional Features

#### 32.6.3.1 Address Recognition

When the SPI is configured for slave operation (CTRLA.MODE=0x2) with address recognition (CTRLA.FORM is 0x2), the SERCOM address recognition logic is enabled: the first character in a transaction is checked for an address match.

0x2: SPI slave operation

0x3: SPI master operation

These bits are not synchronized.

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRL.ENABLE will read back immediately and the Synchronization Enable Busy bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the operation is complete.

This bit is not enable-protected.

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | The peripheral is disabled or being disabled. |

| 1     | The peripheral is enabled or being enabled.   |

#### Bit 0 – SWRST: Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the SERCOM, except DBGCTRL, to their initial state, and the SERCOM will be disabled.

Writing "1' to CTRL.SWRST will always take precedence, meaning that all other writes in the same writeoperation will be discarded. Any register write access during the ongoing reset will result in an APB error. Reading any register will return the reset value of the register.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY. SWRST will both be cleared when the reset is complete.

This bit is not enable-protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 32.8.2 Control B

Name:CTRLBOffset:0x04Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 15      | 14      | 13    | 12       | 11 | 10     | 9        | 8        |

|--------|---------|---------|-------|----------|----|--------|----------|----------|

|        |         |         |       |          |    | LENERR | SEXTTOUT | MEXTTOUT |

| Access |         |         |       |          |    | R/W    | R/W      | R/W      |

| Reset  |         |         |       |          |    | 0      | 0        | 0        |

|        |         |         |       |          |    |        |          |          |

| Bit    | 7       | 6       | 5     | 4        | 3  | 2      | 1        | 0        |

|        | CLKHOLD | LOWTOUT | BUSST | ATE[1:0] |    | RXNACK | ARBLOST  | BUSERR   |

| Access | R       | R/W     | R     | R        |    | R      | R/W      | R/W      |

| Reset  | 0       | 0       | 0     | 0        |    | 0      | 0        | 0        |

#### Bit 10 – LENERR: Transaction Length Error

This bit is set when automatic length is used for a DMA transaction and the slave sends a NACK before ADDR.LEN bytes have been written by the master.

Writing '1' to this bit location will clear STATUS.LENERR. This flag is automatically cleared when writing to the ADDR register.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

#### Bit 9 – SEXTTOUT: Slave SCL Low Extend Time-Out

This bit is set if a slave SCL low extend time-out occurs.

This bit is automatically cleared when writing to the ADDR register.

Writing '1' to this bit location will clear SEXTTOUT. Normal use of the I<sup>2</sup>C interface does not require the SEXTTOUT flag to be cleared by this method.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

#### Bit 8 – MEXTTOUT: Master SCL Low Extend Time-Out

This bit is set if a master SCL low time-out occurs.

Writing '1' to this bit location will clear STATUS.MEXTTOUT. This flag is automatically cleared when writing to the ADDR register.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

#### Bit 7 – CLKHOLD: Clock Hold

This bit is set when the master is holding the SCL line low, stretching the I<sup>2</sup>C clock. Software should consider this bit when INTFLAG.SB or INTFLAG.MB is set.

This bit is cleared when the corresponding interrupt flag is cleared and the next operation is given.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

This bit is not write-synchronized.

#### Bit 6 – LOWTOUT: SCL Low Time-Out

This bit is set if an SCL low time-out occurs.

| Value | Description         |

|-------|---------------------|

| 0     | Tx FIFO operation.  |

| 1     | Tx Queue operation. |

#### Bits 29:24 – TFQS[5:0]: Transmit FIFO/Queue Size

| Value  | Description                                   |

|--------|-----------------------------------------------|

| 0      | No Tx FIFO/Queue.                             |

| 1 - 32 | Number of Tx Buffers used for Tx FIFO/Queue.  |

| >32    | Values greater than 32 are interpreted as 32. |

#### Bits 21:16 – NDTB[5:0]: Number of Dedicated Transmit Buffers

| Value  | Description                                   |

|--------|-----------------------------------------------|

| 0      | No Tx FIFO/Queue.                             |

| 1 - 32 | Number of Tx Buffers used for Tx FIFO/Queue.  |

| >32    | Values greater than 32 are interpreted as 32. |

#### Bits 15:0 – TBSA[15:0]: Tx Buffers Start Address

Start address of Tx Buffers section in Message RAM. When the CAN module addresses the Message RAM it addresses 32-bit words, not single bytes. The configurable start addresses are 32-bit word addresses, i.e. only bits 15 to 2 are evaluated, the two least significant bits are ignored. Bits 1 to 0 will always be read back as "00".

#### 34.8.36 Tx FIFO/Queue Status

**Note:** In case of mixed configurations where dedicated Tx Buffers are combined with a Tx FIFO or a Tx Queue, the Put and Get Indexes indicate the number of the Tx Buffer starting with the first dedicated Tx Buffers. Example: For a configuration of 12 dedicated Tx Buffers and a Tx FIFO of 20 Buffers a Put Index of 15 points to the fourth buffer of the Tx FIFO.

Name:TXFQSOffset:0xC4 [ID-0000a4bb]Reset:0x00000000Property:Read-only

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | The Overrun interrupt is disabled.                                                    |

| 1     | The Overrun interrupt is enabled, and an interrupt request will be generated when the |

|       | Overrun interrupt flag is set.                                                        |

#### Bit 0 – RESRDY: Result Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Result Ready Interrupt Enable bit, which disables the corresponding interrupt request.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The Result Ready interrupt is disabled.                                                    |

| 1     | The Result Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | Result Ready interrupt flag is set.                                                        |

#### 38.8.6 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

Name:INTENSETOffset:0x05 [ID-0000120e]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2      | 1       | 0      |

|--------|---|---|---|---|---|--------|---------|--------|

|        |   |   |   |   |   | WINMON | OVERRUN | RESRDY |

| Access |   |   |   |   |   | R/W    | R/W     | R/W    |

| Reset  |   |   |   |   |   | 0      | 0       | 0      |

#### Bit 2 – WINMON: Window Monitor Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Window Monitor Interrupt bit, which enables the Window Monitor interrupt.

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Window Monitor interrupt is disabled. |

| 1     | The Window Monitor interrupt is enabled.  |

#### Bit 1 – OVERRUN: Overrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overrun Interrupt bit, which enables the Overrun interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Overrun interrupt is disabled. |

| 1     | The Overrun interrupt is enabled.  |

#### Bit 0 – RESRDY: Result Ready Interrupt Enable

Writing a '0' to this bit has no effect.

| Bit    | 31  | 30  | 29  | 28                | 27      | 26  | 25  | 24  |

|--------|-----|-----|-----|-------------------|---------|-----|-----|-----|

| Access |     |     |     |                   |         |     |     |     |

| Reset  |     |     |     |                   |         |     |     |     |

|        |     |     |     |                   |         |     |     |     |

| Bit    | 23  | 22  | 21  | 20                | 19      | 18  | 17  | 16  |

|        |     |     |     | WINUT             | [23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W               | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                 | 0       | 0   | 0   | 0   |

|        |     |     |     |                   |         |     |     |     |

| Bit    | 15  | 14  | 13  | 12                | 11      | 10  | 9   | 8   |

|        |     |     |     | WINU <sup>-</sup> | T[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W               | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                 | 0       | 0   | 0   | 0   |

|        |     |     |     |                   |         |     |     |     |

| Bit    | 7   | 6   | 5   | 4                 | 3       | 2   | 1   | 0   |

| [      |     |     |     | WINU              | T[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W               | R/W     | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                 | 0       | 0   | 0   | 0   |

# Bits 23:0 – WINUT[23:0]: Window Upper Threshold

If the window monitor is enabled, these bits define the upper threshold value.

### 39.8.14 Offset Correction

Name:OFFSETCORROffset:0x14 [ID-0000243d]Reset:0x0000000Property:PAC Write-Protection, Write-Synchronized

| Symbol             | Parameter | Conditions                           |                                              | Meas | Unit    |        |    |

|--------------------|-----------|--------------------------------------|----------------------------------------------|------|---------|--------|----|

|                    |           |                                      |                                              | Min  | Тур     | Max    |    |

|                    |           |                                      | Vddana=5.0V<br>Vref=Vddana/2                 | -    | +/-0.01 | +/-5.6 |    |

|                    |           |                                      | Vddana=2.7V Vref=2.0V                        | -    | +/-0.4  | +/-4.2 |    |

| SFDR               |           | Spurious Free Dynamic Range          | Fs = 1Msps / Fin = 14                        | 63   | 71      | 81     | dB |

| SINAD(1)           |           | Signal to Noise and Distortion ratio | kHz / Full range Input<br>signal Vddana=5.0V | 60   | 65      | 70     |    |

| SNR at -3 db<br>FS |           | Signal to Noise ratio                | Mark Malalana                                |      | 70      |        |    |

| THD                |           | Total Harmonic Distortion            | -                                            | 63   | -70     | 81     |    |

|                    |           | Noise RMS                            | External Reference voltage                   | -    | 0.4     | 3.2    | mV |

- 1. Referred to Full Scale.

- 2. Dynamical input range is +/-6% of Full scale.

# Table 47-7. Single-Ended Mode

| Symbol              | Parameter                     | Conditions                                                     |                                | Mea                     | surement  |         | Unit    |  |

|---------------------|-------------------------------|----------------------------------------------------------------|--------------------------------|-------------------------|-----------|---------|---------|--|

|                     |                               |                                                                |                                | Min                     | Тур       | Max     |         |  |

| ENOB <sup>(1)</sup> | Effective Number of           | Fadc = 500 ksps - R2R disabled                                 | Vddana=3.0V Vref=Vddana        | 9.0                     | 9.7       | 10.2    | bits    |  |

|                     | bits                          |                                                                | Vddana=3.0V Vref=2.0V          | 9.0                     | 9.6       | 10.1    |         |  |

|                     |                               | Fadc = 1 Msps - R2R disabled                                   | Vddana=3.0V Vref=Vddana        | 8.9                     | 9.6       | 10.0    |         |  |

|                     |                               |                                                                | Vddana=3.0V Vref=2.0V          | 8.9                     | 9.4       | 9.7     |         |  |

| TUE                 | Total Unadjusted              | Fadc = 500 ksps - R2R disabled with                            | Vddana=5.0V Vref=Vddana        | -                       | +/-12.9   | +/-25.2 | LSB     |  |

|                     | Error                         | offset and gain compensation                                   | Vddana=2.7V Vref=2.0V          | -                       | +/-25     | +/-49.6 |         |  |

|                     |                               | Fadc = 1 Msps - R2R disabled with offset and gain compensation | Vddana=5.0V Vref=Vddana        | -                       | +/-13.5   | +/-26.4 |         |  |

|                     |                               |                                                                | Vddana=2.7V Vref=2.0V          | -                       | +/-27     | +/-52   |         |  |

| INL                 | Integral Non<br>Linearity     | Fadc = 500 ksps - R2R disabled                                 | Vddana=5.0V Vref=Vddana        | -                       | +/-3.7    | +/-6.5  |         |  |

|                     |                               |                                                                | Vddana=2.7V Vref=2.0V          | -                       | +/-3.4    | +/-5.9  |         |  |

|                     |                               | Fadc = 1 Msps - R2R disabled                                   | Vddana=5.0V Vref=Vddana        | -                       | +/-4.2    | +/-7.4  | LSB     |  |

|                     |                               |                                                                | Vddana=2.7V Vref=2.0V          | -                       | +/-3.5    | +/-6.2  |         |  |

| DNL                 | Differential Non<br>Linearity |                                                                | Vddana=5.0V Vref=Vddana        | -                       | -0.9/+1.2 | -1/+1.6 |         |  |

|                     |                               |                                                                | Vddana=2.7V Vref=2.0V          | -                       | -0.9/+1.3 | -1/+2.3 |         |  |

|                     |                               | Fadc = 1 Msps - R2R disabled                                   | Fadc = 1 Msps - R2R disabled   | Vddana=5.0V Vref=Vddana | -         | -1/+1.1 | -1/+1.3 |  |

|                     |                               |                                                                | Vddana=2.7V Vref=2.0V          | -                       | -1/+1.4   | -1/+3.1 |         |  |

| Gain                | Gain Error                    | Fadc = 1 Msps - R2R disabled w/o gain                          | Vddana=5.0V Vref=Vddana        | -                       | +/-0.2    | +/-0.7  | %       |  |

|                     |                               | compensation                                                   | Vddana=2.7V Vref=2.0V          | -                       | +/-0.3    | +/-1.4  |         |  |

|                     |                               |                                                                | Vddana=5.0V 1V internal<br>Ref | -                       | +/-1.6    | +/-6.6  |         |  |

|                     |                               |                                                                | Vddana=5.0V<br>Vref=Vddana/2   | -                       | +/-0.2    | +/-1.1  |         |  |

| Table 48-14. Device and Package Maximum Weight |        |  |  |  |  |

|------------------------------------------------|--------|--|--|--|--|

| 140 mg                                         |        |  |  |  |  |

| Table 48-15. Package Characteristics           |        |  |  |  |  |

| Moisture Sensitivity Level                     | MSL3   |  |  |  |  |

| Table 48-16. Package Reference                 |        |  |  |  |  |

| JEDEC Drawing Reference                        | MS-026 |  |  |  |  |

| JESD97 Classification E3                       |        |  |  |  |  |