#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 84                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 12x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc20n17a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Peripheral<br>Name | Base<br>Address | IRQ<br>Line | AHI   | B Clock             | API | B Clock             | Generic<br>Clock     | F     | PAC              |         | Events                  | DMA                        |                  |

|--------------------|-----------------|-------------|-------|---------------------|-----|---------------------|----------------------|-------|------------------|---------|-------------------------|----------------------------|------------------|

|                    |                 |             | Index | Enabled<br>at Reset |     | Enabled<br>at Reset | Index                | Index | Prot at<br>Reset | User    | Generator               | Index                      | Sleep<br>Walking |

| SERCOM7            | 0x43000400      | 10          |       |                     | 1   | N                   | 42: CORE<br>18: SLOW | 1     | N                |         |                         | 51: RX<br>52: TX           | Y                |

| TC5                | 0x43000800      | 20          |       |                     | 2   | N                   | 43                   | 2     | N                | 47: EVU | 87: OVF<br>88-89: MC0-1 | 53: OVF<br>54-55:<br>MC0-1 | Y                |

| TC6                | 0x43000C00      | 21          |       |                     | 3   | Ν                   | 44                   | 3     | N                | 48:EVU  | 90: OVF<br>91-92: MC0-1 | 56: OVF<br>57-58:<br>MC0-1 | Y                |

| TC7                | 0x43001000      | 22          |       |                     | 4   | Ν                   | 45                   | 4     | N                | 49:EVU  | 93: OVF<br>94-95: MC0-1 | 59: OVF<br>60-61:<br>MC0-1 | Y                |

| DIVAS              | 0x48000000      |             | 12    | Y                   |     |                     |                      |       |                  |         |                         |                            | N/A              |

# Table 12-2. Peripherals Configuration Summary SAM C20 N

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | B Clock             | AP    | B Clock             | Generic<br>Clock                                  | F     | PAC              |                       | Events                                                 | DMA   |                 |

|---------------------|-----------------|-------------|-------|---------------------|-------|---------------------|---------------------------------------------------|-------|------------------|-----------------------|--------------------------------------------------------|-------|-----------------|

|                     |                 |             | Index | Enabled<br>at Reset | Index | Enabled<br>at Reset | Index                                             | Index | Prot at<br>Reset | User                  | Generator                                              | Index | Sleep<br>Walkin |

| AHB-APB<br>Bridge A | 0x40000000      |             | 0     | Y                   |       |                     |                                                   |       |                  |                       |                                                        |       | N/A             |

| PAC                 | 0x40000000      | 0           | 10    | Y                   | 0     | Y                   |                                                   | 0     | N                |                       | 85 : ACCERR                                            |       | N/A             |

| PM                  | 0x40000400      | 0           |       |                     | 1     | Y                   |                                                   | 1     | N                |                       |                                                        |       | N/A             |

| MCLK                | 0x40000800      | 0           |       |                     | 2     | Y                   |                                                   | 2     | N                |                       |                                                        |       | Y               |

| RSTC                | 0x40000C00      |             |       |                     | 3     | Y                   |                                                   | 3     | N                |                       |                                                        |       | N/A             |

| OSCCTRL             | 0x40001000      | 0           |       |                     | 4     | Y                   | 0: FDPLL96M<br>clk source<br>1: FDPLL96M<br>32kHz |       | N                |                       | 0: XOSC_FAIL                                           |       | Y               |

| OSC32KCTRL          | 0x40001400      | 0           |       |                     | 5     | Y                   |                                                   | 5     | N                |                       | 1: XOSC32K_FAIL                                        |       | Y               |

| SUPC                | 0x40001800      | 0           |       |                     | 6     | Y                   |                                                   | 6     | N                |                       |                                                        |       | N/A             |

| GCLK                | 0x40001C00      |             |       |                     | 7     | Y                   |                                                   | 7     | N                |                       |                                                        |       | N/A             |

| WDT                 | 0x40002000      | 1           |       |                     | 8     | Y                   |                                                   | 8     | N                |                       |                                                        |       | Y               |

| RTC                 | 0x40002400      | 2           |       |                     | 9     | Y                   |                                                   | 9     | N                |                       | 2: CMP0/ALARM0<br>3: CMP1<br>4: OVF5-1<br>5:12: PER0-7 |       | Y               |

| EIC                 | 0x40002800      | 3,<br>NMI   |       |                     | 10    | Y                   | 2                                                 | 10    | N                |                       | 13-28: EXTINT0-15                                      |       | Y               |

| FREQM               | 0x40002C00      | 4           |       |                     | 11    | Y                   | 3: Measure<br>4: Reference                        | 11    | N                |                       |                                                        |       | N/A             |

| AHB-APB<br>Bridge B | 0x41000000      |             | 1     | Y                   |       |                     |                                                   |       |                  |                       |                                                        |       | N/A             |

| PORT                | 0x41000000      |             |       |                     | 0     | Y                   |                                                   | 0     | N                | 1-4 : EV0-3           |                                                        |       | Y               |

| DSU                 | 0x41002000      |             | 3     | Y                   | 1     | Y                   |                                                   | 1     | Y                |                       |                                                        |       | N/A             |

| NVMCTRL             | 0x41004000      | 6           | 5     | Y                   | 2     | Y                   | 39                                                | 2     | N                |                       |                                                        |       | Y               |

| DMAC                | 0x41006000      | 7           | 7     | Y                   |       |                     |                                                   | 3     | Ν                | 5-8: CH0-3            | 30-33: CH0-3                                           |       | Y               |

| MTB                 | 0x41008000      |             |       |                     |       |                     |                                                   |       | N                | 45: START<br>46: STOP |                                                        |       | N/A             |

| AHB-APB<br>Bridge C | 0x42000000      |             | 2     | Y                   |       |                     |                                                   |       |                  |                       |                                                        |       | N/A             |

| EVSYS               | 0x42000000      | 8           |       |                     | 0     | N                   | 6-17: one per<br>CHANNEL                          | 0     | N                |                       |                                                        |       | Y               |

| Bit    | 31  | 30  | 29       | 28     | 27    | 26       | 25  | 24    |

|--------|-----|-----|----------|--------|-------|----------|-----|-------|

|        |     |     |          | DIV[   | 15:8] |          |     |       |

| Access | R/W | R/W | R/W      | R/W    | R/W   | R/W      | R/W | R/W   |

| Reset  | 0   | 0   | 0        | 0      | 0     | 0        | 0   | 0     |

|        |     |     |          |        |       |          |     |       |

| Bit    | 23  | 22  | 21       | 20     | 19    | 18       | 17  | 16    |

|        |     |     |          | DIV    | [7:0] |          |     |       |

| Access | R/W | R/W | R/W      | R/W    | R/W   | R/W      | R/W | R/W   |

| Reset  | 0   | 0   | 0        | 0      | 0     | 0        | 0   | 0     |

|        |     |     |          |        |       |          |     |       |

| Bit    | 15  | 14  | 13       | 12     | 11    | 10       | 9   | 8     |

|        |     |     | RUNSTDBY | DIVSEL | OE    | OOV      | IDC | GENEN |

| Access |     |     |          |        |       | •        |     |       |

| Reset  |     |     | 0        | 0      | 0     | 0        | 0   | 1     |

|        |     |     |          |        |       |          |     |       |

| Bit    | 7   | 6   | 5        | 4      | 3     | 2        | 1   | 0     |

|        |     |     |          |        |       | SRC[4:0] |     |       |

| Access | -   |     |          | R/W    | R/W   | R/W      | R/W | R/W   |

| Reset  |     |     |          | 0      | 0     | 0        | 0   | 0     |

## Bits 31:16 – DIV[15:0]: Division Factor

These bits represent a division value for the corresponding Generator. The actual division factor is dependent on the state of DIVSEL. The number of relevant DIV bits for each Generator can be seen in this table. Written bits outside of the specified range will be ignored.

#### Table 16-3. Division Factor Bits

| Generic Clock Generator | Division Factor Bits                |

|-------------------------|-------------------------------------|

| Generator 0             | 8 division factor bits - DIV[7:0]   |

| Generator 1             | 16 division factor bits - DIV[15:0] |

| Generator 2-11          | 8 division factor bits - DIV[4:0]   |

# Bit 13 - RUNSTDBY: Run in Standby

This bit is used to keep the Generator running in Standby as long as it is configured to output to a dedicated GCLK\_IO pin. If GENCTRLn.OE is zero, this bit has no effect and the generator will only be running if a peripheral requires the clock.

| Value | Description                                                                                                                  |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Generator is stopped in Standby and the GCLK_IO pin state (one or zero) will be dependent on the setting in GENCTRL.OOV. |

| 1     | The Generator is kept running and output to its dedicated GCLK_IO pin during Standby mode.                                   |

# Bit 12 – DIVSEL: Divide Selection

This bit determines how the division factor of the clock source of the Generator will be calculated from DIV. If the clock source should not be divided, DIVSEL must be 0 and the GENCTRLn.DIV value must be either 0 or 1.

| Bit    | 31      | 30 | 29 | 28  | 27  | 26         | 25  | 24  |

|--------|---------|----|----|-----|-----|------------|-----|-----|

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

| Reset  |         |    |    |     |     |            |     |     |

|        |         |    |    |     |     |            |     |     |

| Bit    | 23      | 22 | 21 | 20  | 19  | 18         | 17  | 16  |

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

| Reset  |         |    |    |     |     |            |     |     |

|        |         |    |    |     |     |            |     |     |

| Bit    | 15      | 14 | 13 | 12  | 11  | 10         | 9   | 8   |

|        | WRTLOCK |    |    |     |     | CALIB[4:0] |     |     |

| Access | R/W     |    |    | R/W | R/W | R/W        | R/W | R/W |

| Reset  | 0       |    |    | х   | х   | х          | х   | x   |

|        |         |    |    |     |     |            |     |     |

| Bit    | 7       | 6  | 5  | 4   | 3   | 2          | 1   | 0   |

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

Reset

## Bit 15 – WRTLOCK: Write Lock

This bit locks the OSCULP32K register for future writes to fix the OSCULP32K configuration.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The OSCULP32K configuration is not locked. |

| 1     | The OSCULP32K configuration is locked.     |

# Bits 12:8 – CALIB[4:0]: Oscillator Calibration

These bits control the oscillator calibration.

These bits are loaded from Flash Calibration at startup.

| Bit             | 31  | 30       | 29       | 28    | 27     | 26     | 25     | 24     |

|-----------------|-----|----------|----------|-------|--------|--------|--------|--------|

| Access<br>Reset |     |          |          |       |        |        |        |        |

| Bit             | 23  | 22       | 21       | 20    | 19     | 18     | 17     | 16     |

|                 |     |          |          |       | LEVE   | L[5:0] |        |        |

| Access          |     |          | R/W      | R/W   | R/W    | R/W    | R/W    | R/W    |

| Reset           |     |          | х        | x     | x      | х      | x      | х      |

| Bit             | 15  | 14       | 13       | 12    | 11     | 10     | 9      | 8      |

|                 |     | PSEI     | _[3:0]   |       |        |        |        | ACTCFG |

| Access          | R/W | R/W      | R/W      | R/W   |        |        |        | R/W    |

| Reset           | 0   | 0        | 0        | 0     |        |        |        | 0      |

|                 |     |          |          |       |        |        |        |        |

| Bit             | 7   | 6        | 5        | 4     | 3      | 2      | 1      | 0      |

|                 |     | RUNSTDBY | STDBYCFG | ACTIC | N[1:0] | HYST   | ENABLE |        |

| Access          |     | R/W      | R/W      | R/W   | R/W    | R/W    | R/W    |        |

| Reset           |     | 0        | 0        | x     | x      | x      | x      |        |

## Bits 21:16 – LEVEL[5:0]: BODVDD Threshold Level on VDD

These bits set the triggering voltage threshold for the BODVDD when the BODVDD monitors the VDD.

These bits are loaded from NVM User Row at start-up.

This bit field is not synchronized.

#### Bits 15:12 – PSEL[3:0]: Prescaler Select

Selects the prescaler divide-by output for the BODVDD sampling mode. The input clock comes from the OSCULP32K 1KHz output.

| Value | Name     | Description           |

|-------|----------|-----------------------|

| 0x0   | DIV2     | Divide clock by 2     |

| 0x1   | DIV4     | Divide clock by 4     |

| 0x2   | DIV8     | Divide clock by 8     |

| 0x3   | DIV16    | Divide clock by 16    |

| 0x4   | DIV32    | Divide clock by 32    |

| 0x5   | DIV64    | Divide clock by 64    |

| 0x6   | DIV128   | Divide clock by 128   |

| 0x7   | DIV256   | Divide clock by 256   |

| 0x8   | DIV512   | Divide clock by 512   |

| 0x9   | DIV1024  | Divide clock by 1024  |

| 0xA   | DIV2048  | Divide clock by 2048  |

| 0xB   | DIV4096  | Divide clock by 4096  |

| 0xC   | DIV8192  | Divide clock by 8192  |

| 0xD   | DIV16384 | Divide clock by 16384 |

| 0xE   | DIV32768 | Divide clock by 32768 |

| 0xF   | DIV65536 | Divide clock by 65536 |

# Bit 8 – ACTCFG: BODVDD Configuration in Active Sleep Mode

This bit is not synchronized.

## **Related Links**

Peripheral Clock Masking OSC32KCTRL – 32KHz Oscillators Controller

## 23.5.4 DMA

Not applicable.

# 23.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the WDT interrupt(s) requires the interrupt controller to be configured first.

## **Related Links**

Nested Vector Interrupt Controller Overview Interrupt Line Mapping

# 23.5.6 Events

Not applicable.

# 23.5.7 Debug Operation

When the CPU is halted in debug mode the WDT will halt normal operation.

# 23.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

• Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### 23.5.9 Analog Connections

Not applicable.

# 23.6 Functional Description

# 23.6.1 Principle of Operation

The Watchdog Timer (WDT) is a system for monitoring correct program operation, making it possible to recover from error situations such as runaway code, by issuing a Reset. When enabled, the WDT is a constantly running timer that is configured to a predefined time-out period. Before the end of the time-out period, the WDT should be set back, or else, a system Reset is issued.

The WDT has two modes of operation, Normal mode and Window mode. Both modes offer the option of Early Warning interrupt generation. The description for each of the basic modes is given below. The settings in the Control A register (CTRLA) and the Interrupt Enable register (handled by INTENCLR/INTENSET) determine the mode of operation:

Name:EWCTRLOffset:0x02Reset:X determined from NVM User RowProperty:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3   | 2      | 1        | 0   |

|--------|---|---|---|---|-----|--------|----------|-----|

|        |   |   |   |   |     | EWOFF: | SET[3:0] |     |

| Access |   |   |   |   | R/W | R/W    | R/W      | R/W |

| Reset  |   |   |   |   | x   | х      | х        | x   |

# Bits 3:0 – EWOFFSET[3:0]: Early Warning Interrupt Time Offset

These bits determine the number of GCLK\_WDT clock cycles between the start of the watchdog time-out period and the generation of the Early Warning interrupt. These bits are loaded from NVM User Row at start-up.

| Value     | Name     | Description        |

|-----------|----------|--------------------|

| 0x0       | CYC8     | 8 clock cycles     |

| 0x1       | CYC16    | 16 clock cycles    |

| 0x2       | CYC32    | 32 clock cycles    |

| 0x3       | CYC64    | 64 clock cycles    |

| 0x4       | CYC128   | 128 clock cycles   |

| 0x5       | CYC256   | 256 clock cycles   |

| 0x6       | CYC512   | 512 clock cycles   |

| 0x7       | CYC1024  | 1024 clock cycles  |

| 0x8       | CYC2048  | 2048 clock cycles  |

| 0x9       | CYC4096  | 4096 clock cycles  |

| 0xA       | CYC8192  | 8192 clock cycles  |

| 0xB       | CYC16384 | 16384 clock cycles |

| 0xC - 0xF | -        | Reserved           |

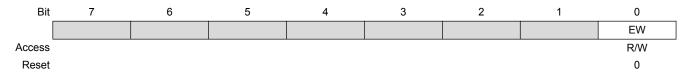

#### 23.8.4 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

Name:INTENCLROffset:0x04 [ID-0000067a]Reset:0x00Property:PAC Write-Protection

# Bit 0 – EW: Early Warning Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Early Warning Interrupt Enable bit, which disables the Early Warning interrupt.

# Bits 3:2 – FQOS[1:0]: Fetch Quality of Service

These bits define the memory priority access during the fetch operation.

| FQOS[1:0] | Name    | Description                         |

|-----------|---------|-------------------------------------|

| 0x0       | DISABLE | Background (no sensitive operation) |

| 0x1       | LOW     | Sensitive Bandwidth                 |

| 0x2       | MEDIUM  | Sensitive Latency                   |

| 0x3       | HIGH    | Critical Latency                    |

# Bits 1:0 – WRBQOS[1:0]: Write-Back Quality of Service

These bits define the memory priority access during the write-back operation.

| WRBQOS[1:0] | Name    | Description                         |

|-------------|---------|-------------------------------------|

| 0x0         | DISABLE | Background (no sensitive operation) |

| 0x1         | LOW     | Sensitive Bandwidth                 |

| 0x2         | MEDIUM  | Sensitive Latency                   |

| 0x3         | HIGH    | Critical Latency                    |

# **Related Links**

SRAM Quality of Service

# 25.8.8 Software Trigger Control

Name:SWTRIGCTRLOffset:0x10Reset:0x0000000Property:PAC Write-Protection

When static arbitration is enabled (PRICTRL0.RRLVLEN2=0) for priority level 2, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN2 written to '0').

## Bit 15 – RRLVLEN1: Level 1 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to Arbitration.

|   | /alue | Description                                                        |

|---|-------|--------------------------------------------------------------------|

| C | )     | Static arbitration scheme for channels with level 1 priority.      |

| 1 |       | Round-robin arbitration scheme for channels with level 1 priority. |

## Bits 11:8 – LVLPRI1[3:0]: Level 1 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN1=1) for priority level 1, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 1.

When static arbitration is enabled (PRICTRL0.RRLVLEN1=0) for priority level 1, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN1 written to '0').

## Bit 7 – RRLVLEN0: Level 0 Round-Robin Scheduling Enable

For details on arbitration schemes, refer to Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 0 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 0 priority. |

# Bits 3:0 – LVLPRI0[3:0]: Level 0 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN0=1) for priority level 0, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 0.

When static arbitration is enabled (PRICTRL0.RRLVLEN0=0) for priority level 0, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN0 written to '0').

## 25.8.10 Interrupt Pending

This register allows the user to identify the lowest DMA channel with pending interrupt.

Name:

INTPEND

Offset:

0x20 [ID-00001ece]

Reset:

0x0000

Property:

Name:INTENSETOffset:0x16 [ID-00000fa7]Reset:0x00Property:PAC Write-Protection

| Bit    | 7     | 6 | 5     | 4     | 3   | 2   | 1   | 0   |

|--------|-------|---|-------|-------|-----|-----|-----|-----|

|        | ERROR |   | RXBRK | CTSIC | RXS | RXC | TXC | DRE |

| Access | R/W   |   | R/W   | R/W   | R/W | R/W | R/W | R/W |

| Reset  | 0     |   | 0     | 0     | 0   | 0   | 0   | 0   |

# Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

# Bit 5 – RXBRK: Receive Break Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Receive Break Interrupt Enable bit, which enables the Receive Break interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Receive Break interrupt is disabled. |

| 1     | Receive Break interrupt is enabled.  |

# Bit 4 – CTSIC: Clear to Send Input Change Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Clear To Send Input Change Interrupt Enable bit, which enables the Clear To Send Input Change interrupt.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | Clear To Send Input Change interrupt is disabled. |

| 1     | Clear To Send Input Change interrupt is enabled.  |

#### Bit 3 – RXS: Receive Start Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Receive Start Interrupt Enable bit, which enables the Receive Start interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | Receive Start interrupt is disabled. |

| 1     | Receive Start interrupt is enabled.  |

# **Bit 2 – RXC: Receive Complete Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Receive Complete Interrupt Enable bit, which enables the Receive Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

#### 33.8.4 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name:INTENSETOffset:0x16 [ID-00001bb3]Reset:0x00Property:PAC Write-Protection

| Bit    | 7     | 6 | 5 | 4 | 3 | 2    | 1      | 0    |

|--------|-------|---|---|---|---|------|--------|------|

|        | ERROR |   |   |   |   | DRDY | AMATCH | PREC |

| Access | R/W   |   |   |   |   | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   |   |   | 0    | 0      | 0    |

## Bit 7 – ERROR: Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

#### Bit 2 – DRDY: Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Ready bit, which enables the Data Ready interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Data Ready interrupt is disabled. |

| 1     | The Data Ready interrupt is enabled.  |

# **Bit 1 – AMATCH: Address Match Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Address Match Interrupt Enable bit, which enables the Address Match interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Address Match interrupt is disabled. |

| 1     | The Address Match interrupt is enabled.  |

#### **Bit 0 – PREC: Stop Received Interrupt Enable**

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Stop Received Interrupt Enable bit, which enables the Stop Received interrupt.

To leave low power mode, CLK\_CANx\_APB and GCLK\_CANx must be active before writing CCCR.CSR to '0'. The CAN will acknowledge this by resetting CCCR.CSA = 0. Afterwards, the application can restart CAN communication by resetting bit CCCR.INIT.

# 34.6.10 Synchronization

Due to the asynchronicity between the main clock domain (CLK\_CAN\_APB) and the peripheral clock domain (GCLK\_CAN) some registers are synchronized when written. When a write-synchronized register is written, the read back value will not be updated until the register has completed synchronization.

The following bits and registers are write-synchronized:

I Initialization bit in CC Control register (CCCR.INIT)

| Bit    | 31 | 30 | 29 | 28 | 27  | 26  | 25    | 24    |

|--------|----|----|----|----|-----|-----|-------|-------|

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19  | 18  | 17    | 16    |

|        |    |    |    |    |     | TCP | [3:0] |       |

| Access |    | ļ  | 1  | Į  | R/W | R/W | R/W   | R/W   |

| Reset  |    |    |    |    | 0   | 0   | 0     | 0     |

|        |    |    |    |    |     |     |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11  | 10  | 9     | 8     |

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3   | 2   | 1     | 0     |

|        |    | -  | -  |    | -   |     | TSS   | [1:0] |

| Access |    |    |    |    |     |     | R/W   | R/W   |

|        |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     | 0     | 0     |

# Bits 19:16 – TCP[3:0]: Timestamp Counter Prescaler

| Value     | Description                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| 0x0 - 0xF | Configures the timestamp and timeout counters time unit in multiples of CAN bit times     |

|           | [116]. The actual interpretation by the hardware of this value is such that one more than |

|           | the value programmed here is used.                                                        |

#### Bits 1:0 – TSS[1:0]: Timestamp Select

This field defines the timestamp counter selection.

| Value  | Name | Description                                 |

|--------|------|---------------------------------------------|

| 0x0 or | ZERO | Timestamp counter value always 0x0000.      |

| 0x3    |      |                                             |

| 0x1    | INC  | Timestamp counter value incremented by TCP. |

| 0x2    | -    | Reserved                                    |

## 34.8.10 Timestamp Counter Value

#### Note:

- 1. A write access to TSCV while in internal mode clears the Timestamp Counter value. A write access to TSCV while in external mode has no impact.

- 2. A "wrap around" is a change of the Timestamp Counter value from non-zero to zero not caused by the write access to TSCV.

Name:

TSCV

Offset:

0x24 [ID-0000a4bb]

Reset:

0x0000000

Property:

Read-only

Name:

TXBAR

Offset:

0xD0 [ID-0000a4bb]

Reset:

0x00000000

Property:

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | ARn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | ARn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | ARn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | ARn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

# Bits 31:0 – ARn: Add Request

Each Tx Buffer has its own Add Request bit.

Writing a '1' will set the corresponding Add Request bit; writing a '0' has no impact. This enables the Host to set transmission requests for multiple Tx Buffers with one write to TXBAR. TXBAR bits are set only for those Tx Buffers configured via TXBC. When no Tx scan is running, the bits are reset immediately, else the bits remain set until the Tx scan process has completed.

# 34.8.40 Tx Buffer Cancellation Request

Name:

TXBCR

Offset:

0xD4 [ID-0000a4bb]

Reset:

0x0000000

Property:

| Value | Name    | Description     |

|-------|---------|-----------------|

| 0x0   | DEFAULT | Default capture |

| 0x1   | CAPTMIN | Minimum capture |

| 0x2   | CAPTMAX | Maximum capture |

| 0x3   |         | Reserved        |

## Bits 20, 21 – COPENx: Capture On Pin x Enable

Bit x of COPEN[1:0] selects the trigger source for capture operation, either events or I/O pin input.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

# Bits 16, 17 – CAPTENx: Capture Channel x Enable

Bit x of CAPTEN[1:0] selects whether channel x is a capture or a compare channel.

These bits are not synchronized.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | CAPTEN disables capture on channel x. |

| 1     | CAPTEN enables capture on channel x.  |

#### Bit 11 – ALOCK: Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | The LUPD bit is not affected on overflow/underflow, and re-trigger event. |

| 1     | The LUPD bit is set on each overflow/underflow or re-trigger event.       |

#### Bits 10:8 – PRESCALER[2:0]: Prescaler

These bits select the counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

# Bit 7 – ONDEMAND: Clock On Demand

This bit selects the clock requirements when the TC is stopped.

In standby mode, if the Run in Standby bit (CTRLA.RUNSTDBY) is '0', ONDEMAND is forced to '0'.

This bit is not synchronized.

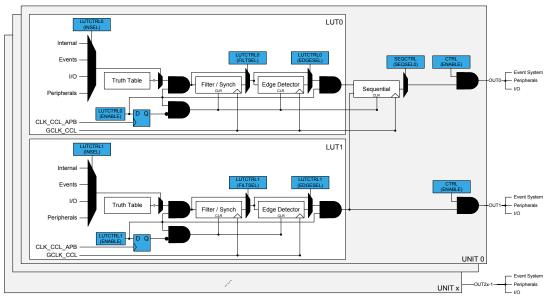

# 37.3 Block Diagram

Figure 37-1. Configurable Custom Logic

# 37.4 Signal Description

| Pin Name   | Туре           | Description              |

|------------|----------------|--------------------------|

| OUT[n:0]   | Digital output | Output from lookup table |

| IN[3n+2:0] | Digital input  | Input to lookup table    |

1. n is the number of CCL groups.

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

# **Related Links**

I/O Multiplexing and Considerations

# 37.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 37.5.1 I/O Lines

Using the CCL I/O lines requires the I/O pins to be configured. Refer to *PORT - I/O Pin Configuration* for details.

#### **Related Links**

PORT: IO Pin Controller

# 37.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

Writing a one to an Event Output bit in the Event Control Register (EVCTRL.xxEO) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the Event System chapter for details on configuring the event system.

The SDADC can take the following actions on an input event:

- Start conversion (START): Start a conversion. Refer to SWTRIG for details.

- Conversion flush (FLUSH): Flush the conversion. Refer to SWTRIG for details.

Writing a one to an Event Input bit into the Event Control register (EVCTRL.xxEI) enables the corresponding action on input event. Writing a zero to this bit disables the corresponding action on input event.

The SDADC uses only asynchronous events and asynchronous Event System channel path must be configured. By default, the SDADC will detect a rising edge on the incoming event. If the SDADC action must be performed on the falling edge of the incoming event, the event line must be inverted first, by writing to one the corresponding Event Invert Enable bit in Event Control register (EVCTRL.xINV).

Note that If FLUSH and START events are available at the same time, the FLUSH event has higher priority.

#### **Related Links**

#### EVSYS – Event System

#### 39.6.7 Sleep Mode Operation

The ONDEMAND and RUNSTDBY bits in the Control A register (CTRLA) control the behavior of the SDADC during standby sleep mode, in cases where the SDADC is enabled (CTRLA.ENABLE = 1). Note that when CTRLA.ONDEMAND is one, the analog

block is powered-off when the conversion is complete. When a start request is detected, the system returns from sleep and starts a new conversion after the start-up time delay.

| CTRLA.RUNSTDBY | CTRLA.ONDEMAND | CTRLA.ENABLE | Description                                        |

|----------------|----------------|--------------|----------------------------------------------------|

| x              | х              | 0            | Disabled                                           |

| 0              | 0              | 1            | Run in all sleep modes except STANDBY.             |

| 0              | 1              | 1            | Run in all sleep modes on request, except STANDBY. |

| 1              | 0              | 1            | Run in all sleep modes.                            |

| 1              | 1              | 1            | Run in all sleep modes on request.                 |

#### 39.6.8 Synchronization

Due to the asynchronicity between CLK\_SDADC\_APB and CLK\_GEN\_SDADC some registers must be synchronized when accessed. A register can require:

- Synchronization when written

- Synchronization when read

- Synchronization when written and read

- No synchronization

When executing an operation that requires synchronization, the corresponding synchronization bit is set in Synchronization Busy register (SYNCBUSY) and cleared when synchronization is complete.

If an operation that require synchronization is executed while its busy bit is on, the operation is discarded and a bus error is generated.

The following bits need synchronization when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

Write-synchronization is denoted by the Write-Synchronized property in the register description.

The following registers need synchronization when written:

- Input Control register (INPUTCTRL)

- Reference Control register (REFCTRL)

- Control C register (CTRLC)

- Window Monitor Lower Threshold register (WINLT)

- Window Monitor Upper Threshold register (WINUT)

- Offset correction register (OFFSETCORR)

- Gain correction register (GAINCORR)

- Shift correction register (SHIFTCORR)

- Software Trigger register (SWTRIG)

- Analog Control Register (ANACTRL)

Write-synchronization is denoted by the Write-Synchronized property in the register description.

| Value   | Name | Description                      |

|---------|------|----------------------------------|

| 0x0     | OFF  | No filtering                     |

| 0x1     | MAJ3 | 3-bit majority function (2 of 3) |

| 0x2     | MAJ5 | 5-bit majority function (3 of 5) |

| 0x3-0x7 | N/A  | Reserved                         |

## Bit 19 – HYSTEN: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn.SINGLE=0).

This bit is not synchronized.

| Value | Description             |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

## Bits 17:16 – SPEED[1:0]: Speed Selection

This bit indicates the speed/propagation delay mode of comparator n. COMPCTRLn.SPEED can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | LOW  | Low speed   |

| 0x3   | HIGH | High speed  |

#### Bit 15 – SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

#### Bits 14:12 – MUXPOS[2:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value   | Name   | Description |

|---------|--------|-------------|

| 0x0     | PIN0   | I/O pin 0   |

| 0x1     | PIN1   | I/O pin 1   |

| 0x2     | PIN2   | I/O pin 2   |

| 0x3     | PIN3   | I/O pin 3   |

| 0x4     | VSCALE | VDD scaler  |

| 0x5–0x7 |        | Reserved    |

## 41.5.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear (INTFLAG) register

- Data Buffer (DATABUF) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger

#### **Related Links**

PAC - Peripheral Access Controller

# 41.5.9 Analog Connections

The DAC has one output pin (VOUT) and one analog input pin (VREFA) that must be configured first.

When internal input is used, it must be enabled before DAC Controller is enabled.

# 41.6 Functional Description

#### 41.6.1 Principle of Operation

The DAC converts the digital value located in the Data register (DATA) into an analog voltage on the DAC output (VOUT).

A conversion is started when new data is written to the Data register. The resulting voltage is available on the DAC output after the conversion time. A conversion can also be started by input events from the Event System.

#### 41.6.2 Basic Operation

#### 41.6.2.1 Initialization

The following registers are enable-protected, meaning they can only be written when the DAC is disabled (CTRLA.ENABLE is zero):

- Control B register (CTRLB)

- Event Control register (EVCTRL)

Enable-protection is denoted by the Enable-Protected property in the register description.

Before enabling the DAC, it must be configured by selecting the voltage reference using the Reference Selection bits in the Control B register (CTRLB.REFSEL).

#### 41.6.2.2 Enabling, Disabling and Resetting

The DAC Controller is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The DAC Controller is disabled by writing a '0' to CTRLA.ENABLE.

The DAC Controller is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the DAC will be reset to their initial state, and the DAC Controller will be disabled. Refer to the CTRLA register for details.

#### 41.6.2.3 Enabling the Output Buffer

To enable the DAC output on the  $V_{OUT}$  pin, the output driver must be enabled by writing a one to the External Output Enable bit in the Control B register (CTRLB.EOEN).

| Symbol | Parameters                         | Conditions (2) | Min    | Тур   | Max   | Unit |

|--------|------------------------------------|----------------|--------|-------|-------|------|

|        |                                    | Int Ref = 5.5V | 83     | 95.6  | 97    |      |

| SINAD  | Signal to Noise + Distortion Ratio | Ext ref = 1.2V | 71.1   | 90.7  | 91.7  | dB   |

|        |                                    | Int Ref = 5.5V | 77.1   | 78.6  | 83.2  |      |

| THD    | Total Harmonic Distortion          | Ext ref = 1.2V | -102.3 | -94.6 | -75.3 | dB   |

|        |                                    | Int Ref = 5.5V | -99.9  | -94.7 | -85.4 |      |

- 1. Values based on characterization.

- 2. OSR=256, Chopper OFF, Sampling Clock Speed at 6MHz.

# 47.4.5 Digital to Analog Converter (DAC) Characteristics

# Table 47-12. Operating Conditions<sup>(1)</sup>

| Symbol | Parameters                   | Conditions     | Min  | Тур       | Мах           | Unit |

|--------|------------------------------|----------------|------|-----------|---------------|------|

| RES    | Input resolution             |                | -    | -         | 10            | Bits |

| VDDANA | Analog supply voltage        |                | 2.7  | -         | 5.5           | V    |

| AVREF  | External reference voltage   |                | 1    | -         | VDDANA - 0.6  | V    |

|        | Internal reference voltage 1 | VREF.SEL = 0x0 | -    | 1.024     | -             | V    |

|        |                              | VREF.SEL = 0x2 | -    | 2.048     | -             |      |

|        |                              | VREF.SEL = 0x3 | -    | 4.096 (2) | -             | -    |

|        | Internal reference voltage 2 |                | -    | VDDANA    | -             | V    |

|        | Linear output voltage range  |                | 0.05 | -         | VDDANA - 0.05 | V    |

|        | Minimum resistive load       |                | 5    | -         | -             | kΩ   |

|        | Maximum capacitance load     |                | -    | -         | 100           | pF   |

1. These are based on simulation. These values are not covered by test or characterization.

2. For VDDANA > 4.5V.

# Table 47-13. Clock and Timing<sup>(1)</sup>

| Symbol | Parameter    | Conditions  | Max.         | Units |    |

|--------|--------------|-------------|--------------|-------|----|

|        |              | Normal mode | 350          | ksps  |    |

|        |              | Rload > 5kΩ | For DDATA=±1 | 1000  |    |

|        | Startup time |             |              | 3     | μs |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

# Table 47-14. Accuracy Characteristics<sup>(1)</sup>

| Symbol | Parameter              | Conditions           | Conditions                |        |        | Units |

|--------|------------------------|----------------------|---------------------------|--------|--------|-------|

| INL    | Integral non-linearity | VREF= Ext 2.0V       | VREF= Ext 2.0V VDD = 2.7V |        | +/-2.4 | LSB   |

|        |                        |                      | VDD = 5.5V                | +/-0.5 | +/-1.6 |       |

|        |                        | VREF = VDDANA        | VDD = 2.7V                | +/-0.6 | +/-2.0 |       |

|        |                        | VDD = 5.5V           | +/-0.4                    | +/-1.6 |        |       |

|        |                        | VREF= 1.024V INT REF | VDD = 2.7V                | +/-1.0 | +/-2.5 |       |