#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e15a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Writing a one to this bit will clear the corresponding INTFLAGC interrupt flag.

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAGC<br>0x1C [ID-00000<br>0x000000<br> | )a18]   |         |         |         |         |       |

|--------|-----------------------------------------|--------------------------------------------|---------|---------|---------|---------|---------|-------|

| Bit    | 31                                      | 30                                         | 29      | 28      | 27      | 26      | 25      | 24    |

|        |                                         |                                            |         |         |         |         |         |       |

| Access |                                         |                                            | ·       |         |         |         |         |       |

| Reset  |                                         |                                            |         |         |         |         |         |       |

| Bit    | 23                                      | 22                                         | 21      | 20      | 19      | 18      | 17      | 16    |

|        | CCL                                     | PTC                                        | DAC     | AC      | SDADC   | ADC1    | ADC0    | TC4   |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       | 0     |

|        |                                         |                                            |         |         |         |         |         |       |

| Bit    | 15                                      | 14                                         | 13      | 12      | 11      | 10      | 9       | 8     |

|        | TC3                                     | TC2                                        | TC1     | TC0     | TCC2    | TCC1    | TCC0    |       |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     |       |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       |       |

|        |                                         |                                            |         |         |         |         |         |       |

| Bit    | 7                                       | 6                                          | 5       | 4       | 3       | 2       | 1       | 0     |

|        | CAN0                                    | SERCOM5                                    | SERCOM4 | SERCOM3 | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS |

| Access | R/W                                     | R/W                                        | R/W     | R/W     | R/W     | R/W     | R/W     | R/W   |

| Reset  | 0                                       | 0                                          | 0       | 0       | 0       | 0       | 0       | 0     |

#### Bit 23 – CCL: Interrupt Flag for CCL

Bit 22 – PTC: Interrupt Flag for PTC

- Bit 21 DAC: Interrupt Flag for DAC

- Bit 20 AC: Interrupt Flag for AC

- Bit 19 SDADC: Interrupt Flag for SDADC

- Bits 17, 18 ADC: Interrupt Flag for ADCn [n=1..0]

- Bits 12, 13, 14, 15, 16 TC: Interrupt Flag for TCn [n = 4..0]

- Bits 9, 10, 11 TCC: Interrupt Flag for TCCn [n = 2..0]

- Bit 7 CAN: Interrupt Flag for CAN

- Bits 1, 2, 3, 4, 5, 6 SERCOM: Interrupt Flag for SERCOMn [n = 5..0]

- Bit 0 EVSYS: Interrupt Flag for EVSYS

- 11.7.9 Peripheral Interrupt Flag Status and Clear D

ADDR.AMOD=0: exit-on-error (default)

In this mode, the algorithm terminates either when a fault is detected or on successful completion. In both cases, STATUSA.DONE is set. If an error was detected, STATUSA.FAIL will be set. User then can read the DATA and ADDR registers to locate the fault.

- ADDR.AMOD=1: pause-on-error

In this mode, the MBIST algorithm is paused when an error is detected. In such a situation, only STATUSA.FAIL is asserted. The state machine waits for user to clear STATUSA.FAIL by writing a '1' in STATUSA.FAIL to resume. Prior to resuming, user can read the DATA and ADDR registers to locate the fault.

- 4. Locating Faults

If the test stops with STATUSA.FAIL set, one or more bits failed the test. The test stops at the first detected error. The position of the failing bit can be found by reading the following registers:

- ADDR: Address of the word containing the failing bit

- DATA: contains data to identify which bit failed, and during which phase of the test it failed.

The DATA register will in this case contains the following bit groups:

Bit Bit Bit phase Bit bit index

#### Figure 13-6. DATA bits Description When MBIST Operation Returns an Error

• bit\_index: contains the bit number of the failing bit

• phase: indicates which phase of the test failed and the cause of the error, as listed in the following table.

| Phase | Test actions                                    |

|-------|-------------------------------------------------|

| 0     | Write all bits to zero. This phase cannot fail. |

| 1     | Read '0', write '1', increment address          |

| 2     | Read '1', write '0'                             |

| 3     | Read '0', write '1', decrement address          |

| 4     | Read '1', write '0', decrement address          |

| 5     | Read '0', write '1'                             |

| 6     | Read '1', write '0', decrement address          |

| 7     | Read all zeros. bit_index is not used           |

#### Table 13-4. MBIST Operation Phases

| Bit    | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|------------|---|---|---|---|---|---|---|

|        | CLEAR[7:0] |   |   |   |   |   |   |   |

| Access | W          | W | W | W | W | W | W | W |

| Reset  | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Bits 7:0 – CLEAR[7:0]: Watchdog Clear

In Normal mode, writing 0xA5 to this register during the watchdog time-out period will clear the Watchdog Timer and the watchdog time-out period is restarted.

In Window mode, any writing attempt to this register before the time-out period started (i.e., during  $TO_{WDTW}$ ) will issue an immediate system Reset. Writing 0xA5 during the time-out period  $TO_{WDT}$  will clear the Watchdog Timer and the complete time-out sequence (first  $TO_{WDTW}$  then  $TO_{WDT}$ ) is restarted.

In both modes, writing any other value than 0xA5 will issue an immediate system Reset.

If CRC calculation is needed, the CRC engine must be configured before it is enabled, as outlined by the following steps:

- The CRC input source must selected by writing the CRC Input Source bit group in the CRC Control register (CRCCTRL.CRCSRC)

- The type of CRC calculation must be selected by writing the CRC Polynomial Type bit group in the CRC Control register (CRCCTRL.CRCPOLY)

- If I/O is selected as input source, the beat size must be selected by writing the CRC Beat Size bit group in the CRC Control register (CRCCTRL.CRCBEATSIZE)

#### **Related Links**

BASEADDR CHCTRLA CHCTRLB CRCCHKSUM CRCCTRL CTRL WRBADDR BTCTRL BTCNT DSTADDR SRCADDR

#### 25.6.2.2 Enabling, Disabling, and Resetting

The DMAC is enabled by writing the DMA Enable bit in the Control register (CTRL.DMAENABLE) to '1'. The DMAC is disabled by writing a '0' to CTRL.DMAENABLE.

A DMA channel is enabled by writing the Enable bit in the Channel Control A register (CHCTRLA.ENABLE) to '1', after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). A DMA channel is disabled by writing a '0' to CHCTRLA.ENABLE.

The CRC is enabled by writing a '1' to the CRC Enable bit in the Control register (CTRL.CRCENABLE). The CRC is disabled by writing a '0' to CTRL.CRCENABLE.

The DMAC is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST) while the DMAC and CRC are disabled. All registers in the DMAC except DBGCTRL will be reset to their initial state.

A DMA channel is reset by writing a '1' to the Software Reset bit in the Channel Control A register (CHCTRLA.SWRST), after writing the corresponding channel id to the Channel ID bit group in the Channel ID register (CHID.ID). The channel registers will be reset to their initial state. The corresponding DMA channel must be disabled in order for the reset to take effect.

#### 25.6.2.3 Transfer Descriptors

Together with the channel configurations the transfer descriptors decides how a block transfer should be executed. Before a DMA channel is enabled (CHCTRLA.ENABLE is written to one), and receives a transfer trigger, its first transfer descriptor has to be initialized and valid (BTCTRL.VALID). The first transfer descriptor describes the first block transfer of a transaction.

All transfer descriptors must reside in SRAM. The addresses stored in the Descriptor Memory Section Base Address (BASEADDR) and Write-Back Memory Section Base Address (WRBADDR) registers tell the DMAC where to find the descriptor memory section and the write-back memory section.

| Offset | Name       | Bit Pos. |                  |                     |             |        |           |   |             |        |  |

|--------|------------|----------|------------------|---------------------|-------------|--------|-----------|---|-------------|--------|--|

| 0x2C   |            |          |                  |                     |             |        |           |   |             |        |  |

|        | Reserved   |          |                  |                     |             |        |           |   |             |        |  |

| 0x2F   |            |          |                  |                     |             |        |           |   |             |        |  |

| 0x30   |            | 7:0      |                  |                     | 1           | DEBOUN | ICEN[7:0] | 1 |             |        |  |

| 0x31   | DEBOUINCEN | 15:8     |                  |                     |             | DEBOUN | CEN[15:8] |   |             |        |  |

| 0x32   | DEBOUNCEN  | 23:16    |                  | DEBOUNCEN[23:16]    |             |        |           |   |             |        |  |

| 0x33   |            | 31:24    | DEBOUNCEN[31:24] |                     |             |        |           |   |             |        |  |

| 0x34   |            | 7:0      | STATESx          | P                   | RESCALERx[2 | :0]    | STATESx   | P | RESCALERx[2 | :0]    |  |

| 0x35   |            | 15:8     | STATESx          | ESx PRESCALERx[2:0] |             |        | STATESx   | Р | RESCALERx[2 | :0]    |  |

| 0x36   | DPRESCALER | 23:16    |                  |                     |             |        |           |   |             | TICKON |  |

| 0x37   |            | 31:24    |                  |                     |             |        |           |   |             |        |  |

| 0x38   |            | 7:0      | PINSTATE[7:0]    |                     |             |        |           |   |             | 1      |  |

| 0x39   | - PINSTATE | 15:8     |                  |                     |             | PINSTA | TE[15:8]  |   |             |        |  |

| 0x3A   |            | 23:16    |                  |                     |             | PINSTA | FE[23:16] |   |             |        |  |

| 0x3B   |            | 31:24    |                  |                     |             | PINSTA | [E[31:24] |   |             |        |  |

### 26.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 26.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4     | 3 | 2 | 1      | 0     |

|--------|---|---|---|-------|---|---|--------|-------|

|        |   |   |   | CKSEL |   |   | ENABLE | SWRST |

| Access |   |   |   | RW    |   |   | RW     | W     |

| Reset  |   |   |   | 0     |   |   | 0      | 0     |

#### Bit 4 – CKSEL: Clock Selection

The EIC can be clocked either by GCLK\_EIC (when a frequency higher than 32KHz is required for filtering) or by CLK\_ULP32K (when power consumption is the priority).

This bit is not Write-Synchronized.

| Bit    | 31            | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |  |

|--------|---------------|-----|-----|-------|----------|-----|-----|-----|--|--|

| ſ      | EXTINT[31:24] |     |     |       |          |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 23            | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |  |

|        |               |     |     | EXTIN | F[23:16] |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 15            | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |  |

| Γ      |               |     |     | EXTIN | T[15:8]  |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

|        |               |     |     |       |          |     |     |     |  |  |

| Bit    | 7             | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |  |

| Γ      |               |     |     | EXTIN | IT[7:0]  |     |     |     |  |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |  |

#### Bits 31:0 – EXTINT[31:0]: External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

Writing a '1' to bit x will set the External Interrupt Enable bit x, which enables the external interrupt EXTINTx.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

#### 26.8.8 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x14Reset:0x0000000Property: -

#### 28.6.2.2 Operation

Each I/O pin y can be controlled by the registers in PORT. Each PORT group has its own set of PORT registers, the base address of the register set for pin y is at byte address PORT + ([y] \* 0x4). The index within that register set is [y].

Refer to I/O Multiplexing and Considerations for details on available pin configuration and PORT groups.

#### **Configuring Pins as Output**

To use pin number y as an *output*, write bit y of the DIR register to '1'. This can also be done by writing bit y in the DIRSET register to '1' - this will avoid disturbing the configuration of other pins in that group. The y bit in the OUT register must be written to the desired output value.

Similarly, writing an OUTSET bit to '1' will set the corresponding bit in the OUT register to '1'. Writing a bit in OUTCLR to '1' will set that bit in OUT to zero. Writing a bit in OUTTGL to '1' will toggle that bit in OUT.

#### **Configuring Pins as Input**

To use pin y as an *input*, bit y in the DIR register must be written to '0'. This can also be done by writing bit y in the DIRCLR register to '1' - this will avoid disturbing the configuration of other pins in that group. The input value can be read from bit y in register IN as soon as the INEN bit in the Pin Configuration register (PINCFGy.INEN) is written to '1'.

By default, the input synchronizer is clocked only when an input read is requested. This will delay the read operation by two CLK\_PORT cycles. To remove the delay, the input synchronizers for each PORT group of eight pins can be configured to be always active, but this will increase power consumption. This is enabled by writing '1' to the corresponding SAMPLINGn bit field of the CTRL register, see CTRL.SAMPLING for details.

#### **Using Alternative Peripheral Functions**

To use pin y as one of the available peripheral functions, the corresponding PMUXEN bit of the PINCFGy register must be '1'. The PINCFGy register for pin y is at byte offset (PINCFG0 + [y]).

The peripheral function can be selected by setting the PMUXO or PMUXE in the PMUXn register. The PMUXO/PMUXE is at byte offset PMUX0 + (y/2). The chosen peripheral must also be configured and enabled.

#### **Related Links**

I/O Multiplexing and Considerations

#### 28.6.3 I/O Pin Configuration

The Pin Configuration register (PINCFGy) is used for additional I/O pin configuration. A pin can be set in a totem-pole or pull configuration.

As pull configuration is done through the Pin Configuration register, all intermediate PORT states during switching of pin direction and pin values are avoided.

The I/O pin configurations are described further in this chapter, and summarized in Table 28-2.

#### 28.6.3.1 Pin Configurations Summary

#### Table 28-2. Pin Configurations Summary

| D | DIR | INEN | PULLEN | OUT | Configuration                             |

|---|-----|------|--------|-----|-------------------------------------------|

| 0 |     | 0    | 0      | Х   | Reset or analog I/O: all digital disabled |

| 0 |     | 0    | 1      | 0   | Pull-down; input disabled                 |

# SAM C20/C21

| Bit    | 31       | 30       | 29  | 28   | 27     | 26      | 25   | 24     |

|--------|----------|----------|-----|------|--------|---------|------|--------|

|        |          |          |     |      |        |         |      |        |

| Access |          |          |     |      |        |         |      |        |

| Reset  |          |          |     |      |        |         |      |        |

|        |          |          |     |      |        |         |      |        |

| Bit    | 23       | 22       | 21  | 20   | 19     | 18      | 17   | 16     |

|        |          |          |     |      |        |         |      |        |

| Access |          | •        | •   |      |        |         |      |        |

| Reset  |          |          |     |      |        |         |      |        |

|        |          |          |     |      |        |         |      |        |

| Bit    | 15       | 14       | 13  | 12   | 11     | 10      | 9    | 8      |

|        | ONDEMAND | RUNSTDBY |     |      | EDGS   | EL[1:0] | PATH | I[1:0] |

| Access | R/W      | R/W      |     |      | R/W    | R/W     | R/W  | R/W    |

| Reset  | 0        | 0        |     |      | 0      | 0       | 0    | 0      |

|        |          |          |     |      |        |         |      |        |

| Bit    | 7        | 6        | 5   | 4    | 3      | 2       | 1    | 0      |

|        |          |          |     | EVGE | N[7:0] |         |      |        |

| Access | R/W      | R/W      | R/W | R/W  | R/W    | R/W     | R/W  | R/W    |

| Reset  | 0        | 0        | 0   | 0    | 0      | 0       | 0    | 0      |

#### Bit 15 – ONDEMAND: Generic Clock On Demand

| Value | Description                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock source is enabled. |

| 1     | Generic clock is requested on demand while an event is handled                                              |

#### Bit 14 – RUNSTDBY: Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                                       |

| 1     | The channel is not stopped in standby sleep mode and depends on the CHANNEL.ONDEMAND |

#### Bits 11:10 – EDGSEL[1:0]: Edge Detection Selection

These bits set the type of edge detection to be used on the channel.

These bits must be written to zero when using the asynchronous path.

| Value | Name          | Description                                                                        |

|-------|---------------|------------------------------------------------------------------------------------|

| 0x0   | NO_EVT_OUTPUT | No event output when using the resynchronized or synchronous path                  |

| 0x1   | RISING_EDGE   | Event detection only on the rising edge of the signal from the event generator     |

| 0x2   | FALLING_EDGE  | Event detection only on the falling edge of the signal from the event generator    |

| 0x3   | BOTH_EDGES    | Event detection on rising and falling edges of the signal from the event generator |

#### Bits 9:8 – PATH[1:0]: Path Selection

These bits are used to choose which path will be used by the selected channel.

The path choice can be limited by the channel source, see the table in USERm.

## 32.7 Register Summary

| Offset | Name     | Bit Pos. |          |         |       |        |           |        |             |           |

|--------|----------|----------|----------|---------|-------|--------|-----------|--------|-------------|-----------|

| 0x00   |          | 7:0      | RUNSTDBY |         |       |        | MODE[2:0] |        | ENABLE      | SWRST     |

| 0x01   |          | 15:8     |          |         |       |        |           |        |             | IBON      |

| 0x02   | CTRLA    | 23:16    |          |         | DIPC  | D[1:0] |           |        | DOPO        | D[1:0]    |

| 0x03   |          | 31:24    |          | DORD    | CPOL  | CPHA   |           | FOR    | V[3:0]      |           |

| 0x04   |          | 7:0      |          | PLOADEN |       |        |           |        | CHSIZE[2:0] |           |

| 0x05   | CTRLB    | 15:8     | AMOD     | E[1:0]  | MSSEN |        |           |        | SSDE        |           |

| 0x06   | CIRLB    | 23:16    |          |         |       |        |           |        | RXEN        |           |

| 0x07   |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x08   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x0B   |          |          |          |         |       |        |           |        |             |           |

| 0x0C   | BAUD     | 7:0      |          |         |       | BAU    | D[7:0]    |        |             |           |

| 0x0D   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x13   |          |          |          |         |       |        | -         |        |             |           |

| 0x14   | INTENCLR | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x15   | Reserved |          |          |         |       |        | -         |        |             |           |

| 0x16   | INTENSET | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x17   | Reserved |          |          |         |       |        |           |        |             |           |

| 0x18   | INTFLAG  | 7:0      | ERROR    |         |       |        | SSL       | RXC    | TXC         | DRE       |

| 0x19   | Reserved |          |          |         |       |        |           |        |             |           |

| 0x1A   | STATUS   | 7:0      |          |         |       |        |           | BUFOVF |             |           |

| 0x1B   |          | 15:8     |          |         |       |        |           |        |             |           |

| 0x1C   |          | 7:0      |          |         |       |        |           | CTRLB  | ENABLE      | SWRST     |

| 0x1D   | SYNCBUSY | 15:8     |          |         |       |        |           |        |             |           |

| 0x1E   |          | 23:16    |          |         |       |        |           |        |             |           |

| 0x1F   |          | 31:24    |          |         |       |        |           |        |             |           |

| 0x20   |          |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x23   |          |          |          |         |       |        |           |        |             |           |

| 0x24   |          | 7:0      |          |         |       | ADD    | R[7:0]    |        |             |           |

| 0x25   | ADDR     | 15:8     |          |         |       |        |           |        |             |           |

| 0x26   |          | 23:16    |          |         |       | ADDRM  | IASK[7:0] |        |             |           |

| 0x27   |          | 31:24    |          |         |       | _      |           |        |             |           |

| 0x28   | DATA     | 7:0      |          |         |       | DAT    | A[7:0]    |        |             |           |

| 0x29   |          | 15:8     |          |         |       |        |           |        |             | DATA[8:8] |

| 0x2A   | _        |          |          |         |       |        |           |        |             |           |

|        | Reserved |          |          |         |       |        |           |        |             |           |

| 0x2F   | DROOTRI  | 7.0      |          |         |       |        |           |        |             | DROCTOR   |

| 0x30   | DBGCTRL  | 7:0      |          |         |       |        |           |        |             | DBGSTOP   |

# SAM C20/C21

| Bit    | 15  | 14  | 13  | 12  | 11     | 10  | 9   | 8         |

|--------|-----|-----|-----|-----|--------|-----|-----|-----------|

|        |     |     |     |     |        |     |     | DATA[8:8] |

| Access |     |     |     |     |        |     |     | R/W       |

| Reset  |     |     |     |     |        |     |     | 0         |

|        |     |     |     |     |        |     |     |           |

| Bit    | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0         |

|        |     |     |     | DAT | A[7:0] |     |     |           |

| Access | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W       |

| Reset  | 0   | 0   | 0   | 0   | 0      | 0   | 0   | 0         |

#### Bits 8:0 - DATA[8:0]: Data

Reading these bits will return the contents of the receive data buffer. The register should be read only when the Receive Complete Interrupt Flag bit in the Interrupt Flag Status and Clear register (INTFLAG.RXC) is set.

Writing these bits will write the transmit data buffer. This register should be written only when the Data Register Empty Interrupt Flag bit in the Interrupt Flag Status and Clear register (INTFLAG.DRE) is set.

#### 32.8.11 Debug Control

Name:DBGCTRLOffset:0x30 [ID-00000e74]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|--------|---|---|---|---|---|---|---|---------|

|        |   |   |   |   |   |   |   | DBGSTOP |

| Access |   |   |   |   |   |   |   | R/W     |

| Reset  |   |   |   |   |   |   |   | 0       |

#### Bit 0 – DBGSTOP: Debug Stop Mode

This bit controls the functionality when the CPU is halted by an external debugger.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The baud-rate generator continues normal operation when the CPU is halted by an external |

|       | debugger.                                                                                |

| 1     | The baud-rate generator is halted when the CPU is halted by an external debugger.        |

#### 33.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

PM - Power Manager

#### 33.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Main Clock Controller. Refer to *Peripheral Clock Masking* for details and default status of this clock.

Two generic clocks are used by SERCOM, GCLK\_SERCOMx\_CORE and GCLK\_SERCOM\_SLOW. The core clock (GCLK\_SERCOMx\_CORE) can clock the I<sup>2</sup>C when working as a master. The slow clock (GCLK\_SERCOM\_SLOW) is required only for certain functions, e.g. SMBus timing. These two clocks must be configured and enabled in the Generic Clock Controller (GCLK) before using the I<sup>2</sup>C.

These generic clocks are asynchronous to the bus clock (CLK\_SERCOMx\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

GCLK - Generic Clock Controller Peripheral Clock Masking PM – Power Manager

#### 33.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

DMAC - Direct Memory Access Controller

#### 33.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 33.5.6 Events

Not applicable.

#### 33.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### 33.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28 | 27  | 26  | 25    | 24    |

|--------|----|----|----|----|-----|-----|-------|-------|

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 23 | 22 | 21 | 20 | 19  | 18  | 17    | 16    |

|        |    |    |    |    |     | TCP | [3:0] |       |

| Access |    | ļ  | 1  | Į  | R/W | R/W | R/W   | R/W   |

| Reset  |    |    |    |    | 0   | 0   | 0     | 0     |

|        |    |    |    |    |     |     |       |       |

| Bit    | 15 | 14 | 13 | 12 | 11  | 10  | 9     | 8     |

|        |    |    |    |    |     |     |       |       |

| Access |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     |       |       |

|        |    |    |    |    |     |     |       |       |

| Bit    | 7  | 6  | 5  | 4  | 3   | 2   | 1     | 0     |

|        |    | -  | -  |    | -   |     | TSS   | [1:0] |

| Access |    |    |    |    |     |     | R/W   | R/W   |

|        |    |    |    |    |     |     |       |       |

| Reset  |    |    |    |    |     |     | 0     | 0     |

#### Bits 19:16 – TCP[3:0]: Timestamp Counter Prescaler

| Value     | Description                                                                               |

|-----------|-------------------------------------------------------------------------------------------|

| 0x0 - 0xF | Configures the timestamp and timeout counters time unit in multiples of CAN bit times     |

|           | [116]. The actual interpretation by the hardware of this value is such that one more than |

|           | the value programmed here is used.                                                        |

#### Bits 1:0 – TSS[1:0]: Timestamp Select

This field defines the timestamp counter selection.

| Value  | Name | Description                                 |

|--------|------|---------------------------------------------|

| 0x0 or | ZERO | Timestamp counter value always 0x0000.      |

| 0x3    |      |                                             |

| 0x1    | INC  | Timestamp counter value incremented by TCP. |

| 0x2    | -    | Reserved                                    |

#### 34.8.10 Timestamp Counter Value

#### Note:

- 1. A write access to TSCV while in internal mode clears the Timestamp Counter value. A write access to TSCV while in external mode has no impact.

- 2. A "wrap around" is a change of the Timestamp Counter value from non-zero to zero not caused by the write access to TSCV.

Name:

TSCV

Offset:

0x24 [ID-0000a4bb]

Reset:

0x0000000

Property:

Read-only

#### Bit 8 – OVFEO: Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

#### Bit 5 – TCEI: TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

#### Bit 4 – TCINV: TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Input event source is not inverted. |

| 1     | Input event source is inverted.     |

#### Bits 2:0 – EVACT[2:0]: Event Action

These bits define the event action the TC will perform on an event.

| Value | Name      | Description                                |

|-------|-----------|--------------------------------------------|

| 0x0   | OFF       | Event action disabled                      |

| 0x1   | RETRIGGER | Start, restart or retrigger TC on event    |

| 0x2   | COUNT     | Count on event                             |

| 0x3   | START     | Start TC on event                          |

| 0x4   | STAMP     | Time stamp capture                         |

| 0x5   | PPW       | Period captured in CC0, pulse width in CC1 |

| 0x6   | PWP       | Period captured in CC1, pulse width in CC0 |

| 0x7   | PW        | Pulse width capture                        |

#### 35.7.2.5 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

# SAM C20/C21

| Offset | Name     | Bit Pos. |              |              |      |         |           |          |              |          |  |

|--------|----------|----------|--------------|--------------|------|---------|-----------|----------|--------------|----------|--|

| 0x65   |          | 15:8     |              |              |      | PGV     | B0[7:0]   |          |              |          |  |

| 0x66   |          |          |              |              |      |         |           |          |              |          |  |

|        | Reserved |          |              |              |      |         |           |          |              |          |  |

| 0x67   |          |          |              |              |      |         |           |          |              |          |  |

| 0x68   |          | 7:0      | CIPERENB     |              | RAMF | PB[1:0] |           | ٧        | VAVEGENB[2:0 | )]       |  |

| 0x69   |          | 15:8     |              |              |      |         | CICCENB3  | CICCENB2 | CICCENB1     | CICCENB0 |  |

| 0x6A   | WAVEBUF  | 23:16    |              |              |      |         | POLB3     | POLB2    | POLB1        | POLB0    |  |

| 0x6B   |          | 31:24    |              |              |      |         | SWAPB 3   | SWAPB 2  | SWAPB 1      | SWAPB 0  |  |

| 0x6C   |          | 7:0      | PERBL        | JF[1:0]      |      |         | DITHER    | BUF[5:0] |              | 1        |  |

| 0x6D   |          | 15:8     |              |              |      | PERE    | BUF[9:2]  |          |              |          |  |

| 0x6E   | PERBUF   | 23:16    |              |              |      | PERB    | JF[17:10] |          |              |          |  |

| 0x6F   |          | 31:24    |              |              |      |         |           |          |              |          |  |

| 0x70   |          | 7:0      | CCBU         | F[1:0]       |      |         | DITHER    | BUF[5:0] | 1            |          |  |

| 0x71   | CCBUF0   | 15:8     |              | CCBUF[9:2]   |      |         |           |          |              |          |  |

| 0x72   | CCBUFU   | 23:16    |              | CCBUF[17:10] |      |         |           |          |              |          |  |

| 0x73   |          | 31:24    |              |              |      |         |           |          |              |          |  |

| 0x74   |          | 7:0      | CCBU         | F[1:0]       |      |         | DITHER    | BUF[5:0] |              |          |  |

| 0x75   | CCBUF1   | 15:8     |              |              |      | CCB     | UF[9:2]   |          |              |          |  |

| 0x76   | CCBUFT   | 23:16    | CCBUF[17:10] |              |      |         |           |          |              |          |  |

| 0x77   |          | 31:24    |              |              |      |         |           |          |              |          |  |

| 0x78   |          | 7:0      | CCBU         | F[1:0]       |      |         | DITHER    | BUF[5:0] |              |          |  |

| 0x79   | CCBUF2   | 15:8     | CCBUF[9:2]   |              |      |         |           |          |              |          |  |

| 0x7A   | CCDUF2   | 23:16    |              |              |      | CCBL    | IF[17:10] |          |              |          |  |

| 0x7B   |          | 31:24    |              |              |      |         |           |          |              |          |  |

| 0x7C   |          | 7:0      | CCBU         | F[1:0]       |      |         | DITHER    | BUF[5:0] |              |          |  |

| 0x7D   | CCBUF3   | 15:8     |              |              |      | CCB     | UF[9:2]   |          |              |          |  |

| 0x7E   | CCDUF3   | 23:16    |              |              |      | CCBL    | IF[17:10] |          |              |          |  |

| 0x7F   |          | 31:24    |              |              |      |         |           |          |              |          |  |

### 36.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 36.8.1 Control A

#### Bit 1 – LUPD: Lock Update

This bit controls the update operation of the TCC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

This bit has no effect when input capture operation is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will enable updating.

| Value | Description                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are copied into the                                                                                               |

|       | corresponding CCx, PER, PGV, PGO and SWAPx registers on hardware update condition.                                                                                               |

| 1     | The CCBx, PERB, PGVB, PGOB, and SWAPBx buffer registers values are <i>not</i> copied into the corresponding CCx, PER, PGV, PGO and SWAPx registers on hardware update condition. |

#### Bit 0 – DIR: Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

#### 36.8.3 Control B Set

This register allows the user to change this register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set (CTRLBCLR) register.

Name:CTRLBSETOffset:0x05 [ID-00002e48]Reset:0x00Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Bit    | 7   | 6        | 5   | 4     | 3       | 2       | 1    | 0   |

|--------|-----|----------|-----|-------|---------|---------|------|-----|

|        |     | CMD[2:0] |     | IDXCN | ID[1:0] | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W | R/W   | R/W     | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   | 0     | 0       | 0       | 0    | 0   |

#### Bits 7:5 – CMD[2:0]: TCC Command

These bits can be used for software control of re-triggering and stop commands of the TCC. When a command has been executed, the CMD bit field will be read back as zero. The commands are executed on the next prescaled GCLK\_TCC clock cycle.

Writing zero to this bit group has no effect

Writing a valid value to this bit group will set the associated command.

Name:STATUSBOffset:0x08Reset:0x00Property:Read-Only

| Bit    | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

|        |   |   |   |   | READYx | READYx | READYx | READYx |

| Access |   |   |   |   | R      | R      | R      | R      |

| Reset  |   |   |   |   | 0      | 0      | 0      | 0      |

#### Bits 3,2,1,0 – READYx: Comparator x Ready

This bit is cleared when the comparator x output is not ready. This bit is set when the comparator x output is ready.

If comparator x is not implemented, READYx always reads as zero.

#### 40.8.9 Debug Control

Name:DBGCTRLOffset:0x09 [ID-00000fbb]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

This bits controls the functionality when the CPU is halted by an external debugger.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The AC is halted when the CPU is halted by an external debugger. Any on-going comparison |

|       | will complete.                                                                           |

| 1     | The AC continues normal operation when the CPU is halted by an external debugger.        |

#### 40.8.10 Window Control

Name:WINCTRLOffset:0x0AReset:0x00Property:PAC Write-Protection, Write-Synchronized

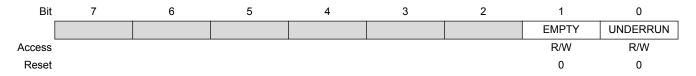

Writing a '1' to this bit will clear the Data Buffer Empty Interrupt Enable bit, which disables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

#### Bit 0 – UNDERRUN: Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Underrun Interrupt Enable bit, which disables the Data Buffer Underrun interrupt.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Data Buffer Underrun interrupt is disabled. |

| 1     | The Data Buffer Underrun interrupt is enabled.  |

#### 41.8.5 Interrupt Enable Set

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name:INTENSETOffset:0x05 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection

#### Bit 1 – EMPTY: Data Buffer Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Empty Interrupt Enable bit, which enables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

#### Bit 0 – UNDERRUN: Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Underrun Interrupt Enable bit, which enables the Data Buffer Underrun interrupt.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Data Buffer Underrun interrupt is disabled. |

| 1     | The Data Buffer Underrun interrupt is enabled.  |

#### 41.8.6 Interrupt Flag Status and Clear

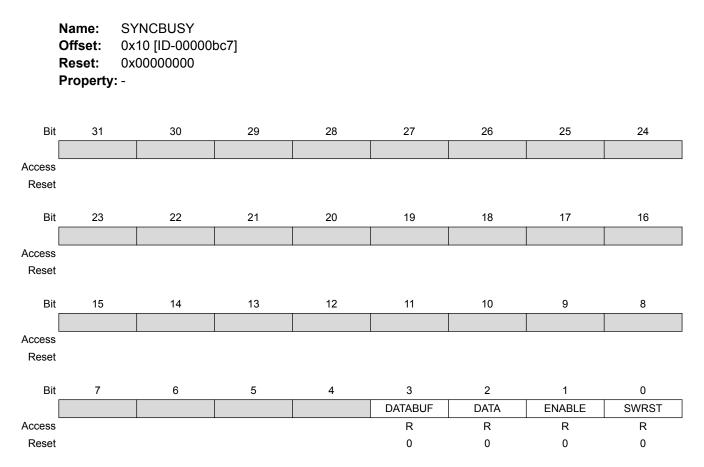

#### 41.8.10 Synchronization Busy

#### Bit 3 – DATABUF: Data Buffer DAC0

This bit is set when DATABUF register is written.

This bit is cleared when DATABUF synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

#### Bit 2 – DATA: Data

This bit is set when DATA register is written.

This bit is cleared when DATA synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

### Bit 1 – ENABLE: DAC Enable Status

This bit is set when CTRLA.ENABLE bit is written.

This bit is cleared when CTRLA.ENABLE synchronization is completed.

| Mode    | Conditions                                                       | Та    | Vcc  | Тур.         | Max.         | Units              |

|---------|------------------------------------------------------------------|-------|------|--------------|--------------|--------------------|

|         | CPU running a CoreMark<br>algorithm                              | 25°C  | 3.0V | 5.2          | 5.7          | mA                 |

|         |                                                                  | 105°C | 3.0V | 5.5          | 6.1          |                    |

|         | CPU running a CoreMark<br>algorithm. with GCLKIN as<br>reference | 25°C  | 5.0V | 115*Freq+167 | 126*Freq+167 | $\mu A$ (with freq |

|         |                                                                  | 105°C | 5.0V | 118*Freq+383 | 121*Freq+823 | in MHz)            |

| IDLE    |                                                                  | 25°C  | 5.0V | 1.2          | 1.3          | mA                 |

|         |                                                                  | 105°C | 5.0V | 1.5          | 2.6          |                    |

| STANDBY | XOSC32K running RTC running at 1kHz                              | 25°C  | 5.0V | 15.9         | 37.0         | μΑ                 |

|         |                                                                  | 105°C | 5.0V | 187.0        | 512.0        |                    |

|         | XOSC32K and RTC stopped                                          | 25°C  | 5.0V | 14.6         | 35.0         |                    |

|         |                                                                  | 105°C | 5.0V | 185.0        | 510.0        |                    |

1. These are based on characterization.

### 46.4 Analog Characteristics

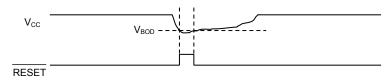

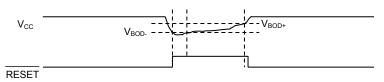

#### 46.4.1 Brown-out Detector Characteristics - BODVDD

See NVM User Row Mapping for the BODVDD default value settings. These values are based on simulation and are not covered by test limits in production or characterization.

#### Figure 46-1. BODVDD Hysteresis OFF

#### Figure 46-2. BODVDD Hysteresis ON

#### Table 46-3. Power Consumption (see Note 1)

| Symbol          | Parameters       | Conditions | Та        | Тур. | Max  | Units |

|-----------------|------------------|------------|-----------|------|------|-------|

| I <sub>DD</sub> | IDLE, Mode CONT  | VDD = 2.7V | Max 105°C | 22.5 | 26.7 | μA    |

|                 |                  | VDD = 5.0V | Typ 25°C  | 41.0 | 47.9 |       |

|                 | IDLE, Mode SAMPL | VDD = 2.7V |           | 0.1  | 1.5  |       |

|                 |                  | VDD = 5.0V |           | 0.1  | 1.9  |       |

## 48. Packaging Information

Table 48-1. Thermal Resistance Data

### 48.1 Thermal Considerations

#### 48.1.1 Thermal Resistance Data

The following table summarizes the thermal resistance data depending on the package.

| Package Type  | θ <sub>JA</sub> | θ <sub>JC</sub> |  |  |  |  |

|---------------|-----------------|-----------------|--|--|--|--|

| 32-pin TQFP   | 63.1°C/W        | 14.3°C/W        |  |  |  |  |

| 48-pin TQFP   | 62.7°C/W        | 11.6°C/W        |  |  |  |  |

| 64-pin TQFP   | 56.3°C/W        | 11.1°C/W        |  |  |  |  |

| 100-pin TQFP  | 55.0°C/W        | 11.1°C/W        |  |  |  |  |

| 32-pin QFN    | 40.5°C/W        | 16.0°C/W        |  |  |  |  |

| 48-pin QFN    | 30.9°C/W        | 10.4°C/W        |  |  |  |  |

| 64-pin QFN    | 31.4°C/W        | 10.2°C/W        |  |  |  |  |

| 56-ball WLCSP | 37.5°C/W        | 5.48°C/W        |  |  |  |  |

#### 48.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- $\theta_{JA}$  = Package thermal resistance, Junction-to-ambient (°C/W), see Thermal Resistance Data

- $\theta_{JC}$  = Package thermal resistance, Junction-to-case thermal resistance (°C/W), see Thermal Resistance Data

- θ<sub>HEATSINK</sub> = Thermal resistance (°C/W) specification of the external cooling device

- P<sub>D</sub> = Device power consumption (W)

- T<sub>A</sub> = Ambient temperature (°C)

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

#### 48.2 Package Drawings

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a>.