#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-TQFP                                                                    |

| Supplier Device Package    | 32-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e15a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 45.3.    | General Operating Ratings                        | 1013 |

|----------|--------------------------------------------------|------|

|          | Injection Current                                |      |

|          | Supply Characteristics                           |      |

|          | Maximum Clock Frequencies                        |      |

|          | Power Consumption                                |      |

|          | Wake-Up Time                                     |      |

|          | I/O Pin Characteristics                          |      |

|          | Analog Characteristics                           |      |

|          | NVM Characteristics                              |      |

|          |                                                  |      |

|          | . Oscillator Characteristics                     |      |

| 45.13    | . Timing Characteristics                         | 1042 |

| 46. Elec | trical Characteristics 105°C (SAM C20/C21 E/G/J) | 1046 |

| 46.1.    | Disclaimer                                       |      |

|          | General Operating Ratings                        |      |

|          | Power Consumption                                |      |

|          | Analog Characteristics                           |      |

|          | NVM Characteristics                              |      |

|          | Oscillator Characteristics                       |      |

| 40.0.    |                                                  |      |

| 47. Elec | trical Characteristics 105°C (SAM C20/C21 N)     | 1054 |

| 47.1.    | Disclaimer                                       | 1054 |

| 47.2.    | General Operating Ratings                        |      |

|          | Power Consumption                                |      |

|          | Analog Characteristics                           |      |

|          | NVM Characteristics                              |      |

|          | Oscillator Characteristics                       |      |

|          |                                                  |      |

|          | kaging Information                               |      |

| 48.1.    | Thermal Considerations                           | 1070 |

| 48.2.    | Package Drawings                                 | 1070 |

| 48.3.    | Soldering Profile                                |      |

| 49. Sch  | ematic Checklist                                 |      |

|          | Introduction                                     |      |

|          | Operation in Noisy Environment                   |      |

|          | Power Supply                                     |      |

|          |                                                  |      |

|          | External Analog Reference Connections            |      |

|          | External Reset Circuit                           |      |

|          | Unused or Unconnected Pins                       |      |

|          | Clocks and Crystal Oscillators                   |      |

| 49.8.    | Programming and Debug Ports                      |      |

| 50. Revi | sion History                                     |      |

| 50.1.    | Revision B - 06/2017                             |      |

| 50.2.    | Revision A - 03/2017                             |      |

|          | Rev KJ - 11/2016                                 |      |

|          | Rev J - 10/2016                                  |      |

|          | Rev I - 09/2016                                  |      |

|          |                                                  |      |

# SAM C20/C21

| Offset       | Name       | Bit Pos.     |          |        |      |          |          |  |

|--------------|------------|--------------|----------|--------|------|----------|----------|--|

|              | Name       |              |          |        |      |          |          |  |

| 0xA9         |            | 15:8         |          |        |      |          |          |  |

| 0xAA         |            | 23:16        |          |        |      |          |          |  |

| 0xAB<br>0xAC |            | 31:24<br>7:0 |          | CHEN   |      |          | ENI[2:0] |  |

| 0xAC<br>0xAD | PCHCTRL11  | 15:8         | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xAD<br>0xAE |            | 23:16        |          |        |      |          |          |  |

| 0xAE<br>0xAF |            | 31:24        |          |        |      |          |          |  |

| 0xAF<br>0xB0 |            | 7:0          | WRTLOCK  | CHEN   |      |          | EN[3:0]  |  |

| 0xB0         |            | 15:8         | WRILOCK  | CHEN   |      | 6        | EN[3.0]  |  |

| 0xB1         | PCHCTRL12  | 23:16        |          |        |      |          |          |  |

| 0xB2         |            | 31:24        |          |        |      |          |          |  |

| 0xB3         |            | 7:0          | WRTLOCK  | CHEN   |      | 6        | EN[3:0]  |  |

| 0xB4         |            | 15:8         | WINTLOOK | CHLIN  |      | 9        |          |  |

| 0xB5<br>0xB6 | PCHCTRL13  | 23:16        |          |        |      |          |          |  |

| 0xB6         |            | 31:24        |          |        |      |          |          |  |

| 0xB7         |            | 7:0          | WRTLOCK  | CHEN   |      | <u> </u> | EN[3:0]  |  |

| 0xB8         |            | 15:8         | WITLOOK  | OTEN   |      | G        |          |  |

| 0xBA         | PCHCTRL14  | 23:16        |          |        |      |          |          |  |

| 0xBB         |            | 31:24        |          |        |      |          |          |  |

| 0xBC         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xBD         | PCHCTRL15  | 15:8         | WITEOOK  | ONEN   |      |          |          |  |

| 0xBE         |            | 23:16        |          |        |      |          |          |  |

| 0xBF         |            | 31:24        |          |        |      |          |          |  |

| 0xC0         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xC1         |            | 15:8         |          | 0.12.1 |      |          |          |  |

| 0xC2         | PCHCTRL16  | 23:16        |          |        |      |          |          |  |

| 0xC3         |            | 31:24        |          |        |      |          |          |  |

| 0xC4         |            | 7:0          | WRTLOCK  | CHEN   | <br> | G        | EN[3:0]  |  |

| 0xC5         |            | 15:8         |          | -      |      |          |          |  |

| 0xC6         | PCHCTRL17  | 23:16        |          |        |      |          |          |  |

| 0xC7         |            | 31:24        |          |        |      |          |          |  |

| 0xC8         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xC9         |            | 15:8         |          |        |      |          |          |  |

| 0xCA         | PCHCTRL18  | 23:16        |          |        |      |          |          |  |

| 0xCB         |            | 31:24        |          |        |      |          |          |  |

| 0xCC         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xCD         | DOLLOTE    | 15:8         |          |        |      |          |          |  |

| 0xCE         | PCHCTRL19  | 23:16        |          |        |      |          |          |  |

| 0xCF         |            | 31:24        |          |        |      |          |          |  |

| 0xD0         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xD1         | DOLLOTELOG | 15:8         |          |        |      |          |          |  |

| 0xD2         | PCHCTRL20  | 23:16        |          |        |      |          |          |  |

| 0xD3         |            | 31:24        |          |        |      |          |          |  |

| 0xD4         |            | 7:0          | WRTLOCK  | CHEN   |      | G        | EN[3:0]  |  |

| 0xD5         |            | 15:8         |          |        |      |          |          |  |

| 0xD6         | PCHCTRL21  | 23:16        |          |        |      |          |          |  |

| 0xD7         | -          | 31:24        |          |        |      |          |          |  |

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBA clock for the MCLK is stopped. |

| 1     | The APBA clock for the MCLK is enabled. |

## Bit 1 – PM: PM APBA Clock Enable

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The APBA clock for the PM is stopped. |

| 1     | The APBA clock for the PM is enabled. |

#### Bit 0 – PAC: PAC APBA Clock Enable

| Va | alue | Description                            |

|----|------|----------------------------------------|

| 0  |      | The APBA clock for the PAC is stopped. |

| 1  |      | The APBA clock for the PAC is enabled. |

#### 17.8.8 APBB Mask

| Name:     | APBBMASK             |

|-----------|----------------------|

| Offset:   | 0x18 [ID-00001086]   |

| Reset:    | 0x0000007            |

| Property: | PAC Write-Protection |

| Bit    | 31 | 30 | 29        | 28 | 27 | 26      | 25  | 24   |

|--------|----|----|-----------|----|----|---------|-----|------|

|        |    |    |           |    |    |         |     |      |

| Access |    |    |           |    |    |         |     |      |

| Reset  |    |    |           |    |    |         |     |      |

|        |    |    |           |    |    |         |     |      |

| Bit    | 23 | 22 | 21        | 20 | 19 | 18      | 17  | 16   |

|        |    |    |           |    |    |         |     |      |

| Access |    |    |           |    |    |         |     |      |

| Reset  |    |    |           |    |    |         |     |      |

|        |    |    |           |    |    |         |     |      |

| Bit    | 15 | 14 | 13        | 12 | 11 | 10      | 9   | 8    |

|        |    |    |           |    |    |         |     |      |

| Access |    |    |           |    |    |         |     |      |

| Reset  |    |    |           |    |    |         |     |      |

|        |    |    |           |    |    |         |     |      |

| Bit    | 7  | 6  | 5         | 4  | 3  | 2       | 1   | 0    |

|        |    |    | HMATRIXHS |    |    | NVMCTRL | DSU | PORT |

| Access |    |    | R/W       |    |    | R/W     | R/W | R/W  |

| Reset  |    |    | 0         |    |    | 1       | 1   | 1    |

#### Bit 5 – HMATRIXHS: HMATRIXHS APBB Clock Enable

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The APBB clock for the HMATRIXHS is stopped |

| 1     | The APBB clock for the HMATRIXHS is enabled |

# Bit 2 – NVMCTRL: NVMCTRL APBB Clock Enable

## Table 19-3. RAM Back-Biasing Mode

| STB | YCDFG.BBIASHS             | RAM                                                            |

|-----|---------------------------|----------------------------------------------------------------|

| 0x0 | No Back Biasing           | RAM is not back-biased if the device is in standby sleep mode. |

| 0x1 | Standby Back Biasing mode | RAM is back-biased if the device is in standby sleep mode.     |

#### 19.6.4.2 Regulator Automatic Low Power Mode

In standby mode, the PM selects either the main or the low power voltage regulator to supply the VDDCORE. By default the low power voltage regulator is used.

If a sleepwalking task is working on either asynchronous clocks (generic clocks) or synchronous clock (APB/AHB clocks), the main voltage regulator is used. This behavior can be changed by writing the Voltage Regulator Standby Mode bits in the Standby Configuration register (STDBYCFG.VREGSMOD). Refer to the following table for details.

## Table 19-4. Regulator State in Sleep Mode

| Sleep<br>Mode | STDBYCFG.<br>VREGSMOD | SleepWalking | Regulator state for VDDCORE |  |  |

|---------------|-----------------------|--------------|-----------------------------|--|--|

| Active        | -                     | -            | main voltage regulator      |  |  |

| Idle          | -                     | -            | main voltage regulator      |  |  |

| Standby       | 0x0: AUTO             | NO           | low power regulator         |  |  |

|               |                       | YES          | main voltage regulator      |  |  |

|               | 0x1: PERFORMANCE      | -            | main voltage regulator      |  |  |

|               | 0x2: LP               | -            | low power regulator         |  |  |

## 19.6.5 DMA Operation

Not applicable.

## 19.6.6 Interrupts

Not applicable.

## 19.6.7 Events

Not applicable.

# 19.6.8 Sleep Mode Operation

The Power Manager is always active.

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28        | 27                                    | 26      | 25       | 24       |

|--------|----|----|----|-----------|---------------------------------------|---------|----------|----------|

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 23 | 22 | 21 | 20        | 19                                    | 18      | 17       | 16       |

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 15 | 14 | 13 | 12        | 11                                    | 10      | 9        | 8        |

|        |    |    |    |           | DPLLLDRTO                             | DPLLLTO | DPLLLCKF | DPLLLCKR |

| Access |    |    |    |           | R/W                                   | R/W     | R/W      | R/W      |

| Reset  |    |    |    |           | 0                                     | 0       | 0        | 0        |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 7  | 6  | 5  | 4         | 3                                     | 2       | 1        | 0        |

|        |    |    |    | OSC48MRDY |                                       |         | CLKFAIL  | XOSCRDY  |

| Access |    | •  | •  | R/W       | · · · · · · · · · · · · · · · · · · · |         | R/W      | R/W      |

| Reset  |    |    |    | 0         |                                       |         | 0        | 0        |

# Bit 11 – DPLLLDRTO: DPLL Loop Divider Ratio Update Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Loop Divider Ratio Update Complete Interrupt Enable bit, which disables the DPLL Loop Divider Ratio Update Complete interrupt.

| Value | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Loop Divider Ratio Update Complete interrupt is disabled.                                                                                                                   |

| 1     | The DPLL Loop Divider Ratio Update Complete interrupt is enabled, and an interrupt request will be generated when the DPLL Loop Divider Ratio Update Complete Interrupt flag is set. |

## Bit 10 – DPLLLTO: DPLL Lock Timeout Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Timeout Interrupt Enable bit, which disables the DPLL Lock Timeout interrupt.

| Value | Description                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Timeout interrupt is disabled.                                                                                             |

| 1     | The DPLL Lock Timeout interrupt is enabled, and an interrupt request will be generated when the DPLL Lock Timeout Interrupt flag is set. |

## Bit 9 – DPLLLCKF: DPLL Lock Fall Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Fall Interrupt Enable bit, which disables the DPLL Lock Fall interrupt.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Fall interrupt is disabled.                                                    |

| 1     | The DPLL Lock Fall interrupt is enabled, and an interrupt request will be generated when the |

|       | DPLL Lock Fall Interrupt flag is set.                                                        |

Increase Priority (INCPRI): increase channel priority

Setting the Channel Control B Event Input Enable bit (CHCTRLB.EVIE=1) enables the corresponding action on input event. clearing this bit disables the corresponding action on input event. Note that several actions can be enabled for incoming events. If several events are connected to the peripheral, any enabled action will be taken for any of the incoming events. For further details on event input actions, refer to Event Input Action section.

## **Related Links**

EVSYS – Event System CHCTRLB BTCTRL

## 25.6.7 Sleep Mode Operation

Each DMA channel can be configured to operate in any sleep mode. To be able to run in standby, the RUNSTDBY bit in Channel Control A register (CHCTRLA.RUNSTDBY) must be written to '1'. The DMAC can wake up the device using interrupts from any sleep mode or perform actions through the Event System.

For channels with CHCTRLA.RUNSTDBY=0, it is up to software to stop DMA transfers on these channels and wait for completion before going to standby mode using the following sequence:

- 1. Suspend the DMAC channels for which CHCTRLA.RUNSTDBY=0.

- 2. Check the SYNCBUSY bits of registers accessed by the DMAC channels being suspended.

- 3. Go to sleep

- 4. When the device wakes up, resume the suspended channels.

**Note:** In standby sleep mode, the DMAC can only access RAM when it is not back biased (PM.STDBYCFG.BBIASxx=0x0)

## 25.6.8 Synchronization

Not applicable.

| Bit    | 31            | 30  | 29  | 28    | 27      | 26  | 25  | 24  |  |

|--------|---------------|-----|-----|-------|---------|-----|-----|-----|--|

|        | EXTINT[31:24] |     |     |       |         |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |

|        |               |     |     |       |         |     |     |     |  |

| Bit    | 23            | 22  | 21  | 20    | 19      | 18  | 17  | 16  |  |

|        |               |     |     | EXTIN | [23:16] |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |

|        |               |     |     |       |         |     |     |     |  |

| Bit    | 15            | 14  | 13  | 12    | 11      | 10  | 9   | 8   |  |

| [      |               |     |     | EXTIN | T[15:8] |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |

|        |               |     |     |       |         |     |     |     |  |

| Bit    | 7             | 6   | 5   | 4     | 3       | 2   | 1   | 0   |  |

|        |               |     |     | EXTIN | IT[7:0] |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W     | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0       | 0   | 0   | 0   |  |

#### Bits 31:0 – EXTINT[31:0]: External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

Writing a '1' to bit x will clear the External Interrupt Enable bit x, which disables the external interrupt EXTINTx.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

#### 26.8.7 Interrupt Enable Set

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

Name:INTENSETOffset:0x10Reset:0x00000000Property:PAC Write-Protection

| Bit    | 31            | 30  | 29  | 28    | 27       | 26  | 25  | 24  |  |

|--------|---------------|-----|-----|-------|----------|-----|-----|-----|--|

| [      | EXTINT[31:24] |     |     |       |          |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |               |     |     |       |          |     |     |     |  |

| Bit    | 23            | 22  | 21  | 20    | 19       | 18  | 17  | 16  |  |

|        |               |     |     | EXTIN | F[23:16] |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |               |     |     |       |          |     |     |     |  |

| Bit    | 15            | 14  | 13  | 12    | 11       | 10  | 9   | 8   |  |

| Γ      |               |     |     | EXTIN | T[15:8]  |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |

|        |               |     |     |       |          |     |     |     |  |

| Bit    | 7             | 6   | 5   | 4     | 3        | 2   | 1   | 0   |  |

| Γ      |               |     |     | EXTIN | IT[7:0]  |     |     |     |  |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |  |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |  |

## Bits 31:0 – EXTINT[31:0]: External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

Writing a '1' to bit x will set the External Interrupt Enable bit x, which enables the external interrupt EXTINTx.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

## 26.8.8 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x14Reset:0x0000000Property: -

# 27.4 Signal Description

Not applicable.

# 27.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described in the following sections.

## 27.5.1 Power Management

The NVMCTRL will continue to operate in any sleep mode where the selected source clock is running. The NVMCTRL interrupts can be used to wake up the device from sleep modes.

The Power Manager will automatically put the NVM block into a low-power state when entering sleep mode. This is based on the Control B register (CTRLB) SLEEPPRM bit setting. Refer to the CTRLB.SLEEPPRM register description for more details. The NVM block goes into low-power mode automatically when the device enters STANDBY mode regardless of SLEEPPRM. The NVM Page Buffer is lost when the NVM goes into low power mode therefore a write command must be issued prior entering the NVM low power mode. NVMCTRL SLEEPPRM can be disabled to avoid such loss when the CPU goes into sleep except if the device goes into STANDBY mode for which there is no way to retain the Page Buffer.

#### **Related Links**

PM – Power Manager

## 27.5.2 Clocks

Two synchronous clocks are used by the NVMCTRL. One is provided by the AHB bus (CLK\_NVMCTRL\_AHB) and the other is provided by the APB bus (CLK\_NVMCTRL\_APB). For higher system frequencies, a programmable number of wait states can be used to optimize performance. When changing the AHB bus frequency, the user must ensure that the NVM Controller is configured with the proper number of wait states. Refer to the Electrical Characteristics for the exact number of wait states to be used for a particular frequency range.

## **Related Links**

Electrical Characteristics 85°C (SAM C20/C21 E/G/J)

## 27.5.3 Interrupts

The NVM Controller interrupt request line is connected to the interrupt controller. Using the NVMCTRL interrupt requires the interrupt controller to be programmed first.

## 27.5.4 Debug Operation

When an external debugger forces the CPU into debug mode, the peripheral continues normal operation.

Access to the NVM block can be protected by the security bit. In this case, the NVM block will not be accessible. See the section on the NVMCTRL Security Bit for details.

## 27.5.5 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following registers:

- Interrupt Flag Status and Clear register (INTFLAG)

- Status register (STATUS)

# 30.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

## **Related Links**

**Register Synchronization**

- Master operation, CTRLA.RUNSTDBY=1: The peripheral clock GCLK\_SERCOM\_CORE will continue to run in idle sleep mode and in standby sleep mode. Any interrupt can wake up the device.

- Master operation, CTRLA.RUNSTDBY=0: GLK\_SERCOMx\_CORE will be disabled after the ongoing transaction is finished. Any interrupt can wake up the device.

- Slave operation, CTRLA.RUNSTDBY=1: The Receive Complete interrupt can wake up the device.

- Slave operation, CTRLA.RUNSTDBY=0: All reception will be dropped, including the ongoing transaction.

## 32.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Receiver Enable bit in the CTRLB register (CTRLB.RXEN)

**Note:** CTRLB.RXEN is write-synchronized somewhat differently. See also *CTRLB* register for details.

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

# **Related Links**

**Register Synchronization**

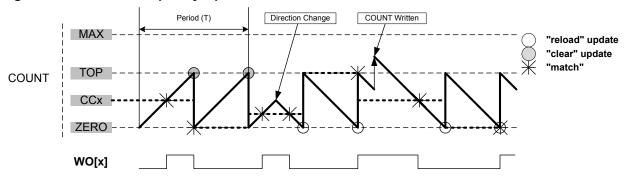

When using the TC and the Compare/Capture Value registers (CCx) for compare operations, the counter value is continuously compared to the values in the CCx registers. This can be used for timer or for waveform operation.

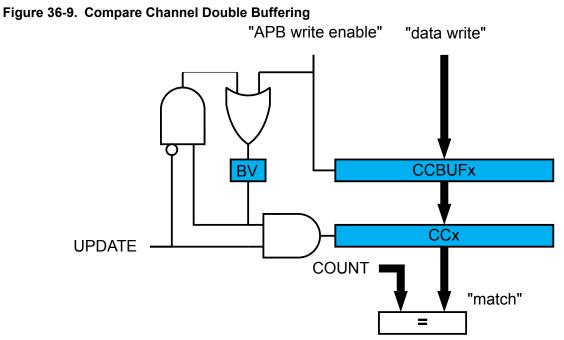

The Channel x Compare Buffer (CCBUFx) registers provide double buffer capability. The double buffering synchronizes the update of the CCx register with the buffer value at the UPDATE condition or a forced update command (CTRLBSET.CMD=UPDATE). For further details, refer to Double Buffering. The synchronization prevents the occurrence of odd-length, non-symmetrical pulses and ensures glitch-free output.

## Waveform Output Operations

The compare channels can be used for waveform generation on output port pins. To make the waveform available on the connected pin, the following requirements must be fulfilled:

- 1. Choose a waveform generation mode in the Waveform Generation Operation bit in Waveform register (WAVE.WAVEGEN).

- 2. Optionally invert the waveform output WO[x] by writing the corresponding Output Waveform x Invert Enable bit in the Driver Control register (DRVCTRL.INVENx).

- 3. Configure the pins with the I/O Pin Controller. Refer to PORT I/O Pin Controller for details.

The counter value is continuously compared with each CCx value. On a comparison match, the Match or Capture Channel x bit in the Interrupt Flag Status and Clear register (INTFLAG.MCx) will be set on the next zero-to-one transition of CLK\_TC\_CNT (see Normal Frequency Operation). An interrupt/and or event can be generated on comparison match if enabled. The same condition generates a DMA request.

There are four waveform configurations for the Waveform Generation Operation bit group in the Waveform register (WAVE.WAVEGEN). This will influence how the waveform is generated and impose restrictions on the top value. The configurations are:

- Normal frequency (NFRQ)

- Match frequency (MFRQ)

- Normal pulse-width modulation (NPWM)

- Match pulse-width modulation (MPWM)

When using NPWM or NFRQ configuration, the TOP will be determined by the counter resolution. In 8-bit counter mode, the Period register (PER) is used as TOP, and the TOP can be changed by writing to the PER register. In 16- and 32-bit counter mode, TOP is fixed to the maximum (MAX) value of the counter.

# Normal Frequency Generation (NFRQ)

For Normal Frequency Generation, the period time (T) is controlled by the period register (PER) for 8-bit counter mode and MAX for 16- and 32-bit mode. The waveform generation output (WO[x]) is toggled on each compare match between COUNT and CCx, and the corresponding Match or Capture Channel x Interrupt Flag (INTFLAG.MCx) will be set.

## Figure 35-4. Normal Frequency Operation

| Bit    | 15  | 14  | 13  | 12               | 11    | 10  | 9   | 8   |

|--------|-----|-----|-----|------------------|-------|-----|-----|-----|

| Γ      |     |     |     | CC[ <sup>2</sup> | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

|        |     |     |     |                  |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4                | 3     | 2   | 1   | 0   |

| Γ      |     |     |     | CC[              | [7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

#### Bits 15:0 – CC[15:0]: Channel x Compare/Capture Value

These bits contain the compare/capture value in 16-bit TC mode. In Match frequency (MFRQ) or Match PWM (MPWM) waveform operation (WAVE.WAVEGEN), the CC0 register is used as a period register.

#### 35.7.2.16 Period Buffer Value, 16-bit Mode

Name:PERBUFOffset:0x2EReset:0xFFFFProperty:Write-Synchronized

| Bit    | 15  | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

|--------|-----|-----|-----|-------|----------|-----|-----|-----|

|        |     |     |     | PERBL | JF[15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

|        |     |     |     | PERB  | JF[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 1   |

|        |     |     |     |       |          |     |     |     |

## Bits 15:0 – PERBUF[15:0]: Period Buffer Value

These bits hold the value of the period buffer register. The value is copied to PER register on UPDATE condition.

#### 35.7.2.17 Channel x Compare Buffer Value, 16-bit Mode

Name:CCBUFxOffset:0x30 + x\*0x02 [x=0..1]Reset:0x0000Property:Write-Synchronized

| Pin Name          | Туре           | Description                       |

|-------------------|----------------|-----------------------------------|

|                   |                |                                   |

| TCCx/WO[WO_NUM-1] | Digital output | Compare channel n waveform output |

Refer to *I/O Multiplexing and Considerations* for details on the pin mapping for this peripheral. One signal can be mapped on several pins.

#### **Related Links**

I/O Multiplexing and Considerations

# 36.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 36.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

#### **Related Links**

PORT: IO Pin Controller

#### 36.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### 36.5.3 Clocks

The TCC bus clock (CLK\_TCCx\_APB, with x instance number of the TCCx) is enabled by default, and can be enabled and disabled in the Main Clock.

A generic clock (GCLK\_TCCx) is required to clock the TCC. This clock must be configured and enabled in the generic clock controller before using the TCC. Note that TCC0 and TCC1 share a peripheral clock generator.

The generic clocks (GCLK\_TCCx) are asynchronous to the bus clock (CLK\_TCCx\_APB). Due to this asynchronicity, writing certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

#### 36.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

DMAC - Direct Memory Access Controller

Both the registers (PATT/WAVE/PER/CCx) and corresponding buffer registers (PATTBUF/WAVEBUFV/ PERBUF/CCBUFx) are available in the I/O register map, and the double buffering feature is not mandatory. The double buffering is disabled by writing a '1' to CTRLSET.LUPD.

**Note:** In NFRQ, MFRQ or PWM down-counting counter mode (CTRLBSET.DIR=1), when double buffering is enabled (CTRLBCLR.LUPD=1), PERBUF register is continuously copied into the PER independently of update conditions.

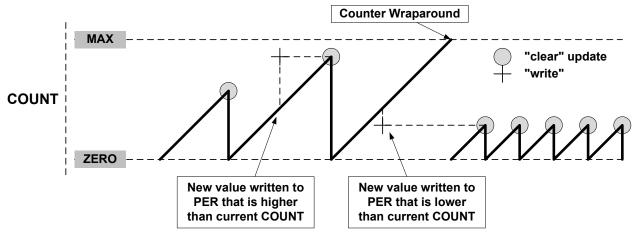

# Changing the Period

The counter period can be changed by writing a new Top value to the Period register (PER or CC0, depending on the waveform generation mode), any period update on registers (PER or CCx) is effective after the synchronization delay, whatever double buffering enabling is.

| Figure 36-10. Unbuffered Single-Slope Up-Counting Operation | Figure 36-10. | Unbuffered | Single-Slope | <b>Up-Counting</b> | Operation |

|-------------------------------------------------------------|---------------|------------|--------------|--------------------|-----------|

|-------------------------------------------------------------|---------------|------------|--------------|--------------------|-----------|

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Number of<br>Automatic Right<br>Shifts | Final Result<br>Precision | Automatic<br>Division Factor |

|-------------------------------------|-----------------------|----------------------------------------|---------------------------|------------------------------|

| 4                                   | 0x2                   | 0                                      | 14 bits                   | 0                            |

| 8                                   | 0x3                   | 0                                      | 15 bits                   | 0                            |

| 16                                  | 0x4                   | 0                                      | 16 bits                   | 0                            |

| 32                                  | 0x5                   | 1                                      | 16 bits                   | 2                            |

| 64                                  | 0x6                   | 2                                      | 16 bits                   | 4                            |

| 128                                 | 0x7                   | 3                                      | 16 bits                   | 8                            |

| 256                                 | 0x8                   | 4                                      | 16 bits                   | 16                           |

| 512                                 | 0x9                   | 5                                      | 16 bits                   | 32                           |

| 1024                                | 0xA                   | 6                                      | 16 bits                   | 64                           |

| Reserved                            | 0xB –0xF              |                                        | 12 bits                   | 0                            |

#### 38.6.2.10 Averaging

Averaging is a feature that increases the sample accuracy, at the cost of a reduced sampling rate. This feature is suitable when operating in noisy conditions.

Averaging is done by accumulating m samples, as described in Accumulation, and dividing the result by m. The averaged result is available in the RESULT register. The number of samples to be accumulated is specified by writing to AVGCTRL.SAMPLENUM as shown in Table 38-2.

The division is obtained by a combination of the automatic right shift described above, and an additional right shift that must be specified by writing to the Adjusting Result/Division Coefficient field in AVGCTRL (AVGCTRL.ADJRES), as described in Table 38-2.

**Note:** To perform the averaging of two or more samples, the Conversion Result Resolution field in the Control C register (CTRLC.RESSEL) must be set.

Averaging AVGCTRL.SAMPLENUM samples will reduce the un-averaged sampling rate by a factor

#### AVGCTRL.SAMPLENUM.

When the averaged result is available, the INTFLAG.RESRDY bit will be set.

#### Table 38-2. Averaging

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result<br>Precision | Number of<br>Automatic<br>Right<br>Shifts |    | AVGCTRL.ADJRES | Total<br>Number<br>of Right<br>Shifts | Final<br>Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|----|----------------|---------------------------------------|------------------------------|---------------------------------|

| 1                                   | 0x0                   | 12 bits                             | 0                                         | 1  | 0x0            |                                       | 12 bits                      | 0                               |

| 2                                   | 0x1                   | 13                                  | 0                                         | 2  | 0x1            | 1                                     | 12 bits                      | 0                               |

| 4                                   | 0x2                   | 14                                  | 0                                         | 4  | 0x2            | 2                                     | 12 bits                      | 0                               |

| 8                                   | 0x3                   | 15                                  | 0                                         | 8  | 0x3            | 3                                     | 12 bits                      | 0                               |

| 16                                  | 0x4                   | 16                                  | 0                                         | 16 | 0x4            | 4                                     | 12 bits                      | 0                               |

| 32                                  | 0x5                   | 17                                  | 1                                         | 16 | 0x4            | 5                                     | 12 bits                      | 2                               |

# SAM C20/C21

| Bit    | 31 | 30 | 29        | 28  | 27   | 26     | 25  | 24  |

|--------|----|----|-----------|-----|------|--------|-----|-----|

|        |    |    |           |     |      |        |     |     |

| Access |    |    |           |     |      |        |     |     |

| Reset  |    |    |           |     |      |        |     |     |

|        |    |    |           |     |      |        |     |     |

| Bit    | 23 | 22 | 21        | 20  | 19   | 18     | 17  | 16  |

|        |    |    |           |     |      |        |     |     |

| Access |    |    |           |     |      |        |     |     |

| Reset  |    |    |           |     |      |        |     |     |

|        |    |    |           |     |      |        |     |     |

| Bit    | 15 | 14 | 13        | 12  | 11   | 10     | 9   | 8   |

| [      |    |    |           |     | TCAI | _[5:0] |     |     |

| Access |    |    | R/W       | R/W | R/W  | R/W    | R/W | R/W |

| Reset  |    |    | 0         | 0   | 0    | 0      | 0   | 0   |

|        |    |    |           |     |      |        |     |     |

| Bit    | 7  | 6  | 5         | 4   | 3    | 2      | 1   | 0   |

|        |    |    | FCAL[5:0] |     |      |        |     |     |

| Access |    |    | R/W       | R/W | R/W  | R/W    | R/W | R/W |

| Reset  |    |    | 0         | 0   | 0    | 0      | 0   | 0   |

#### Bits 13:8 – TCAL[5:0]: Temperature Calibration

This value from production test must be loaded from the NVM software calibration row into the CAL register by software to achieve the specified accuracy. The value must be copied only, and must not be changed.

#### Bits 5:0 – FCAL[5:0]: Frequency Calibration

This value from production test must be loaded from the NVM software calibration row into the CAL register by software to achieve the specified accuracy. The value must be copied only, and must not be changed.

#### 43.8.16 Debug Control

Name:

DBGCTRL

Offset:

0x24 [ID-00001f13]

Reset:

0x00

Property:

–

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

## Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

This bits controls the functionality when the CPU is halted by an external debugger.

# 46. Electrical Characteristics 105°C (SAM C20/C21 E/G/J)

# 46.1 Disclaimer

All typical values are measured at Ta = 25°C unless otherwise specified. All minimum and maximum values are valid across operating temperature and voltage unless otherwise specified.

This chapter contains only characteristics specific for the SAM C20/C21 E/G/J (Ta = 105°C). For all other values or missing characteristics, refer to the 85°C chapter.

# 46.2 General Operating Ratings

The device must operate within the ratings listed in the table below in order for all other electrical characteristics and typical characteristics of the device to be valid.

Table 46-1. General operating conditions

| Symbol         | Parameter            | Min. | Тур. | Max. | Units |

|----------------|----------------------|------|------|------|-------|

| T <sub>A</sub> | Temperature range    | -40  | 25   | 105  | °C    |

| TJ             | Junction temperature | -    | -    | 125  | °C    |

# 46.3 Power Consumption

## Table 46-2. Power Consumption<sup>(1)</sup>

| Mode   | Conditions                           | Та    | Vcc  | Тур.        | Max.        | Units         |  |

|--------|--------------------------------------|-------|------|-------------|-------------|---------------|--|

| ACTIVE | CPU running a While 1                | 25°C  | 5.0V | 3.8         | 4.2         | mA            |  |

|        | algorithm                            | 105°C | 5.0V | 4.0         | 4.5         |               |  |

|        | CPU running a While 1                | 25°C  | 3.0V | 3.7         | 4.1         | mA            |  |

|        | algorithm                            | 105°C | 3.0V | 4.0         | 4.5         |               |  |

|        | CPU running a While 1                | 25°C  | 5.0V | 71*Freq+160 | 78*Freq+162 | μA (with freq |  |

|        | algorithm. with GCLKIN as reference  | 105°C | 5.0V | 71*Freq+374 | 72*Freq+819 | in MHz)       |  |

|        | CPU running a Fibonacci<br>algorithm | 25°C  | 5.0V | 4.7         | 5.2         | mA            |  |

|        |                                      | 105°C | 5.0V | 5.0         | 5.5         |               |  |

|        | CPU running a Fibonacci<br>algorithm | 25°C  | 3.0V | 4.7         | 5.1         | mA            |  |

|        |                                      | 105°C | 3.0V | 5.0         | 5.5         |               |  |

|        | CPU running a Fibonacci              | 25°C  | 5.0V | 90*Freq+163 | 99*Freq+168 | µA (with freq |  |

|        | algorithm. with GCLKIN as reference  | 105°C | 5.0V | 90*Freq+379 | 92*Freq+820 | in MHz)       |  |

|        | CPU running a CoreMark               | 25°C  | 5.0V | 5.9         | 6.4         | mA            |  |

|        | algorithm                            | 105°C | 5.0V | 6.3         | 6.9         |               |  |

resistor. External or internal pull up/down resistors can be used, e.g. the pins can be configured in pull-up or pull-down mode eliminating the need for external components. There are no obvious benefit in choosing external vs. internal pull resistors.

## **Related Links**

PORT - I/O Pin Controller

# 49.7 Clocks and Crystal Oscillators

The SAM C20/C21 can be run from internal or external clock sources, or a mix of internal and external sources. An example of usage will be to use the internal 8MHz oscillator as source for the system clock, and an external 32.768kHz watch crystal as clock source for the Real-Time counter (RTC).

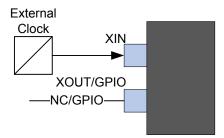

## 49.7.1 External Clock Source

## Figure 49-6. External Clock Source Schematic

## Table 49-4. External Clock Source Connections

| Signal Name | Recommended Pin Connection                        | Description                        |

|-------------|---------------------------------------------------|------------------------------------|

| XIN         | XIN is used as input for an external clock signal | Input for inverting oscillator pin |

| XOUT/GPIO   | Can be left unconnected or used as normal GPIO    | NC/GPIO                            |

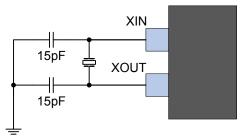

## 49.7.2 Crystal Oscillator

## Figure 49-7. Crystal Oscillator Schematic

The crystal should be located as close to the device as possible. Long signal lines may cause too high load to operate the crystal, and cause crosstalk to other parts of the system.

## Table 49-5. Crystal Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description                           |

|-------------|---------------------------------------|---------------------------------------|

| XIN         | Load capacitor 15pF <sup>(1)(2)</sup> | External crystal between 0.4 to 32MHz |

| XOUT        | Load capacitor 15pF <sup>(1)(2)</sup> |                                       |

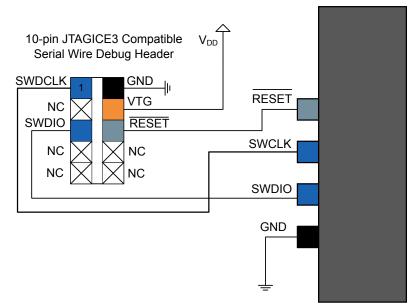

Figure 49-13. 10-pin JTAGICE3 Compatible Serial Wire Debug Interface

Table 49-9.

10-pin JTAGICE3 Compatible Serial Wire Debug Interface

| Header Signal Name | Description                                                      |

|--------------------|------------------------------------------------------------------|

| SWDCLK             | Serial wire clock pin                                            |

| SWDIO              | Serial wire bidirectional data pin                               |

| RESET              | Target device reset pin, active low                              |

| VTG                | Target voltage sense, should be connected to the device $V_{DD}$ |

| GND                | Ground                                                           |

## 49.8.3 20-pin IDC JTAG Connector

For debuggers and/or programmers that support the 20-pin IDC JTAG Connector, e.g. the SAM-ICE, the signals should be connected as shown in Figure 49-14 with details described in Table 49-10.