# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e16a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 8. **Product Mapping**

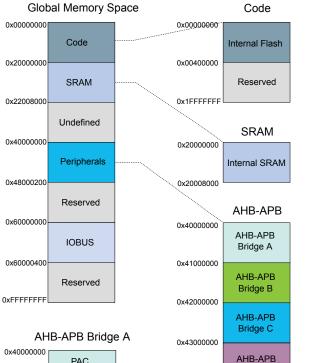

Figure 8-1. SAM C21 N Product Mapping

#### 0x40000000 PAC 0x40000400 ΡM 0x40000800 MCLK 0x40000C00 RSTC 0x40001000 OSCCTRL 0x40001400 OSC32KCTRL 0x40001800 SUPC 0x40001C00 GCLK 0x40002000 WDT 0x40002400 RTC 0x40002800 EIC 0x40002C00 FREQM 0x40003000 TSENS 0x40003400 Reserved 0x40FFFFFF

| AHE        | 3-APB Bridge | С |

|------------|--------------|---|

| 0x42000000 | EVSYS        |   |

| 0x42000400 | SERCOM0      |   |

| 0x42000800 | SERCOM1      |   |

| 0x42000C00 | SERCOM2      |   |

| 0x42001000 | SERCOM3      |   |

| 0x42001400 | SERCOM4      |   |

| 0x42001800 | SERCOM5      |   |

| 0x42001C00 | CAN0         |   |

| 0x42002000 | CAN1         |   |

| 0x42002400 | TCC0         |   |

| 0x42002800 | TCC1         |   |

| 0x42002C00 | TCC2         |   |

| 0x42003000 | тсо          |   |

| 0x42003400 | TC1          |   |

| 0x42003800 | TC2          |   |

| 0x42003C00 | TC3          |   |

| 0x42004000 | TC4          |   |

| 0x42004400 | ADC0         |   |

| 0x42004800 | ADC1         |   |

| 0x42004C00 | SDADC        |   |

| 0x42005000 | AC           |   |

| 0x42005400 | DAC          |   |

| 0x42005800 | PTC          |   |

| 0x42005C00 | CCL          |   |

| 0x42006000 | Reserved     |   |

| 0x42FFFFFF |              | _ |

#### AHB-APB Bridge D

| 0 1000000                |          |

|--------------------------|----------|

| 0x43000000<br>0x43000400 | SERCOM6  |

|                          | SERCOM7  |

| 0x43000800               | TC5      |

| 0x43000C00<br>0x43001000 | TC6      |

|                          | TC7      |

| 0x43001400<br>0x43001800 | Reserved |

| 0843001800               |          |

DS60001479B-page 43

Bridge D

AHB DIVAS

AHB-APB Bridge B

PORT

DSU

NVMCTRL

DMAC

MTB

Reserved

0x48000000

0x480001FF

0x41000000

0x41002000

0x41004000

0x41006000

0x41008000

0x41009000

0x41FFFFFF

PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45

#### 16.6.3.4 Configuration Lock

The peripheral clock configuration can be locked for further write accesses by setting the Write Lock bit in the Peripheral Channel Control register PCHCTRLm.WRTLOCK=1). All writing to the PCHCTRLm register will be ignored. It can only be unlocked by a Power Reset.

The Generator source of a locked Peripheral Channel will be locked, too: The corresponding GENCTRLn register is locked, and can be unlocked only by a Power Reset.

There is one exception concerning the Generator 0. As it is used as GCLK\_MAIN, it cannot be locked. It is reset by any Reset and will start up in a known configuration. The software reset (CTRLA.SWRST) can not unlock the registers.

In case of an external Reset, the Generator source will be disabled. Even if the WRTLOCK bit is written to '1' the peripheral channels are disabled (PCHCTRLm.CHEN set to '0') until the Generator source is enabled again. Then, the PCHCTRLm.CHEN are set to '1' again.

# Related Links

#### CTRLA

#### 16.6.4 Additional Features

#### 16.6.4.1 Peripheral Clock Enable after Reset

The Generic Clock Controller must be able to provide a generic clock to some specific peripherals after a Reset. That means that the configuration of the Generators and Peripheral Channels after Reset is device-dependent.

Refer to GENCTRLn.SRC for details on GENCTRLn reset.

Refer to PCHCTRLm.SRC for details on PCHCTRLm reset.

#### 16.6.5 Sleep Mode Operation

#### 16.6.5.1 SleepWalking

The GCLK module supports the SleepWalking feature.

If the system is in a sleep mode where the Generic Clocks are stopped, a peripheral that needs its clock in order to execute a process must request it from the Generic Clock Controller.

The Generic Clock Controller receives this request, determines which Generic Clock Generator is involved and which clock source needs to be awakened. It then wakes up the respective clock source, enables the Generator and Peripheral Channel stages successively, and delivers the clock to the peripheral.

The RUNSTDBY bit in the Generator Control register controls clock output to pin during standby sleep mode. If the bit is cleared, the Generator output is not available on pin. When set, the GCLK can continuously output the generator output to GCLK\_IO. Refer to External Clock for details.

#### **Related Links**

PM – Power Manager

| Value     | Name     | Description              |

|-----------|----------|--------------------------|

| 0x06      | OSC48M   | OSC48M oscillator output |

| 0x07      | DPLL96M  | DPLL96M output           |

| 0x08-0x1F | Reserved | Reserved for future use  |

A Power Reset will reset all GENCTRLn registers. the Reset values of the GENCTRLn registers are shown in table below.

#### Table 16-5. GENCTRLn Reset Value after a Power Reset

| GCLK Generator | Reset Value after a Power Reset |

|----------------|---------------------------------|

| 0              | 0x0000106                       |

| others         | 0x0000000                       |

A User Reset will reset the associated GENCTRL register unless the Generator is the source of a locked Peripheral Channel (PCHCTRLm.WRTLOCK=1). The reset values of the GENCTRL register are as shown in the table below.

#### Table 16-6. GENCTRLn Reset Value after a User Reset

| GCLK Generator | Reset Value after a User Reset                                                                       |

|----------------|------------------------------------------------------------------------------------------------------|

| 0              | 0x0000106                                                                                            |

| others         | No change if the generator is used by a Peripheral Channel m with PCHCTRLm.WRTLOCK=1 else 0x00000000 |

#### Related Links

PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45

#### 16.8.4 Peripheral Channel Control

PCHTRLm controls the settings of Peripheral Channel number m (m=0..45).

Name: PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36,

#### Bit 12 – TC0: TC0 APBC Mask Clock Enable

| Value | Description                            |  |

|-------|----------------------------------------|--|

| 0     | The APBC clock for the TC0 is stopped. |  |

| 1     | The APBC clock for the TC0 is enabled. |  |

#### Bit 11 – TCC2: TCC2 APBC Mask Clock Enable

| Value | Description                             |  |

|-------|-----------------------------------------|--|

| 0     | The APBC clock for the TCC2 is stopped. |  |

| 1     | The APBC clock for the TCC2 is enabled. |  |

#### Bit 10 – TCC1: TCC1 APBC Mask Clock Enable

| Value | Description                             |  |

|-------|-----------------------------------------|--|

| 0     | The APBC clock for the TCC1 is stopped. |  |

| 1     | The APBC clock for the TCC1 is enabled. |  |

#### Bit 9 – TCC0: TCC0 APBC Mask Clock Enable

| Value | Description                             |  |

|-------|-----------------------------------------|--|

| 0     | The APBC clock for the TCC0 is stopped. |  |

| 1     | The APBC clock for the TCC0 is enabled. |  |

#### Bit 6 – SERCOM5: SERCOM5 APBC Mask Clock Enable

| Value | Description                                |  |

|-------|--------------------------------------------|--|

| 0     | The APBC clock for the SERCOM5 is stopped. |  |

| 1     | The APBC clock for the SERCOM5 is enabled. |  |

#### Bit 5 – SERCOM4: SERCOM4 APBC Mask Clock Enable

| Va | alue | Description                                |

|----|------|--------------------------------------------|

| 0  |      | The APBC clock for the SERCOM4 is stopped. |

| 1  |      | The APBC clock for the SERCOM4 is enabled. |

#### Bit 4 – SERCOM3: SERCOM3 APBC Mask Clock Enable

| Value | Description                                |  |

|-------|--------------------------------------------|--|

| 0     | The APBC clock for the SERCOM3 is stopped. |  |

| 1     | The APBC clock for the SERCOM3 is enabled. |  |

#### Bit 3 – SERCOM2: SERCOM2 APBC Mask Clock Enable

| Value | Description                                |  |

|-------|--------------------------------------------|--|

| 0     | The APBC clock for the SERCOM2 is stopped. |  |

| 1     | The APBC clock for the SERCOM2 is enabled. |  |

#### Bit 2 – SERCOM1: SERCOM1 APBC Mask Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM1 is stopped. |

| 1     | The APBC clock for the SERCOM1 is enabled. |

#### **Related Links**

GCLK - Generic Clock Controller

#### 20.6.3 Clock Failure Detection Operation

The Clock Failure Detector (CFD) allows the user to monitor the external clock or crystal oscillator signal provided by the external oscillator (XOSC). The CFD detects failing operation of the XOSC clock with reduced latency, and allows to switch to a safe clock source in case of clock failure. The user can also switch from the safe clock back to XOSC in case of recovery. The safe clock is derived from the OSC48M oscillator with a configurable prescaler. This allows to configure the safe clock in order to fulfill the operative conditions of the microcontroller.

In sleep modes, CFD operation is automatically disabled when the external oscillator is not requested to run by a peripheral. See the Sleep Behavior table above when this is the case.

The user interface registers allow to enable, disable, and configure the CFD. The Status register provides status flags on failure and clock switch conditions. The CFD can optionally trigger an interrupt or an event when a failure is detected.

#### **Clock Failure Detection**

The CFD is reset only at power-on (POR). The CFD does not monitor the XOSC clock when the oscillator is disabled (XOSCCTRL.ENABLE=0).

Before starting CFD operation, the user must start and enable the safe clock source (OSC48M oscillator).

CFD operation is started by writing a '1' to the CFD Enable bit in the External Oscillator Control register (XOCCTRL.CFDEN). After starting or restarting the XOSC, the CFD does not detect failure until the startup time has elapsed. The start-up time is configured by the Oscillator Start-Up Time in the External Multipurpose Crystal Oscillator Control register (XOSCCTRL.STARTUP). Once the XOSC Start-Up Time is elapsed, the XOSC clock is constantly monitored.

During a period of 4 safe clocks (monitor period), the CFD watches for a clock activity from the XOSC. There must be at least one rising and one falling XOSC clock edge during 4 safe clock periods to meet non-failure conditions. If no or insufficient activity is detected, the failure status is asserted: The Clock Failure Detector status bit in the Status register (STATUS.CLKFAIL) and the Clock Failure Detector interrupt flag bit in the Interrupt Flag register (INTFLAG.CLKFAIL) are set. If the CLKFAIL bit in the Interrupt Enable Set register (INTENSET.CLKFAIL) is set, an interrupt is generated as well. If the Event Output enable bit in the Event Control register (EVCTRL.CFDEO) is set, an output event is generated, too.

After a clock failure was issued the monitoring of the XOSC clock is continued, and the Clock Failure Detector status bit in the Status register (STATUS.CLKFAIL) reflects the current XOSC activity.

#### **Clock Switch**

When a clock failure is detected, the XOSC clock is replaced by the safe clock in order to maintain an active clock during the XOSC clock failure. The safe clock source is the OSC48M oscillator clock. The safe clock source can be scaled down by a configurable prescaler to ensure that the safe clock frequency does not exceed the operating conditions selected by the application. When the XOSC clock is switched to the safe clock, the Clock Switch bit in the Status register (STATUS.CLKSW) is set.

When the CFD has switched to the safe clock, the XOSC is not disabled. If desired, the application must take the necessary actions to disable the oscillator. The application must also take the necessary actions to configure the system clocks to continue normal operations.

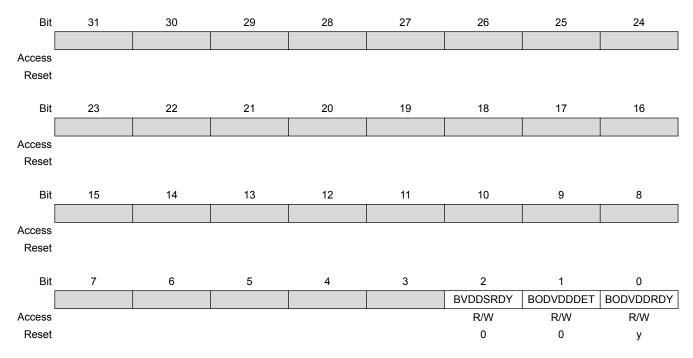

#### Bit 1 – BODVDDDET: BODVDD Detection Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the BODVDD Detection Interrupt Enable bit, which enables the BODVDD Detection interrupt.

| Value | Description                                                                                                                            |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0     | The BODVDD Detection interrupt is disabled.                                                                                            |  |  |

| 1     | The BODVDD Detection interrupt is enabled, and an interrupt request will be generated when the BODVDD Detection Interrupt flag is set. |  |  |

#### Bit 0 – BODVDDRDY: BODVDD Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the BODVDD Ready Interrupt Enable bit, which enables the BODVDD Ready interrupt.

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BODVDD Ready interrupt is disabled.                                                                                        |

| 1     | The BODVDD Ready interrupt is enabled, and an interrupt request will be generated when the BODVDD Ready Interrupt flag is set. |

#### 22.8.3 Interrupt Flag Status and Clear

Name: INTFLAG

Offset: 0x08 [ID-00001e33]

| Reset:   | 0x0000010X, X= determined from NVM User Row (0xX=0bx00y) |  |

|----------|----------------------------------------------------------|--|

| Property | -                                                        |  |

#### Bit 2 – BVDDSRDY: BODVDD Synchronization Ready

This flag is cleared by writing a '1' to it.

# 23. WDT – Watchdog Timer

### 23.1 Overview

The Watchdog Timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is configured to a predefined time-out period, and is constantly running when enabled. If the WDT is not cleared within the time-out period, it will issue a system reset. An early-warning interrupt is available to indicate an upcoming watchdog time-out condition.

The window mode makes it possible to define a time slot (or window) inside the total time-out period during which the WDT must be cleared. If the WDT is cleared outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes the WDT to be cleared frequently.

When enabled, the WDT will run in active mode and all sleep modes. It is asynchronous and runs from a CPU-independent clock source. The WDT will continue operation and issue a system reset or interrupt even if the main clocks fail.

### 23.2 Features

- Issues a system reset if the Watchdog Timer is not cleared before its time-out period

- Early Warning interrupt generation

- Asynchronous operation from dedicated oscillator

- Two types of operation

- Normal

- Window mode

- Selectable time-out periods

- From 8 cycles to 16,384 cycles in Normal mode

- From 16 cycles to 32,768 cycles in Window mode

- Always-On capability

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | The Source Address Increment is disabled. |

| 1     | The Source Address Increment is enabled.  |

#### Bits 9:8 – BEATSIZE[1:0]: Beat Size

These bits define the size of one beat. A beat is the size of one data transfer bus access, and the setting apply to both read and write accesses.

| Value | Name  | Description         |

|-------|-------|---------------------|

| 0x0   | BYTE  | 8-bit bus transfer  |

| 0x1   | HWORD | 16-bit bus transfer |

| 0x2   | WORD  | 32-bit bus transfer |

| other |       | Reserved            |

#### Bits 4:3 – BLOCKACT[1:0]: Block Action

These bits define what actions the DMAC should take after a block transfer has completed.

| BLOCKACT[1:0] | Name    | Description                                                                                      |

|---------------|---------|--------------------------------------------------------------------------------------------------|

| 0x0           | NOACT   | Channel will be disabled if it is the last block transfer in the transaction                     |

| 0x1           | INT     | Channel will be disabled if it is the last block transfer in the transaction and block interrupt |

| 0x2           | SUSPEND | Channel suspend operation is completed                                                           |

| 0x3           | BOTH    | Both channel suspend operation and block interrupt                                               |

#### Bits 2:1 – EVOSEL[1:0]: Event Output Selection

These bits define the event output selection.

| EVOSEL[1:0] | Name    | Description                               |

|-------------|---------|-------------------------------------------|

| 0x0         | DISABLE | Event generation disabled                 |

| 0x1         | BLOCK   | Event strobe when block transfer complete |

| 0x2         |         | Reserved                                  |

| 0x3         | BEAT    | Event strobe when beat transfer complete  |

#### Bit 0 – VALID: Descriptor Valid

Writing a '0' to this bit in the Descriptor or Write-Back memory will suspend the DMA channel operation when fetching the corresponding descriptor.

The bit is automatically cleared in the Write-Back memory section when channel is aborted, when an error is detected during the block transfer, or when the block transfer is completed.

| Value | Description                  |  |

|-------|------------------------------|--|

| 0     | The descriptor is not valid. |  |

| 1     | The descriptor is valid.     |  |

#### 25.10.2 Block Transfer Count

The BTCNT register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| BAUD Register Value | Serial Engine CPF | f <sub>BAUD</sub> at 48MHz Serial Engine Frequency (f <sub>REF</sub> ) |

|---------------------|-------------------|------------------------------------------------------------------------|

| 0 – 406             | 160               | 3MHz                                                                   |

| 407 – 808           | 161               | 2.981MHz                                                               |

| 809 – 1205          | 162               | 2.963MHz                                                               |

|                     |                   |                                                                        |

| 65206               | 31775             | 15.11kHz                                                               |

| 65207               | 31871             | 15.06kHz                                                               |

| 65208               | 31969             | 15.01kHz                                                               |

Table 30-3. BAUD Register Value vs. Baud Frequency

#### 30.6.3 Additional Features

#### 30.6.3.1 Address Match and Mask

The SERCOM address match and mask feature is capable of matching either one address, two unique addresses, or a range of addresses with a mask, based on the mode selected. The match uses seven or eight bits, depending on the mode.

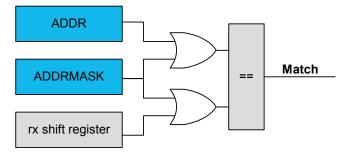

#### Address With Mask

An address written to the Address bits in the Address register (ADDR.ADDR), and a mask written to the Address Mask bits in the Address register (ADDR.ADDRMASK) will yield an address match. All bits that are masked are not included in the match. Note that writing the ADDR.ADDRMASK to 'all zeros' will match a single unique address, while writing ADDR.ADDRMASK to 'all ones' will result in all addresses being accepted.

#### Figure 30-4. Address With Mask

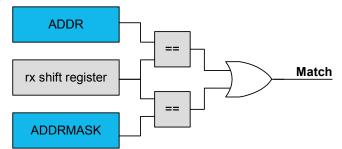

#### **Two Unique Addresses**

The two addresses written to ADDR and ADDRMASK will cause a match.

#### Figure 30-5. Two Unique Addresses

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

#### Bit 0 – DRE: Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Register Empty Interrupt Enable bit, which enables the Data Register Empty interrupt.

| V | alue | Description                                |

|---|------|--------------------------------------------|

| 0 |      | Data Register Empty interrupt is disabled. |

| 1 |      | Data Register Empty interrupt is enabled.  |

#### 32.8.6 Interrupt Flag Status and Clear

Name:

INTFLAG

Offset:

0x18 [ID-00000e74]

Reset:

0x00

Property:

| Bit    | 7     | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|-------|---|---|---|-----|-----|-----|-----|

| Γ      | ERROR |   |   |   | SSL | RXC | TXC | DRE |

| Access | R/W   |   |   |   | R/W | R   | R/W | R   |

| Reset  | 0     |   |   |   | 0   | 0   | 0   | 0   |

#### Bit 7 - ERROR: Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status flags in the STATUS register. The BUFOVF error will set this interrupt flag.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 3 – SSL: Slave Select Low

This flag is cleared by writing '1' to it.

This bit is set when a high to low transition is detected on the \_SS pin in slave mode and Slave Select Low Detect (CTRLB.SSDE) is enabled.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 2 – RXC: Receive Complete

This flag is cleared by reading the Data (DATA) register or by disabling the receiver.

This flag is set when there are unread data in the receive buffer. If address matching is enabled, the first data received in a transaction will be an address.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

#### Table 33-4. Command Description

| CMD[1:0] | Direction | Action                                                           |  |

|----------|-----------|------------------------------------------------------------------|--|

| 0x0      | Х         | (No action)                                                      |  |

| 0x1      | Х         | execute acknowledge action succeeded by repeated Start           |  |

| 0x2      | 0 (Write) | No operation                                                     |  |

|          | 1 (Read)  | Execute acknowledge action succeeded by a byte read operation    |  |

| 0x3      | Х         | Execute acknowledge action succeeded by issuing a stop condition |  |

These bits are not enable-protected.

#### Bit 9 – QCEN: Quick Command Enable

This bit is not write-synchronized.

| Value | Description                |

|-------|----------------------------|

| 0     | Quick Command is disabled. |

| 1     | Quick Command is enabled.  |

#### Bit 8 – SMEN: Smart Mode Enable

When smart mode is enabled, acknowledge action is sent when DATA.DATA is read.

This bit is not write-synchronized.

| Value | Description             |

|-------|-------------------------|

| 0     | Smart mode is disabled. |

| 1     | Smart mode is enabled.  |

### 33.10.3 Baud Rate

Name:BAUDOffset:0x0C [ID-00001bb3]Reset:0x0000Property:PAC Write-Protection, Enable-Protected

Writing '1' to this bit location will clear this bit. This flag is automatically cleared when writing to the ADDR register.

Writing '0' to this bit has no effect.

This bit is not write-synchronized.

#### Bits 5:4 – BUSSTATE[1:0]: Bus State

These bits indicate the current I<sup>2</sup>C bus state.

When in UNKNOWN state, writing 0x1 to BUSSTATE forces the bus state into the IDLE state. The bus state cannot be forced into any other state.

Writing BUSSTATE to idle will set SYNCBUSY.SYSOP.

| Value | Name    | Description                                                                                   |

|-------|---------|-----------------------------------------------------------------------------------------------|

| 0x0   | UNKNOWN | The bus state is unknown to the I <sup>2</sup> C master and will wait for a stop condition to |

|       |         | be detected or wait to be forced into an idle state by software                               |

| 0x1   | IDLE    | The bus state is waiting for a transaction to be initialized                                  |

| 0x2   | OWNER   | The I <sup>2</sup> C master is the current owner of the bus                                   |

| 0x3   | BUSY    | Some other I <sup>2</sup> C master owns the bus                                               |

#### Bit 2 – RXNACK: Received Not Acknowledge

This bit indicates whether the last address or data packet sent was acknowledged or not.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

This bit is not write-synchronized.

| Value | Description                |

|-------|----------------------------|

| 0     | Slave responded with ACK.  |

| 1     | Slave responded with NACK. |

#### **Bit 1 – ARBLOST:** Arbitration Lost

This bit is set if arbitration is lost while transmitting a high data bit or a NACK bit, or while issuing a start or repeated start condition on the bus. The Master on Bus interrupt flag (INTFLAG.MB) will be set when STATUS.ARBLOST is set.

Writing the ADDR.ADDR register will automatically clear STATUS.ARBLOST.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

This bit is not write-synchronized.

#### Bit 0 – BUSERR: Bus Error

This bit indicates that an illegal bus condition has occurred on the bus, regardless of bus ownership. An illegal bus condition is detected if a protocol violating start, repeated start or stop is detected on the I<sup>2</sup>C bus lines. A start condition directly followed by a stop condition is one example of a protocol violation. If a time-out occurs during a frame, this is also considered a protocol violation, and will set BUSERR.

If the I<sup>2</sup>C master is the bus owner at the time a bus error occurs, STATUS.ARBLOST and INTFLAG.MB will be set in addition to BUSERR.

Writing the ADDR.ADDR register will automatically clear the BUSERR flag.

#### 34.6.4 Timeout Counter

To signal timeout conditions for Rx FIFO 0, Rx FIFO 1, and the Tx Event FIFO the CAN supplies a 16-bit Timeout Counter. It operates as down-counter and uses the same prescaler controlled by TSCC.TCP as the Timestamp Counter. The Timeout Counter is configured via register TOCC. The actual counter value can be read from TOCV.TOC. The Timeout Counter can only be started while CCCR.INIT = '0'. It is stopped when CCCR.INIT = '1', e.g. when the CAN enters Bus\_Off state.

The operation mode is selected by TOCC.TOS. When operating in Continuous Mode, the counter starts when CCCR.INIT is reset. A write to TOCV presets the counter to the value configured by TOCC.TOP and continues down-counting.

When the Timeout Counter is controlled by one of the FIFOs, an empty FIFO presets the counter to the value configured by TOCC.TOP. Down-counting is started when the first FIFO element is stored. Writing to TOCV has no effect.

When the counter reaches zero, interrupt flag IR.TOO is set. In Continuous Mode, the counter is immediately restarted at TOCC.TOP.

Note: The clock signal for the Timeout Counter is derived from the CAN Core's sample point signal. Therefore the point in time where the Timeout Counter is decremented may vary due to the synchronization / re-synchronization mechanism of the CAN Core. If the baud rate switch feature in CAN FD is used, the timeout counter is clocked differently in arbitration and data field.

#### 34.6.5 Rx Handling

The Rx Handler controls the acceptance filtering, the transfer of received messages to the Rx Buffers or to one of the two Rx FIFOs, as well as the Rx FIFO's Put and Get Indices.

#### 34.6.5.1 Acceptance Filtering

The CAN offers the possibility to configure two sets of acceptance filters, one for standard identifiers and one for extended identifiers. These filters can be assigned to an Rx Buffer or to Rx FIFO 0,1. For acceptance filtering each list of filters is executed from element #0 until the first matching element. Acceptance filtering stops at the first matching element. The following filter elements are not evaluated for this message.

The main features are:

- Each filter element can be configured as

- range filter (from to)

- filter for one or two dedicated IDs

- classic bit mask filter

- Each filter element is configurable for acceptance or rejection filtering

- · Each filter element can be enabled / disabled individually

- Filters are checked sequentially, execution stops with the first matching filter element

Related configuration registers are:

- Global Filter Configuration GFC

- Standard ID Filter Configuration SIDFC

- Extended ID Filter Configuration XIDFC

- Extended ID AND Mask XIDAM

Depending on the configuration of the filter element (SFEC/EFEC) a match triggers one of the following actions:

• Store received frame in FIFO 0 or FIFO 1

#### 35.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 35.5.6 Events

The events of this peripheral are connected to the Event System.

#### **Related Links**

EVSYS – Event System

#### 35.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will halt normal operation. This peripheral can be forced to continue operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### **Related Links**

DBGCTRL

#### 35.5.8 Register Access Protection

Registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC), except for the following:

- Interrupt Flag Status and Clear register (INTFLAG)

- Status register (STATUS)

- Count register (COUNT)

- Period and Period Buffer registers (PER, PERBUF)

- Compare/Capture Value registers and Compare/Capture Value Buffer registers (CCx, CCBUFx)

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### 35.5.9 Analog Connections

Not applicable.

### 35.6 Functional Description

#### 35.6.1 Principle of Operation

The following definitions are used throughout the documentation:

#### Table 35-2. Timer/Counter Definitions

| Name | Description                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| ТОР  | The counter reaches TOP when it becomes equal to the highest value in the count sequence. The TOP value can be the same as Period (PER) |

These bits are not synchronized.

| Value | Name   | Description                                                                    |

|-------|--------|--------------------------------------------------------------------------------|

| 0x0   | GCLK   | Reload or reset the counter on next generic clock                              |

| 0x1   | PRESC  | Reload or reset the counter on next prescaler clock                            |

| 0x2   | RESYNC | Reload or reset the counter on next generic clock. Reset the prescaler counter |

| 0x3   | -      | Reserved                                                                       |

#### Bits 3:2 – MODE[1:0]: Timer Counter Mode

These bits select the counter mode.

These bits are not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT16 | Counter in 16-bit mode |

| 0x1   | COUNT8  | Counter in 8-bit mode  |

| 0x2   | COUNT32 | Counter in 32-bit mode |

| 0x3   | -       | Reserved               |

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately, and the ENABLE Synchronization Busy bit in the SYNCBUSY register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

This bit is not enable protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the TC, except DBGCTRL, to their initial state, and the TC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence; all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

This bit is not enable protected.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 35.7.1.2 Control B Clear

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

| Name    | Description                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TOP     | The counter reaches TOP when it becomes equal to the highest value in the count sequence. The TOP value can be the same as Period (PER) or the Compare Channel 0 (CC0) register value depending on the waveform generator mode in Waveform Output Generation Operations. |

| ZERO    | The counter reaches ZERO when it contains all zeroes.                                                                                                                                                                                                                    |

| MAX     | The counter reaches maximum when it contains all ones.                                                                                                                                                                                                                   |

| UPDATE  | The timer/counter signals an update when it reaches ZERO or TOP, depending on the direction settings.                                                                                                                                                                    |

| Timer   | The timer/counter clock control is handled by an internal source.                                                                                                                                                                                                        |

| Counter | The clock control is handled externally (e.g., counting external events).                                                                                                                                                                                                |

| CC      | For compare operations, the CC are referred to as "compare channels."<br>For capture operations, the CC are referred to as "capture channels."                                                                                                                           |

Each TCC instance has up to four compare/capture channels (CCx).

The counter register (COUNT), period registers with buffer (PER and PERBUF), and compare and capture registers with buffers (CCx and CCBUFx) are 16- or 24-bit registers, depending on each TCC instance. Each buffer register has a buffer valid (BUFV) flag that indicates when the buffer contains a new value.

Under normal operation, the counter value is continuously compared to the TOP or ZERO value to determine whether the counter has reached TOP or ZERO. In either case, the TCC can generate interrupt requests, request DMA transactions, or generate events for the Event System. In waveform generator mode, these comparisons are used to set the waveform period or pulse width.

A prescaled generic clock (GCLK\_TCCx) and events from the event system can be used to control the counter. The event system is also used as a source to the input capture.

The Recoverable Fault Unit enables event controlled waveforms by acting directly on the generated waveforms of the TCC compare channels output. These events can restart, halt the timer/counter period, shorten the output pulse active time, or disable waveform output as long as the fault condition is present. This can typically be used for current sensing regulation, and zero-crossing and demagnetization re-triggering.

The MCE0 and MCE1 asynchronous event sources are shared with the Recoverable Fault Unit. Only asynchronous events are used internally when fault unit extension is enabled. For further details on how to configure asynchronous events routing, refer to *EVSYS – Event System*.

Recoverable fault sources can be filtered and/or windowed to avoid false triggering, for example from I/O pin glitches, by using digital filtering, input blanking, and qualification options. See also Recoverable Faults.

In order to support applications with different types of motor control, ballast, LED, H-bridge, power converter, and other types of power switching applications, the following independent units are implemented in some of the TCC instances as optional and successive units:

- Recoverable faults and non-recoverable faults

- Output matrix

The Channel x Compare/Capture Buffer Value (CCBUFx) registers provide double buffer capability. The double buffering synchronizes the update of the CCx register with the buffer value at the UPDATE condition or a force update command (CTRLBSET.CMD=0x3, UPDATE). For further details, refer to Double Buffering. The synchronization prevents the occurrence of odd-length, non-symmetrical pulses and ensures glitch-free output.

#### Waveform Output Generation Operations

The compare channels can be used for waveform generation on output port pins. To make the waveform available on the connected pin, the following requirements must be fulfilled:

- 1. Choose a waveform generation mode in the Waveform Generation Operation bit in Waveform register (WAVE.WAVEGEN).

- 2. Optionally invert the waveform output WO[x] by writing the corresponding Waveform Output x Inversion bit in the Driver Control register (DRVCTRL.INVENx).

- 3. Configure the pins with the I/O Pin Controller. Refer to PORT I/O Pin Controller for details.

The counter value is continuously compared with each CCx value. On a comparison match, the Match or Capture Channel x bit in the Interrupt Flag Status and Clear register (INTFLAG.MCx) will be set on the next zero-to-one transition of CLK\_TCC\_COUNT (see Normal Frequency Operation). An interrupt and/or event can be generated on the same condition if Match/Capture occurs, i.e. INTENSET.MCx and/or EVCTRL.MCEOx is '1'. Both interrupt and event can be generated simultaneously. The same condition generates a DMA request.

There are seven waveform configurations for the Waveform Generation Operation bit group in the Waveform register (WAVE.WAVEGEN). This will influence how the waveform is generated and impose restrictions on the top value. The configurations are:

- Normal Frequency (NFRQ)

- Match Frequency (MFRQ)

- Normal Pulse-Width Modulation (NPWM)

- Dual-slope, interrupt/event at TOP (DSTOP)

- Dual-slope, interrupt/event at ZERO (DSBOTTOM)

- Dual-slope, interrupt/event at Top and ZERO (DSBOTH)

- Dual-slope, critical interrupt/event at ZERO (DSCRITICAL)

When using MFRQ configuration, the TOP value is defined by the CC0 register value. For the other waveform operations, the TOP value is defined by the Period (PER) register value.

For dual-slope waveform operations, the update time occurs when the counter reaches ZERO. For the other waveforms generation modes, the update time occurs on counter wraparound, on overflow, underflow, or re-trigger.

The table below shows the update counter and overflow event/interrupt generation conditions in different operation modes.

| Name | Operation           | ТОР | Update       | Output Wav | eform     | OVFIF/Ev | ent  |

|------|---------------------|-----|--------------|------------|-----------|----------|------|

|      |                     |     |              | On Match   | On Update | Up       | Down |

| NFRQ | Normal<br>Frequency | PER | TOP/<br>ZERO | Toggle     | Stable    | ТОР      | ZERO |

| MFRQ | Match<br>Frequency  | CC0 | TOP/<br>ZERO | Toggle     | Stable    | TOP      | ZERO |

#### Table 36-2. Counter Update and Overflow Event/interrupt Conditions

## 37.6 Functional Description

#### 37.6.1 Principle of Operation

Configurable Custom Logic (CCL) is a programmable logic block that can use the device port pins, internal peripherals, and the internal Event System as both input and output channels. The CCL can serve as glue logic between the device and external devices. The CCL can eliminate the need for external logic component and can also help the designer overcome challenging real-time constrains by combining core independent peripherals in clever ways to handle the most time critical parts of the application independent of the CPU.

#### 37.6.2 Operation

#### 37.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the corresponding even LUT is disabled (LUTCTRLx.ENABLE=0):

• Sequential Selection bits in the Sequential Control x (SEQCTRLx.SEQSEL) register

The following registers are enable-protected, meaning that they can only be written when the corresponding LUT is disabled (LUTCTRLx.ENABLE=0):

• LUT Control x (LUTCTRLx) register, except the ENABLE bit

Enable-protected bits in the LUTCTRLx registers can be written at the same time as LUTCTRLx.ENABLE is written to '1', but not at the same time as LUTCTRLx.ENABLE is written to '0'.

Enable-protection is denoted by the Enable-Protected property in the register description.

#### 37.6.2.2 Enabling, Disabling, and Resetting

The CCL is enabled by writing a '1' to the Enable bit in the Control register (CTRL.ENABLE). The CCL is disabled by writing a '0' to CTRL.ENABLE.

Each LUT is enabled by writing a '1' to the Enable bit in the LUT Control x register (LUTCTRLx.ENABLE). Each LUT is disabled by writing a '0' to LUTCTRLx.ENABLE.

The CCL is reset by writing a '1' to the Software Reset bit in the Control register (CTRL.SWRST). All registers in the CCL will be reset to their initial state, and the CCL will be disabled. Refer to CTRL for details.

#### 37.6.2.3 Lookup Table Logic

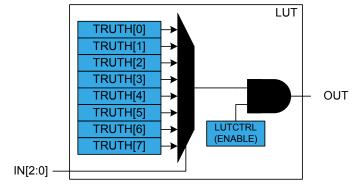

The lookup table in each LUT unit can generate any logic expression OUT as a function of three inputs (IN[2:0]), as shown in Figure 37-2. One or more inputs can be masked. The truth table for the expression is defined by TRUTH bits in LUT Control x register (LUTCTRLx.TRUTH).

#### Figure 37-2. Truth Table Output Value Selection

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 40.8.1 Control A

Name:CTRLAOffset:0x00 [ID-00000fbb]Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access |   |   |   |   |   |   | R/W    | W     |

| Reset  |   |   |   |   |   |   | 0      | 0     |

#### Bit 1 – ENABLE: Enable

Due to synchronization, there is delay from updating the register until the peripheral is enabled/disabled. The value written to CTRL.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE is cleared when the peripheral is enabled/disabled.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The AC is disabled.                                                                       |

| 1     | The AC is enabled. Each comparator must also be enabled individually by the Enable bit in |

|       | the Comparator Control register (COMPCTRLn.ENABLE).                                       |

#### Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the AC to their initial state, and the AC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization, there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 40.8.2 Control B

| Value   | Name | Description                      |

|---------|------|----------------------------------|

| 0x0     | OFF  | No filtering                     |

| 0x1     | MAJ3 | 3-bit majority function (2 of 3) |

| 0x2     | MAJ5 | 5-bit majority function (3 of 5) |

| 0x3-0x7 | N/A  | Reserved                         |

#### Bit 19 – HYSTEN: Hysteresis Enable

This bit indicates the hysteresis mode of comparator n. Hysteresis is available only for continuous mode (COMPCTRLn.SINGLE=0).

This bit is not synchronized.

| Value | Description             |

|-------|-------------------------|

| 0     | Hysteresis is disabled. |

| 1     | Hysteresis is enabled.  |

#### Bits 17:16 – SPEED[1:0]: Speed Selection

This bit indicates the speed/propagation delay mode of comparator n. COMPCTRLn.SPEED can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | LOW  | Low speed   |

| 0x3   | HIGH | High speed  |

#### Bit 15 – SWAP: Swap Inputs and Invert

This bit swaps the positive and negative inputs to COMPn and inverts the output. This function can be used for offset cancellation. COMPCTRLn.SWAP can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The output of MUXPOS connects to the positive input, and the output of MUXNEG connects |

|       | to the negative input.                                                                 |

| 1     | The output of MUXNEG connects to the positive input, and the output of MUXPOS connects |

|       | to the negative input.                                                                 |

#### Bits 14:12 – MUXPOS[2:0]: Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value   | Name   | Description |

|---------|--------|-------------|

| 0x0     | PIN0   | I/O pin 0   |

| 0x1     | PIN1   | I/O pin 1   |

| 0x2     | PIN2   | I/O pin 2   |

| 0x3     | PIN3   | I/O pin 3   |

| 0x4     | VSCALE | VDD scaler  |

| 0x5–0x7 |        | Reserved    |