## E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e17a-mnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The Quality of Service (QoS) level is independently selected for each master accessing the RAM. For any access to the RAM the RAM also receives the QoS level. The QoS levels and their corresponding bit values for the QoS level configuration is shown in below.

| Value | Name    | Description                         |

|-------|---------|-------------------------------------|

| 0x0   | DISABLE | Background (no sensitive operation) |

| 0x1   | LOW     | Sensitive Bandwidth                 |

| 0x2   | MEDIUM  | Sensitive Latency                   |

| 0x3   | HIGH    | Critical Latency                    |

| Table 10-8. | Quality of Service | Level Configuration |

|-------------|--------------------|---------------------|

|-------------|--------------------|---------------------|

If a master is configured with QoS level DISABLE (0x0) or LOW (0x1) there will be minimum latency of one cycle for the RAM access.

The priority order for concurrent accesses are decided by two factors. First, the QoS level for the master and second, a static priority given by Table 10-7. The lowest port ID has the highest static priority.

The MTB has fixed QoS level HIGH (0x3) and the DSU has fixed QoS level LOW (0x1).

The CPU QoS level can be written/read at address 0x41007110, bits [1:0]. Its reset value is 0x0.

Refer to different master QOSCTRL registers for configuring QoS for the other masters (for SAM C21: CAN, DMAC; for SAM C20: DMAC).

| Bit    | 31          | 30     | 29       | 28 | 27    | 26          | 25      | 24 |

|--------|-------------|--------|----------|----|-------|-------------|---------|----|

|        |             | PROCES | SOR[3:0] |    |       | FAMILY[4:1] |         |    |

| Access | R           | R      | R        | R  | R     | R           | R       | R  |

| Reset  | р           | р      | р        | р  | f     | f           | f       | f  |

|        |             |        |          |    |       |             |         |    |

| Bit    | 23          | 22     | 21       | 20 | 19    | 18          | 17      | 16 |

|        | FAMILY[0:0] |        |          |    | SERIE | ES[5:0]     |         |    |

| Access | R           |        | R        | R  | R     | R           | R       | R  |

| Reset  | f           |        | S        | S  | S     | s           | S       | s  |

|        |             |        |          |    |       |             |         |    |

| Bit    | 15          | 14     | 13       | 12 | 11    | 10          | 9       | 8  |

|        |             | DIE    | [3:0]    |    |       | REVISI      | ON[3:0] |    |

| Access | R           | R      | R        | R  | R     | R           | R       | R  |

| Reset  | d           | d      | d        | d  | r     | r           | r       | r  |

|        |             |        |          |    |       |             |         |    |

| Bit    | 7           | 6      | 5        | 4  | 3     | 2           | 1       | 0  |

|        | DEVSEL[7:0] |        |          |    |       |             |         |    |

| Access | R           | R      | R        | R  | R     | R           | R       | R  |

| Reset  | x           | x      | x        | x  | х     | x           | х       | x  |

#### Bits 31:28 – PROCESSOR[3:0]: Processor

The value of this field defines the processor used on the device.

#### Bits 27:23 – FAMILY[4:0]: Product Family

The value of this field corresponds to the product family part of the ordering code.

#### Bits 21:16 – SERIES[5:0]: Product Series

The value of this field corresponds to the product series part of the ordering code.

#### Bits 15:12 – DIE[3:0]: Die Number

Identifies the die family.

#### Bits 11:8 - REVISION[3:0]: Revision Number

Identifies the die revision number. 0x0=rev.A, 0x1=rev.B etc.

**Note:** The device variant (last letter of the ordering number) is independent of the die revision (DSU.DID.REVISION): The device variant denotes functional differences, whereas the die revision marks evolution of the die.

#### Bits 7:0 – DEVSEL[7:0]: Device Selection

This bit field identifies a device within a product family and product series. Refer to the ordering information for device configurations and corresponding values for Flash memory density, pin count, and device variant.

#### 13.13.10 CoreSight ROM Table Entry 0

Name:ENTRY0Offset:0x1000 [ID-00001c14]Reset:0xXXXXX00XProperty:PAC Write-Protection

## SAM C20/C21

| Bit    | 31 | 30 | 29 | 28 | 27 | 26      | 25        | 24         |

|--------|----|----|----|----|----|---------|-----------|------------|

| ſ      |    |    |    |    |    |         |           |            |

| Access |    |    |    |    |    |         |           |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18      | 17        | 16         |

|        |    |    |    |    |    |         |           |            |

| Access |    | •  |    |    |    |         | •         |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10      | 9         | 8          |

|        |    |    |    |    |    |         |           |            |

| Access |    | •  |    |    |    |         | •         |            |

| Reset  |    |    |    |    |    |         |           |            |

|        |    |    |    |    |    |         |           |            |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2       | 1         | 0          |

| ſ      |    |    |    |    |    | CLKFAIL | OSC32KRDY | XOSC32KRDY |

| Access |    |    |    |    |    | R/W     | R/W       | R/W        |

| Reset  |    |    |    |    |    | 0       | 0         | 0          |

#### Bit 2 – CLKFAIL: XOSC32K Clock Failure Detection

This flag is cleared by writing a '1' to it.

This flag is set on a zero-to-one transition of the XOSC32K Clock Failure Detection bit in the Status register (STATUS.CLKFAIL) and will generate an interrupt request if INTENSET.CLKFAIL is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Clock Failure Detection flag.

#### Bit 1 – OSC32KRDY: OSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the OSC32K Ready bit in the Status register (STATUS.OSC32KRDY), and will generate an interrupt request if INTENSET.OSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the OSC32K Ready interrupt flag.

#### Bit 0 – XOSC32KRDY: XOSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the XOSC32K Ready bit in the Status register (STATUS.XOSC32KRDY), and will generate an interrupt request if INTENSET.XOSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the XOSC32K Ready interrupt flag.

#### 21.8.4 Status

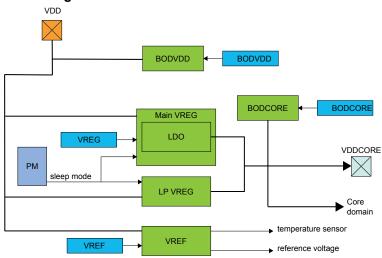

#### 22.3 Block Diagram

Figure 22-1. SUPC Block Diagram

#### 22.4 Signal Description

Not appclicable.

#### **Related Links**

I/O Multiplexing and Considerations

#### 22.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 22.5.1 I/O Lines

Not applicable.

#### 22.5.2 Power Management

The SUPC can operate in all sleep modes.

**Related Links**

PM - Power Manager

#### 22.5.3 Clocks

The SUPC bus clock (CLK\_SUPC\_APB) can be enabled and disabled in the Main Clock module.

A 32KHz clock, asynchronous to the user interface clock (CLK\_SUPC\_APB), is required to run BODVDD and BODCORE in sampled mode. Due to this asynchronicity, writing to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

#### **Related Links**

OSC32KCTRL – 32KHz Oscillators Controller Peripheral Clock Masking

#### 22.5.4 DMA

Not applicable.

# Name:COUNTOffset:0x18Reset:0x0000Property:PAC Write-Protection, Write-Synchronized, Read-Synchronized

| Bit    | 15          | 14  | 13  | 12  | 11  | 10  | 9   | 8   |  |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|--|

|        | COUNT[15:8] |     |     |     |     |     |     |     |  |

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

|        |             |     |     |     |     |     |     |     |  |

| Bit    | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|        | COUNT[7:0]  |     |     |     |     |     |     |     |  |

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

#### Bits 15:0 – COUNT[15:0]: Counter Value

These bits define the value of the 16-bit RTC counter in COUNT16 mode (CTRLA.MODE=1).

#### 24.10.10 Counter Period in COUNT16 mode (CTRLA.MODE=1)

Name:PEROffset:0x1CReset:0x0000Property:PAC Write-Protection, Write-Synchronized

| Bit    | 15       | 14  | 13  | 12   | 11     | 10  | 9   | 8   |

|--------|----------|-----|-----|------|--------|-----|-----|-----|

|        |          |     |     | PER[ | [15:8] |     |     |     |

| Access | R/W      | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0        | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

|        |          |     |     |      |        |     |     |     |

| Bit    | 7        | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|        | PER[7:0] |     |     |      |        |     |     |     |

| Access | R/W      | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0        | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 15:0 – PER[15:0]: Counter Period

These bits define the value of the 16-bit RTC period in COUNT16 mode (CTRLA.MODE=1).

#### 24.10.11 Compare n Value in COUNT16 mode (CTRLA.MODE=1)

Name:COMPOffset:0x20 + n\*0x02 [n=0..1]Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

## SAM C20/C21

| CMD[6:0]  | Group<br>Configuration | Description                                                                                                                                                                                                       |

|-----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00-0x01 | -                      | Reserved                                                                                                                                                                                                          |

| 0x02      | ER                     | Erase Row - Erases the row addressed by the ADDR register in the NVM main array.                                                                                                                                  |

| 0x03      | -                      | Reserved                                                                                                                                                                                                          |

| 0x04      | WP                     | Write Page - Writes the contents of the page buffer to the page addressed by the ADDR register.                                                                                                                   |

| 0x05      | EAR                    | Erase Auxiliary Row - Erases the auxiliary row addressed by the ADDR register. This command can be given only when the security bit is not set and only to the User Configuration Row.                            |

| 0x06      | WAP                    | Write Auxiliary Page - Writes the contents of the page buffer to the page addressed by the ADDR register. This command can be given only when the security bit is not set and only to the User Configuration Row. |

| 0x07-0x0E | -                      | Reserved                                                                                                                                                                                                          |

| 0x0F      | WL                     | Write Lockbits- write the LOCK register                                                                                                                                                                           |

| 0x1A-0x19 | -                      | Reserved                                                                                                                                                                                                          |

| 0x1A      | RWWEEER                | RWWEE Erase Row - Erases the row addressed by the ADDR register in the RWWEE array.                                                                                                                               |

| 0x1B      | -                      | Reserved                                                                                                                                                                                                          |

| 0x1C      | RWWEEWP                | RWWEE Write Page - Writes the contents of the page buffer to the page addressed by the ADDR register in the RWWEE array.                                                                                          |

| 0x1D-0x3F | -                      | Reserved                                                                                                                                                                                                          |

| 0x40      | LR                     | Lock Region - Locks the region containing the address location in the ADDR register.                                                                                                                              |

| 0x41      | UR                     | Unlock Region - Unlocks the region containing the address location in the ADDR register.                                                                                                                          |

| 0x42      | SPRM                   | Sets the Power Reduction Mode.                                                                                                                                                                                    |

| 0x43      | CPRM                   | Clears the Power Reduction Mode.                                                                                                                                                                                  |

| 0x44      | PBC                    | Page Buffer Clear - Clears the page buffer.                                                                                                                                                                       |

| 0x45      | SSB                    | Set Security Bit - Sets the security bit by writing 0x00 to the first byte in the lockbit row.                                                                                                                    |

| 0x46      | INVALL                 | Invalidates all cache lines.                                                                                                                                                                                      |

| 0x47      | LDR                    | Lock Data Region - Locks the data region containing the address<br>location in the ADDR register.<br>When the Security Extension is enabled, only secure access can<br>lock secure regions.                       |

| Bit    | 31           | 30   | 29      | 28  | 27      | 26 | 25       | 24 |

|--------|--------------|------|---------|-----|---------|----|----------|----|

|        | RWWEEP[11:4] |      |         |     |         |    |          |    |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |

| Reset  | 0            | 0    | 0       | 0   | 0       | 0  | 0        | 0  |

|        |              |      |         |     |         |    |          |    |

| Bit    | 23           | 22   | 21      | 20  | 19      | 18 | 17       | 16 |

|        |              | RWWE | EP[3:0] |     |         |    | PSZ[2:0] |    |

| Access | R            | R    | R       | R   |         | R  | R        | R  |

| Reset  | 0            | 0    | 0       | 0   |         | x  | x        | x  |

|        |              |      |         |     |         |    |          |    |

| Bit    | 15           | 14   | 13      | 12  | 11      | 10 | 9        | 8  |

|        |              |      |         | NVM | P[15:8] |    |          |    |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |

| Reset  | x            | x    | x       | x   | х       | х  | х        | x  |

|        |              |      |         |     |         |    |          |    |

| Bit    | 7            | 6    | 5       | 4   | 3       | 2  | 1        | 0  |

|        |              |      |         | NVM | P[7:0]  |    |          |    |

| Access | R            | R    | R       | R   | R       | R  | R        | R  |

| Reset  | x            | x    | x       | x   | х       | x  | x        | x  |

#### Bits 31:20 – RWWEEP[11:0]: Read While Write EEPROM emulation area Pages

Indicates the number of pages in the RWW EEPROM emulation address space.

#### Bits 18:16 – PSZ[2:0]: Page Size

Indicates the page size. Not all devices of the device families will provide all the page sizes indicated in the table.

| Value | Name | Description |

|-------|------|-------------|

| 0x0   | 8    | 8 bytes     |

| 0x1   | 16   | 16 bytes    |

| 0x2   | 32   | 32 bytes    |

| 0x3   | 64   | 64 bytes    |

| 0x4   | 128  | 128 bytes   |

| 0x5   | 256  | 256 bytes   |

| 0x6   | 512  | 512 bytes   |

| 0x7   | 1024 | 1024 bytes  |

#### Bits 15:0 – NVMP[15:0]: NVM Pages

Indicates the number of pages in the NVM main address space.

#### 27.8.4 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x0C [ID-0000b2c]Reset:0x00Property:PAC Write-Protection

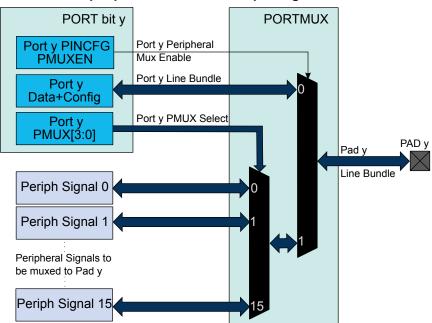

Figure 28-3. Overview of the peripheral functions multiplexing

The I/O pins of the device are controlled by PORT peripheral registers. Each port pin has a corresponding bit in the Data Direction (DIR) and Data Output Value (OUT) registers to enable that pin as an output and to define the output state.

The direction of each pin in a PORT group is configured by the DIR register. If a bit in DIR is set to '1', the corresponding pin is configured as an output pin. If a bit in DIR is set to '0', the corresponding pin is configured as an input pin.

When the direction is set as output, the corresponding bit in the OUT register will set the level of the pin. If bit y in OUT is written to '1', pin y is driven HIGH. If bit y in OUT is written to '0', pin y is driven LOW. Pin configuration can be set by Pin Configuration (PINCFGy) registers, with y=00, 01, ...31 representing the bit position.

The Data Input Value (IN) is set as the input value of a port pin with resynchronization to the PORT clock. To reduce power consumption, these input synchronizers are clocked only when system requires reading the input value. The value of the pin can always be read, whether the pin is configured as input or output. If the Input Enable bit in the Pin Configuration registers (PINCFGy.INEN) is '0', the input value will not be sampled.

In PORT, the Peripheral Multiplexer Enable bit in the PINCFGy register (PINCFGy.PMUXEN) can be written to '1' to enable the connection between peripheral functions and individual I/O pins. The Peripheral Multiplexing n (PMUXn) registers select the peripheral function for the corresponding pin. This will override the connection between the PORT and that I/O pin, and connect the selected peripheral signal to the particular I/O pin instead of the PORT line bundle.

#### 28.6.2 Basic Operation

#### 28.6.2.1 Initialization

After reset, all standard function device I/O pads are connected to the PORT with outputs tri-stated and input buffers disabled, even if there is no clock running.

However, specific pins, such as those used for connection to a debugger, may be configured differently, as required by their special function.

#### 29.4 Signal Description

Not applicable.

#### 29.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 29.5.1 I/O Lines

Not applicable.

#### 29.5.2 Power Management

The EVSYS can be used to wake up the CPU from all sleep modes, even if the clock used by the EVSYS channel and the EVSYS bus clock are disabled. Refer to the *PM* – *Power Manager* for details on the different sleep modes.

Although the clock for the EVSYS is stopped, the device still can wake up the EVSYS clock. Some event generators can generate an event when their clocks are stopped. The generic clock for the channel (GCLK\_EVSYS\_CHANNEL\_n) will be restarted if that channel uses a synchronized path or a resynchronized path. It does not need to wake the system from sleep.

#### **Related Links**

PM – Power Manager

#### 29.5.3 Clocks

The EVSYS bus clock (CLK\_EVSYS\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_EVSYS\_APB can be found in *Peripheral Clock Masking*.

Each EVSYS channel has a dedicated generic clock (GCLK\_EVSYS\_CHANNEL\_n). These are used for event detection and propagation for each channel. These clocks must be configured and enabled in the generic clock controller before using the EVSYS. Refer to *GCLK* - *Generic Clock Controller* for details.

#### **Related Links**

Peripheral Clock Masking GCLK - Generic Clock Controller

#### 29.5.4 DMA

Not applicable.

#### 29.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the EVSYS interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 29.5.6 Events

Not applicable.

#### 29.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or

| RXPO[1:0] | Name   | Description                              |

|-----------|--------|------------------------------------------|

| 0x0       | PAD[0] | SERCOM PAD[0] is used for data reception |

| 0x1       | PAD[1] | SERCOM PAD[1] is used for data reception |

| 0x2       | PAD[2] | SERCOM PAD[2] is used for data reception |

| 0x3       | PAD[3] | SERCOM PAD[3] is used for data reception |

#### Bits 17:16 – TXPO[1:0]: Transmit Data Pinout

These bits define the transmit data (TxD) and XCK pin configurations.

This bit is not synchronized.

| ТХРО | TxD Pin Location | XCK Pin Location (When<br>Applicable) | RTS/TE        | стѕ           |

|------|------------------|---------------------------------------|---------------|---------------|

| 0x0  | SERCOM PAD[0]    | SERCOM PAD[1]                         | N/A           | N/A           |

| 0x1  | SERCOM PAD[2]    | SERCOM PAD[3]                         | N/A           | N/A           |

| 0x2  | SERCOM PAD[0]    | N/A                                   | SERCOM PAD[2] | SERCOM PAD[3] |

| 0x3  | SERCOM_PAD[0]    | SERCOM_PAD[1]                         | SERCOM_PAD[2] | N/A           |

#### Bits 15:13 – SAMPR[2:0]: Sample Rate

These bits select the sample rate.

These bits are not synchronized.

| SAMPR[2:0] | Description                                              |

|------------|----------------------------------------------------------|

| 0x0        | 16x over-sampling using arithmetic baud rate generation. |

| 0x1        | 16x over-sampling using fractional baud rate generation. |

| 0x2        | 8x over-sampling using arithmetic baud rate generation.  |

| 0x3        | 8x over-sampling using fractional baud rate generation.  |

| 0x4        | 3x over-sampling using arithmetic baud rate generation.  |

| 0x5-0x7    | Reserved                                                 |

#### Bit 8 – IBON: Immediate Buffer Overflow Notification

This bit controls when the buffer overflow status bit (STATUS.BUFOVF) is asserted when a buffer overflow occurs.

| Value | Description                                                  |

|-------|--------------------------------------------------------------|

| 0     | STATUS.BUFOVF is asserted when it occurs in the data stream. |

| 1     | STATUS.BUFOVF is asserted immediately upon buffer overflow.  |

#### Bit 7 – RUNSTDBY: Run In Standby

This bit defines the functionality in standby sleep mode.

This bit is not synchronized.

Name:RXF1SOffset:0xB4 [ID-0000a4bb]Reset:0x00000000Property:Read-only

| Bit    | 31 | 30     | 29 | 28        | 27        | 26     | 25   | 24  |

|--------|----|--------|----|-----------|-----------|--------|------|-----|

|        | DM | S[1:0] |    |           |           |        | RF1L | F1F |

| Access | R  | R      | •  |           |           |        | R    | R   |

| Reset  | 0  | 0      |    |           |           |        | 0    | 0   |

|        |    |        |    |           |           |        |      |     |

| Bit    | 23 | 22     | 21 | 20        | 19        | 18     | 17   | 16  |

|        |    |        |    |           | F1P       | I[5:0] |      |     |

| Access |    |        | R  | R         | R         | R      | R    | R   |

| Reset  |    |        | 0  | 0         | 0         | 0      | 0    | 0   |

|        |    |        |    |           |           |        |      |     |

| Bit    | 15 | 14     | 13 | 12        | 11        | 10     | 9    | 8   |

|        |    |        |    | F1GI[5:0] |           |        |      |     |

| Access |    |        | R  | R         | R         | R      | R    | R   |

| Reset  |    |        | 0  | 0         | 0         | 0      | 0    | 0   |

|        |    |        |    |           |           |        |      |     |

| Bit    | 7  | 6      | 5  | 4         | 3         | 2      | 1    | 0   |

|        |    |        |    |           | F1FL[6:0] |        |      |     |

| Access |    | R      | R  | R         | R         | R      | R    | R   |

| Reset  |    | 0      | 0  | 0         | 0         | 0      | 0    | 0   |

#### Bits 31:30 – DMS[1:0]: Debug Message Status

This field defines the debug message status.

| Value | Name | Description                                                               |

|-------|------|---------------------------------------------------------------------------|

| 0x0   | IDLE | Idle state, wait for reception of debug messages, DMA request is cleared. |

| 0x1   | DBGA | Debug message A received.                                                 |

| 0x2   | DBGB | Debug message A, B received.                                              |

| 0x3   | DBGC | Debug message A, B, C received, DMA request is set.                       |

#### Bit 25 – RF1L: Rx FIFO 1 Message Lost

This bit is a copy of interrupt flag IR.RF1L. When IR.RF1L is reset, this bit is also reset.

Overwriting the oldest message when RXF1C.F0OM = '1' will not set this flag.

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | No Rx FIFO 1 message lost.                                                      |

| 1     | Rx FIFO 1 message lost, also set after write attempt to Rx FIFO 1 of size zero. |

#### Bit 24 – F1F: Rx FIFO 1 Full

| Value | Description         |

|-------|---------------------|

| 0     | Rx FIFO 1 not full. |

| 1     | Rx FIFO 1 full.     |

#### Bits 21:16 – F1PI[5:0]: Rx FIFO 1 Put Index

Rx FIFO 1 write index pointer, range 0 to 63.

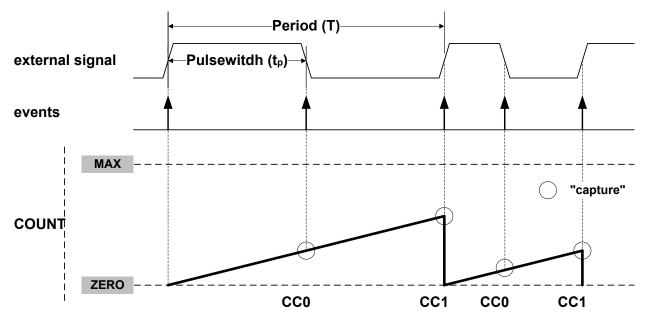

Figure 35-13. PWP Capture

Selecting PWP in the Event Action bit group in the Event Control register (EVCTRL.EVACT) enables the TC to perform one capture action on the rising edge and the other one on the falling edge. The period T will be captured into CC1 and the pulse width  $t_p$  in CC0. EVCTRL.EVACT=PPW (period and pulse-width) offers identical functionality, but will capture T into CC0 and  $t_p$  into CC1.

The TC Event Input Invert Enable bit in the Event Control register (EVCTRL.TCINV) is used to select whether the wraparound should occur on the rising edge or the falling edge. If EVCTRL.TCINV=1, the wraparound will happen on the falling edge. In case pin capture is enabled, this can also be achieved by modifying the value of the DRVCTRL.INVENx bit.

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

**Note:** The corresponding capture is working only if the channel is enabled in capture mode (CTRLA.CAPTENx=1). If not, the capture action is ignored and the channel is enabled in compare mode of operation. Consequently, both channels must be enabled in order to fully characterize the input.

#### Pulse-Width Capture Action

The TC performs the input capture on the falling edge of the input signal. When the edge is detected, the counter value is cleared and the TC stops counting. When a rising edge is detected on the input signal, the counter restarts the counting operation. To enable the operation on opposite edges, the input signal to capture must be inverted (refer to DRVCTRL.INVEN or EVCTRL.TCEINV).

#### Bit 8 – OVFEO: Overflow/Underflow Event Output Enable

This bit enables the Overflow/Underflow event. When enabled, an event will be generated when the counter overflows/underflows.

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| 0     | Overflow/Underflow event is disabled and will not be generated.                                     |

| 1     | Overflow/Underflow event is enabled and will be generated for every counter overflow/<br>underflow. |

#### Bit 5 – TCEI: TC Event Enable

This bit is used to enable asynchronous input events to the TC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

#### Bit 4 – TCINV: TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| Value | Description                         |  |  |

|-------|-------------------------------------|--|--|

| 0     | Input event source is not inverted. |  |  |

| 1     | Input event source is inverted.     |  |  |

#### Bits 2:0 – EVACT[2:0]: Event Action

These bits define the event action the TC will perform on an event.

| Value | Name      | Description                                |

|-------|-----------|--------------------------------------------|

| 0x0   | OFF       | Event action disabled                      |

| 0x1   | RETRIGGER | Start, restart or retrigger TC on event    |

| 0x2   | COUNT     | Count on event                             |

| 0x3   | START     | Start TC on event                          |

| 0x4   | STAMP     | Time stamp capture                         |

| 0x5   | PPW       | Period captured in CC0, pulse width in CC1 |

| 0x6   | PWP       | Period captured in CC1, pulse width in CC0 |

| 0x7   | PW        | Pulse width capture                        |

#### 35.7.2.5 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

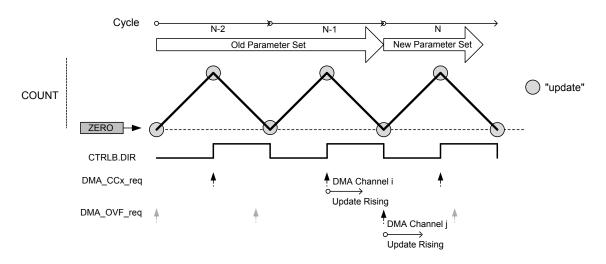

#### Figure 36-38. DMA Triggers in DSBOTH Operation Mode and Circular Buffer Enabled

#### 36.6.5.2 Interrupts

The TCC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Retrigger (TRG)

- Count (CNT) refer also to description of EVCTRL.CNTSEL.

- Capture Overflow Error (ERR)

- Non-Recoverable Update Fault (UFS)

- Debug Fault State (DFS)

- Recoverable Faults (FAULTn)

- Non-recoverable Faults (FAULTx)

- Compare Match or Capture Channels (MCx)

These interrupts are asynchronous wake-up sources. See Sleep Mode Entry and Exit Table in PM/Sleep Mode Controller section for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TCC is reset. See INTFLAG for details on how to clear interrupt flags. The TCC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller Sleep Mode Controller

#### 36.6.5.3 Events

The TCC can generate the following output events:

#### 38.6.2.13 Window Monitor

The window monitor feature allows the conversion result in the RESULT register to be compared to predefined threshold values. The window mode is selected by setting the Window Monitor Mode bits in the Control C register (CTRLC.WINMODE). Threshold values must be written in the Window Monitor Lower Threshold register (WINLT) and Window Monitor Upper Threshold register (WINUT).

If differential input is selected, the WINLT and WINUT are evaluated as signed values. Otherwise they are evaluated as unsigned values. The significant WINLT and WINUT bits are given by the precision selected in the Conversion Result Resolution bit group in the Control C register (CTRLC.RESSEL). This means that for example in 8-bit mode, only the eight lower bits will be considered. In addition, in differential mode, the eight bit will be considered as the sign bit, even if the ninth bit is zero.

The INTFLAG.WINMON interrupt flag will be set if the conversion result matches the window monitor condition.

#### 38.6.2.14 Offset and Gain Correction

Inherent gain and offset errors affect the absolute accuracy of the ADC.

The offset error is defined as the deviation of the actual ADC transfer function from an ideal straight line at zero input voltage. The offset error cancellation is handled by the Offset Correction register (OFFSETCORR). The offset correction value is subtracted from the converted data before writing the Result register (RESULT).

The gain error is defined as the deviation of the last output step's midpoint from the ideal straight line, after compensating for offset error. The gain error cancellation is handled by the Gain Correction register (GAINCORR).

To correct these two errors, the Digital Correction Logic Enabled bit in the Control C register (CTRLC.CORREN) must be set.

Offset and gain error compensation results are both calculated according to:

Result = (Conversion value+ - OFFSETCORR)  $\cdot$  GAINCORR

The correction will introduce a latency of 13 CLK\_ADC clock cycles. In free running mode this latency is introduced on the first conversion only, since its duration is always less than the propagation delay. In single conversion mode this latency is introduced for each conversion.

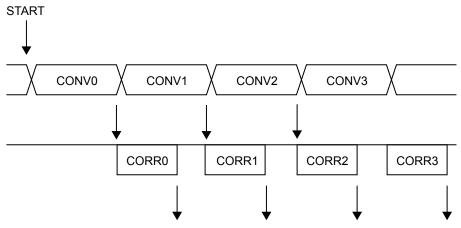

#### Figure 38-8. ADC Timing Correction Enabled

## SAM C20/C21

| Bit    | 31         | 30    | 29    | 28      | 27      | 26     | 25        | 24       |

|--------|------------|-------|-------|---------|---------|--------|-----------|----------|

|        |            |       |       |         |         |        |           |          |

| Access |            |       |       |         |         |        |           |          |

| Reset  |            |       |       |         |         |        |           |          |

|        |            |       |       |         |         |        |           |          |

| Bit    | 23         | 22    | 21    | 20      | 19      | 18     | 17        | 16       |

|        |            |       |       |         |         |        |           |          |

| Access |            |       | •     |         |         |        |           |          |

| Reset  |            |       |       |         |         |        |           |          |

|        |            |       |       |         |         |        |           |          |

| Bit    | 15         | 14    | 13    | 12      | 11      | 10     | 9         | 8        |

|        |            |       |       |         | ANACTRL | SWTRIG | SHIFTCORR | GAINCORR |

| Access |            |       |       |         | R       | R      | R         | R        |

| Reset  |            |       |       |         | 0       | 0      | 0         | 0        |

|        |            |       |       |         |         |        |           |          |

| Bit    | 7          | 6     | 5     | 4       | 3       | 2      | 1         | 0        |

|        | OFFSETCORR | WINUT | WINLT | WINCTRL | MUXCTRL | CTRLC  | ENABLE    | SWRST    |

| Access | R          | R     | R     | R       | R       | R      | R         | R        |

| Reset  | 0          | 0     | 0     | 0       | 0       | 0      | 0         | 0        |

#### Bit 11 – ANACTRL: Analog Control Synchronization Busy

This bit is cleared when the synchronization of ANACTRL register between the clock domains is complete.

This bit is set when the synchronization of ANACTRL register between clock domains is started.

#### Bit 10 – SWTRIG: Software Trigger Synchronization Busy

This bit is cleared when the synchronization of SWTRIG register between the clock domains is complete.

This bit is set when the synchronization of SWTRIG register between clock domains is started.

#### **Bit 9 – SHIFTCORR: Shift Correction Synchronization Busy**

This bit is cleared when the synchronization of SHIFTCORR register between the clock domains is complete.

This bit is set when the synchronization of SHIFTCORR register between clock domains is started.

#### Bit 8 – GAINCORR: Gain Correction Synchronization Busy

This bit is cleared when the synchronization of GAINCORR register between the clock domains is complete.

This bit is set when the synchronization of GAINCORR register between clock domains is started.

#### Bit 7 – OFFSETCORR: Offset Correction Synchronization Busy

This bit is cleared when the synchronization of OFFSETCORR register between the clock domains is complete.

This bit is set when the synchronization of OFFSETCORR register between clock domains is started.

#### Bit 6 – WINUT: Window Monitor Lower Threshold Synchronization Busy

This bit is cleared when the synchronization of WINUT register between the clock domains is complete.

This bit is set when the synchronization of WINUT register between clock domains is started.

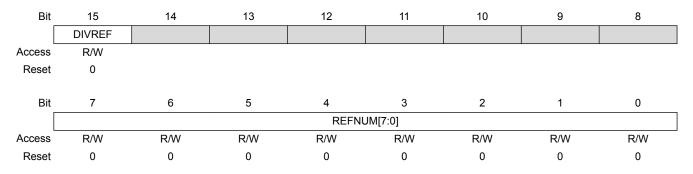

Name:CFGAOffset:0x02 [ID-00000e03]Reset:0x0000Property:PAC Write-Protection, Enable-protected

#### Bit 15 – DIVREF: Divide Reference Clock

Divides the reference clock by 8

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The reference clock is divided by 1. |

| 1     | The reference clock is divided by 8. |

#### Bits 7:0 – REFNUM[7:0]: Number of Reference Clock Cycles

Selects the duration of a measurement in number of CLK\_FREQM\_REF cycles. This must be a non-zero value, i.e. 0x01 (one cycle) to 0xFF (255 cycles).

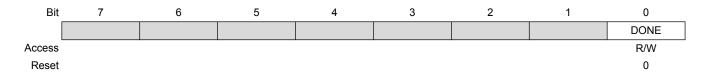

#### 44.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x08 [ID-00000e03]Reset:0x00Property:PAC Write-Protection

#### Bit 0 – DONE: Measurement Done Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Measurement Done Interrupt Enable bit, which disables the Measurement Done interrupt.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The Measurement Done interrupt is disabled. |

| 1     | The Measurement Done interrupt is enabled.  |

#### 44.8.5 Interrupt Enable Set

## SAM C20/C21

| Symbol | Parameter  | Conditions                | Min. | Тур. | Max. | Units |

|--------|------------|---------------------------|------|------|------|-------|

|        |            | f <sub>IN</sub> = 2 MHz,  |      |      |      |       |

|        |            | f <sub>OUT</sub> = 96 MHz |      |      |      |       |

| Duty   | Duty cycle |                           | -    | 50   | -    | %     |

- 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

- 2. These values are based on characterization.

#### Table 45-46. Power Consumption<sup>(1)</sup>

| Symbol | Parameters          | Conditions         | Та       | Тур. | Max | Units |

|--------|---------------------|--------------------|----------|------|-----|-------|

| IDD    | Current Consumption | Ck=48MHz, VDD=5.0V | Max 85°C | 536  | 612 | μA    |

|        |                     | Ck=96MHz, VDD=5.0V | Typ 25°C | 865  | 970 |       |

1. These values are based on characterization.

#### 45.12.4 32.768kHz Internal oscillator (OSC32K) Characteristics Table 45-47. 32 kHz RC Oscillator Characteristics

| Symbol               | Parameter        | Condition                          | Min    | Тур    | Max    | Units |

|----------------------|------------------|------------------------------------|--------|--------|--------|-------|

| f <sub>OUT</sub>     | Output frequency | T =25°C, VDDANA = 5.0V             | 32.112 | 32.768 | 33.423 | kHz   |

|                      |                  | T =25°C, over [2.7, 5.5]V          | 29.491 | 32.768 | 36.044 |       |

|                      |                  | over [-40, 85]°C, over [2.7, 5.5]V | 25.559 | 32.768 | 37.355 |       |

| t <sub>STARTUP</sub> | Startup time     |                                    |        | 1      | 2      | cycle |

| Duty <sup>(1)</sup>  | Duty Cycle       |                                    |        | 50     |        | %     |

1. These are based on simulation. These values are not covered by test or characterization.

#### Table 45-48. Power Consumption<sup>(1)</sup>

| Symbol | Parameters          | Conditions | Та       | Тур.  | Мах   | Units |

|--------|---------------------|------------|----------|-------|-------|-------|

| IDD    | Current consumption | VDD = 5.0V | Max 85°C | 0.864 | 1.080 | μA    |

|        |                     |            | Typ 25°C |       |       |       |

1. These are based on characterization.

#### 45.12.5 Ultra Low Power Internal 32kHz RC Oscillator (OSCULP32K) Characteristics Table 45-49. Ultra Low Power Internal 32 kHz RC Oscillator Electrical Characteristics

| Sym              | nbol | Parameter        | Condition                 | Min    | Тур    | Мах   | Units |

|------------------|------|------------------|---------------------------|--------|--------|-------|-------|

| f <sub>OUT</sub> | -    | Output frequency | T =25°C, VDDANA = 5.0V    | 30.965 | 32.768 | 34.57 | kHz   |

|                  |      |                  | T =25°C, over [2.7, 5.5]V | 30.801 | 32.768 | 34.73 |       |

- 1. These values are only given as a typical example.

- 2. The capacitors should be placed close to the device for each supply pin pair in the signal group.

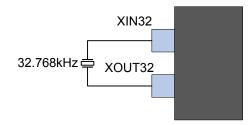

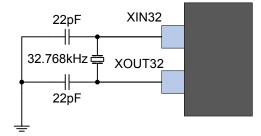

#### 49.7.3 External Real Time Oscillator

The low frequency crystal oscillator is optimized for use with a 32.768kHz watch crystal. When selecting crystals, load capacitance and the crystal's Equivalent Series Resistance (ESR) must be taken into consideration. Both values are specified by the crystal vendor.

SAM C20/C21 oscillator is optimized for very low power consumption, hence close attention should be made when selecting crystals.

The typical parasitic load capacitance values are available in the Electrical Characteristics section. This capacitance and PCB capacitance can allow using a crystal inferior to 12.5pF load capacitance without external capacitors as shown in Figure 49-8.

#### Figure 49-8. External Real Time Oscillator without Load Capacitor

To improve accuracy and Safety Factor, the crystal datasheet can recommend adding external capacitors as shown in Figure 49-9.

To find suitable load capacitance for a 32.768kHz crystal, consult the crystal datasheet.

#### Figure 49-9. External Real Time Oscillator with Load Capacitor

#### Table 49-6. External Real Time Oscillator Checklist

| Signal Name | Recommended Pin Connection            | Description             |  |  |

|-------------|---------------------------------------|-------------------------|--|--|

| XIN32       | Load capacitor 22pF <sup>(1)(2)</sup> | Timer oscillator input  |  |  |

| XOUT32      | Load capacitor 22pF <sup>(1)(2)</sup> | Timer oscillator output |  |  |

1. These values are only given as typical examples.

2. The capacitors should be placed close to the device for each supply pin pair in the signal group.

**Note:** In order to minimize the cycle-to-cycle jitter of the external oscillator, keep the neighboring pins as steady as possible. For neighboring pin details, refer to the Oscillator Pinout section.

### The Microchip Web Site

Microchip provides online support via our web site at http://www.microchip.com/. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Customer Change Notification Service**

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at http://www.microchip.com/. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support