# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e17a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Offset | Name      | Bit Pos. |      |         |         |         |         |         |         |         |

|--------|-----------|----------|------|---------|---------|---------|---------|---------|---------|---------|

| 0x3A   |           | 23:16    |      |         |         |         |         |         |         |         |

| 0x3B   |           | 31:24    |      |         |         |         |         |         |         |         |

| 0x3C   |           | 7:0      | CAN0 | SERCOM5 | SERCOM4 | SERCOM3 | SERCOM2 | SERCOM1 | SERCOM0 | EVSYS   |

| 0x3D   | STATUSC   | 15:8     | TC3  | TC2     | TC1     | TC0     | TCC2    | TC2     | TC1     | TC0     |

| 0x3E   | - STATUSC | 23:16    | CCL  | PTC     | DAC     | AC      | SDADC   | ADC1    | ADC0    | TC4     |

| 0x3F   |           | 31:24    |      |         |         |         |         |         |         |         |

| 0x40   |           | 7:0      |      |         |         | TC7     | TC6     | TC5     | SERCOM7 | SERCOM6 |

| 0x41   | STATUSD   | 15:8     |      |         |         |         |         |         |         |         |

| 0x42   |           | 23:16    |      |         |         |         |         |         |         |         |

| 0x43   |           | 31:24    |      |         |         |         |         |         |         |         |

# **11.7** Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to the related links.

# 11.7.1 Write Control

| Name:     | WRCTRL             |

|-----------|--------------------|

| Offset:   | 0x00 [ID-00000a18] |

| Reset:    | 0x00000000         |

| Property: | -                  |

also be entered when the CPU exits the lowest priority ISR. This mechanism can be useful for applications that only require the processor to run when an interrupt occurs. Before entering the IDLE mode, the user must configure the Sleep Configuration register.

Exiting IDLE mode: The processor wakes the system up when it detects any non-masked interrupt with sufficient priority to cause exception entry. The system goes back to the ACTIVE mode. The CPU and affected modules are restarted.

Regulator operates in normal mode.

# STANDBY Mode

The STANDBY mode is the lowest power configuration while keeping the state of the logic and the content of the RAM.

In this mode, all clocks are stopped except those which are kept running if requested by a running peripheral or have the ONDEMAND bit written to "0". For example, the RTC can operate in STANDBY mode. In this case, its GCLK clock source will also be enabled.

All features that don't require CPU intervention are supported in STANDBY mode. Here are examples:

- Autonomous peripherals features.

- Features relying on Event System allowing autonomous communication between peripherals.

- Features relying on on-demand clock.

- DMA transfers.

- Entering STANDBY mode: This mode is entered by executing the WFI instruction with the SLEEPCFG register written to STANDBY. The SLEEPONEXIT feature is also available as in IDLE mode.

- Exiting STANDBY mode: Any peripheral able to generate an asynchronous interrupt can wake up the system. For example, a peripheral running on a GCLK clock can trigger an interrupt. When the enabled asynchronous wake-up event occurs and the system is woken up, the device will either execute the interrupt service routine or continue the normal program execution according to the Priority Mask Register (PRIMASK) configuration of the CPU.

Depending on the configuration of these modules, the current consumption of the device in STANDBY mode can be slightly different.

The regulator operates in low-power mode (LP VREG) by default and can switch automatically to the main regulator if a task required by a peripheral requires more power. It returns automatically in the low power mode as soon as the task is completed.

# 19.6.4 Advanced Features

# 19.6.4.1 RAM Automatic Low Power Mode

The RAM is by default put in low power mode (back-biased) if the device is in standby sleep mode.

This behavior can be changed by configuring the Back Bias bit in the Standby Configuration register (STDBYCFG.BBIASHS), refer to the table below for details.

**Note:** In standby sleep mode, the RAM is put in low-power mode by default. This means that the RAM is back-biased, and the DMAC cannot access it. The DMAC can only access the RAM when it is not back biased (PM.STDBYCFG.BBIASxx=0x0).

# Table 19-3. RAM Back-Biasing Mode

| STBYCDFG.BBIASHS |                           | RAM                                                            |

|------------------|---------------------------|----------------------------------------------------------------|

| 0x0              | No Back Biasing           | RAM is not back-biased if the device is in standby sleep mode. |

| 0x1              | Standby Back Biasing mode | RAM is back-biased if the device is in standby sleep mode.     |

# 19.6.4.2 Regulator Automatic Low Power Mode

In standby mode, the PM selects either the main or the low power voltage regulator to supply the VDDCORE. By default the low power voltage regulator is used.

If a sleepwalking task is working on either asynchronous clocks (generic clocks) or synchronous clock (APB/AHB clocks), the main voltage regulator is used. This behavior can be changed by writing the Voltage Regulator Standby Mode bits in the Standby Configuration register (STDBYCFG.VREGSMOD). Refer to the following table for details.

# Table 19-4. Regulator State in Sleep Mode

| Sleep<br>Mode | STDBYCFG.<br>VREGSMOD | SleepWalking | Regulator state for VDDCORE |

|---------------|-----------------------|--------------|-----------------------------|

| Active        | -                     | -            | main voltage regulator      |

| Idle          | -                     | -            | main voltage regulator      |

| Standby       | 0x0: AUTO             | NO           | low power regulator         |

|               |                       | YES          | main voltage regulator      |

|               | 0x1: PERFORMANCE      | -            | main voltage regulator      |

|               | 0x2: LP               | -            | low power regulator         |

# 19.6.5 DMA Operation

Not applicable.

# 19.6.6 Interrupts

Not applicable.

# 19.6.7 Events

Not applicable.

# 19.6.8 Sleep Mode Operation

The Power Manager is always active.

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28        | 27                                    | 26      | 25       | 24       |

|--------|----|----|----|-----------|---------------------------------------|---------|----------|----------|

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 23 | 22 | 21 | 20        | 19                                    | 18      | 17       | 16       |

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 15 | 14 | 13 | 12        | 11                                    | 10      | 9        | 8        |

|        |    |    |    |           | DPLLLDRTO                             | DPLLLTO | DPLLLCKF | DPLLLCKR |

| Access |    |    |    |           | R/W                                   | R/W     | R/W      | R/W      |

| Reset  |    |    |    |           | 0                                     | 0       | 0        | 0        |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 7  | 6  | 5  | 4         | 3                                     | 2       | 1        | 0        |

|        |    |    |    | OSC48MRDY |                                       |         | CLKFAIL  | XOSCRDY  |

| Access |    | •  | •  | R/W       | · · · · · · · · · · · · · · · · · · · |         | R/W      | R/W      |

| Reset  |    |    |    | 0         |                                       |         | 0        | 0        |

# Bit 11 – DPLLLDRTO: DPLL Loop Divider Ratio Update Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Loop Divider Ratio Update Complete Interrupt Enable bit, which disables the DPLL Loop Divider Ratio Update Complete interrupt.

| Value | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Loop Divider Ratio Update Complete interrupt is disabled.                                                                                                                   |

| 1     | The DPLL Loop Divider Ratio Update Complete interrupt is enabled, and an interrupt request will be generated when the DPLL Loop Divider Ratio Update Complete Interrupt flag is set. |

# Bit 10 – DPLLLTO: DPLL Lock Timeout Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Timeout Interrupt Enable bit, which disables the DPLL Lock Timeout interrupt.

| Value | Description                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Timeout interrupt is disabled.                                                                                             |

| 1     | The DPLL Lock Timeout interrupt is enabled, and an interrupt request will be generated when the DPLL Lock Timeout Interrupt flag is set. |

# Bit 9 – DPLLLCKF: DPLL Lock Fall Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Fall Interrupt Enable bit, which disables the DPLL Lock Fall interrupt.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Fall interrupt is disabled.                                                    |

| 1     | The DPLL Lock Fall interrupt is enabled, and an interrupt request will be generated when the |

|       | DPLL Lock Fall Interrupt flag is set.                                                        |

# Bit 7 – ONDEMAND: On Demand Control

This bit controls how the XOSC32K behaves when a peripheral clock request is detected. For details, refer to XOSC32K Sleep Behavior.

#### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the XOSC32K behaves during standby sleep mode. For details, refer to XOSC32K Sleep Behavior.

# Bit 4 – EN1K: 1KHz Output Enable

| Value | Description                  |

|-------|------------------------------|

| 0     | The 1KHz output is disabled. |

| 1     | The 1KHz output is enabled.  |

#### Bit 3 – EN32K: 32KHz Output Enable

| Value | Description                   |

|-------|-------------------------------|

| 0     | The 32KHz output is disabled. |

| 1     | The 32KHz output is enabled.  |

#### Bit 2 – XTALEN: Crystal Oscillator Enable

This bit controls the connections between the I/O pads and the external clock or crystal oscillator.

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | External clock connected on XIN32. XOUT32 can be used as general-purpose I/O. |

| 1     | Crystal connected to XIN32/XOUT32.                                            |

# Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

#### 21.8.6 Clock Failure Detector Control

Name:CFDCTRLOffset:0x16Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2        | 1      | 0     |

|--------|---|---|---|---|---|----------|--------|-------|

|        |   |   |   |   |   | CFDPRESC | SWBACK | CFDEN |

| Access |   |   |   |   |   | R/W      | R/W    | R/W   |

| Reset  |   |   |   |   |   | 0        | 0      | 0     |

# **Bit 2 – CFDPRESC:** Clock Failure Detector Prescaler

This bit selects the prescaler for the Clock Failure Detector.

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The CFD safe clock frequency is the OSCULP32K frequency              |

| 1     | The CFD safe clock frequency is the OSCULP32K frequency divided by 2 |

| Bit    | 31       | 30       | 29  | 28      | 27         | 26    | 25           | 24  |

|--------|----------|----------|-----|---------|------------|-------|--------------|-----|

| Access |          |          |     |         |            |       |              |     |

| Reset  |          |          |     |         |            |       |              |     |

| Bit    | 23       | 22       | 21  | 20      | 19         | 18    | 17           | 16  |

|        |          |          |     |         | CALIB[6:0] |       |              |     |

| Access |          | R/W      | R/W | R/W     | R/W        | R/W   | R/W          | R/W |

| Reset  |          | 0        | 0   | 0       | 0          | 0     | 0            | 0   |

|        |          |          |     |         |            |       |              |     |

| Bit    | 15       | 14       | 13  | 12      | 11         | 10    | 9            | 8   |

|        |          |          |     | WRTLOCK |            |       | STARTUP[2:0] |     |

| Access |          |          |     | R/W     |            | R/W   | R/W          | R/W |

| Reset  |          |          |     | 0       |            | 0     | 0            | 0   |

|        |          |          |     |         |            |       |              |     |

| Bit    | 7        | 6        | 5   | 4       | 3          | 2     | 1            | 0   |

|        | ONDEMAND | RUNSTDBY |     |         | EN1K       | EN32K | ENABLE       |     |

| Access | R/W      | R/W      |     |         | R/W        | R/W   | R/W          |     |

| Reset  | 1        | 0        |     |         | 0          | 0     | 0            |     |

# Bits 22:16 – CALIB[6:0]: Oscillator Calibration

These bits control the oscillator calibration. The calibration values must be loaded by the user from the NVM Software Calibration Area.

# Bit 12 – WRTLOCK: Write Lock

This bit locks the OSC32K register for future writes, effectively freezing the OSC32K configuration.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The OSC32K configuration is not locked. |

| 1     | The OSC32K configuration is locked.     |

# Bits 10:8 – STARTUP[2:0]: Oscillator Start-Up Time

These bits select start-up time for the oscillator.

The OSCULP32K oscillator is used as input clock to the start-up counter.

# Table 21-4. Start-Up Time for 32KHz Internal Oscillator

| STARTUP[2:0] | Number of OSC32K clock cycles | Approximate Equivalent Time [ms] |

|--------------|-------------------------------|----------------------------------|

| 0x0          | 3                             | 0.092                            |

| 0x1          | 4                             | 0.122                            |

| 0x2          | 6                             | 0.183                            |

| 0x3          | 10                            | 0.305                            |

| 0x4          | 18                            | 0.549                            |

| 0x5          | 34                            | 1.038                            |

| 0x6          | 66                            | 2.014                            |

| 0x7          | 130                           | 3.967                            |

channel is disabled. This register bit cannot be cleared by the application when the CRC is used with a DMA channel.

This bit is set when a source configuration is selected and as long as the source is using the CRC module.

# 25.8.6 Debug Control

Name:DBGCTRLOffset:0x0DReset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   | • |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

# Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

| Value | Description                                                                         |

|-------|-------------------------------------------------------------------------------------|

| 0     | The DMAC is halted when the CPU is halted by an external debugger.                  |

| 1     | The DMAC continues normal operation when the CPU is halted by an external debugger. |

# 25.8.7 Quality of Service Control

| Name:     | QOSCTRL              |

|-----------|----------------------|

| Offset:   | 0x0E [ID-00001ece]   |

| Reset:    | 0x2A                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5         | 4   | 3         | 2   | 1           | 0   |

|--------|---|---|-----------|-----|-----------|-----|-------------|-----|

|        |   |   | DQOS[1:0] |     | FQOS[1:0] |     | WRBQOS[1:0] |     |

| Access |   |   | R/W       | R/W | R/W       | R/W | R/W         | R/W |

| Reset  |   |   | 1         | 0   | 1         | 0   | 1           | 0   |

# Bits 5:4 – DQOS[1:0]: Data Transfer Quality of Service

These bits define the memory priority access during the data transfer operation.

| DQOS[1:0] | Name    | Description                         |

|-----------|---------|-------------------------------------|

| 0x0       | DISABLE | Background (no sensitive operation) |

| 0x1       | LOW     | Sensitive Bandwidth                 |

| 0x2       | MEDIUM  | Sensitive Latency                   |

| 0x3       | HIGH    | Critical Latency                    |

Name:INTSTATUSOffset:0x24Reset:0x0000000Property:-

| Bit    | 31     | 30     | 29     | 28     | 27     | 26     | 25     | 24     |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|        |        |        |        |        |        |        |        |        |

| Access |        |        |        |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |        |

| Bit    | 23     | 22     | 21     | 20     | 19     | 18     | 17     | 16     |

|        |        |        |        |        |        |        |        |        |

| Access |        |        |        |        |        |        |        |        |

| Reset  |        |        |        |        |        |        |        |        |

|        |        |        |        |        |        |        |        |        |

| Bit    | 15     | 14     | 13     | 12     | 11     | 10     | 9      | 8      |

|        |        |        |        |        | CHINTn | CHINTn | CHINTn | CHINTn |

| Access |        |        |        |        | R      | R      | R      | R      |

| Reset  |        |        |        |        | 0      | 0      | 0      | 0      |

|        |        |        |        |        |        |        |        |        |

| Bit    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|        | CHINTn |

| Access | R      | R      | R      | R      | R      | R      | R      | R      |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

# Bits 11:0 – CHINTn: Channel n Pending Interrupt [n=11..0]

This bit is set when Channel n has a pending interrupt/the interrupt request is received.

This bit is cleared when the corresponding Channel n interrupts are disabled or the interrupts sources are cleared.

# 25.8.12 Busy Channels

Name:

BUSYCH

Offset:

0x28

Reset:

0x0000000

Property:

# 31.6.2.3 Clock Generation and Selection

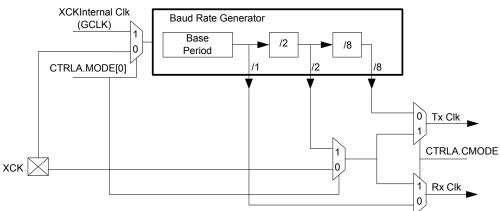

For both synchronous and asynchronous modes, the clock used for shifting and sampling data can be generated internally by the SERCOM baud-rate generator or supplied externally through the XCK line.

The synchronous mode is selected by writing a '1' to the Communication Mode bit in the Control A register (CTRLA.CMODE), the asynchronous mode is selected by writing a zero to CTRLA.CMODE.

The internal clock source is selected by writing 0x1 to the Operation Mode bit field in the Control A register (CTRLA.MODE), the external clock source is selected by writing 0x0 to CTRLA.MODE.

The SERCOM baud-rate generator is configured as in the figure below.

In asynchronous mode (CTRLA.CMODE=0), the 16-bit Baud register value is used.

In synchronous mode (CTRLA.CMODE=1), the eight LSBs of the Baud register are used. Refer to *Clock Generation – Baud-Rate Generator* for details on configuring the baud rate.

#### Figure 31-3. Clock Generation

#### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

#### Synchronous Clock Operation

In synchronous mode, the CTRLA.MODE bit field determines whether the transmission clock line (XCK) serves either as input or output. The dependency between clock edges, data sampling, and data change is the same for internal and external clocks. Data input on the RxD pin is sampled at the opposite XCK clock edge when data is driven on the TxD pin.

The Clock Polarity bit in the Control A register (CTRLA.CPOL) selects which XCK clock edge is used for RxD sampling, and which is used for TxD change:

When CTRLA.CPOL is '0', the data will be changed on the rising edge of XCK, and sampled on the falling edge of XCK.

When CTRLA.CPOL is '1', the data will be changed on the falling edge of XCK, and sampled on the rising edge of XCK.

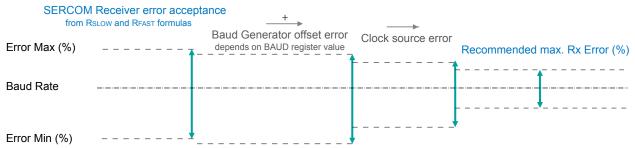

The following equations calculate the ratio of the incoming data rate and internal receiver baud rate:

$$R_{\text{SLOW}} = \frac{(D+1)S}{S-1+D\cdot S+S_F}$$

,  $R_{\text{FAST}} = \frac{(D+2)S}{(D+1)S+S_M}$

- R<sub>SLOW</sub> is the ratio of the slowest incoming data rate that can be accepted in relation to the receiver baud rate

- *R*<sub>FAST</sub> is the ratio of the fastest incoming data rate that can be accepted in relation to the receiver baud rate

- *D* is the sum of character size and parity size (D = 5 to 10 bits)

- S is the number of samples per bit (S = 16, 8 or 3)

- $S_F$  is the first sample number used for majority voting ( $S_F = 7, 3, \text{ or } 2$ ) when CTRLA.SAMPA=0.

- $S_M$  is the middle sample number used for majority voting ( $S_M$  = 8, 4, or 2) when CTRLA.SAMPA=0.

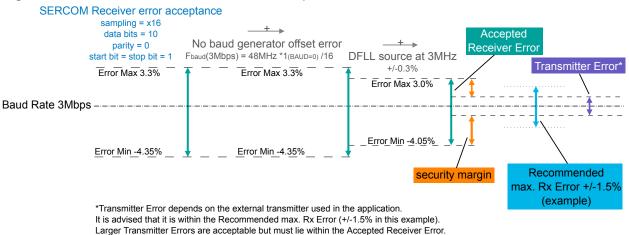

The recommended maximum Rx Error assumes that the receiver and transmitter equally divide the maximum total error. Its connection to the SERCOM Receiver error acceptance is depicted in this figure:

#### Figure 31-5. USART Rx Error Calculation

The recommendation values in the table above accommodate errors of the clock source and the baud generator. The following figure gives an example for a baud rate of 3Mbps:

#### Figure 31-6. USART Rx Error Calculation Example

#### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

#### 31.6.3 Additional Features

# 31.6.3.1 Parity

Even or odd parity can be selected for error checking by writing 0x1 to the Frame Format bit field in the Control A register (CTRLA.FORM).

data bit is shifted in. And the Receive Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) will be set. The received data can be retrieved by reading DATA.

When the last character has been transmitted and there is no valid data in DATA, the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set. When the transaction is finished, the master must pull the  $\overline{SS}$  line high to notify the slave. If Master Slave Select Enable (CTRLB.MSSEN) is set to '0', the software must pull the  $\overline{SS}$  line high.

#### Slave

In slave mode (CTRLA.MODE=0x2), the SPI interface will remain inactive with the MISO line tri-stated as long as the  $\overline{SS}$  pin is pulled high. Software may update the contents of DATA at any time as long as the Data Register Empty flag in the Interrupt Status and Clear register (INTFLAG.DRE) is set.

When  $\overline{SS}$  is pulled low and SCK is running, the slave will sample and shift out data according to the transaction mode set. When the content of TxDATA has been loaded into the shift register, INTFLAG.DRE will be set, and new data can be written to DATA.

Similar to the master, the slave will receive one character for each character transmitted. A character will be transferred into the two-level receive buffer within the same clock cycle its last data bit is received. The received character can be retrieved from DATA when the Receive Complete interrupt flag (INTFLAG.RXC) is set.

When the master pulls the  $\overline{SS}$  line high, the transaction is done and the Transmit Complete Interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.TXC) will be set.

After DATA is written it takes up to three SCK clock cycles until the content of DATA is ready to be loaded into the shift register on the next character boundary. As a consequence, the first character transferred in a SPI transaction will not be the content of DATA. This can be avoided by using the preloading feature. Refer to Preloading of the Slave Shift Register.

When transmitting several characters in one SPI transaction, the data has to be written into DATA register with at least three SCK clock cycles left in the current character transmission. If this criteria is not met, the previously received character will be transmitted.

Once the DATA register is empty, it takes three CLK\_SERCOM\_APB cycles for INTFLAG.DRE to be set.

# 32.6.2.7 Receiver Error Bit

The SPI receiver has one error bit: the Buffer Overflow bit (BUFOVF), which can be read from the Status register (STATUS). Once an error happens, the bit will stay set until it is cleared by writing '1' to it. The bit is also automatically cleared when the receiver is disabled.

There are two methods for buffer overflow notification, selected by the immediate buffer overflow notification bit in the Control A register (CTRLA.IBON):

If CTRLA.IBON=1, STATUS.BUFOVF is raised immediately upon buffer overflow. Software can then empty the receive FIFO by reading RxDATA until the receiver complete interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG.RXC) goes low.

If CTRLA.IBON=0, the buffer overflow condition travels with data through the receive FIFO. After the received data is read, STATUS.BUFOVF and INTFLAG.ERROR will be set along with INTFLAG.RXC, and RxDATA will be zero.

# 32.6.3 Additional Features

# 32.6.3.1 Address Recognition

When the SPI is configured for slave operation (CTRLA.MODE=0x2) with address recognition (CTRLA.FORM is 0x2), the SERCOM address recognition logic is enabled: the first character in a transaction is checked for an address match.

| Bit    | 31   | 30      | 29    | 28 | 27 | 26  | 25          | 24  |

|--------|------|---------|-------|----|----|-----|-------------|-----|

| Access |      |         |       |    |    |     |             |     |

| Reset  |      |         |       |    |    |     |             |     |

|        |      |         |       |    |    |     |             |     |

| Bit    | 23   | 22      | 21    | 20 | 19 | 18  | 17          | 16  |

| [      |      |         |       |    |    |     | RXEN        |     |

| Access |      |         |       |    |    |     | R/W         |     |

| Reset  |      |         |       |    |    |     | 0           |     |

|        |      |         |       |    |    |     |             |     |

| Bit    | 15   | 14      | 13    | 12 | 11 | 10  | 9           | 8   |

|        | AMOD | DE[1:0] | MSSEN |    |    |     | SSDE        |     |

| Access | R/W  | R/W     | R/W   |    |    |     | R/W         |     |

| Reset  | 0    | 0       | 0     |    |    |     | 0           |     |

|        |      |         |       |    |    |     |             |     |

| Bit    | 7    | 6       | 5     | 4  | 3  | 2   | 1           | 0   |

|        |      | PLOADEN |       |    |    |     | CHSIZE[2:0] |     |

| Access |      | R/W     |       |    |    | R/W | R/W         | R/W |

| Reset  |      | 0       |       |    |    | 0   | 0           | 0   |

# Bit 17 – RXEN: Receiver Enable

Writing '0' to this bit will disable the SPI receiver immediately. The receive buffer will be flushed, data from ongoing receptions will be lost and STATUS.BUFOVF will be cleared.

Writing '1' to CTRLB.RXEN when the SPI is disabled will set CTRLB.RXEN immediately. When the SPI is enabled, CTRLB.RXEN will be cleared, SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the SPI is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | The receiver is disabled or being enabled.                         |

| 1     | The receiver is enabled or it will be enabled when SPI is enabled. |

#### Bits 15:14 – AMODE[1:0]: Address Mode

These bits set the slave addressing mode when the frame format (CTRLA.FORM) with address is used. They are unused in master mode.

| AMODE[1:0] | Name    | Description                                                                                                   |

|------------|---------|---------------------------------------------------------------------------------------------------------------|

| 0x0        | MASK    | ADDRMASK is used as a mask to the ADDR register                                                               |

| 0x1        | 2_ADDRS | The slave responds to the two unique addresses in ADDR and ADDRMASK                                           |

| 0x2        | RANGE   | The slave responds to the range of addresses between and including ADDR and ADDRMASK. ADDR is the upper limit |

| 0x3        | -       | Reserved                                                                                                      |

# Bit 13 – MSSEN: Master Slave Select Enable

This bit enables hardware slave select ( $\overline{SS}$ ) control.

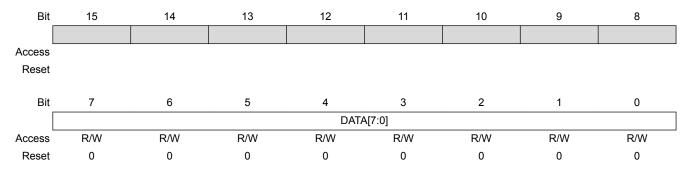

Name:DATAOffset:0x28 [ID-00001bb3]Reset:0x0000Property:Write-Synchronized, Read-Synchronized

# Bits 7:0 - DATA[7:0]: Data

The slave data register I/O location (DATA.DATA) provides access to the master transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is held low by the slave (STATUS.CLKHOLD is set). An exception occurs when reading the last data byte after the stop condition has been received.

Accessing DATA.DATA auto-triggers I<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

Writing or reading DATA.DATA when not in smart mode does not require synchronization.

The table below shows the update counter and overflow event/interrupt generation conditions in different operation modes.

| Name | Operation        | ТОР | Update    | Output Waveform        |        | OVFIF/Event |      |

|------|------------------|-----|-----------|------------------------|--------|-------------|------|

|      |                  |     |           | On Match On Update     |        | Up          | Down |

| NFRQ | Normal Frequency | PER | TOP/ ZERO | Toggle                 | Stable | TOP         | ZERO |

| MFRQ | Match Frequency  | CC0 | TOP/ ZERO | Toggle                 | Stable | TOP         | ZERO |

| NPWM | Single-slope PWM | PER | TOP/ ZERO | See description above. |        | TOP         | ZERO |

| MPWM | Single-slope PWM | CC0 | TOP/ ZERO | Toggle Toggle          |        | TOP         | ZERO |

Table 35-3. Counter Update and Overflow Event/interrupt Conditions in TC

# **Related Links**

PORT: IO Pin Controller

# 35.6.2.7 Double Buffering

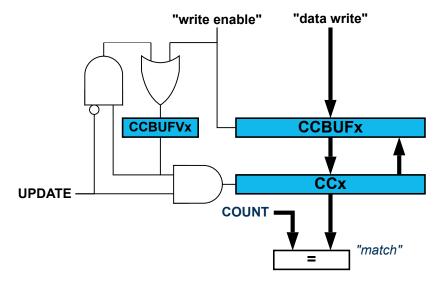

The Compare Channels (CCx) registers, and the Period (PER) register in 8-bit mode are double buffered. Each buffer register has a buffer valid bit (CCBUFVx or PERBUFV) in the STATUS register, which indicates that the buffer register contains a new valid value that can be copied into the corresponding register. As long as the respective buffer valid status flag (PERBUFV or CCBUFVx) are set to '1', related syncbusy bits are set (SYNCBUSY.PER or SYNCBUSY.CCx), a write to the respective PER/PERBUF or CCx/CCBUFx registers will generate a PAC error, and access to the respective PER or CCx register is invalid.

When the buffer valid flag bit in the STATUS register is '1' and the Lock Update bit in the CTRLB register is set to '0', (writing CTRLBCLR.LUPD to '1'), double buffering is enabled: the data from buffer registers will be copied into the corresponding register under hardware UPDATE conditions, then the buffer valid flags bit in the STATUS register are automatically cleared by hardware.

**Note:** The software update command (CTRLBSET.CMD=0x3) is acting independently of the LUPD value.

A compare register is double buffered as in the following figure.

# Figure 35-7. Compare Channel Double Buffering

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0       |

|--------|---|---|---|---|---|---|-------|---------|

|        |   |   |   |   |   |   | WAVEG | EN[1:0] |

| Access |   |   |   |   |   |   | R/W   | R/W     |

| Reset  |   |   |   |   |   |   | 0     | 0       |

|        |   |   |   |   |   |   |       |         |

# Bits 1:0 – WAVEGEN[1:0]: Waveform Generation Mode

These bits select the waveform generation operation. They affect the top value, as shown in Waveform Output Operations. They also control whether frequency or PWM waveform generation should be used. The waveform generation operations are explained in Waveform Output Operations.

These bits are not synchronized.

| Value | Name | Operation        | Top Value              | Output<br>Waveform<br>on Match | Output Waveform<br>on Wraparound |

|-------|------|------------------|------------------------|--------------------------------|----------------------------------|

| 0x0   | NFRQ | Normal frequency | PER <sup>1</sup> / Max | Toggle                         | No action                        |

| 0x1   | MFRQ | Match frequency  | CC0                    | Toggle                         | No action                        |

| 0x2   | NPWM | Normal PWM       | PER <sup>1</sup> / Max | Set                            | Clear                            |

| 0x3   | MPWM | Match PWM        | CC0                    | Set                            | Clear                            |

1) This depends on the TC mode: In 8-bit mode, the top value is the Period Value register (PER). In 16and 32-bit mode it is the respective MAX value.

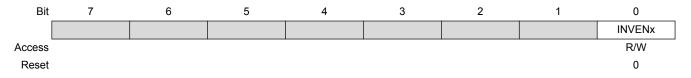

# 35.7.1.10 Driver Control

Name:DRVCTRLOffset:0x0DReset:0x00Property:PAC Write-Protection, Enable-Protected

# Bit 0 – INVENx: Output Waveform x Invert Enable

Bit x of INVEN[1:0] selects inversion of the output or capture trigger input of channel x.

| V | alue | Description                                             |

|---|------|---------------------------------------------------------|

| 0 |      | Disable inversion of the WO[x] output and IO input pin. |

| 1 |      | Enable inversion of the WO[x] output and IO input pin.  |

#### 35.7.1.11 Debug Control

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Number of<br>Automatic Right<br>Shifts | Final Result<br>Precision | Automatic<br>Division Factor |

|-------------------------------------|-----------------------|----------------------------------------|---------------------------|------------------------------|

| 4                                   | 0x2                   | 0                                      | 14 bits                   | 0                            |

| 8                                   | 0x3                   | 0                                      | 15 bits                   | 0                            |

| 16                                  | 0x4                   | 0                                      | 16 bits                   | 0                            |

| 32                                  | 0x5                   | 1                                      | 16 bits                   | 2                            |

| 64                                  | 0x6                   | 2                                      | 16 bits                   | 4                            |

| 128                                 | 0x7                   | 3                                      | 16 bits                   | 8                            |

| 256                                 | 0x8                   | 4                                      | 16 bits                   | 16                           |

| 512                                 | 0x9                   | 5                                      | 16 bits                   | 32                           |

| 1024                                | 0xA                   | 6                                      | 16 bits                   | 64                           |

| Reserved                            | 0xB –0xF              |                                        | 12 bits                   | 0                            |

# 38.6.2.10 Averaging

Averaging is a feature that increases the sample accuracy, at the cost of a reduced sampling rate. This feature is suitable when operating in noisy conditions.

Averaging is done by accumulating m samples, as described in Accumulation, and dividing the result by m. The averaged result is available in the RESULT register. The number of samples to be accumulated is specified by writing to AVGCTRL.SAMPLENUM as shown in Table 38-2.

The division is obtained by a combination of the automatic right shift described above, and an additional right shift that must be specified by writing to the Adjusting Result/Division Coefficient field in AVGCTRL (AVGCTRL.ADJRES), as described in Table 38-2.

**Note:** To perform the averaging of two or more samples, the Conversion Result Resolution field in the Control C register (CTRLC.RESSEL) must be set.

Averaging AVGCTRL.SAMPLENUM samples will reduce the un-averaged sampling rate by a factor

#### AVGCTRL.SAMPLENUM.

When the averaged result is available, the INTFLAG.RESRDY bit will be set.

#### Table 38-2. Averaging

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Intermediate<br>Result<br>Precision | Number of<br>Automatic<br>Right<br>Shifts |    | AVGCTRL.ADJRES | Total<br>Number<br>of Right<br>Shifts | Final<br>Result<br>Precision | Automatic<br>Division<br>Factor |

|-------------------------------------|-----------------------|-------------------------------------|-------------------------------------------|----|----------------|---------------------------------------|------------------------------|---------------------------------|

| 1                                   | 0x0                   | 12 bits                             | 0                                         | 1  | 0x0            |                                       | 12 bits                      | 0                               |

| 2                                   | 0x1                   | 13                                  | 0                                         | 2  | 0x1            | 1                                     | 12 bits                      | 0                               |

| 4                                   | 0x2                   | 14                                  | 0                                         | 4  | 0x2            | 2                                     | 12 bits                      | 0                               |

| 8                                   | 0x3                   | 15                                  | 0                                         | 8  | 0x3            | 3                                     | 12 bits                      | 0                               |

| 16                                  | 0x4                   | 16                                  | 0                                         | 16 | 0x4            | 4                                     | 12 bits                      | 0                               |

| 32                                  | 0x5                   | 17                                  | 1                                         | 16 | 0x4            | 5                                     | 12 bits                      | 2                               |

**Note:** If several events are connected to the ADC, the enabled action will be taken on any of the incoming events. If FLUSH and START events are available at the same time, the FLUSH event has priority.

#### **Related Links**

EVSYS - Event System

# 38.6.7 Sleep Mode Operation

The ONDEMAND and RUNSTDBY bits in the Control A register (CTRLA) control the behavior of the ADC during standby sleep mode, in cases where the ADC is enabled (CTRLA.ENABLE = 1). For further details on available options, refer to Table 38-4.

**Note:** When CTRLA.ONDEMAND=1, the analog block is powered-off when the conversion is complete. When a start request is detected, the system returns from sleep and starts a new conversion after the start-up time delay.

| CTRLA.RUNSTDBY | CTRLA.ONDEMAND | CTRLA.ENABLE | Description                                        |

|----------------|----------------|--------------|----------------------------------------------------|

| x              | x              | 0            | Disabled                                           |

| 0              | 0              | 1            | Run in all sleep modes except STANDBY.             |

| 0              | 1              | 1            | Run in all sleep modes on request, except STANDBY. |

| 1              | 0              | 1            | Run in all sleep modes.                            |

| 1              | 1              | 1            | Run in all sleep modes on request.                 |

# Table 38-4. ADC Sleep Behavior

# 38.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

The following registers are synchronized when written:

- Input Control register (INPUTCTRL)

- Control C register (CTRLC)

- Average control register (AVGCTRL)

- Sampling time control register (SAMPCTRL)

- Window Monitor Lower Threshold register (WINLT)

- Window Monitor Upper Threshold register (WINUT)

- Gain correction register (GAINCORR)

- Offset Correction register (OFFSETCORR)

- Software Trigger register (SWTRIG)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

#### **Related Links**

# 40.7 Register Summary

| Offset | Name      | Bit Pos. |        |           |             |           |           |         |             |         |

|--------|-----------|----------|--------|-----------|-------------|-----------|-----------|---------|-------------|---------|

| 0x00   | CTRLA     | 7:0      |        |           |             |           |           |         | ENABLE      | SWRST   |

| 0x01   | CTRLB     | 7:0      |        |           |             |           | STARTx    | STARTx  | STARTx      | STARTx  |

| 0x02   | EVICTER   | 7:0      |        |           | WINEOx      | WINEOx    | COMPEOx   | COMPEOx | COMPEOx     | COMPEOx |

| 0x03   | EVCTRL    | 15:8     | INVEIx | INVEIx    | INVEIx      | INVEIx    | COMPEIx   | COMPEIx | COMPEIx     | COMPEIx |

| 0x04   | INTENCLR  | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x05   | INTENSET  | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x06   | INTFLAG   | 7:0      |        |           | WINx        | WINx      | COMPx     | COMPx   | COMPx       | COMPx   |

| 0x07   | STATUSA   | 7:0      | WSTA   | TE1[1:0]  | WSTAT       | E0[1:0]   | STATEx    | STATEx  | STATEx      | STATEx  |

| 0x08   | STATUSB   | 7:0      |        |           |             |           | READYx    | READYx  | READYx      | READYx  |

| 0x09   | DBGCTRL   | 7:0      |        |           |             |           |           |         |             | DBGRUN  |

| 0x0A   | WINCTRL   | 7:0      |        | WINTS     | EL1[1:0]    | WEN1      |           | WINTS   | EL0[1:0]    | WEN0    |

| 0x0B   | Reserved  |          |        |           |             |           |           |         |             |         |

| 0x0C   | SCALERn0  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x0D   | SCALERn1  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x0E   | SCALERn2  | 7:0      |        |           |             |           | VALU      | E[5:0]  |             |         |

| 0x0F   | SCALERn3  | 7:0      |        |           | VALUE[5:0]  |           |           |         |             |         |

| 0x10   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x11   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x12   | COMPCTRL0 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x13   |           | 31:24    |        |           | OUT         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x14   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x15   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x16   | COMPCTRL1 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x17   |           | 31:24    |        |           | TUO         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x18   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x19   | COMPCTRL2 | 15:8     | SWAP   |           | MUXPOS[2:0] | -         |           |         | MUXNEG[2:0] |         |

| 0x1A   | COWPCTRL2 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x1B   |           | 31:24    |        |           | τυο         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x1C   |           | 7:0      |        | RUNSTDBY  |             | INTSE     | EL[1:0]   | SINGLE  | ENABLE      |         |

| 0x1D   |           | 15:8     | SWAP   |           | MUXPOS[2:0] |           |           |         | MUXNEG[2:0] |         |

| 0x1E   | COMPCTRL3 | 23:16    |        |           |             |           | HYSTEN    |         | SPEE        | D[1:0]  |

| 0x1F   |           | 31:24    |        |           | τυο         | [1:0]     |           |         | FLEN[2:0]   |         |

| 0x20   |           | 7:0      |        | COMPCTRLx | COMPCTRLx   | COMPCTRLx | COMPCTRLx | WINCTRL | ENABLE      | SWRST   |

| 0x21   | SYNCBUSY  | 15:8     |        |           |             |           |           |         |             |         |

| 0x22   | STINCBUST | 23:16    |        |           |             |           |           |         |             |         |

| 0x23   |           | 31:24    |        |           |             |           |           |         |             |         |

# 40.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

# SAM C20/C21

| Symbol | Parameter                     | Conditions                              |                            | Measurement |           |         | Unit  |  |

|--------|-------------------------------|-----------------------------------------|----------------------------|-------------|-----------|---------|-------|--|

|        |                               |                                         |                            | Min         | Тур       | Мах     |       |  |

|        |                               |                                         | Vddana=2.7V<br>Vref=2.0V   | -           | 30.4      | 61.0    |       |  |

| INL    | Integral Non<br>Linearity     | Fadc = 500 ksps                         | Vddana=5.0V<br>Vref=Vddana | -           | +/-2.4    | +/-4    | LSB   |  |

|        |                               |                                         | Vddana=2.7V<br>Vref=2.0V   | -           | +/-3.7    | +/-6    |       |  |

|        |                               | Fadc = 1 Msps                           | Vddana=5.0V<br>Vref=Vddana | -           | +/-2.2    | +/-4    |       |  |

|        |                               |                                         | Vddana=2.7V<br>Vref=2.0V   | -           | +/-4.1    | +/-6    |       |  |

| DNL    | Differential<br>Non Linearity | Fadc = 500 ksps                         | Vddana=5.0V<br>Vref=Vddana | -           | -0.8/+1.1 | -1/+3.8 | LSB   |  |

|        |                               |                                         | Vddana=2.7V<br>Vref=2.0V   | -           | -0.8/+1.1 | -1/+1.7 |       |  |

|        |                               | Fadc = 1 Msps                           | Vddana=5.0V<br>Vref=Vddana | -           | -0.8/+1   | -1/+2   |       |  |

|        |                               |                                         | Vddana=2.7V<br>Vref=2.0V   | -           | -1/+1.1   | -1/+2.4 |       |  |

| Gain   | Gain Error <sup>(1)</sup>     | Gain Error <sup>(1)</sup> Fadc = 1 Msps | Vddana=2.7V<br>Vref=2.0V   | -           | +/-13     | +/-28   | mV    |  |

|        |                               |                                         | Vddana=5.0V<br>Vref=4.096V | -           | +/-26     | +/-52   |       |  |

|        |                               |                                         | Vddana=3.0V<br>Vref=Vddana | -           | +/-14     | +/-24   |       |  |

|        |                               |                                         | Vddana=5.0V<br>Vref=Vddana |             | +/-22     | +/-42   |       |  |

| TCg    | Gain Drift                    | Fadc = 1 Msps                           | Vddana=5.0V<br>Vref=Vddana | -170        | -140      | -80     | uV/°C |  |

| Offset | Offset Error <sup>(1)</sup>   | Fadc = 1 Msps                           | Vddana=2.7V<br>Vref=2.0V   | -           | +/-2.2    | +/-21   | mV    |  |

|        |                               |                                         | Vddana=5.0V<br>Vref=4.096V | -           | +/-2.3    | +/-61   |       |  |

|        |                               |                                         | Vddana=3.0V<br>Vref=Vddana | -           | +/-15     | +/-42   |       |  |

|        |                               |                                         | Vddana=5.0V<br>Vref=Vddana |             | +/-31     | +/-80   |       |  |

| Тсо    | Offset Drift                  | Fadc = 1 Msps                           | Vddana=5.0V<br>Vref=Vddana | 160         | 180       | 210     | µV/°C |  |

| Symbol | Parameter                 | Conditions    | Min. | Тур. | Max  | Units   |

|--------|---------------------------|---------------|------|------|------|---------|

|        |                           | F = 4 MHz     | -    | -    | 20   |         |

|        |                           | F = 8 MHz     | -    | -    | 20   |         |

|        |                           | F = 16 MHz    | -    | -    | 20   |         |

|        |                           | F = 32 MHz    | -    | -    | 18   |         |

| ESR    | Crystal Equivalent Series | F = 0.455 MHz | -    | -    | 443  | Ω       |

|        | Resistance - SF = 3       | CL = 100pF    |      |      |      |         |

|        |                           | XOSC.GAIN = 0 |      |      |      |         |

|        |                           | F = 2MHz      | -    | -    | 383  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=0   |      |      |      |         |

|        |                           | F = 4MHz      | -    | _    | 218  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=1   |      |      |      |         |

|        |                           | F = 8MHz      | -    | -    | 114  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=2   |      |      |      |         |

|        |                           | F = 16MHz     | _    | _    | 61   |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=3   |      |      |      |         |

|        |                           | F = 32MHz     | -    | _    | 41   |         |

|        |                           | CL=18pF       |      |      |      |         |

|        |                           | XOSC.GAIN=4   |      |      |      |         |

| Cxin   | Parasitic load capacitor  |               | -    | 5.9  | _    | - pF    |

| Cxout  | _                         |               | -    | 3.1  | -    |         |

| Tstart | Startup time              | F = 2MHz      | -    | 12.3 | 35.3 | KCycles |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=0   |      |      |      |         |

|        |                           | F = 4MHz      | -    | 8.2  | 21.4 |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=1   |      |      |      |         |

|        |                           | F = 8MHz      | -    | 6.2  | 14.3 |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | •             |      |      |      |         |