# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Dectano                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 10x12b, 1x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-VQFN (5x5)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21e18a-mnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 19.8.2 Standby Configuration

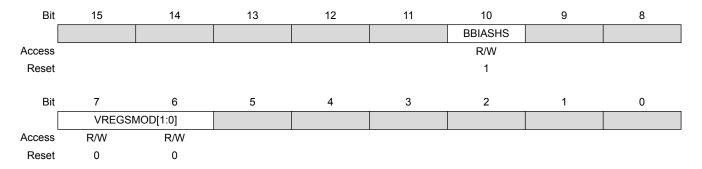

Name:STDBYCFGOffset:0x08 [ID-00000a2f]Reset:0x0400Property:PAC Write-Protection

### Bit 10 – BBIASHS: Back Bias for HMCRAMCHS

Refer to RAM Automatic Low Power Mode for details.

| Value | Description               |

|-------|---------------------------|

| 0     | No Back Biasing Mode      |

| 1     | Standby Back Biasing Mode |

### Bits 7:6 – VREGSMOD[1:0]: VREG Switching Mode

Refer to for Regulator Automatic Low Power Mode details.

| Value | Name        | Description                    |

|-------|-------------|--------------------------------|

| 0x0   | AUTO        | Automatic Mode                 |

| 0x1   | PERFORMANCE | Performance oriented           |

| 0x2   | LP          | Low Power consumption oriented |

| 0x9   | Reserved    | Reserved                       |

| CPU Mode | OSC48MCTRL.RUN<br>STDBY | OSC48MCTRL.OND<br>EMAND | Sleep Behavior                 |

|----------|-------------------------|-------------------------|--------------------------------|

| Standby  | 1                       | 1                       | Run if requested by peripheral |

| Standby  | 0                       | -                       | Run if requested by peripheral |

After a hard reset, or when waking up from a sleep mode where the OSC48M was disabled, the OSC48M will need a certain amount of time to stabilize on the correct frequency. This start-up time can be configured by changing the Oscillator Start-Up Delay bit group (OSC48MSTUP.STARTUP) in the OSC48M Startup register. During the start-up time, the oscillator output is masked to ensure that no unstable clock propagates to the digital logic. The OSC48M Ready bit in the Status register (STATUS.OSC48MRDY) is set when the oscillator is stable and ready to be used as a clock source. An interrupt is generated on a zero-to-one transition on STATUS.OSC48MRDY if the OSC48M Ready bit in the Interrupt Enable Set register (INTENSET.OSC48MRDY) is set.

Faster start-up times are achievable by selecting shorter delays. However, the oscillator frequency may not stabilize within tolerances when short delays are used. If a fast start-up time is desired at the expense of initial accuracy, the division factor should be set to two or higher (OSC48MDIV.DIV > 0).

The OSC48M is used as a clock source for the generic clock generators.

### **Related Links**

### GCLK - Generic Clock Controller

### 20.6.5 Digital Phase Locked Loop (DPLL) Operation

The task of the DPLL is to maintain coherence between the input (reference) signal and the respective output frequency, CLK\_DPLL, via phase comparison. The DPLL controller supports three independent sources of reference clocks:

- XOSC32K: this clock is provided by the 32K External Crystal Oscillator (XOSC32K).

- XOSC: this clock is provided by the External Multipurpose Crystal Oscillator (XOSC).

- GCLK: this clock is provided by the Generic Clock Controller.

When the controller is enabled, the relationship between the reference clock frequency and the output clock frequency is:

$$f_{\rm CK} = f_{\rm CKR} \times \left( {\rm LDR} + 1 + \frac{{\rm LDRFRAC}}{16} \right) \times \frac{1}{2^{\rm PRESC}}$$

Where  $f_{CK}$  is the frequency of the DPLL output clock, LDR is the loop divider ratio integer part, LDRFRAC is the loop divider ratio fractional part,  $f_{CKR}$  is the frequency of the selected reference clock, and PRESC is the output prescaler value.

If the ONDEMAND bit has been previously written to '1', the oscillator will be running only when requested by a peripheral. If there is no peripheral requesting the oscillator's clock source, the oscillator will be in a disabled state.

If On Demand is disabled, the oscillator will always be running when enabled.

In standby sleep mode, the On Demand operation is still active.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The oscillator is always on, if enabled.                                                       |

| 1     | The oscillator is enabled when a peripheral is requesting the oscillator to be used as a clock |

|       | source. The oscillator is disabled if no peripheral is requesting the clock source.            |

### Bit 6 – RUNSTDBY: Run in Standby

This bit controls how the XOSC behaves during standby sleep mode, together with the ONDEMAND bit:

| Value | Description                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC is not running in Standby sleep mode if no peripheral requests the clock.                                                                                                                          |

| 1     | The XOSC is running in Standby sleep mode. If ONDEMAND=1, the XOSC will be running when a peripheral is requesting the clock. If ONDEMAND=0, the clock source will always be running in Standby sleep mode. |

### Bit 4 – SWBACK: Clock Switch Back

This bit controls the XOSC output switch back to the external clock or crystal oscillator in case of clock recovery:

| Value | Description                                                                                                                                  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The clock switch back is disabled.                                                                                                           |

| 1     | The clock switch back is enabled. This bit is reset once the XOSC putput clock is switched back to the external clock or crystal oscillator. |

### Bit 3 – CFDEN: Clock Failure Detector Enable

This bit controls the clock failure detector:

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Clock Failure Detector is disabled. |

| 1     | the Clock Failure Detector is enabled.  |

### Bit 2 – XTALEN: Crystal Oscillator Enable

This bit controls the connections between the I/O pads and the external clock or crystal oscillator:

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | External clock connected on XIN. XOUT can be used as general-purpose I/O. |

| 1     | Crystal connected to XIN/XOUT.                                            |

### Bit 1 – ENABLE: Oscillator Enable

| Value | Description                 |

|-------|-----------------------------|

| 0     | The oscillator is disabled. |

| 1     | The oscillator is enabled.  |

### 20.8.6 Clock Failure Detector Prescaler

## SAM C20/C21

| Bit             | 31  | 30       | 29       | 28    | 27     | 26     | 25     | 24     |

|-----------------|-----|----------|----------|-------|--------|--------|--------|--------|

| Access<br>Reset |     |          |          |       |        |        |        |        |

| Bit             | 23  | 22       | 21       | 20    | 19     | 18     | 17     | 16     |

|                 |     |          |          |       | LEVE   | L[5:0] |        |        |

| Access          |     |          | R/W      | R/W   | R/W    | R/W    | R/W    | R/W    |

| Reset           |     |          | х        | x     | x      | х      | x      | х      |

| Bit             | 15  | 14       | 13       | 12    | 11     | 10     | 9      | 8      |

|                 |     | PSEI     | _[3:0]   |       |        |        |        | ACTCFG |

| Access          | R/W | R/W      | R/W      | R/W   |        |        |        | R/W    |

| Reset           | 0   | 0        | 0        | 0     |        |        |        | 0      |

|                 |     |          |          |       |        |        |        |        |

| Bit             | 7   | 6        | 5        | 4     | 3      | 2      | 1      | 0      |

|                 |     | RUNSTDBY | STDBYCFG | ACTIC | N[1:0] | HYST   | ENABLE |        |

| Access          |     | R/W      | R/W      | R/W   | R/W    | R/W    | R/W    |        |

| Reset           |     | 0        | 0        | x     | x      | x      | x      |        |

### Bits 21:16 – LEVEL[5:0]: BODVDD Threshold Level on VDD

These bits set the triggering voltage threshold for the BODVDD when the BODVDD monitors the VDD.

These bits are loaded from NVM User Row at start-up.

This bit field is not synchronized.

### Bits 15:12 – PSEL[3:0]: Prescaler Select

Selects the prescaler divide-by output for the BODVDD sampling mode. The input clock comes from the OSCULP32K 1KHz output.

| Value | Name     | Description           |

|-------|----------|-----------------------|

| 0x0   | DIV2     | Divide clock by 2     |

| 0x1   | DIV4     | Divide clock by 4     |

| 0x2   | DIV8     | Divide clock by 8     |

| 0x3   | DIV16    | Divide clock by 16    |

| 0x4   | DIV32    | Divide clock by 32    |

| 0x5   | DIV64    | Divide clock by 64    |

| 0x6   | DIV128   | Divide clock by 128   |

| 0x7   | DIV256   | Divide clock by 256   |

| 0x8   | DIV512   | Divide clock by 512   |

| 0x9   | DIV1024  | Divide clock by 1024  |

| 0xA   | DIV2048  | Divide clock by 2048  |

| 0xB   | DIV4096  | Divide clock by 4096  |

| 0xC   | DIV8192  | Divide clock by 8192  |

| 0xD   | DIV16384 | Divide clock by 16384 |

| 0xE   | DIV32768 | Divide clock by 32768 |

| 0xF   | DIV65536 | Divide clock by 65536 |

### Bit 8 – ACTCFG: BODVDD Configuration in Active Sleep Mode

This bit is not synchronized.

of CLK\_WDT\_OSC clocks before the interrupt is generated, relative to the start of the watchdog time-out period.

The user must take caution when programming the Early Warning Offset bits. If these bits define an Early Warning interrupt generation time greater than the watchdog time-out period, the watchdog time-out system reset is generated prior to the Early Warning interrupt. Consequently, the Early Warning interrupt will never be generated.

*In window mode*, the Early Warning interrupt is generated at the start of the open window period. In a typical application where the system is in sleep mode, the Early Warning interrupt can be used to wake up and clear the Watchdog Timer, after which the system can perform other tasks or return to sleep mode.

If the WDT is operating in Normal mode with CONFIG.PER = 0x2 and EWCTRL.EWOFFSET = 0x1, the Early Warning interrupt is generated 16 CLK\_WDT\_OSC clock cycles after the start of the time-out period. The time-out system reset is generated 32 CLK\_WDT\_OSC clock cycles after the start of the watchdog timeout period.

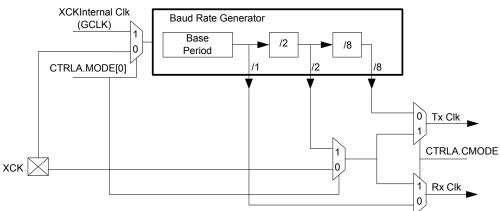

### 31.6.2.3 Clock Generation and Selection

For both synchronous and asynchronous modes, the clock used for shifting and sampling data can be generated internally by the SERCOM baud-rate generator or supplied externally through the XCK line.

The synchronous mode is selected by writing a '1' to the Communication Mode bit in the Control A register (CTRLA.CMODE), the asynchronous mode is selected by writing a zero to CTRLA.CMODE.

The internal clock source is selected by writing 0x1 to the Operation Mode bit field in the Control A register (CTRLA.MODE), the external clock source is selected by writing 0x0 to CTRLA.MODE.

The SERCOM baud-rate generator is configured as in the figure below.

In asynchronous mode (CTRLA.CMODE=0), the 16-bit Baud register value is used.

In synchronous mode (CTRLA.CMODE=1), the eight LSBs of the Baud register are used. Refer to *Clock Generation – Baud-Rate Generator* for details on configuring the baud rate.

#### Figure 31-3. Clock Generation

### **Related Links**

Clock Generation – Baud-Rate Generator Asynchronous Arithmetic Mode BAUD Value Selection

### Synchronous Clock Operation

In synchronous mode, the CTRLA.MODE bit field determines whether the transmission clock line (XCK) serves either as input or output. The dependency between clock edges, data sampling, and data change is the same for internal and external clocks. Data input on the RxD pin is sampled at the opposite XCK clock edge when data is driven on the TxD pin.

The Clock Polarity bit in the Control A register (CTRLA.CPOL) selects which XCK clock edge is used for RxD sampling, and which is used for TxD change:

When CTRLA.CPOL is '0', the data will be changed on the rising edge of XCK, and sampled on the falling edge of XCK.

When CTRLA.CPOL is '1', the data will be changed on the falling edge of XCK, and sampled on the rising edge of XCK.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

### 31.8.1 Control A

Name: CTRLA Offset: 0x00 Reset: 0x0000000 Property: PAC Write-Protection, Enable-Protected

| Bit    | 31       | 30         | 29   | 28     | 27        | 26   | 25     | 24     |

|--------|----------|------------|------|--------|-----------|------|--------|--------|

|        |          | DORD       | CPOL | CMODE  |           | FORM | A[3:0] |        |

| Access |          | R/W        | R/W  | R/W    | R/W       | R/W  | R/W    | R/W    |

| Reset  |          | 0          | 0    | 0      | 0         | 0    | 0      | 0      |

|        |          |            |      |        |           |      |        |        |

| Bit    | 23       | 22         | 21   | 20     | 19        | 18   | 17     | 16     |

|        | SAMF     | PA[1:0]    | RXP  | D[1:0] |           |      | TXPC   | D[1:0] |

| Access | R/W      | R/W        | R/W  | R/W    |           |      | R/W    | R/W    |

| Reset  | 0        | 0          | 0    | 0      |           |      | 0      | 0      |

|        |          |            |      |        |           |      |        |        |

| Bit    | 15       | 14         | 13   | 12     | 11        | 10   | 9      | 8      |

|        |          | SAMPR[2:0] |      |        |           |      |        | IBON   |

| Access | R/W      | R/W        | R/W  |        |           |      |        | R      |

| Reset  | 0        | 0          | 0    |        |           |      |        | 0      |

|        |          |            |      |        |           |      |        |        |

| Bit    | 7        | 6          | 5    | 4      | 3         | 2    | 1      | 0      |

|        | RUNSTDBY |            |      |        | MODE[2:0] |      | ENABLE | SWRST  |

| Access | R/W      |            |      | R/W    | R/W       | R/W  | R/W    | R/W    |

| Reset  | 0        |            |      | 0      | 0         | 0    | 0      | 0      |

### Bit 30 – DORD: Data Order

This bit selects the data order when a character is shifted out from the Data register.

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | MSB is transmitted first. |

| 1     | LSB is transmitted first. |

### Bit 29 – CPOL: Clock Polarity

This bit selects the relationship between data output change and data input sampling in synchronous mode.

This bit is not synchronized.

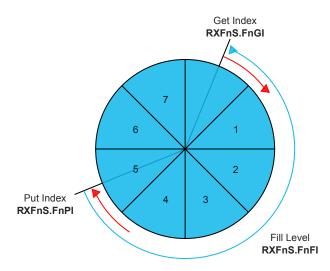

### Figure 34-7. Rx FIFO Status

When reading from an Rx FIFO, Rx FIFO Get Index RXFnS.FnGI • FIFO Element Size has to be added to the corresponding Rx FIFO start address RXFnC.FnSA.

| Table 34-3. | Rx Buffer / | FIFO Element Size |  |

|-------------|-------------|-------------------|--|

|             |             |                   |  |

| RXESC.RBDS[2:0]<br>RXESC.FnDS[2:0] | Data Field<br>[bytes] | FIFO Element Size<br>[RAM words] |

|------------------------------------|-----------------------|----------------------------------|

| 000                                | 8                     | 4                                |

| 001                                | 12                    | 5                                |

| 010                                | 16                    | 6                                |

| 011                                | 20                    | 7                                |

| 100                                | 24                    | 8                                |

| 101                                | 32                    | 10                               |

| 110                                | 48                    | 14                               |

| 111                                | 64                    | 18                               |

### **Rx FIFO Blocking Mode**

The Rx FIFO blocking mode is configured by RXFnC.FnOM = '0'. This is the default operation mode for the Rx FIFOs.

When an Rx FIFO full condition is reached (RXFnS.FnPI = RXFnS.FnGI), no further messages are written to the corresponding Rx FIFO until at least one message has been read out and the Rx FIFO Get Index has been incremented. An Rx FIFO full condition is signaled by RXFnS.FnF = '1'. In addition interrupt flag IR.RFnF is set.

In case a message is received while the corresponding Rx FIFO is full, this message is discarded and the message lost condition is signalled by RXFnS.RFnL = '1'. In addition interrupt flag IR.RFnL is set.

### **Rx FIFO Overwrite Mode**

The Rx FIFO overwrite mode is configured by RXFnC.FnOM = '1'.

| Value | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0   | NONE  | No Error: No error occurred since LEC has been reset by successful reception or transmission.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x1   | STUFF | Stuff Error: More than 5 equal bits in a sequence have occurred in a part of a received message where this is not allowed.                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x2   | FORM  | Form Error: A fixed format part of a received frame has the wrong format.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0x3   | ACK   | Ack Error: The message transmitted by the CAN was not acknowledged by another node.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0x4   | BIT1  | Bit1 Error: During the transmission of a message (with the exception of the arbitration field), the device wanted to send a recessive level (bit of logical value '1'), but the monitored bus was dominant.                                                                                                                                                                                                                                                                                                         |

| 0x5   | BITO  | Bit0 Error: During the transmission of a message (or acknowledge bit, or active error flag, or overload flag), the device wanted to send a dominant level (data or identifier bit logical value '0'), but the monitored bus value was recessive. During Bus_Off recovery this status is set each time a sequence of 11 recessive bits have been monitored. This enables the CPU to monitor the proceeding of the Bus_Off recovery sequence (indicating the bus is not stuck at dominant or continuously disturbed). |

| 0x6   | CRC   | CRC Error: The CRC checksum of a received message was incorrect. The CRC of an incoming message does not match with the CRC calculated from the received data.                                                                                                                                                                                                                                                                                                                                                      |

| 0x7   | NC    | No Change: Any read access to the Protocol Status Register re-initializes the LEC to '7'. When the LEC shows the value '7', no CAN bus event was detected since the last CPU read access to the Protocol Status Register.                                                                                                                                                                                                                                                                                           |

### 34.8.15 Transmitter Delay Compensation

This register is write-restricted and only writable if bit fields CCCR.CCE = 1 and CCCR.INIT = 1.

Name:TDCROffset:0x48 [ID-0000a4bb]Reset:0x0000000Property:Write-restricted

### Bit 26 – WDIL: Watchdog Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 25 – BOL: Bus\_Off Status Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 24 – EWL: Error Warning Status Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 23 – EPL: Error Passive Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 22 – ELOL: Error Logging Overflow Interrupt Line

| Valu | е | Description                                 |

|------|---|---------------------------------------------|

| 0    |   | Interrupt assigned to CAN interrupt line 0. |

| 1    |   | Interrupt assigned to CAN interrupt line 1. |

### Bit 21 – BEUL: Bit Error Uncorrected Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 20 – BECL: Bit Error Corrected Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 19 – DRXL: Message stored to Dedicated Rx Buffer Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

### Bit 18 – TOOL: Timeout Occurred Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

Name:SIDFCOffset:0x84 [ID-0000a4bb]Reset:0x0000000Property:Write-restricted

| 31          | 30                                           | 29                                                                                                                        | 28                                                                                                                                                                                | 27                                                                                                                                                                                                                                      | 26                                                                                                                                                                                                                                                                                                                                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23          | 22                                           | 21                                                                                                                        | 20                                                                                                                                                                                | 19                                                                                                                                                                                                                                      | 18                                                                                                                                                                                                                                                                                                                                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |                                              |                                                                                                                           | LSS                                                                                                                                                                               | [7:0]                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/W         | R/W                                          | R/W                                                                                                                       | R/W                                                                                                                                                                               | R/W                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0           | 0                                            | 0                                                                                                                         | 0                                                                                                                                                                                 | 0                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15          | 14                                           | 13                                                                                                                        | 12                                                                                                                                                                                | 11                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FLSSA[15:8] |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/W         | R/W                                          | R/W                                                                                                                       | R/W                                                                                                                                                                               | R/W                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0           | 0                                            | 0                                                                                                                         | 0                                                                                                                                                                                 | 0                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7           | 6                                            | 5                                                                                                                         | 4                                                                                                                                                                                 | 3                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FLSSA[7:0]  |                                              |                                                                                                                           |                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R/W         | R/W                                          | R/W                                                                                                                       | R/W                                                                                                                                                                               | R/W                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                                                                               | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0           | 0                                            | 0                                                                                                                         | 0                                                                                                                                                                                 | 0                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | 23<br>R/W<br>0<br>15<br>R/W<br>0<br>7<br>R/W | 23     22       R/W     R/W       0     0       15     14       R/W     R/W       0     0       7     6       R/W     R/W | 23     22     21       R/W     R/W     R/W       0     0     0       15     14     13       R/W     R/W     R/W       0     0     0       7     6     5       R/W     R/W     R/W | 23     22     21     20       LSS       R/W     R/W     R/W       0     0     0       15     14     13     12       FLSS/       R/W     R/W     R/W       0     0     0       7     6     5     4       FLSS/       R/W     R/W     R/W | 23     22     21     20     19       LSS[7:0]     LSS[7:0]       R/W     R/W     R/W     R/W       0     0     0     0       15     14     13     12     11       FLSSA[15:8]     FLSSA[15:8]       R/W     R/W     R/W     R/W       0     0     0     0       7     6     5     4     3       FLSSA[7:0]     FLSSA[7:0]     F/W | 23       22       21       20       19       18         LSS[7:0]       LSS[7:0]         R/W       R/W       R/W       R/W         0       0       0       0       0         15       14       13       12       11       10         FLSSA[15:8]         R/W       R/W       R/W       R/W         0       0       0       0       0         7       6       5       4       3       2         FLSSA[7:0]       FLSSA[7:0]       FLSSA[7:0]       FLSSA[7:0]       FLSSA[7:0] | 23       22       21       20       19       18       17         LSS[7:0]         R/W       R/W       R/W       R/W       R/W       R/W         0       0       0       0       0       0         15       14       13       12       11       10       9         FLSSA[15:8]         R/W       R/W       R/W       R/W       R/W         0       0       0       0       0       0         7       6       5       4       3       2       1         7       6       5       4       3       2       1         FLSSA[7:0]         R/W       R/W       R/W       R/W       R/W       R/W |

### Bits 23:16 – LSS[7:0]: List Size Standard

| Value   | Description                                     |

|---------|-------------------------------------------------|

| 0       | No standard Message ID filter.                  |

| 1 - 128 | Number of standard Message ID filter elements.  |

| > 128   | Values greater than 128 are interpreted as 128. |

### Bits 15:0 – FLSSA[15:0]: Filter List Standard Start Address

Start address of standard Message ID filter list. When the CAN module addresses the Message RAM it addresses 32-bit words, not single bytes. The configurable start addresses are 32-bit word addresses, i.e. only bits 15 to 2 are evaluated, the two least significant bits are ignored. Bits 1 to 0 will always be read back as "00".

### 34.8.22 Extended ID Filter Configuration

Name:XIDFCOffset:0x88 [ID-0000a4bb]Reset:0x00000000Property:Write-restricted

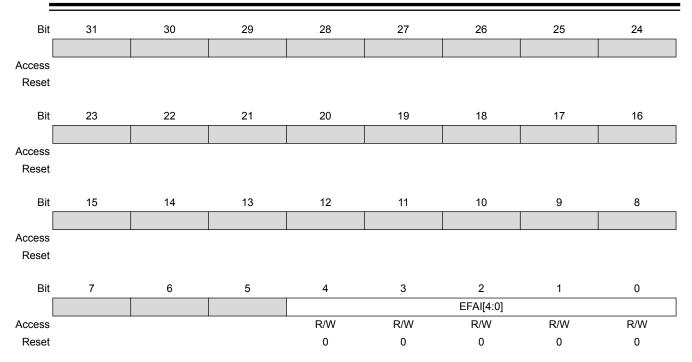

## SAM C20/C21

### Bits 4:0 – EFAI[4:0]: Event FIFO Acknowledge Index

After the Host has read an element or a sequence of elements from the Tx Event FIFO it has to write the index of the last element read from Tx Event FIFO to EFAI. This will set the Tx Event FIFO Get Index TXEFS.EFGI to EFAI + 1 and update the FIFO 0 Fill Level TXEFS.EFFL.

### 34.9 Message RAM

For storage of Rx/Tx messages and for storage of the filter configuration a single- or dual-ported Message RAM has to be connected to the CAN module.

### 34.9.1 Message RAM Configuration

The Message RAM has a width of 32 bits. In case parity checking or ECC is used a respective number of bits has to be added to each word. The CAN module can be configured to allocate up to 4352 words in the Message RAM. It is not necessary to configure each of the sections listed in the figure below, nor is there any restriction with respect to the sequence of the sections.

When operated in CAN FD mode the required Message RAM size strongly depends on the element size configured for Rx FIFO 0, Rx FIFO 1, Rx Buffers, and Tx Buffers via RXESC.F0DS, RXESC.F1DS, RXESC.RBDS, and TXESC.TBDS.

This register allows the user to clear bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Set register (CTRLBSET).

Name:CTRLBCLROffset:0x04Reset:0x00Property:PAC Write-Protection, Read-Synchronized, Write-Synchronized

| Bit    | 7   | 6        | 5   | 4 | 3 | 2       | 1    | 0   |

|--------|-----|----------|-----|---|---|---------|------|-----|

| [      |     | CMD[2:0] |     |   |   | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W |   |   | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   |   |   | 0       | 0    | 0   |

### Bits 7:5 – CMD[2:0]: Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a '1' to any of these bits will clear the pending command.

### Bit 2 – ONESHOT: One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect

Writing a '1' to this bit will disable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

### Bit 1 – LUPD: Lock Update

This bit controls the update operation of the TC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

This bit has no effect when input capture operation is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the LUPD bit.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The CCBUFx and PERBUF buffer registers value are copied into CCx and PER registers on  |

|       | hardware update condition.                                                             |

| 1     | The CCBUFx and PERBUF buffer registers value are not copied into CCx and PER registers |

|       | on hardware update condition.                                                          |

### Bit 0 – DIR: Counter Direction

This bit is used to change the direction of the counter.

## **36.** TCC – Timer/Counter for Control Applications

### 36.1 Overview

The device provides three instances of the Timer/Counter for Control applications (TCC) peripheral, TCC[2:0].

Each TCC instance consists of a counter, a prescaler, compare/capture channels and control logic. The counter can be set to count events or clock pulses. The counter together with the compare/capture channels can be configured to time stamp input events, allowing capture of frequency and pulse-width. It can also perform waveform generation such as frequency generation and pulse-width modulation.

Waveform extensions are featured for motor control, ballast, LED, H-bridge, power converters, and other types of power control applications. They allow for low- and high-side output with optional dead-time insertion. Waveform extensions can also generate a synchronized bit pattern across the waveform output pins. The fault options enable fault protection for safe and deterministic handling, disabling and/or shut down of external drivers.

Figure 36-1 shows all features in TCC.

**Note:** The TCC configurations, such as channel numbers and features, may be reduced for some of the TCC instances.

### **Related Links**

**TCC Configurations**

### 36.2 Features

- Up to four compare/capture channels (CC) with:

- Double buffered period setting

- Double buffered compare or capture channel

- Circular buffer on period and compare channel registers

- Waveform generation:

- Frequency generation

- Single-slope pulse-width modulation (PWM)

- Dual-slope pulse-width modulation with half-cycle reload capability

- Input capture:

- Event capture

- Frequency capture

- Pulse-width capture

- Waveform extensions:

- Configurable distribution of compare channels outputs across port pins

- Low- and high-side output with programmable dead-time insertion

- Waveform swap option with double buffer support

- Pattern generation with double buffer support

- Dithering support

- Fault protection for safe disabling of drivers:

- Two recoverable fault sources

### **Fault Actions**

Different fault actions can be configured individually for Fault A and Fault B. Most fault actions are not mutually exclusive; hence two or more actions can be enabled at the same time to achieve a result that is a combination of fault actions.

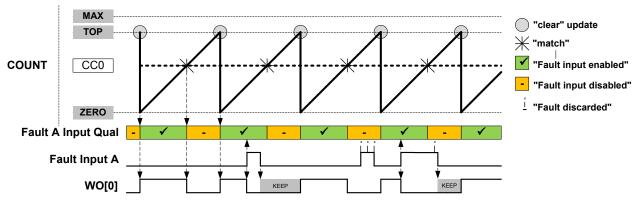

KeepThis is enabled by writing the Fault n Keeper bit in the Recoverable Fault n ConfigurationActionregister (FCTRLn.KEEP) to '1'. When enabled, the corresponding channel output will be<br/>clamped to zero as long as the fault condition is present. The clamp will be released on the<br/>start of the first cycle after the fault condition is no longer present, see next Figure.

Figure 36-25. Waveform Generation with Fault Qualification and Keep Action