#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b, 2x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21g15a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

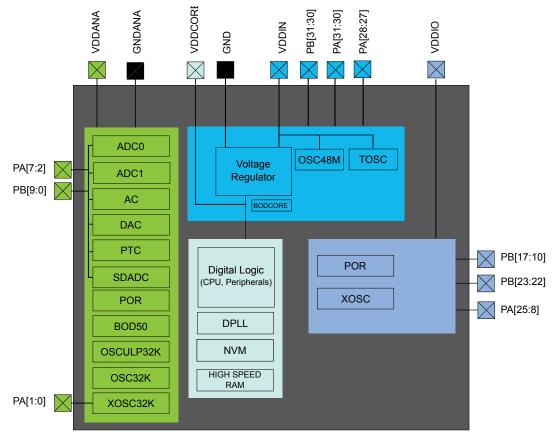

# 7. Power Supply and Start-Up Considerations

# 7.1 Power Domain Overview

Figure 7-1. Power Domain Overview, SAM C20/C21 E/G/J

This flag is cleared by writing a one to the flag.

This flag is set when a Peripheral Access Error occurs while accessing the peripheral associated with the respective INTFLAGD bit, and will generate an interrupt request if INTENCLR/SET.ERR is one.

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the corresponding INTFLAGD interrupt flag.

Name:

INTFLAGD

Offset:

0x20 [ID-00000a18]

Reset:

0x000000

Property:

| Bit    | 31 | 30 | 29 | 28  | 27  | 26  | 25      | 24      |

|--------|----|----|----|-----|-----|-----|---------|---------|

|        |    |    |    |     |     |     |         |         |

| Access |    |    |    |     | -   |     |         |         |

| Reset  |    |    |    |     |     |     |         |         |

|        |    |    |    |     |     |     |         |         |

| Bit    | 23 | 22 | 21 | 20  | 19  | 18  | 17      | 16      |

|        |    |    |    |     |     |     |         |         |

| Access |    |    |    |     |     |     |         |         |

| Reset  |    |    |    |     |     |     |         |         |

|        |    |    |    |     |     |     |         |         |

| Bit    | 15 | 14 | 13 | 12  | 11  | 10  | 9       | 8       |

|        |    |    |    |     |     |     |         |         |

| Access |    |    |    |     |     |     |         |         |

| Reset  |    |    |    |     |     |     |         |         |

| Dit    | 7  | 0  | _  |     | 0   | 0   | 1       | 0       |

| Bit    | 7  | 6  | 5  | 4   | 3   | 2   | 1       | 0       |

|        |    |    |    | TC7 | TC6 | TC5 | SERCOM7 | SERCOM6 |

| Access |    |    |    | R/W | R/W | R/W | R/W     | R/W     |

| Reset  |    |    |    | 0   | 0   | 0   | 0       | 0       |

|        |    |    |    |     |     |     |         |         |

Bits 2, 3, 4 – TC5, TC6, TC7: Interrupt Flag for TCn [n = 7..5]

Bits 0, 1 – SERCOM6, SERCOM7: Interrupt Flag for SERCOMn [n = 7..6]

#### 11.7.10 Peripheral Write Protection Status A

Writing to this register has no effect.

Reading STATUS register returns peripheral write protection status:

| Value | Description                        |

|-------|------------------------------------|

| 0     | Peripheral is not write protected. |

| 1     | Peripheral is write protected.     |

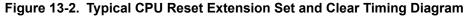

# 13.6.2 CPU Reset Extension

"CPU reset extension" refers to the extension of the reset phase of the CPU core after the external reset is released. This ensures that the CPU is not executing code at startup while a debugger is connects to the system. The debugger is detected on a RESET release event when SWCLK is low. At startup, SWCLK is internally pulled up to avoid false detection of a debugger if the SWCLK pin is left unconnected. When the CPU is held in the reset extension phase, the CPU Reset Extension bit of the Status A register (STATUSA.CRSTEXT) is set. To release the CPU, write a '1' to STATUSA.CRSTEXT. STATUSA.CRSTEXT will then be set to '0'. Writing a '0' to STATUSA.CRSTEXT has no effect. For security reasons, it is not possible to release the CPU reset extension when the device is protected by the NVMCTRL security bit. Trying to do so sets the Protection Error bit (PERR) of the Status A register (STATUSA.PERR).

# **Related Links**

NVMCTRL – Non-Volatile Memory Controller Security Bit

# 13.6.3 Debugger Probe Detection

# 13.6.3.1 Cold Plugging

Cold-Plugging is the detection of a debugger when the system is in reset. Cold-Plugging is detected when the CPU reset extension is requested, as described above.

# 13.6.3.2 Hot Plugging

Hot-Plugging is the detection of a debugger probe when the system is not in reset. Hot-Plugging is not possible under reset because the detector is reset when POR or RESET are asserted. Hot-Plugging is active when a SWCLK falling edge is detected. The SWCLK pad is multiplexed with other functions and the user must ensure that its default function is assigned to the debug system. If the SWCLK function is changed, the Hot-Plugging feature is disabled until a power-reset or external reset occurs. Availability of the Hot-Plugging feature can be read from the Hot-Plugging Enable bit of the Status B register (STATUSB.HPE).

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24    |

|--------|----|----|----|----|----|----|----|-------|

|        |    |    |    |    |    |    |    |       |

| Access |    |    |    |    |    |    |    |       |

| Reset  |    |    |    |    |    |    |    |       |

|        |    |    |    |    |    |    |    |       |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16    |

|        |    |    |    |    |    |    |    |       |

| Access |    |    |    |    |    |    |    |       |

| Reset  |    |    |    |    |    |    |    |       |

|        |    |    |    |    |    |    |    |       |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     |

|        |    |    |    |    |    |    |    |       |

| Access |    |    |    |    |    |    |    |       |

| Reset  |    |    |    |    |    |    |    |       |

|        |    |    |    |    |    |    |    |       |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0     |

|        |    |    |    |    |    |    |    | SMEMP |

| Access |    |    |    |    |    |    |    | R     |

| Reset  |    |    |    |    |    |    |    | x     |

### Bit 0 – SMEMP: System Memory Present

This bit indicates whether system memory is present on the bus that connects to the ROM table.

This bit is set at power-up if the device is not protected, indicating that the system memory is accessible from a debug adapter.

This bit is cleared at power-up if the device is protected, indicating that the system memory is not accessible from a debug adapter.

### 13.13.14 Peripheral Identification 4

Name:

PID4

Offset:

0x1FD0

Reset:

0x0000000

Property:

# SAM C20/C21

| Offset       | Name      | Bit Pos.       |         |         |          |        |       |     |                |       |

|--------------|-----------|----------------|---------|---------|----------|--------|-------|-----|----------------|-------|

| 0x41         |           | 15:8           |         |         | RUNSTDBY | DIVSEL | OE    | OOV | IDC            | GENEN |

| 0x42         |           | 23:16          |         |         |          | DIV[   | 7:0]  |     | 1              |       |

| 0x43         |           | 31:24          |         |         |          | DIV[1  | 15:8] |     |                |       |

| 0x44         |           |                |         |         |          |        |       |     |                |       |

|              | Reserved  |                |         |         |          |        |       |     |                |       |

| 0x7F         |           |                |         |         |          |        |       |     |                |       |

| 0x80         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0x81         | PCHCTRL0  | 15:8           |         |         |          |        |       |     |                |       |

| 0x82         |           | 23:16          |         |         |          |        |       |     |                |       |

| 0x83         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0x84         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0x85         | PCHCTRL1  | 15:8           |         |         |          |        |       |     |                |       |

| 0x86         |           | 23:16          |         |         |          |        |       |     |                |       |

| 0x87         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0x88         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0x89         | PCHCTRL2  | 15:8           |         |         |          |        |       |     |                |       |

| 0x8A         |           | 23:16          |         |         |          |        |       |     |                |       |

| 0x8B         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0x8C         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0x8D         | PCHCTRL3  | 15:8           |         |         |          |        |       |     |                |       |

| 0x8E         | -         | 23:16          |         |         |          |        |       |     |                |       |

| 0x8F         |           | 31:24          |         | OUEN    |          |        |       | 051 | 1[2-0]         |       |

| 0x90         | PCHCTRL4  | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>J</b> [3:0] |       |

| 0x91         |           | 15:8           |         |         |          |        |       |     |                |       |

| 0x92<br>0x93 |           | 23:16<br>31:24 |         |         |          |        |       |     |                |       |

| 0x93<br>0x94 |           | 7:0            | WRTLOCK | CHEN    |          |        |       |     | J[3:0]         |       |

| 0x94         |           | 15:8           | WRILOCK | CHEN    |          |        |       | GLI | 4[J.U]         |       |

| 0x96         | PCHCTRL5  | 23:16          |         |         |          |        |       |     |                |       |

| 0x97         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0x98         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | J[3:0]         |       |

| 0x99         |           | 15:8           |         | 0.1.E.N |          |        |       |     | .[0.0]         |       |

| 0x9A         | PCHCTRL6  | 23:16          |         |         |          |        |       |     |                |       |

| 0x9B         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0x9C         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>J</b> [3:0] |       |

| 0x9D         |           | 15:8           |         |         |          |        |       |     | -              |       |

| 0x9E         | PCHCTRL7  | 23:16          |         |         |          |        |       |     |                |       |

| 0x9F         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0xA0         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0xA1         | DOLLOTT   | 15:8           |         |         |          |        |       |     |                |       |

| 0xA2         | PCHCTRL8  | 23:16          |         |         |          |        |       |     |                |       |

| 0xA3         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0xA4         |           | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| 0xA5         |           | 15:8           |         |         |          |        |       |     |                |       |

| 0xA6         | PCHCTRL9  | 23:16          |         |         |          |        |       |     |                |       |

| 0xA7         |           | 31:24          |         |         |          |        |       |     |                |       |

| 0xA8         | PCHCTRL10 | 7:0            | WRTLOCK | CHEN    |          |        |       | GEN | <b>I</b> [3:0] |       |

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | XOSC is not switched and provides the external clock or crystal oscillator clock. |

| 1     | XOSC is switched and provides the safe clock.                                     |

# Bit 1 – CLKFAIL: XOSC Clock Failure

| Value | Description                  |

|-------|------------------------------|

| 0     | No XOSC failure detected.    |

| 1     | A XOSC failure was detected. |

#### Bit 0 – XOSCRDY: XOSC Ready

| Ν | /alue | Description                                            |

|---|-------|--------------------------------------------------------|

| C |       | XOSC is not ready.                                     |

| 1 |       | XOSC is stable and ready to be used as a clock source. |

### 20.8.5 External Multipurpose Crystal Oscillator (XOSC) Control

Name:XOSCCTRLOffset:0x10 [ID-00001eee]Reset:0x0080Property:PAC Write-Protection

| Bit    | 15       | 14       | 13      | 12     | 11    | 10     | 9         | 8   |

|--------|----------|----------|---------|--------|-------|--------|-----------|-----|

|        |          | START    | UP[3:0] |        | AMPGC |        | GAIN[2:0] |     |

| Access | R/W      | R/W      | R/W     | R/W    | R/W   | R/W    | R/W       | R/W |

| Reset  | 0        | 0        | 0       | 0      | 0     | 0      | 0         | 0   |

|        |          |          |         |        |       |        |           |     |

| Bit    | 7        | 6        | 5       | 4      | 3     | 2      | 1         | 0   |

|        | ONDEMAND | RUNSTDBY |         | SWBACK | CFDEN | XTALEN | ENABLE    |     |

| Access | R/W      | R/W      |         | R/W    | R/W   | R/W    | R/W       |     |

| Reset  | 1        | 0        |         | 0      | 0     | 0      | 0         |     |

#### Bits 15:12 - STARTUP[3:0]: Start-Up Time

These bits select start-up time for the oscillator.

The OSCULP32K oscillator is used to clock the start-up counter.

# Table 20-5. Start-Up Time for External Multipurpose Crystal Oscillator

| STARTUP[3:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC<br>Clock Cycles | Approximate Equivalent<br>Time [µs] |

|--------------|-------------------------------------|--------------------------------|-------------------------------------|

| 0x0          | 1                                   | 3                              | 31                                  |

| 0x1          | 2                                   | 3                              | 61                                  |

| 0x2          | 4                                   | 3                              | 122                                 |

| 0x3          | 8                                   | 3                              | 244                                 |

| 0x4          | 16                                  | 3                              | 488                                 |

| 0x5          | 32                                  | 3                              | 977                                 |

# 21. OSC32KCTRL – 32KHz Oscillators Controller

# 21.1 Overview

The 32KHz Oscillators Controller (OSC32KCTRL) provides a user interface to the 32.768kHz oscillators: XOSC32K, OSC32K, and OSCULP32K.

The OSC32KCTRL sub-peripherals can be enabled, disabled, calibrated, and monitored through interface registers.

All sub-peripheral statuses are collected in the Status register (STATUS). They can additionally trigger interrupts upon status changes via the INTENSET, INTENCLR, and INTFLAG registers.

# 21.2 Features

- 32.768kHz Crystal Oscillator (XOSC32K)

- Programmable start-up time

- Crystal or external input clock on XIN32 I/O

- Clock failure detection with safe clock switch

- Clock failure event output

- 32.768kHz High Accuracy Internal Oscillator (OSC32K)

- Frequency fine tuning

- Programmable start-up time

- 32.768kHz Ultra Low Power Internal Oscillator (OSCULP32K)

- Ultra low power, always-on oscillator

- Frequency fine tuning

- Calibration value loaded from Flash factory calibration at reset

- 1.024kHz clock outputs available

# Bit 2 – VREFOE: Voltage Reference Output Enable

| Value | Description                                                            |

|-------|------------------------------------------------------------------------|

| 0     | The Voltage Reference output is not available as an ADC input channel. |

| 1     | The Voltage Reference output is routed to an ADC input channel.        |

# Bit 1 – TSEN: Temperature Sensor Enable

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | Temperature Sensor is disabled.                                   |

| 1     | Temperature Sensor is enabled and routed to an ADC input channel. |

## 23.6.7 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following registers are synchronized when written:

- Enable bit in Control A register (CTRLA.ENABLE)

- Window Enable bit in Control A register (CTRLA.WEN)

- Always-On bit in control Control A (CTRLA.ALWAYSON)

The following registers are synchronized when read:

• Watchdog Clear register (CLEAR)

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

Required read-synchronization is denoted by the "Read-Synchronized" property in the register description.

#### 23.6.8 Additional Features

#### 23.6.8.1 Always-On Mode

The Always-On mode is enabled by setting the Always-On bit in the Control A register (CTRLA.ALWAYSON=1). When the Always-On mode is enabled, the WDT runs continuously, regardless of the state of CTRLA.ENABLE. Once written, the Always-On bit can only be cleared by a power-on reset. The Configuration (CONFIG) and Early Warning Control (EWCTRL) registers are read-only registers while the CTRLA.ALWAYSON bit is set. Thus, the time period configuration bits (CONFIG.PER, CONFIG.WINDOW, EWCTRL.EWOFFSET) of the WDT cannot be changed.

Enabling or disabling Window mode operation by writing the Window Enable bit (CTRLA.WEN) is allowed while in Always-On mode, but note that CONFIG.PER cannot be changed.

The Interrupt Clear and Interrupt Set registers are accessible in the Always-On mode. The Early Warning interrupt can still be enabled or disabled while in the Always-On mode, but note that EWCTRL.EWOFFSET cannot be changed.

Table WDT Operating Modes With Always-On shows the operation of the WDT for CTRLA.ALWAYSON=1.

| WEN | Interrupt Enable | Mode                                                   |

|-----|------------------|--------------------------------------------------------|

| 0   | 0                | Always-on and normal mode                              |

| 0   | 1                | Always-on and normal mode with Early Warning interrupt |

| 1   | 0                | Always-on and window mode                              |

| 1   | 1                | Always-on and window mode with Early Warning interrupt |

Table 23-2. WDT Operating Modes With Always-On

#### 23.6.8.2 Early Warning

The Early Warning interrupt notifies that the WDT is approaching its time-out condition. The Early Warning interrupt behaves differently in Normal mode and in Window mode.

*In Normal mode*, the Early Warning interrupt generation is defined by the Early Warning Offset in the Early Warning Control register (EWCTRL.EWOFFSET). The Early Warning Offset bits define the number

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|--------|------|------|------|------|------|------|------|------|

|        | OVF  |      |      |      |      |      | CMPn | CMPn |

| Access | R/W  |      |      | ·    |      |      | R/W  | R/W  |

| Reset  | 0    |      |      |      |      |      | 0    | 0    |

|        |      |      |      |      |      |      |      |      |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|        | PERn |

| Access | R/W  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# Bit 15 - OVF: Overflow

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after an overflow condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

### Bits 9:8 – CMPn: Compare n [n = 1..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with the compare condition, and an interrupt request will be generated if INTENCLR/SET.COMPn is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Compare n interrupt flag.

#### Bits 7:0 – PERn: Periodic Interval n [n = 7..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the 0-to-1 transition of prescaler bit [n+2], and an interrupt request will be generated if INTENCLR/SET.PERx is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Periodic Interval n interrupt flag.

#### 24.10.6 Debug Control

Name: DBGCTRL Offset: 0x0E Reset: 0x00 Property: PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

# Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

# 24.12.11 Alarm Mask in Clock/Calendar mode (CTRLA.MODE=2)

Name:MASKOffset:0x24Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1        | 0   |

|--------|---|---|---|---|---|-----|----------|-----|

|        |   |   |   |   |   |     | SEL[2:0] |     |

| Access |   |   |   |   |   | R/W | R/W      | R/W |

| Reset  |   |   |   |   |   | 0   | 0        | 0   |

## Bits 2:0 – SEL[2:0]: Alarm Mask Selection

These bits define which bit groups of ALARM are valid.

| Value | Name         | Description                                            |

|-------|--------------|--------------------------------------------------------|

| 0x0   | OFF          | Alarm Disabled                                         |

| 0x1   | SS           | Match seconds only                                     |

| 0x2   | MMSS         | Match seconds and minutes only                         |

| 0x3   | HHMMSS       | Match seconds, minutes, and hours only                 |

| 0x4   | DDHHMMSS     | Match seconds, minutes, hours, and days only           |

| 0x5   | MMDDHHMMSS   | Match seconds, minutes, hours, days, and months only   |

| 0x6   | YYMMDDHHMMSS | Match seconds, minutes, hours, days, months, and years |

| 0x7   | -            | Reserved                                               |

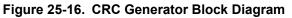

**CRC on** CRC-16 or CRC-32 calculations can be performed on data passing through any DMA

DMA channel. Once a DMA channel is selected as the source, the CRC engine will continuously generate the CRC on the data passing through the DMA channel. The checksum is available for readout once the DMA transaction is completed or aborted. A CRC can also be generated on SRAM, Flash, or I/O memory by passing these data through a DMA channel. If the latter is done, the destination register for the DMA data can be the data input (CRCDATAIN) register in the CRC engine.

CRC using the I/OBefore using the CRC engine with the I/O interface, the application must set the<br/>CRC Beat Size bits in the CRC Control register (CRCCTRL.CRCBEATSIZE).<br/>8/16/32-bit bus transfer type can be selected.

CRC can be performed on any data by loading them into the CRC engine using the CPU and writing the data to the CRCDATAIN register. Using this method, an arbitrary number of bytes can be written to the register by the CPU, and CRC is done continuously for each byte. This means if a 32-bit data is written to the CRCDATAIN register the CRC engine takes four cycles to calculate the CRC. The CRC complete is signaled by a set CRCBUSY bit in the CRCSTATUS register. New data can be written only when CRCBUSY flag is not set.

# 25.6.4 DMA Operation

Not applicable.

| Bit    | 31       | 30 | 29 | 28 | 27           | 26    | 25       | 24  |  |

|--------|----------|----|----|----|--------------|-------|----------|-----|--|

|        | RRLVLEN3 |    |    |    |              | LVLPF | RI3[3:0] |     |  |

| Access | R/W      |    |    |    | R/W          | R/W   | R/W      | R/W |  |

| Reset  | 0        |    |    |    | 0            | 0     | 0        | 0   |  |

|        |          |    |    |    |              |       |          |     |  |

| Bit    | 23       | 22 | 21 | 20 | 19           | 18    | 17       | 16  |  |

|        | RRLVLEN2 |    |    |    |              | LVLPF | RI2[3:0] |     |  |

| Access | R/W      | •  | •  |    | R/W          | R/W   | R/W      | R/W |  |

| Reset  | 0        |    |    |    | 0            | 0     | 0        | 0   |  |

|        |          |    |    |    |              |       |          |     |  |

| Bit    | 15       | 14 | 13 | 12 | 11           | 10    | 9        | 8   |  |

|        | RRLVLEN1 |    |    |    |              | LVLPF | RI1[3:0] |     |  |

| Access | R/W      | •  | •  |    | R/W          | R/W   | R/W      | R/W |  |

| Reset  | 0        |    |    |    | 0            | 0     | 0        | 0   |  |

|        |          |    |    |    |              |       |          |     |  |

| Bit    | 7        | 6  | 5  | 4  | 3            | 2     | 1        | 0   |  |

|        | RRLVLEN0 |    |    |    | LVLPRI0[3:0] |       |          |     |  |

| Access | R/W      |    |    |    | R/W          | R/W   | R/W      | R/W |  |

| Reset  | 0        |    |    |    | 0            | 0     | 0        | 0   |  |

#### Bit 31 – RRLVLEN3: Level 3 Round-Robin Arbitration Enable

This bit controls which arbitration scheme is selected for DMA channels with priority level 3. For details on arbitration schemes, refer to Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 3 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 3 priority. |

#### Bits 27:24 – LVLPRI3[3:0]: Level 3 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN3=1) for priority level 3, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 3.

When static arbitration is enabled (PRICTRL0.RRLVLEN3=0) for priority level 3, and the value of this bit group is non-zero, it will not affect the static priority scheme.

This bit group is not reset when round-robin arbitration gets disabled (PRICTRL0.RRLVLEN3 written to '0').

#### Bit 23 – RRLVLEN2: Level 2 Round-Robin Arbitration Enable

This bit controls which arbitration scheme is selected for DMA channels with priority level 2. For details on arbitration schemes, refer to Arbitration.

| Value | Description                                                        |

|-------|--------------------------------------------------------------------|

| 0     | Static arbitration scheme for channels with level 2 priority.      |

| 1     | Round-robin arbitration scheme for channels with level 2 priority. |

#### Bits 19:16 – LVLPRI2[3:0]: Level 2 Channel Priority Number

When round-robin arbitration is enabled (PRICTRL0.RRLVLEN2=1) for priority level 2, this register holds the channel number of the last DMA channel being granted access as the active channel with priority level 2.

| Value | Description                   |

|-------|-------------------------------|

| 0     | High-speed transfer disabled. |

| 1     | High-speed transfer enabled.  |

#### Bit 13 – LENEN: Transfer Length Enable

| Value | Description                         |

|-------|-------------------------------------|

| 0     | Automatic transfer length disabled. |

| 1     | Automatic transfer length enabled.  |

#### Bits 10:0 - ADDR[10:0]: Address

When ADDR is written, the consecutive operation will depend on the bus state:

UNKNOWN: INTFLAG.MB and STATUS.BUSERR are set, and the operation is terminated.

BUSY: The I<sup>2</sup>C master will await further operation until the bus becomes IDLE.

IDLE: The I<sup>2</sup>C master will issue a start condition followed by the address written in ADDR. If the address is acknowledged, SCL is forced and held low, and STATUS.CLKHOLD and INTFLAG.MB are set.

OWNER: A repeated start sequence will be performed. If the previous transaction was a read, the acknowledge action is sent before the repeated start bus condition is issued on the bus. Writing ADDR to issue a repeated start is performed while INTFLAG.MB or INTFLAG.SB is set.

STATUS.BUSERR, STATUS.ARBLOST, INTFLAG.MB and INTFLAG.SB will be cleared when ADDR is written.

The ADDR register can be read at any time without interfering with ongoing bus activity, as a read access does not trigger the master logic to perform any bus protocol related operations.

The I<sup>2</sup>C master control logic uses bit 0 of ADDR as the bus protocol's read/write flag (R/W); 0 for write and 1 for read.

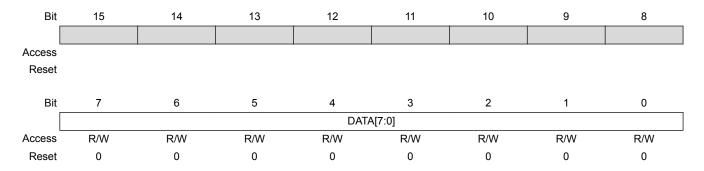

### 33.10.10 Data

Name:DATAOffset:0x18 [ID-00001bb3]Reset:0x0000Property:Write-Synchronized, Read-Synchronized

#### Bits 7:0 - DATA[7:0]: Data

The master data register I/O location (DATA) provides access to the master transmit and receive data buffers. Reading valid data or writing data to be transmitted can be successfully done only when SCL is

# SAM C20/C21

| Offset       | Name     | Bit Pos. |       |             |     |      |                |             |      |     |  |  |  |

|--------------|----------|----------|-------|-------------|-----|------|----------------|-------------|------|-----|--|--|--|

| 0x86         |          | 23:16    |       |             |     | LSS  | [7:0]          |             |      |     |  |  |  |

| 0x87         |          | 31:24    |       |             |     |      |                |             |      |     |  |  |  |

| 0x88         |          | 7:0      |       |             |     | FLES | A[7:0]         |             |      |     |  |  |  |

| 0x89         |          | 15:8     |       | FLESA[15:8] |     |      |                |             |      |     |  |  |  |

| 0x8A         | XIDFC    | 23:16    |       |             |     |      | LSE[6:0]       |             |      |     |  |  |  |

| 0x8B         |          | 31:24    |       |             |     |      |                |             |      |     |  |  |  |

| 0x8C         |          |          |       |             |     |      |                |             |      |     |  |  |  |

|              | Reserved |          |       |             |     |      |                |             |      |     |  |  |  |

| 0x8F<br>0x90 |          | 7:0      |       |             |     | EIDN | 4[7:0]         |             |      |     |  |  |  |

| 0x90<br>0x91 |          | 15:8     |       |             |     | EIDM |                |             |      |     |  |  |  |

| 0x91<br>0x92 | XIDAM    | 23:16    |       |             |     | EIDM |                |             |      |     |  |  |  |

| 0x92<br>0x93 |          | 31:24    |       |             |     |      | 23.10]         | EIDM[28:24] |      |     |  |  |  |

| 0x93         |          | 7:0      | MS    | [[1:0]      |     |      | BID>           |             |      |     |  |  |  |

| 0x94<br>0x95 |          | 15:8     | FLST  | .[]         |     |      | FIDX[6:0]      | .[]         |      |     |  |  |  |

| 0x96         | HPMS     | 23:16    | . 201 |             |     |      | 5,(0.0]        |             |      |     |  |  |  |

| 0x97         |          | 31:24    |       |             |     |      |                |             |      |     |  |  |  |

| 0x98         |          | 7:0      | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x99         | NDAT1    | 15:8     | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9A         |          | 23:16    | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9B         |          | 31:24    | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9C         |          | 7:0      | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9D         |          | 15:8     | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9E         | NDAT2    | 23:16    | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0x9F         |          | 31:24    | NDn   | NDn         | NDn | NDn  | NDn            | NDn         | NDn  | NDn |  |  |  |

| 0xA0         |          | 7:0      |       |             |     | F0SA | A[7:0]         |             |      |     |  |  |  |

| 0xA1         |          | 15:8     |       |             |     | F0SA | [15:8]         |             |      |     |  |  |  |

| 0xA2         | RXF0C    | 23:16    |       |             |     |      | F0S[6:0]       |             |      |     |  |  |  |

| 0xA3         |          | 31:24    | F0OM  |             |     |      | F0WM[6:0]      |             |      |     |  |  |  |

| 0xA4         |          | 7:0      |       |             |     |      | F0FL[6:0]      |             |      |     |  |  |  |

| 0xA5         | DVEQQ    | 15:8     |       |             |     |      | F0G            | I[5:0]      |      |     |  |  |  |

| 0xA6         | RXF0S    | 23:16    |       |             |     |      | F0P            | I[5:0]      |      |     |  |  |  |

| 0xA7         |          | 31:24    |       |             |     |      |                |             | RF0L | F0F |  |  |  |

| 0xA8         |          | 7:0      |       |             |     |      | F0A            | I[5:0]      |      |     |  |  |  |

| 0xA9         | RXF0A    | 15:8     |       |             |     |      |                |             |      |     |  |  |  |

| 0xAA         | INAEUA   | 23:16    |       |             |     |      |                |             |      |     |  |  |  |

| 0xAB         |          | 31:24    |       |             |     |      |                |             |      |     |  |  |  |

| 0xAC         |          | 7:0      |       |             |     | RBS  | <b>A</b> [7:0] |             |      |     |  |  |  |

| 0xAD         | RXBC     | 15:8     |       |             |     | RBSA | [15:8]         |             |      |     |  |  |  |

| 0xAE         | TABO     | 23:16    |       |             |     |      |                |             |      |     |  |  |  |

| 0xAF         |          | 31:24    |       |             |     |      |                |             |      |     |  |  |  |

| 0xB0         |          | 7:0      |       |             |     | F1SA |                |             |      |     |  |  |  |

| 0xB1         | RXF1C    | 15:8     |       |             |     | F1SA |                |             |      |     |  |  |  |

| 0xB2         |          | 23:16    |       |             |     |      | F1S[6:0]       |             |      |     |  |  |  |

| 0xB3         |          | 31:24    | F1OM  |             |     |      | F1WM[6:0]      |             |      |     |  |  |  |

| 0xB4         | RXF1S    | 7:0      |       |             |     |      | F1FL[6:0]      |             |      |     |  |  |  |

| 0xB5         |          | 15:8     |       |             |     |      | F1G            | I[5:0]      |      |     |  |  |  |

| 31   | 30                                            | 29                                                                                                                                                   | 28                                                                                                                                                                                                                                                                                                  | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                                                                                                                   | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F1OM |                                               |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                     | F1WM[6:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R/W  | R/W                                           | R/W                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0    | 0                                             | 0                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                               |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23   | 22                                            | 21                                                                                                                                                   | 20                                                                                                                                                                                                                                                                                                  | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                                                                                                                   | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |                                               |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                     | F1S[6:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | R/W                                           | R/W                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |