Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b, 2x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-QFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21g15a-mut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 1. The AHB-APB bridge D is available only on C21N and C20N.

- 2. The CAN peripheral is available only on C21.

### Table 10-5. Bus Matrix Masters

| Bus Matrix Masters                                   | Master ID |

|------------------------------------------------------|-----------|

| CM0+ - Cortex M0+ Processor                          | 0         |

| DSU - Device Service Unit                            | 1         |

| DMAC - Direct Memory Access Controller / Data Access | 2         |

#### Table 10-6. Bus Matrix Slaves

| Bus Matrix Slaves              | Slave ID |

|--------------------------------|----------|

| Internal Flash Memory          | 0        |

| SRAM Port 4 - CM0+ Access      | 1        |

| SRAM Port 6 - DSU Access       | 2        |

| AHB-APB Bridge A               | 3        |

| AHB-APB Bridge B               | 4        |

| AHB-APB Bridge C               | 5        |

| SRAM Port 5 - DMAC Data Access | 6        |

| DIVAS - Divide Accelerator     | 7        |

# Table 10-7. SRAM Port Connections

| SRAM Port Connection                                         | Port ID | Connection Type |

|--------------------------------------------------------------|---------|-----------------|

| CM0+ - Cortex M0+ Processor                                  | 0       | Bus Matrix      |

| DSU - Device Service Unit                                    | 1       | Bus Matrix      |

| DMAC - Direct Memory Access Controller - Data Access         | 2       | Bus Matrix      |

| DMAC - Direct Memory Access Controller - Fetch Access 0      | 3       | Direct          |

| DMAC - Direct Memory Access Controller - Fetch Access 1      | 4       | Direct          |

| DMAC - Direct Memory Access Controller - Write-Back Access 0 | 5       | Direct          |

| DMAC - Direct Memory Access Controller - Write-Back Access 1 | 6       | Direct          |

| CAN0 - Controller Area Network 0                             | 7       | Direct          |

| CAN1 - Controller Area Network 1                             | 8       | Direct          |

| MTB - Micro Trace Buffer                                     | 9       | Direct          |

# 10.4.3 SRAM Quality of Service

To ensure that masters with latency requirements get sufficient priority when accessing RAM, the different masters can be configured to have a given priority for different type of access.

The "set protection" operation will set the write access protection for the peripheral selected by WRCTRL.PERID. Write accesses are not allowed for the registers with write protection property in this peripheral.

The "set and lock protection" operation will set the write access protection for the peripheral selected by WRCTRL.PERID and locks the access rights of the selected peripheral registers. The write access protection will only be cleared by a hardware reset.

The peripheral access control status can be read from the corresponding STATUSn register.

#### 11.5.2.6 Write Access Protection Management Errors

Only word-wise writes to the WRCTRL register will effectively change the access protection. Other type of accesses will have no effect and will cause a PAC write access error. This error is reported in the INTFLAGn.PAC bit corresponding to the PAC module.

PAC also offers an additional safety feature for correct program execution with an interrupt generated on double write clear protection or double write set protection. If a peripheral is write protected and a subsequent set protection operation is detected then the PAC returns an error, and similarly for a double clear protection operation.

In addition, an error is generated when writing a "set and lock" protection to a write-protected peripheral or when a write access is done to a locked set protection. This can be used to ensure that the application follows the intended program flow by always following a write protect with an unprotect and conversely. However in applications where a write protected peripheral is used in several contexts, e.g. interrupt, care should be taken so that either the interrupt can not happen while the main application or other interrupt levels manipulates the write protection status or when the interrupt handler needs to unprotect the peripheral based on the current protection status by reading the STATUS register.

The errors generated while accessing the PAC module registers (eg. key error, double protect error...) will set the INTFLAGn.PAC flag.

#### 11.5.2.7 AHB Slave Bus Errors

The PAC module reports errors occurring at the AHB Slave bus level. These errors are generated when an access is performed at an address where no slave (bridge or peripheral) is mapped. These errors are reported in the corresponding bits of the INTFLAGAHB register.

#### 11.5.2.8 Generating Events

The PAC module can also generate an event when any of the Interrupt Flag registers bit are set. To enable the PAC event generation, the control bit EVCTRL.ERREO must be set a '1'.

#### 11.5.3 DMA Operation

Not applicable.

#### 11.5.4 Interrupts

The PAC has the following interrupt source:

- Error (ERR): Indicates that a peripheral access violation occurred in one of the peripherals controlled by the PAC module, or a bridge error occurred in one of the bridges reported by the PAC

- This interrupt is a synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAGAHB and INTFLAGn) registers is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared,

# 12. Peripherals Configuration Summary

# 12.1 SAM C20/C21 N

# Table 12-1. Peripherals Configuration Summary SAM C21 N

| Peripheral<br>Name  | Base<br>Address | IRQ<br>Line | AHI   | 3 Clock             | AP | B Clock             | Generic<br>Clock                                  | P     | AC               |                       | Events                                                 | DMA            |                  |

|---------------------|-----------------|-------------|-------|---------------------|----|---------------------|---------------------------------------------------|-------|------------------|-----------------------|--------------------------------------------------------|----------------|------------------|

|                     |                 |             | Index | Enabled<br>at Reset |    | Enabled<br>at Reset | Index                                             | Index | Prot at<br>Reset | User                  | Generator                                              | Index          | Sleep<br>Walking |

| AHB-APB<br>Bridge A | 0x40000000      |             | 0     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| PAC                 | 0x40000000      | 0           | 10    | Y                   | 0  | Y                   |                                                   | 0     | Ν                |                       | 85 : ACCERR                                            |                | N/A              |

| PM                  | 0x40000400      | 0           |       |                     | 1  | Y                   |                                                   | 1     | Ν                |                       |                                                        |                | N/A              |

| MCLK                | 0x40000800      | 0           |       |                     | 2  | Y                   |                                                   | 2     | N                |                       |                                                        |                | Y                |

| RSTC                | 0x40000C00      |             |       |                     | 3  | Y                   |                                                   | 3     | N                |                       |                                                        |                | N/A              |

| OSCCTRL             | 0x40001000      | 0           |       |                     | 4  | Y                   | 0: FDPLL96M<br>clk source<br>1: FDPLL96M<br>32kHz | 4     | Ν                |                       | 0: XOSC_FAIL                                           |                | Y                |

| OSC32KCTRL          | 0x40001400      | 0           |       |                     | 5  | Y                   |                                                   | 5     | Ν                |                       | 1: XOSC32K_FAIL                                        |                | Y                |

| SUPC                | 0x40001800      | 0           |       |                     | 6  | Y                   |                                                   | 6     | Ν                |                       |                                                        |                | N/A              |

| GCLK                | 0x40001C00      |             |       |                     | 7  | Y                   |                                                   | 7     | N                |                       |                                                        |                | N/A              |

| WDT                 | 0x40002000      | 1           |       |                     | 8  | Y                   |                                                   | 8     | Ν                |                       |                                                        |                | Y                |

| RTC                 | 0x40002400      | 2           |       |                     | 9  | Y                   |                                                   | 9     | Ν                |                       | 2: CMP0/ALARM0<br>3: CMP1<br>4: OVF5-1<br>5:12: PER0-7 |                | Y                |

| EIC                 | 0x40002800      | 3,<br>NMI   |       |                     | 10 | Y                   | 2                                                 | 10    | N                |                       | 13-28: EXTINT0-15                                      |                | Y                |

| FREQM               | 0x40002C00      | 4           |       |                     | 11 | Y                   | 3: Measure<br>4: Reference                        | 11    | N                |                       |                                                        |                | N/A              |

| TSENS               | 0x40003000      | 5           |       |                     | 12 | Ν                   | 5                                                 | 12    | Ν                | 0: START              | 29: WINMON                                             | 1: RESRDY      | A                |

| AHB-APB<br>Bridge B | 0x41000000      |             | 1     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| PORT                | 0x41000000      |             |       |                     | 0  | Y                   |                                                   | 0     | Ν                | 1-4 : EV0-3           |                                                        |                | Y                |

| DSU                 | 0x41002000      |             | 3     | Y                   | 1  | Y                   |                                                   | 1     | Y                |                       |                                                        |                | N/A              |

| NVMCTRL             | 0x41004000      | 6           | 5     | Y                   | 2  | Y                   | 39                                                | 2     | Ν                |                       |                                                        |                | Y                |

| DMAC                | 0x41006000      | 7           | 7     | Y                   |    |                     |                                                   | 3     | Ν                | 5-8: CH0-3            | 30-33: CH0-3                                           |                | Y                |

| MTB                 | 0x41008000      |             |       |                     |    |                     |                                                   |       | N                | 45: START<br>46: STOP |                                                        |                | N/A              |

| AHB-APB<br>Bridge C | 0x42000000      |             | 2     | Y                   |    |                     |                                                   |       |                  |                       |                                                        |                | N/A              |

| EVSYS               | 0x42000000      | 8           |       |                     | 0  | Ν                   | 6-17: one per<br>CHANNEL                          | 0     | N                |                       |                                                        |                | Y                |

| SERCOM0             | 0x42000400      | 9           |       |                     | 1  | N                   | 19: CORE<br>18: SLOW                              | 1     | N                |                       |                                                        | 2: RX<br>3: TX | Y                |

| SERCOM1             | 0x42000800      | 10          |       |                     | 2  | N                   | 20: CORE<br>18: SLOW                              | 2     | N                |                       |                                                        | 4: RX<br>5: TX | Y                |

| SERCOM2             | 0x42000C00      | 11          |       |                     | 3  | N                   | 21: CORE<br>18: SLOW                              | 3     | N                |                       |                                                        | 6: RX<br>7: TX | Y                |

| SERCOM3             | 0x42001000      | 12          |       |                     | 4  | N                   | 22: CORE<br>18: SLOW                              | 4     | Ν                |                       |                                                        | 8: RX<br>9: TX | Y                |

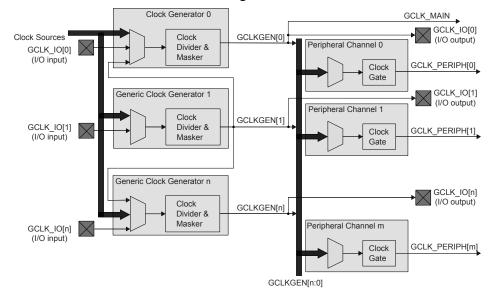

#### Figure 16-2. Generic Clock Controller Block Diagram

# 16.4 Signal Description

#### Table 16-1. GCLK Signal Description

| Signal Name  | Туре        | Description                            |

|--------------|-------------|----------------------------------------|

| GCLK_IO[7:0] | Digital I/O | Clock source for Generators when input |

|              |             | Generic Clock signal when output       |

Note: One signal can be mapped on several pins.

#### Related Links

I/O Multiplexing and Considerations

# 16.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 16.5.1 I/O Lines

Using the GCLK I/O lines requires the I/O pins to be configured.

#### **Related Links**

PORT - I/O Pin Controller

#### 16.5.2 Power Management

The GCLK can operate in sleep modes, if required. Refer to the sleep mode description in the Power Manager (PM) section.

#### **Related Links**

PM – Power Manager

# 19.7 Register Summary

| Offset | Name     | Bit Pos. |       |           |  |         |             |    |

|--------|----------|----------|-------|-----------|--|---------|-------------|----|

| 0x01   | SLEEPCFG | 7:0      |       |           |  | S       | LEEPMODE[2: | 0] |

| 0x02   |          |          |       |           |  |         |             |    |

|        | Reserved |          |       |           |  |         |             |    |

| 0x07   |          |          |       |           |  |         |             |    |

| 0x08   | STDBYCFG | 7:0      | VREGS | /IOD[1:0] |  |         |             |    |

| 0x09   | STUBTURG | 15:8     |       |           |  | BBIASHS |             |    |

# **19.8 Register Description**

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

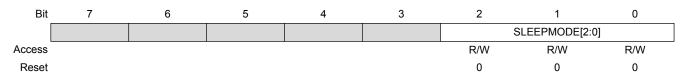

#### 19.8.1 Sleep Configuration

Name:SLEEPCFGOffset:0x01 [ID-00000a2f]Reset:0x00Property:PAC Write-Protection

#### Bits 2:0 – SLEEPMODE[2:0]: Sleep Mode

**Note:** A small latency happens between the store instruction and actual writing of the SLEEPCFG register due to bridges. Software has to make sure the SLEEPCFG register reads the wanted value before issuing Wait For Interrupt (WFI) instruction.

| Value     | Name     | Definition |

|-----------|----------|------------|

| 0x0       |          |            |

| 0x1       |          |            |

| 0x2       | IDLE     |            |

| 0x3       | Reserved | Reserved   |

| 0x4       | STANDBY  |            |

| 0x5 - 0x7 | Reserved | Reserved   |

# 20.7 Register Summary

| Offset | Name          | Bit Pos. |          |          |         |           |           |           |              |          |

|--------|---------------|----------|----------|----------|---------|-----------|-----------|-----------|--------------|----------|

| 0x00   |               | 7:0      |          |          |         | OSC48MRDY |           |           | CLKFAIL      | XOSCRDY  |

| 0x01   |               | 15:8     |          |          |         |           | DPLLLDRTO | DPLLLTO   | DPLLLCKF     | DPLLLCKR |

| 0x02   | INTENCLR      | 23:16    |          |          |         |           |           |           |              |          |

| 0x03   |               | 31:24    |          |          |         |           |           |           |              |          |

| 0x04   |               | 7:0      |          |          |         | OSC48MRDY |           |           | CLKFAIL      | XOSCRDY  |

| 0x05   | NITENOET      | 15:8     |          |          |         |           | DPLLLDRTO | DPLLLTO   | DPLLLCKF     | DPLLLCKR |

| 0x06   | INTENSET      | 23:16    |          |          |         |           |           |           |              |          |

| 0x07   |               | 31:24    |          |          |         |           |           |           |              |          |

| 0x08   |               | 7:0      |          |          |         | OSC48MRDY |           |           | CLKFAIL      | XOSCRDY  |

| 0x09   |               | 15:8     |          |          |         |           | DPLLLDRTO | DPLLLTO   | DPLLLCKF     | DPLLLCKR |

| 0x0A   | INTFLAG       | 23:16    |          |          |         |           |           |           |              |          |

| 0x0B   |               | 31:24    |          |          |         |           |           |           |              |          |

| 0x0C   |               | 7:0      |          |          |         | OSC48MRDY |           | CLKSW     | CLKFAIL      | XOSCRDY  |

| 0x0D   | 0717110       | 15:8     |          |          |         |           | DPLLLDRTO | DPLLLTO   | DPLLLCKF     | DPLLLCKR |

| 0x0E   | STATUS        | 23:16    |          |          |         |           |           |           |              |          |

| 0x0F   |               | 31:24    |          |          |         |           |           |           |              |          |

| 0x10   | VOCOTT        | 7:0      | ONDEMAND | RUNSTDBY |         | SWBACK    | CFDEN     | XTALEN    | ENABLE       |          |

| 0x11   | XOSCCTRL      | 15:8     |          | START    | UP[3:0] |           | AMPGC     |           | GAIN[2:0]    |          |

| 0x12   | CFDPRESC      | 7:0      |          |          |         |           |           | (         | CFDPRESC[2:0 | )]       |

| 0x13   | EVCTRL        | 7:0      |          |          |         |           |           |           |              | CFDEO    |

| 0x14   | OSC48MCTRL    | 7:0      | ONDEMAND | RUNSTDBY |         |           |           |           | ENABLE       |          |

| 0x15   | OSC48MDIV     | 7:0      |          |          |         |           |           | DIV       | [3:0]        |          |

| 0x16   | OSC48MSTUP    | 7:0      |          |          |         |           |           |           | STARTUP[2:0] |          |

| 0x17   | Reserved      |          |          |          |         |           |           |           |              |          |

| 0x18   |               | 7:0      |          |          |         |           |           | OSC48MDIV |              |          |

| 0x19   | OSC48MSYNCBUS | 15:8     |          |          |         |           |           |           |              |          |

| 0x1A   | Y             | 23:16    |          |          |         |           |           |           |              |          |

| 0x1B   | -             | 31:24    |          |          |         |           |           |           |              |          |

| 0x1C   | DPLLCTRLA     | 7:0      | ONDEMAND | RUNSTDBY |         |           |           |           | ENABLE       |          |

| 0x1D   |               |          |          |          |         |           |           |           |              |          |

|        | Reserved      |          |          |          |         |           |           |           |              |          |

| 0x1F   |               |          |          |          |         |           |           |           |              |          |

| 0x20   |               | 7:0      |          |          |         | LDR       | [7:0]     |           |              |          |

| 0x21   | DPLLRATIO     | 15:8     |          |          |         |           |           | LDR       | [11:8]       |          |

| 0x22   | DELLKAIIO     | 23:16    |          |          |         |           |           | LDRFR     | AC[3:0]      |          |

| 0x23   |               | 31:24    |          |          |         |           |           |           |              |          |

| 0x24   |               | 7:0      |          |          | REFC    | LK[1:0]   | WUF       | LPEN      | FILTE        | R[1:0]   |

| 0x25   |               | 15:8     |          |          |         | LBYPASS   |           |           | LTIME[2:0]   |          |

| 0x26   | DPLLCTRLB     | 23:16    |          |          |         | DIV       | [7:0]     |           |              |          |

| 0x27   |               | 31:24    |          |          |         |           |           |           | DIV[10:8]    |          |

| 0x28   | DPLLPRESC     | 7:0      |          |          |         |           |           |           | PRES         | 6C[1:0]  |

| 0x29   |               |          |          |          |         |           |           |           |              |          |

|        | Reserved      |          |          |          |         |           |           |           |              |          |

| 0x2B   |               |          |          |          |         |           |           |           |              |          |

#### Bit 2 – FREQCORR: Frequency Correction Synchronization Busy Status

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Write synchronization for FREQCORR register is complete. |

| 1     | Write synchronization for FREQCORR register is ongoing.  |

#### Bit 1 – ENABLE: Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

#### Bit 0 – SWRST: Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

#### 24.8.8 Frequency Correction

Name:FREQCORROffset:0x14Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 7    | 6   | 5   | 4   | 3          | 2   | 1   | 0   |

|--------|------|-----|-----|-----|------------|-----|-----|-----|

|        | SIGN |     |     |     | VALUE[6:0] |     |     |     |

| Access | R/W  | R/W | R/W | R/W | R/W        | R/W | R/W | R/W |

| Reset  | 0    | 0   | 0   | 0   | 0          | 0   | 0   | 0   |

#### Bit 7 – SIGN: Correction Sign

| Value | Description                                                          |

|-------|----------------------------------------------------------------------|

| 0     | The correction value is positive, i.e., frequency will be decreased. |

| 1     | The correction value is negative, i.e., frequency will be increased. |

#### Bits 6:0 – VALUE[6:0]: Correction Value

These bits define the amount of correction applied to the RTC prescaler.

| Value   | Description                                                |

|---------|------------------------------------------------------------|

| 0       | Correction is disabled and the RTC frequency is unchanged. |

| 1 - 127 | The RTC frequency is adjusted according to the value.      |

#### 24.8.9 Counter Value in COUNT32 mode (CTRLA.MODE=0)

| Name:    | COUNT                                                         |

|----------|---------------------------------------------------------------|

| Offset:  | 0x18                                                          |

| Reset:   | 0x0000000                                                     |

| Property | : PAC Write-Protection, Write-Synchronized, Read-Synchronized |

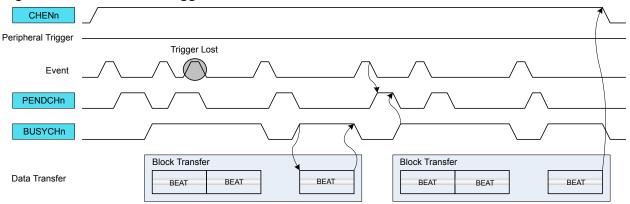

Figure 25-11. Beat Event Trigger Action

#### **Conditional Transfer on Strobe**

The event input is used to trigger a transfer on peripherals with pending transfer requests. This event action is intended to be used with peripheral triggers, e.g. for timed communication protocols or periodic transfers between peripherals: only when the peripheral trigger coincides with the occurrence of a (possibly cyclic) event the transfer is issued.

The event is acknowledged as soon as the event is received. The peripheral trigger request is stored internally when the previous trigger action is completed (i.e. the channel is not pending) and when an active event is received. If the peripheral trigger is active, the DMA will wait for an event before the peripheral trigger is internally registered. When both event and peripheral transfer trigger are active, both CHSTATUS.PEND and PENDCH.PENDCHn are set. A software trigger will now trigger a transfer.

The figure below shows an example where the peripheral beat transfer is started by a conditional strobe event action.

# Figure 25-12. Periodic Event with Beat Peripheral Triggers

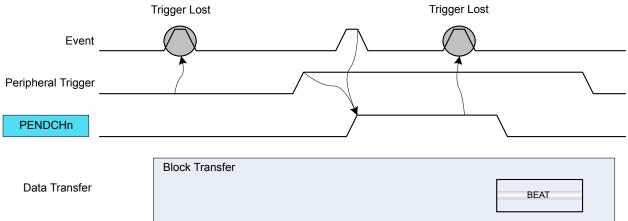

#### **Conditional Transfer**

The event input is used to trigger a conditional transfer on peripherals with pending transfer requests. As example, this type of event can be used for peripheral-to-peripheral transfers, where one peripheral is the source of event and the second peripheral is the source of the trigger.

Each peripheral trigger is stored internally when the event is received. When the peripheral trigger is stored internally, the Channel Pending status bit is set (CHSTATUS.PEND), the respective Pending Channel n Bit in the Pending Channels register is set (PENDCH.PENDCHn), and the event is acknowledged. A software trigger will now trigger a transfer.

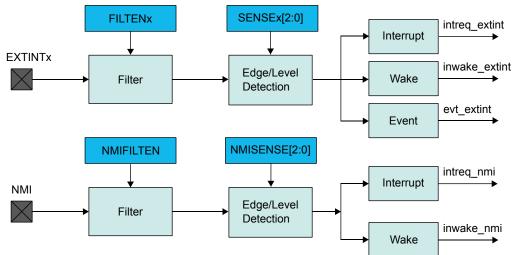

# 26. EIC – External Interrupt Controller

# 26.1 Overview

The External Interrupt Controller (EIC) allows external pins to be configured as interrupt lines. Each interrupt line can be individually masked and can generate an interrupt on rising, falling, or both edges, or on high or low levels. Each external pin has a configurable filter to remove spikes. Each external pin can also be configured to be asynchronous in order to wake up the device from sleep modes where all clocks have been disabled. External pins can also generate an event.

A separate non-maskable interrupt (NMI) is also supported. It has properties similar to the other external interrupts, but is connected to the NMI request of the CPU, enabling it to interrupt any other interrupt mode.

# 26.2 Features

- Up to 32 external pins (EXTINTx), plus one non-maskable pin (NMI)

- Dedicated, individually maskable interrupt for each pin

- Interrupt on rising, falling, or both edges

- Synchronous or asynchronous edge detection mode

- Interrupt pin debouncing

- Interrupt on high or low levels

- Asynchronous interrupts for sleep modes without clock

- Filtering of external pins

- Event generation from EXTINTx

# 26.3 Block Diagram

#### Figure 26-1. EIC Block Diagram

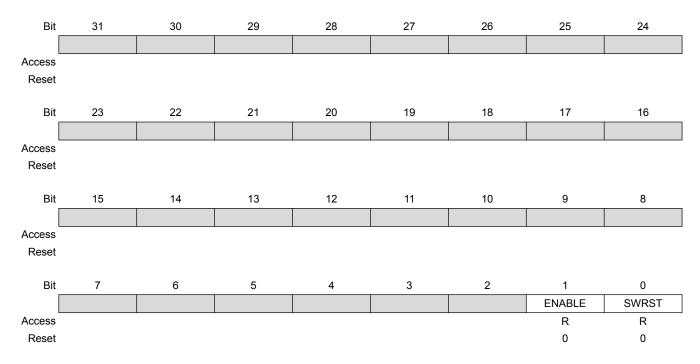

Name:SYNCBUSYOffset:0x04Reset:0x0000000Property:-

#### Bit 1 – ENABLE: Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

#### Bit 0 – SWRST: Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

#### 26.8.5 Event Control

Name:EVCTRLOffset:0x08Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 31  | 30  | 29  | 28    | 27       | 26  | 25  | 24  |

|--------|-----|-----|-----|-------|----------|-----|-----|-----|

| ſ      |     |     |     | EXTIN | [31:24]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 23  | 22  | 21  | 20    | 19       | 18  | 17  | 16  |

|        |     |     |     | EXTIN | F[23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 15  | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

| Γ      |     |     |     | EXTIN | T[15:8]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |     |     |     |       |          |     |     |     |

| Bit    | 7   | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

| Γ      |     |     |     | EXTIN | IT[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

#### Bits 31:0 – EXTINT[31:0]: External Interrupt Enable

The bit x of EXTINT enables the interrupt associated with the EXTINTx pin.

Writing a '0' to bit x has no effect.

Writing a '1' to bit x will set the External Interrupt Enable bit x, which enables the external interrupt EXTINTx.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The external interrupt x is disabled. |

| 1     | The external interrupt x is enabled.  |

#### 26.8.8 Interrupt Flag Status and Clear

Name:INTFLAGOffset:0x14Reset:0x0000000Property: -

• External clocking, CTRLA.RUNSTDBY=0: External clock will be disconnected, after any ongoing transfer was completed. All reception will be dropped.

#### 31.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Receiver Enable bit in the CTRLB register (CTRLB.RXEN)

- Transmitter Enable bit in the Control B register (CTRLB.TXEN)

**Note:** CTRLB.RXEN is write-synchronized somewhat differently. See also CTRLB for details.

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

# **Related Links**

**Register Synchronization**

held low by the master (STATUS.CLKHOLD is set). An exception is reading the last data byte after the stop condition has been sent.

Accessing DATA.DATA auto-triggers I<sup>2</sup>C bus operations. The operation performed depends on the state of CTRLB.ACKACT, CTRLB.SMEN and the type of access (read/write).

Writing or reading DATA.DATA when not in smart mode does not require synchronization.

#### 33.10.11 Debug Control

Name:DBGCTRLOffset:0x30 [ID-00001bb3]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|--------|---|---|---|---|---|---|---|---------|

|        |   |   |   |   |   |   |   | DBGSTOP |

| Access |   |   |   |   |   |   |   | R/W     |

| Reset  |   |   |   |   |   |   |   | 0       |

#### Bit 0 – DBGSTOP: Debug Stop Mode

This bit controls functionality when the CPU is halted by an external debugger.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The baud-rate generator continues normal operation when the CPU is halted by an external |

|       | debugger.                                                                                |

| 1     | The baud-rate generator is halted when the CPU is halted by an external debugger.        |

| Value | Description                           |

|-------|---------------------------------------|

| 0     | CAPTEN disables capture on channel x. |

| 1     | CAPTEN enables capture on channel x.  |

#### Bit 11 – ALOCK: Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | The LUPD bit is not affected on overflow/underflow, and re-trigger event. |

| 1     | The LUPD bit is set on each overflow/underflow or re-trigger event.       |

#### Bits 10:8 - PRESCALER[2:0]: Prescaler

These bits select the counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

#### Bit 7 – ONDEMAND: Clock On Demand

This bit selects the clock requirements when the TC is stopped.

In standby mode, if the Run in Standby bit (CTRLA.RUNSTDBY) is '0', ONDEMAND is forced to '0'.

This bit is not synchronized.

| Value | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| 0     | The On Demand is disabled. If On Demand is disabled, the TC will continue to request the   |

|       | clock when its operation is stopped (STATUS.STOP=1).                                       |

| 1     | The On Demand is enabled. When On Demand is enabled, the stopped TC will not request       |

|       | the clock. The clock is requested when a software re-trigger command is applied or when an |

|       | event with start/re-trigger action is detected.                                            |

#### Bit 6 – RUNSTDBY: Run in Standby

This bit is used to keep the TC running in standby mode.

This bit is not synchronized.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The TC is halted in standby.        |

| 1     | The TC continues to run in standby. |

#### Bits 5:4 – PRESCSYNC[1:0]: Prescaler and Counter Synchronization

These bits select whether the counter should wrap around on the next GCLK\_TCx clock or the next prescaled GCLK\_TCx clock. It also makes it possible to reset the prescaler.

| Value | ОТМХ[3] | ОТМХ[2] | ОТМХ[1] | ОТМХ[0] |

|-------|---------|---------|---------|---------|

| 0x2   | CC0     | CC0     | CC0     | CC0     |

| 0x3   | CC1     | CC1     | CC1     | CC0     |

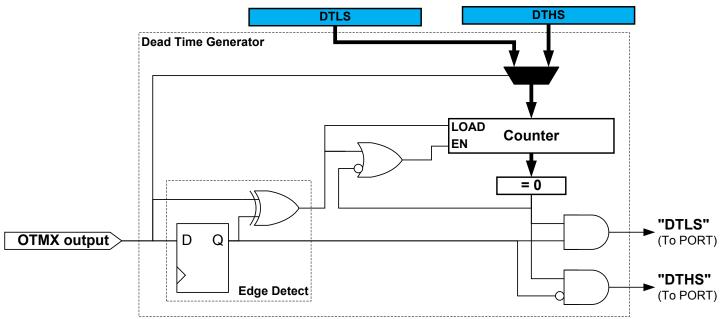

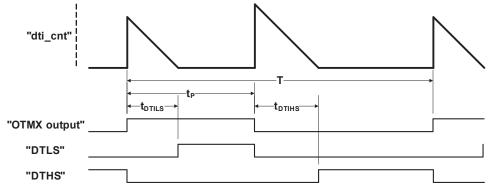

**The dead-time insertion (DTI)** unit generates OFF time with the non-inverted low side (LS) and inverted high side (HS) of the wave generator output forced at low level. This OFF time is called dead time. Dead-time insertion ensures that the LS and HS will never switch simultaneously.

The DTI stage consists of four equal dead-time insertion generators; one for each of the first four compare channels. Figure 36-34 shows the block diagram of one DTI generator. The four channels have a common register which controls the dead time, which is independent of high side and low side setting.

#### Figure 36-34. Dead-Time Generator Block Diagram

As shown in Figure 36-35, the 8-bit dead-time counter is decremented by one for each peripheral clock cycle until it reaches zero. A non-zero counter value will force both the low side and high side outputs into their OFF state. When the output matrix (OTMX) output changes, the dead-time counter is reloaded according to the edge of the input. When the output changes from low to high (positive edge) it initiates a counter reload of the DTLS register. When the output changes from high to low (negative edge) it reloads the DTHS register.

- Hardware gain and offset compensation

- Averaging and oversampling with decimation to support up to 16-bit result

- Selectable sampling time

- Flexible Power / Throughput rate management

ADC0 can be configured to serve the Peripheral Touch Controller (PTC). This setup features:

- Low-power, high-sensitivity, environmentally robust capacitive touch elements:

- Buttons

- Sliders

- Wheels

- Proximity sensing

- Supports mutual capacitance and self-capacitance sensing:

- Up to 32 buttons in self-capacitance mode

- Up to 256 buttons in mutual-capacitance mode

- Mix-and-match mutual-and self-capacitance sensors

- One pin per electrode no external components

- Load compensating charge sensing Parasitic capacitance compensation and adjustable gain for superior sensitivity

- Zero drift over temperature and supply voltage range

- Auto calibration and re-calibration of sensors

- Selectable channel change delay Allows choosing the settling time on a new channel, as required

- Supported by the Atmel<sup>®</sup> QTouch<sup>®</sup> Composer development tool, which comprises QTouch Library project builder and QTouch analyzer

Name:ANACTRLOffset:0x2C [ID-0000243d]Reset:0x00Property:PAC Write-Protection, Write-Synchronized.

| Bit    | 7       | 6      | 5 | 4   | 3   | 2             | 1   | 0   |

|--------|---------|--------|---|-----|-----|---------------|-----|-----|

|        | BUFTEST | ONCHOP |   |     |     | CTLSDADC[4:0] |     |     |

| Access | R/W     | R/W    |   | R/W | R/W | R/W           | R/W | R/W |

| Reset  | 0       | 0      |   | 0   | 0   | 0             | 0   | 0   |

#### Bit 7 – BUFTEST: Buffer Test

#### Bit 6 – ONCHOP: ONCHOP

| Value | Description               |

|-------|---------------------------|

| 0     | No Chopper at SDADC input |

| 1     | Chopper at SDADC input    |

#### Bits 4:0 – CTLSDADC[4:0]: CTLSDADC

SDADC Bias Current Control and used for Debugg/Characterization

#### 39.8.22 Debug Control

Name:DBGCTRLOffset:0x2E [ID-0000243d]Reset:0x00Property:PAC Write-Protectedion

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

This bit should be written only while a conversion is not ongoing.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The SDADC is halted when the CPU is halted by an external debugger.                  |

| 1     | The SDADC continues normal operation when the CPU is halted by an external debugger. |

| Bit    | 7 | 6     | 5        | 4    | 3 | 2      | 1        | 0    |

|--------|---|-------|----------|------|---|--------|----------|------|

|        |   | WINTS | EL1[1:0] | WEN1 |   | WINTSE | EL0[1:0] | WEN0 |

| Access |   | R/W   | R/W      | R/W  |   | R/W    | R/W      | R/W  |

| Reset  |   | 0     | 0        | 0    |   | 0      | 0        | 0    |

#### Bits 6:5 – WINTSEL1[1:0]: Window 1 Interrupt Selection

These bits configure the interrupt mode for the comparator window 1 mode.

| Value | Name    | Description                        |

|-------|---------|------------------------------------|

| 0x0   | ABOVE   | Interrupt on signal above window   |

| 0x1   | INSIDE  | Interrupt on signal inside window  |

| 0x2   | BELOW   | Interrupt on signal below window   |

| 0x3   | OUTSIDE | Interrupt on signal outside window |

#### Bit 4 – WEN1: Window 1 Mode Enable

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Window mode is disabled for comparators 2 and 3. |

| 1     | Window mode is enabled for comparators 2 and 3.  |

#### Bits 2:1 – WINTSEL0[1:0]: Window 0 Interrupt Selection

These bits configure the interrupt mode for the comparator window 0 mode.

| Value | Name    | Description                        |

|-------|---------|------------------------------------|

| 0x0   | ABOVE   | Interrupt on signal above window   |

| 0x1   | INSIDE  | Interrupt on signal inside window  |

| 0x2   | BELOW   | Interrupt on signal below window   |

| 0x3   | OUTSIDE | Interrupt on signal outside window |

### Bit 0 – WEN0: Window 0 Mode Enable

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | Window mode is disabled for comparators 0 and 1. |

| 1     | Window mode is enabled for comparators 0 and 1.  |

#### 40.8.11 Scaler n

Name: SCALERn Offset: 0x0C + n\*0x01 [n=0..3] Reset: 0x00 Property: Write-Protected

| Bit    | 7 | 6 | 5   | 4   | 3    | 2      | 1   | 0   |

|--------|---|---|-----|-----|------|--------|-----|-----|

|        |   |   |     |     | VALU | E[5:0] |     |     |

| Access |   |   | R/W | R/W | R/W  | R/W    | R/W | R/W |

| Reset  |   |   | 0   | 0   | 0    | 0      | 0   | 0   |

#### Bits 5:0 – VALUE[5:0]: Scaler Value

These bits define the scaling factor for channel n of the  $V_{DD}$  voltage scaler. The output voltage,  $V_{SCALE}$ , is:

# SAM C20/C21

| Symbol | Parameters          | Conditions | Та | Тур. | Мах | Units |

|--------|---------------------|------------|----|------|-----|-------|

|        | STANDBY, Mode SAMPL | VDD = 2.7V |    | 0.8  | 2.1 |       |

|        |                     | VDD = 5.0V |    | 3.5  | 4.9 |       |

#### Note:

1. These values are based on characterization.

#### Table 46-4. BODVDD Characteristics (see Note 2)

| Symbol                       | Parameters                                           | Conditions                              | Min  | Тур  | Max  | Unit |

|------------------------------|------------------------------------------------------|-----------------------------------------|------|------|------|------|

| VBOD+ (see Note 1)           | BODVDD high threshold<br>Level                       | VDD level, BOD setting =<br>8 (default) | -    | 2.86 | 2.98 | V    |

|                              |                                                      | VDD level, BOD setting =<br>9           | -    | 2.92 | 3.01 |      |

|                              |                                                      | VDD level, BOD setting =<br>44          | -    | 4.57 | 4.82 |      |

| VBOD- / VBOD (see<br>Note 1) | BODVDD low threshold Level                           | VDD level, BOD setting =<br>8 (default) | 2.71 | 2.8  | 2.90 |      |

|                              |                                                      | VDD level, BOD setting =<br>9           | 2.75 | 2.85 | 2.96 |      |

|                              |                                                      | VDD level, Bod setting =<br>44          | 4.37 | 4.51 | 4.66 |      |

|                              | Step size                                            |                                         | -    | 60   | -    | mV   |

| VHys (see Note 1)            | Hysteresis (VBOD+ - VBOD-)<br>BODVDD.LEVEL = 8 to 48 | VDD                                     | 40   | -    | 75   | mV   |

| Tstart (see Note 3)          | Startup time                                         | Time from enable to RDY                 | -    | 3.1  | -    | μs   |

#### Note:

- 1. These values are based on characterization.

- 2. BODVDD in Continuous mode.

- 3. These values are based on simulation, and are not covered by test or characterization.

#### **Related Links**

NVM User Row Mapping NVM User Row Mapping

# 46.4.2 Analog-to-Digital Converter (ADC) Characteristics Table 46-5. Power Consumption<sup>(1)</sup>

| Symbol | Parameters   | Conditions                     | Та        | Тур. | Max  | Units |

|--------|--------------|--------------------------------|-----------|------|------|-------|

| IDD    | Differential | •                              | Max 105°C | 905  | 1034 | μA    |

| VDDANA | mode         | disabled / BIASREFBUF = '111', | Typ 25°C  |      |      |       |

# 48. Packaging Information

Table 48-1. Thermal Resistance Data

# 48.1 Thermal Considerations

#### 48.1.1 Thermal Resistance Data

The following table summarizes the thermal resistance data depending on the package.

| Package Type  | θ <sub>JA</sub> | θ <sub>JC</sub> |  |  |  |  |

|---------------|-----------------|-----------------|--|--|--|--|

| 32-pin TQFP   | 63.1°C/W        | 14.3°C/W        |  |  |  |  |

| 48-pin TQFP   | 62.7°C/W        | 11.6°C/W        |  |  |  |  |

| 64-pin TQFP   | 56.3°C/W        | 11.1°C/W        |  |  |  |  |

| 100-pin TQFP  | 55.0°C/W        | 11.1°C/W        |  |  |  |  |

| 32-pin QFN    | 40.5°C/W        | 16.0°C/W        |  |  |  |  |

| 48-pin QFN    | 30.9°C/W        | 10.4°C/W        |  |  |  |  |

| 64-pin QFN    | 31.4°C/W        | 10.2°C/W        |  |  |  |  |

| 56-ball WLCSP | 37.5°C/W        | 5.48°C/W        |  |  |  |  |

#### 48.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.  $T_J = T_A + (P_D \times \theta_{JA})$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- $\theta_{JA}$  = Package thermal resistance, Junction-to-ambient (°C/W), see Thermal Resistance Data

- $\theta_{JC}$  = Package thermal resistance, Junction-to-case thermal resistance (°C/W), see Thermal Resistance Data

- θ<sub>HEATSINK</sub> = Thermal resistance (°C/W) specification of the external cooling device

- P<sub>D</sub> = Device power consumption (W)

- T<sub>A</sub> = Ambient temperature (°C)

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

# 48.2 Package Drawings

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at <a href="http://www.microchip.com/packaging">http://www.microchip.com/packaging</a>.