#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b, 2x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21g16a-aut |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3. Block Diagram

**Note:** Not all features are available for all devices. Please refer to Table 1-3 and Table 1-4 to determine feature availability for the particular device.

| Bit Position | Name       | Description                                                                           |

|--------------|------------|---------------------------------------------------------------------------------------|

| 40:19        | CAL48M 5V  | OSC48M Calibration: VDD range 3.6V to 5.5V. Should be written to the CAL48M register. |

| 62:41        | CAL48M 3V3 | OSC48M Calibration: VDD range 2.7V to 3.6V. Should be written to the CAL48M register. |

| 63           | Reserved   |                                                                                       |

#### Table 9-6. SAM C20 NVM Software Calibration Area Mapping

| Bit Position | Name           | Description                                                                           |

|--------------|----------------|---------------------------------------------------------------------------------------|

| 2:0          | ADC0 LINEARITY | ADC0 Linearity Calibration. Should be written to the CALIB register.                  |

| 5:3          | ADC0 BIASCAL   | ADC0 Bias Calibration. Should be written to the CALIB register.                       |

| 11:6         | Reserved       |                                                                                       |

| 18:12        | OSC32K CAL     | OSC32K Calibration. Should be written to OSC32K register.                             |

| 40:19        | CAL48M 5V      | OSC48M Calibration: VDD range 3.6V to 5.5V. Should be written to the CAL48M register. |

| 62:41        | CAL48M 3V3     | OSC48M Calibration: VDD range 2.7V to 3.6V. Should be written to the CAL48M register. |

| 63           | Reserved       |                                                                                       |

#### **Related Links**

CAL48M

# 9.5 NVM Temperature Calibration Area Mapping, SAM C21

The NVM Temperature Calibration Area contains calibration data that are measured and written during production test. These calibration values should be read by the application software and written back to the corresponding register.

The NVM Temperature Calibration Area can be read at address 0x806030.

The NVM Temperature Calibration Area can not be written.

| Table 9-7. NVM | M Temperature Calibration | Area Mapping, SAM C21 |

|----------------|---------------------------|-----------------------|

|----------------|---------------------------|-----------------------|

| Bit Position | Name       | Description                                                                 |

|--------------|------------|-----------------------------------------------------------------------------|

| 5:0          | TSENS TCAL | TSENS Temperature Calibration. Should be written to the TSENS CAL register. |

| 11:6         | TSENS FCAL | TSENS Frequency Calibration. Should be written to the TSENS CAL register.   |

| 35:12        | TSENS GAIN | TSENS Gain Calibration. Should be written to the TSENS GAIN register.       |

The Quality of Service (QoS) level is independently selected for each master accessing the RAM. For any access to the RAM the RAM also receives the QoS level. The QoS levels and their corresponding bit values for the QoS level configuration is shown in below.

| Value | Name    | Description                         |

|-------|---------|-------------------------------------|

| 0x0   | DISABLE | Background (no sensitive operation) |

| 0x1   | LOW     | Sensitive Bandwidth                 |

| 0x2   | MEDIUM  | Sensitive Latency                   |

| 0x3   | HIGH    | Critical Latency                    |

| Table 10-8. | Quality of Service | Level Configuration |

|-------------|--------------------|---------------------|

|-------------|--------------------|---------------------|

If a master is configured with QoS level DISABLE (0x0) or LOW (0x1) there will be minimum latency of one cycle for the RAM access.

The priority order for concurrent accesses are decided by two factors. First, the QoS level for the master and second, a static priority given by Table 10-7. The lowest port ID has the highest static priority.

The MTB has fixed QoS level HIGH (0x3) and the DSU has fixed QoS level LOW (0x1).

The CPU QoS level can be written/read at address 0x41007110, bits [1:0]. Its reset value is 0x0.

Refer to different master QOSCTRL registers for configuring QoS for the other masters (for SAM C21: CAN, DMAC; for SAM C20: DMAC).

#### 16.5.3 Clocks

The GCLK bus clock (CLK\_GCLK\_APB) can be enabled and disabled in the Main Clock Controller.

#### Related Links

Peripheral Clock Masking OSC32KCTRL – 32KHz Oscillators Controller

## 16.5.4 DMA

Not applicable.

#### 16.5.5 Interrupts

Not applicable.

#### 16.5.6 Events

Not applicable.

#### 16.5.7 Debug Operation

When the CPU is halted in debug mode the GCLK continues normal operation. If the GCLK is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 16.5.8 Register Access Protection

All registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC).

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

When the CPU is halted in debug mode, all write-protection is automatically disabled. Write-protection does not apply for accesses through an external debugger.

#### **Related Links**

PAC - Peripheral Access Controller

#### 16.5.9 Analog Connections

Not applicable.

# 16.6 Functional Description

#### 16.6.1 Principle of Operation

The GCLK module is comprised of nine Generic Clock Generators (Generators) sourcing up to 64 Peripheral Channels and the Main Clock signal GCLK\_MAIN.

A clock source selected as input to a Generator can either be used directly, or it can be prescaled in the Generator. A generator output is used by one or more Peripheral Channels to provide a peripheral generic clock signal (GCLK\_PERIPH) to the peripherals.

#### 16.6.2 Basic Operation

#### 16.6.2.1 Initialization

Before a Generator is enabled, the corresponding clock source should be enabled. The Peripheral clock must be configured as outlined by the following steps:

#### 19.6.3.2 Enabling, Disabling and Resetting

The PM is always enabled and can not be reset.

#### 19.6.3.3 Sleep Mode Controller

A Sleep mode is entered by executing the Wait For Interrupt instruction (WFI). The Sleep Mode bits in the Sleep Configuration register (SLEEPCFG.SLEEPMODE) select the level of the sleep mode.

**Note:** A small latency happens between the store instruction and actual writing of the SLEEPCFG register due to bridges. Software must ensure that the SLEEPCFG register reads the desired value before issuing a WFI instruction.

#### Table 19-1. Sleep Mode Entry and Exit Table

| Mode    | Mode Entry                   | Wake-Up Sources                                                       |

|---------|------------------------------|-----------------------------------------------------------------------|

| IDLE    | SLEEPCFG.SLEEPMODE = IDLE    | Synchronous <sup>(2)</sup> (APB, AHB),<br>asynchronous <sup>(1)</sup> |

| STANDBY | SLEEPCFG.SLEEPMODE = STANDBY | Synchronous <sup>(3)</sup> , Asynchronous                             |

Note:

- 1. Asynchronous: interrupt generated on generic clock, external clock, or external event.

- 2. Synchronous: interrupt generated on the APB clock.

- 3. Synchronous interrupt only for peripherals configured to run in standby.

**Note:** The type of wake-up sources (synchronous or asynchronous) is given in each module interrupt section.

The sleep modes (idle, standby) and their effect on the clocks activity, the regulator and the NVM state are described in the table and the sections below.

#### Table 19-2. Sleep Mode Overview

| Mode CPU |       | AHB                 | APB clock           |       | GCLK                | Oscilla                        | ators               | Regulator             | RAM                      |

|----------|-------|---------------------|---------------------|-------|---------------------|--------------------------------|---------------------|-----------------------|--------------------------|

|          | clock | clock               |                     | clock | clocks              | ONDEMAND = 0                   | ONDEMAND =<br>1     |                       |                          |

| IDLE     | Stop  | Stop <sup>(2)</sup> | Stop <sup>(2)</sup> | Run   | Run <sup>(1)</sup>  | Run                            | Run if<br>requested | Main                  | Normal                   |

| STANDBY  | Stop  | Stop <sup>(2)</sup> | Stop <sup>(2)</sup> | Stop  | Stop <sup>(2)</sup> | Run if requested or RUNSTDBY=1 | Run if<br>requested | LPVREG <sup>(3)</sup> | Low power <sup>(4)</sup> |

#### Note:

- 1. Running if requested by peripheral.

- 2. Running during SleepWalking.

- 3. Regulator state is programmable by using STDBYCFG.VREGSMOD bits.

- 4. RAM state is programmable by using STDBYCFG.BBIASHS bit.

#### **IDLE Mode**

The IDLE mode allows power optimization with the fastest wake-up time.

The CPU is stopped. To further reduce power consumption, the user can disable the clocking of modules and clock sources by configuring the SLEEPCFG bit group to IDLE. The peripheral will be halted regardless of the bit settings of the mask registers in the MCLK (MCLK.AHBMASK, MCLK.APBxMASK).

• Entering IDLE mode: The IDLE mode is entered by executing the WFI instruction. Additionally, if the SLEEPONEXIT bit in the ARM Cortex System Control register (SCR) is set, the IDLE mode will

# SAM C20/C21

| Bit    | 31      | 30 | 29 | 28  | 27  | 26         | 25  | 24  |

|--------|---------|----|----|-----|-----|------------|-----|-----|

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

| Reset  |         |    |    |     |     |            |     |     |

|        |         |    |    |     |     |            |     |     |

| Bit    | 23      | 22 | 21 | 20  | 19  | 18         | 17  | 16  |

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

| Reset  |         |    |    |     |     |            |     |     |

|        |         |    |    |     |     |            |     |     |

| Bit    | 15      | 14 | 13 | 12  | 11  | 10         | 9   | 8   |

|        | WRTLOCK |    |    |     |     | CALIB[4:0] |     |     |

| Access | R/W     |    |    | R/W | R/W | R/W        | R/W | R/W |

| Reset  | 0       |    |    | х   | х   | х          | х   | x   |

|        |         |    |    |     |     |            |     |     |

| Bit    | 7       | 6  | 5  | 4   | 3   | 2          | 1   | 0   |

|        |         |    |    |     |     |            |     |     |

| Access |         |    |    |     |     |            |     |     |

Reset

#### Bit 15 – WRTLOCK: Write Lock

This bit locks the OSCULP32K register for future writes to fix the OSCULP32K configuration.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The OSCULP32K configuration is not locked. |

| 1     | The OSCULP32K configuration is locked.     |

#### Bits 12:8 – CALIB[4:0]: Oscillator Calibration

These bits control the oscillator calibration.

These bits are loaded from Flash Calibration at startup.

# 23.7 Register Summary

| Offset | Name            | Bit Pos. |          |      |         |            |  |       |          |    |  |  |  |

|--------|-----------------|----------|----------|------|---------|------------|--|-------|----------|----|--|--|--|

| 0x00   | CTRLA           | 7:0      | ALWAYSON |      |         |            |  | WEN   | ENABLE   |    |  |  |  |

| 0x01   | CONFIG          | 7:0      |          | WIND | OW[3:0] |            |  | PER   | R[3:0]   |    |  |  |  |

| 0x02   | EWCTRL          | 7:0      |          |      |         |            |  | EWOFF | SET[3:0] |    |  |  |  |

| 0x03   | Reserved        |          |          |      |         |            |  |       |          |    |  |  |  |

| 0x04   | INTENCLR        | 7:0      |          |      |         |            |  |       |          | EW |  |  |  |

| 0x05   | INTENSET        | 7:0      |          |      |         |            |  |       |          | EW |  |  |  |

| 0x06   | INTFLAG         | 7:0      |          |      |         |            |  |       |          | EW |  |  |  |

| 0x07   | Reserved        |          |          |      |         |            |  |       |          |    |  |  |  |

| 0x08   |                 | 7:0      |          |      |         |            |  | WEN   | ENABLE   |    |  |  |  |

| 0x09   | <b>EXNODUEX</b> | 15:8     |          |      |         |            |  |       |          |    |  |  |  |

| 0x0A   | SYNCBUSY        | 23:16    |          |      |         |            |  |       |          |    |  |  |  |

| 0x0B   |                 | 31:24    |          |      |         |            |  |       |          |    |  |  |  |

| 0x0C   | CLEAR           | 7:0      |          |      |         | CLEAR[7:0] |  |       |          |    |  |  |  |

# 23.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 23.8.1 Control A

Name:CTRLAOffset:0x00Reset:X determined from NVM User RowProperty:PAC Write-Protection, Write-Synchronized

| Bit    | 7        | 6 | 5 | 4 | 3 | 2   | 1      | 0 |

|--------|----------|---|---|---|---|-----|--------|---|

|        | ALWAYSON |   |   |   |   | WEN | ENABLE |   |

| Access | R/W      |   |   |   |   | R/W | R/W    |   |

| Reset  | х        |   |   |   |   | х   | х      |   |

# Bit 7 – ALWAYSON: Always-On

This bit allows the WDT to run continuously. After being set, this bit cannot be written to '0', and the WDT will remain enabled until a power-on Reset is received. When this bit is '1', the Control A register

# Related Links

PORT: IO Pin Controller

#### 31.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes.

#### **Related Links**

PM - Power Manager

#### 31.5.3 Clocks

The SERCOM bus clock (CLK\_SERCOMx\_APB) can be enabled and disabled in the Main Clock Controller. Refer to *Peripheral Clock Masking* for details and default status of this clock.

A generic clock (GCLK\_SERCOMx\_CORE) is required to clock the SERCOMx\_CORE. This clock must be configured and enabled in the Generic Clock Controller before using the SERCOMx\_CORE. Refer to *GCLK - Generic Clock Controller* for details.

This generic clock is asynchronous to the bus clock (CLK\_SERCOMx\_APB). Therefore, writing to certain registers will require synchronization to the clock domains. Refer to *Synchronization* for further details.

#### **Related Links**

Peripheral Clock Masking Synchronization GCLK - Generic Clock Controller

#### 31.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

#### **Related Links**

DMAC - Direct Memory Access Controller

#### 31.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. In order to use interrupt requests of this peripheral, the Interrupt Controller (NVIC) must be configured first. Refer to *Nested Vector Interrupt Controller* for details.

#### **Related Links**

Nested Vector Interrupt Controller

#### 31.5.6 Events

Not applicable.

#### 31.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### **Related Links**

DBGCTRL

| Bit    | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|        |     |     |     |     |     |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|        | NDn |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Bits 31:0 - NDn: New Data [n = 32..64]

The register holds the New Data flags of Rx Buffers 32 to 63. The flags are set when the respective Rx Buffer has been updated from a received frame. The flags remain set until the Host clears them. A flag is cleared by writing 1 to the corresponding bit position. Writing a 0 has no effect. A hard reset will clear the register.

#### 34.8.27 Rx FIFO 0 Configuration

Name:RXF0COffset:0xA0 [ID-0000a4bb]Reset:0x00000000Property:Write-restricted

# 35. TC – Timer/Counter

# 35.1 Overview

There are up to eight TC peripheral instances.

Each TC consists of a counter, a prescaler, compare/capture channels and control logic. The counter can be set to count events, or clock pulses. The counter, together with the compare/capture channels, can be configured to timestamp input events or IO pin edges, allowing for capturing of frequency and/or pulse width.

A TC can also perform waveform generation, such as frequency generation and pulse-width modulation.

# 35.2 Features

- Selectable configuration

- 8-, 16- or 32-bit TC operation, with compare/capture channels

- 2 compare/capture channels (CC) with:

- Double buffered timer period setting (in 8-bit mode only)

- Double buffered compare channel

- Waveform generation

- Frequency generation

- Single-slope pulse-width modulation

- Input capture

- Event / IO pin edge capture

- Frequency capture

- Pulse-width capture

- Time-stamp capture

- Minimum and maximum capture

- One input event

- Interrupts/output events on:

- Counter overflow/underflow

- Compare match or capture

- Internal prescaler

- DMA support

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR: Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

#### Bit 0 – OVF: Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### 35.7.2.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x0A    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5 | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|---|-----|---|---|-----|-----|

|        |   |   |   | MCx |   |   | ERR | OVF |

| Access |   |   |   | R/W |   |   | R/W | R/W |

| Reset  |   |   |   | 0   |   |   | 0   | 0   |

#### Bit 4 – MCx: Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

#### Bit 1 – ERR: Error Interrupt Flag

This flag is set when a new capture occurs on a channel while the corresponding Match or Capture Channel x interrupt flag is set, in which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Error interrupt flag.

```

value = cycle * dithercy;

if (((MASK & value) + dithercy) > MASK)

return 1;

return 0;

}

```

# Dithering on Period

Writing DITHERCY in PER will lead to an average PWM period configured by the following formulas.

DITH4 mode:

$$PwmPeriod = \left(\frac{\text{DITHERCY}}{16} + \text{PER}\right) \left(\frac{1}{f_{\text{GCLK}_{\text{TCC}}}}\right)$$

**Note:** If DITH4 mode is enabled, the last 4 significant bits from PER/CCx or COUNT register correspond to the DITHERCY value, rest of the bits corresponds to PER/CCx or COUNT value.

DITH5 mode:

$$PwmPeriod = \left(\frac{\text{DITHERCY}}{32} + \text{PER}\right) \left(\frac{1}{f_{\text{GCLK}_{\text{TCC}}}}\right)$$

DITH6 mode:

$$PwmPeriod = \left(\frac{\text{DITHERCY}}{64} + \text{PER}\right) \left(\frac{1}{f_{\text{GCLK}_{\text{TCC}}}}\right)$$

#### **Dithering on Pulse Width**

Writing DITHERCY in CCx will lead to an average PWM pulse width configured by the following formula.

DITH4 mode:

$$PwmPulseWidth = \left(\frac{\text{DITHERCY}}{16} + \text{CCx}\right) \left(\frac{1}{f_{\text{GCLK}_{\text{TCC}}}}\right)$$

DITH5 mode:

$$PwmPulseWidth = \left(\frac{\text{DITHERCY}}{32} + \text{CCx}\right) \left(\frac{1}{f_{\text{GCLK}_{\text{TCC}}}}\right)$$

DITH6 mode:

$$PwmPulseWidth = \left(\frac{\text{DITHERCY}}{64} + \text{CCx}\right) \left(\frac{1}{f_{\text{GCLK}\_\text{TCC}}}\right)$$

Note: The PWM period will remain static in this case.

#### 36.6.3.4 Ramp Operations

Three ramp operation modes are supported. All of them require the timer/counter running in single-slope PWM generation. The ramp mode is selected by writing to the Ramp Mode bits in the Waveform Control register (WAVE.RAMP).

#### **RAMP1** Operation

This is the default PWM operation, described in Single-Slope PWM Generation.

#### **RAMP2** Operation

These operation modes are dedicated for power factor correction (PFC), Half-Bridge and Push-Pull SMPS topologies, where two consecutive timer/counter cycles are interleaved, see Figure 36-18. In cycle

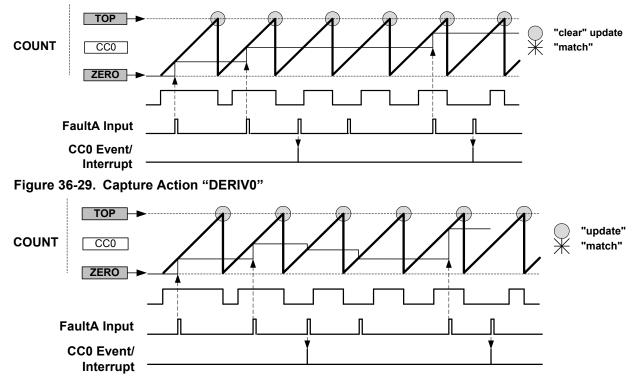

relative local Minimum (for CAPTMIN) or Maximum (for CAPTMAX) value has been detected. DERIV0 is equivalent to an OR function of (LOCMIN, LOCMAX).

In CAPT operation, capture is performed on each capture event. The MCx interrupt flag is set on each new capture.

In CAPTMIN and CAPTMAX operation, capture is performed only when on capture event time, the counter value is lower (for CAPTMIN) or upper (for CAPMAX) than the last captured value. The MCx interrupt flag is set only when on capture event time, the counter value is upper or equal (for CAPTMIN) or lower or equal (for CAPTMAX) to the value captured on the previous event. So interrupt flag is set when a new absolute local Minimum (for CAPTMIN) or Maximum (for CAPTMAX) value has been detected.

#### Interrupt Generation

In CAPT mode, an interrupt is generated on each filtered Fault n and each dedicated CCx channel capture counter value. In other modes, an interrupt is only generated on an extreme captured value.

#### Figure 36-28. Capture Action "CAPTMAX"

Hardware This is configured by writing 0x1 to the Fault n Halt mode bits in the Recoverable Fault nHalt Action Configuration register (FCTRLn.HALT). When enabled, the timer/counter is halted and the cycle is extended as long as the corresponding fault is present.

The next figure ('Waveform Generation with Halt and Restart Actions') shows an example where both restart action and hardware halt action are enabled for Fault A. The compare channel 0 output is clamped to inactive level as long as the timer/counter is halted. The timer/counter resumes the counting operation as soon as the fault condition is no longer present. As the restart action is enabled in this example, the timer/counter is restarted after the fault condition is no longer present.

Channel For a capture channel, the request is set when valid data is present in the CCx register, and cleared once the CCx register is read.(MCx) In this operation mode, the CTRLA.DMAOS bit value is ignored.

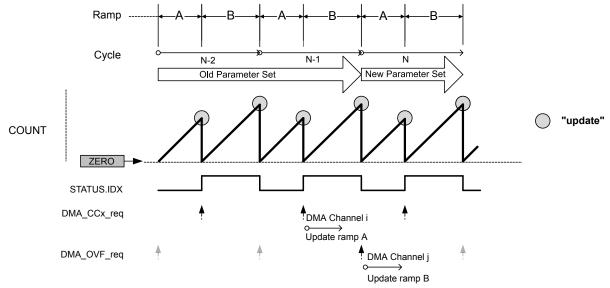

#### DMA Operation with Circular Buffer

When circular buffer operation is enabled, the buffer registers must be written in a correct order and synchronized to the update times of the timer. The DMA triggers of the TCC provide a way to ensure a safe and correct update of circular buffers.

Note: Circular buffer are intended to be used with RAMP2, RAMP2A and DSBOTH operation only.

#### DMA Operation with Circular Buffer in RAMP and RAMP2A Mode

When a CCx channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of ramp B.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of ramp A with an effective DMA transfer on previous ramp B (DMA acknowledge).

The update of all circular buffer values for ramp A can be done through a DMA channel triggered on a MC trigger. The update of all circular buffer values for ramp B, can be done through a second DMA channel triggered by the overflow DMA request.

Figure 36-37. DMA Triggers in RAMP and RAMP2 Operation Mode and Circular Buffer Enabled

DMA Operation with Circular Buffer in DSBOTH Mode

When a CC channel is selected as a circular buffer, the related DMA request is not set on a compare match detection, but on start of down-counting phase.

If at least one circular buffer is enabled, the DMA overflow request is conditioned to the start of upcounting phase with an effective DMA transfer on previous down-counting phase (DMA acknowledge).

When up-counting, all circular buffer values can be updated through a DMA channel triggered by MC trigger. When down-counting, all circular buffer values can be updated through a second DMA channel, triggered by the OVF DMA request.

# Table 37-1. Truth Table of LUT

| IN[2] | IN[1] | IN[0] | OUT      |

|-------|-------|-------|----------|

| 0     | 0     | 0     | TRUTH[0] |

| 0     | 0     | 1     | TRUTH[1] |

| 0     | 1     | 0     | TRUTH[2] |

| 0     | 1     | 1     | TRUTH[3] |

| 1     | 0     | 0     | TRUTH[4] |

| 1     | 0     | 1     | TRUTH[5] |

| 1     | 1     | 0     | TRUTH[6] |

| 1     | 1     | 1     | TRUTH[7] |

#### 37.6.2.4 Truth Table Inputs Selection

#### Input Overview

The inputs can be individually:

- Masked

- Driven by peripherals:

- Analog comparator output (AC)

- Timer/Counters waveform outputs (TC)

- Serial Communication output transmit interface (SERCOM)

- Driven by internal events from Event System

- Driven by other CCL sub-modules

The Input Selection for each input y of LUT x is configured by writing the Input y Source Selection bit in the LUT x Control register (LUTCTRLx.INSELy).

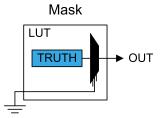

#### Masked Inputs (MASK)

When a LUT input is masked (LUTCTRLx.INSELy=MASK), the corresponding TRUTH input (IN) is internally tied to zero, as shown in this figure:

#### Figure 37-3. Masked Input Selection

#### Internal Feedback Inputs (FEEDBACK)

When selected (LUTCTRLx.INSELy=FEEDBACK), the Sequential (SEQ) output is used as input for the corresponding LUT.

The output from an internal sequential sub-module can be used as input source for the LUT, see figure below for an example for LUT0 and LUT1. The sequential selection for each LUT follows the formula:

© 2017 Microchip Technology Inc.

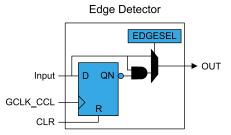

#### Figure 37-13. Edge Detector

#### 37.6.2.7 Sequential Logic

Each LUT pair can be connected to the internal sequential logic which can be configured to work as D flip flop, JK flip flop, gated D-latch or RS-latch by writing the Sequential Selection bits on the corresponding Sequential Control x register (SEQCTRLx.SEQSEL). Before using sequential logic, the GCLK\_CCL clock and optionally each LUT filter or edge detector must be enabled.

**Note:** While configuring the sequential logic, the even LUT must be disabled. When configured the even LUT must be enabled.

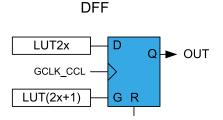

## Gated D Flip-Flop (DFF)

When the DFF is selected, the D-input is driven by the even LUT output (LUT0 and LUT2), and the G-input is driven by the odd LUT output (LUT1 and LUT3), as shown in Figure 37-14.

## Figure 37-14. D Flip Flop

When the even LUT is disabled (LUTCTRL0.ENABLE=0 / LUTCTRL2.ENABLE=0), the flip-flop is asynchronously cleared. The reset command (R) is kept enabled for one APB clock cycle. In all other cases, the flip-flop output (OUT) is refreshed on rising edge of the GCLK\_CCL, as shown in Table 37-2.

| R | G | D | ОИТ                    |

|---|---|---|------------------------|

| 1 | X | х | Clear                  |

| 0 | 1 | 1 | Set                    |

|   |   | 0 | Clear                  |

|   | 0 | Х | Hold state (no change) |

#### JK Flip-Flop (JK)

When this configuration is selected, the J-input is driven by the even LUT output (LUT0 and LUT2), and the K-input is driven by the odd LUT output (LUT1 and LUT3), as shown in Figure 37-15.

#### 39.5.6 Events

The events are connected to the Event System. Refer to the Event System section for details on how to configure the Event System.

#### **Related Links**

EVSYS – Event System

# 39.5.7 Debug Operation

When the CPU is halted in debug mode the SDADC will halt normal operation. The SDADC can be forced to continue operation

during debugging. Refer to DBGCTRL for details.

#### 39.5.8 Register Access Protection

All registers with write-access are optionally write-protected by the peripheral access controller (PAC), except the following register:

• Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply for accesses through an external debugger.

#### 39.5.9 Analog Connections

I/O-pins (AINx), as well as the REF reference voltage pins are analog inputs to the SDADC.

# 39.6 Functional Description

#### **39.6.1** Principle of Operation

The Sigma-Delta Analog-to-Digital Converter (SDADC) converts analog signals to digital values. The SDADC has 16-bit resolution, and is capable of converting up to 1.5 Msps divided by the OSR data over sampling ratio. The input selection is up to three input analog channels. The SDADC provides unsigned results.

#### **Related Links**

CTRLB

#### 39.6.2 Basic Operation

#### 39.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the SDADC is disabled (CTRLA.ENABLE is zero):

- CTRLA ONEDEMAND and RUNSTDBY bits

- CTRLB

- CTRLC

- EVCTRL

- ANACTRL

Enable-protection is denoted by the Enable-Protected property in the register description.

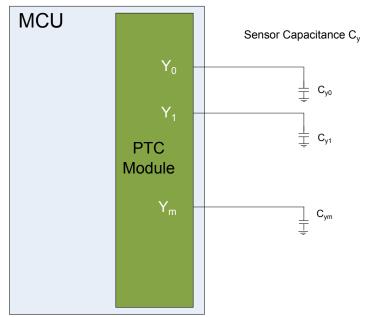

Figure 42-4. Self-capacitance Sensor Arrangement

For more information about designing the touch sensor, refer to Buttons, Sliders and Wheels Touch Sensor Design Guide.

# 42.5.2 Analog-Digital Converter (ADC)

The PTC is using the ADC for signal conversion and acquisition. The ADC must be enabled and configured appropriatly in order to allow correct behavior of the PTC.

#### **Related Links**

ADC - Analog-to-Digital Converter

# 42.6 Functional Description

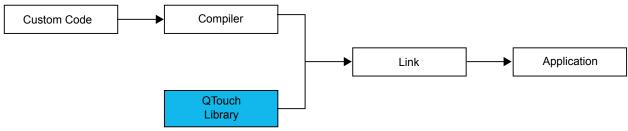

In order to access the PTC, the user must use the QTouch Composer tool to configure and link the QTouch Library firmware with the application software. QTouch Library can be used to implement buttons, sliders, wheels in a variety of combinations on a single interface.

For more information about QTouch Library, refer to the QTouch Library Peripheral Touch Controller User Guide.

| Symbol | Parameters                         | Conditions (2) | Min  | Тур  | Max  | Unit |

|--------|------------------------------------|----------------|------|------|------|------|

| ENOB   | Effective Number Of Bits           | Ext ref = 1.2V | 13.5 | 14.2 | 14.4 | dB   |

|        |                                    | Int Ref = 5.5V | 11   | 11.2 | 11.4 |      |

| DR     | Dynamic Range                      | Ext ref = 1.2V | 89   | 91   | 92   | dB   |

|        |                                    | Int Ref = 5.5V | 83   | 92   | 96   |      |

| SNR    | Signal to Noise Ratio              | Ext ref = 1.2V | 84   | 88   | 89   | dB   |

|        |                                    | Int Ref = 5.5V | 77   | 79   | 80   |      |

| SINAD  | Signal to Noise + Distortion Ratio | Ext ref = 1.2V | 83   | 87   | 89   | dB   |

|        |                                    | Int Ref = 5.5V | 68   | 69   | 71   |      |

| THD    | Total Harmonic Distortion          | Ext ref = 1.2V | -105 | -100 | -92  | dB   |

|        |                                    | Int Ref = 5.5V | -70  | -69  | -69  |      |

Table 45-24. SDADC AC Performance: : Differential Input Mode<sup>(1)</sup>

- 1. These are based on characterization.

- 2. OSR=256

#### Table 45-25. Power consumption <sup>(1)</sup>

| Symbol        | Parameters           | Conditions                                                                              | Та                   | Тур. | Max | Units |

|---------------|----------------------|-----------------------------------------------------------------------------------------|----------------------|------|-----|-------|

| IDD<br>VDDANA | Power<br>consumption | CTLSDADC=0x0 External Ref -<br>VCCANA = 5.5V Vref = 2V Ref buf on<br>SCLK_SDADC = 6 MHz | Max 85°C<br>Typ 25°C | 588  | 658 | μA    |

|               |                      | CTLSDADC=0x0 Internal Ref -<br>VDDANA=Vref= 5.5V Ref buf off<br>SCLK_SDADC = 6 MHz      | -                    | 552  | 608 |       |

1. These are based on characterization.

# 45.10.6 Digital to Analog Converter (DAC) Characteristics Table 45-26. Operating Conditions<sup>(1)</sup>

| Symbol | Parameters                   | Conditions     | Min  | Тур       | Мах           | Unit |

|--------|------------------------------|----------------|------|-----------|---------------|------|

| RES    | Input resolution             |                | -    | -         | 10            | Bits |

| VDDANA | Analog supply voltage        |                | 2.7  | -         | 5.5           | V    |

| AVREF  | External reference voltage   |                | 1    | -         | VDDANA - 0.6  | V    |

|        | Internal reference voltage 1 | VREF.SEL = 0x0 | -    | 1.024     | -             | V    |

|        |                              | VREF.SEL = 0x2 | -    | 2.048     | -             |      |

|        |                              | VREF.SEL = 0x3 | -    | 4.096 (2) | -             |      |

|        | Internal reference voltage 2 |                | -    | VDDANA    | -             | V    |

|        | Linear output voltage range  |                | 0.05 | -         | VDDANA - 0.05 | V    |

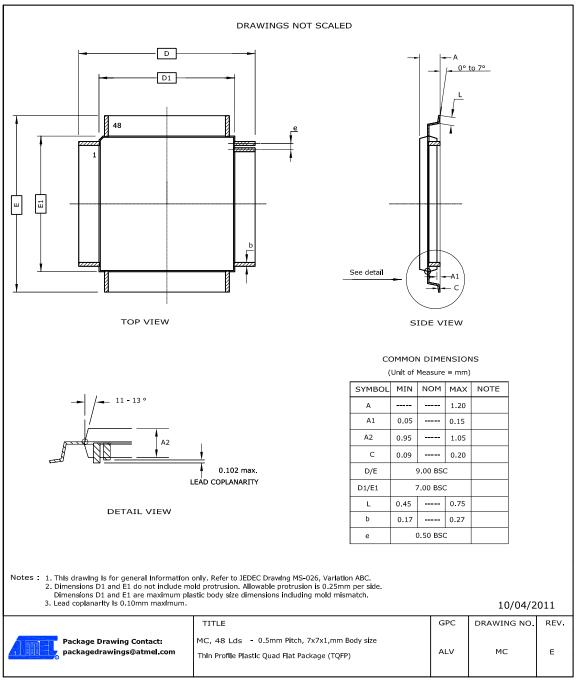

# Table 48-12. Package Characteristics Moisture Sensitivity Level MSL1 Table 48-13. Package Reference JEDEC Drawing Reference N/A JESD97 Classification e1

#### 48.2.5 48 pin TQFP