#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 38                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 14x12b, 2x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-TQFP                                                                    |

| Supplier Device Package    | 48-TQFP (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21g18a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 13. DSU - Device Service Unit

## 13.1 Overview

The Device Service Unit (DSU) provides a means of detecting debugger probes. It enables the ARM Debug Access Port (DAP) to have control over multiplexed debug pads and CPU reset. The DSU also provides system-level services to debug adapters in an ARM debug system. It implements a CoreSight Debug ROM that provides device identification as well as identification of other debug components within the system. Hence, it complies with the ARM Peripheral Identification specification. The DSU also provides system services to applications that need memory testing, as required for IEC60730 Class B compliance, for example. The DSU can be accessed simultaneously by a debugger and the CPU, as it is connected on the High-Speed Bus Matrix. For security reasons, some of the DSU features will be limited or unavailable when the device is protected by the NVMCTRL security bit.

## **Related Links**

System Services Availability when Accessed Externally and Device is Protected NVMCTRL – Non-Volatile Memory Controller Security Bit

## 13.2 Features

- CPU reset extension

- Debugger probe detection (Cold- and Hot-Plugging)

- Chip-Erase command and status

- 32-bit cyclic redundancy check (CRC32) of any memory accessible through the bus matrix

- ARM<sup>®</sup> CoreSight<sup>™</sup> compliant device identification

- Two debug communications channels with DMA connection

- Debug access port security filter

- Onboard memory built-in self-test (MBIST)

# SAM C20/C21

| Offset       | Name        | Bit Pos.     |         |        |      |          |          |  |

|--------------|-------------|--------------|---------|--------|------|----------|----------|--|

|              | Name        |              |         |        |      |          |          |  |

| 0xA9         |             | 15:8         |         |        |      |          |          |  |

| 0xAA         |             | 23:16        |         |        |      |          |          |  |

| 0xAB<br>0xAC |             | 31:24<br>7:0 |         | CHEN   |      |          | ENI[2:0] |  |

| 0xAC<br>0xAD |             | 15:8         | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xAD<br>0xAE | PCHCTRL11   | 23:16        |         |        |      |          |          |  |

| 0xAE<br>0xAF |             | 31:24        |         |        |      |          |          |  |

| 0xAF<br>0xB0 |             | 7:0          | WRTLOCK | CHEN   |      |          | EN[3:0]  |  |

| 0xB0         |             | 15:8         | WRILOCK | CHEN   |      | 6        | EN[3.0]  |  |

| 0xB1         | PCHCTRL12   | 23:16        |         |        |      |          |          |  |

| 0xB2         |             | 31:24        |         |        |      |          |          |  |

| 0xB3         |             | 7:0          | WRTLOCK | CHEN   |      | 6        | EN[3:0]  |  |

| 0xB4         |             | 15:8         | WRILOCK | CHLIN  |      | 9        |          |  |

| 0xB5<br>0xB6 | PCHCTRL13   | 23:16        |         |        |      |          |          |  |

| 0xB6         |             | 31:24        |         |        |      |          |          |  |

| 0xB7         |             | 7:0          | WRTLOCK | CHEN   |      | <u> </u> | EN[3:0]  |  |

| 0xB8         |             | 15:8         | WITLOOK | OTEN   |      | G        |          |  |

| 0xBA         | PCHCTRL14   | 23:16        |         |        |      |          |          |  |

| 0xBB         |             | 31:24        |         |        |      |          |          |  |

| 0xBC         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xBD         |             | 15:8         | WITEOOK | ONEN   |      |          |          |  |

| 0xBE         | PCHCTRL15   | 23:16        |         |        |      |          |          |  |

| 0xBF         |             | 31:24        |         |        |      |          |          |  |

| 0xC0         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xC1         |             | 15:8         |         | 0.12.1 |      |          | [0.0]    |  |

| 0xC2         | PCHCTRL16   | 23:16        |         |        |      |          |          |  |

| 0xC3         |             | 31:24        |         |        |      |          |          |  |

| 0xC4         |             | 7:0          | WRTLOCK | CHEN   | <br> | G        | EN[3:0]  |  |

| 0xC5         |             | 15:8         |         | -      |      |          |          |  |

| 0xC6         | PCHCTRL17   | 23:16        |         |        |      |          |          |  |

| 0xC7         |             | 31:24        |         |        |      |          |          |  |

| 0xC8         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xC9         |             | 15:8         |         |        |      |          |          |  |

| 0xCA         | PCHCTRL18   | 23:16        |         |        |      |          |          |  |

| 0xCB         |             | 31:24        |         |        |      |          |          |  |

| 0xCC         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xCD         | DOLLOTE     | 15:8         |         |        |      |          |          |  |

| 0xCE         | PCHCTRL19   | 23:16        |         |        |      |          |          |  |

| 0xCF         |             | 31:24        |         |        |      |          |          |  |

| 0xD0         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xD1         | DOLLOTELOG  | 15:8         |         |        |      |          |          |  |

| 0xD2         | PCHCTRL20   | 23:16        |         |        |      |          |          |  |

| 0xD3         |             | 31:24        |         |        |      |          |          |  |

| 0xD4         |             | 7:0          | WRTLOCK | CHEN   |      | G        | EN[3:0]  |  |

| 0xD5         |             | 15:8         |         |        |      |          |          |  |

| 0xD6         | - PCHCTRL21 | 23:16        |         |        |      |          |          |  |

| 0xD7         |             | 31:24        |         |        |      |          |          |  |

## Bit 1 – SERCOM0: SERCOM0 APBC Mask Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBC clock for the SERCOM0 is stopped. |

| 1     | The APBC clock for the SERCOM0 is enabled. |

## Bit 0 – EVSYS: EVSYS APBC Clock Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The APBC clock for the EVSYS is stopped. |

| 1     | The APBC clock for the EVSYS is enabled. |

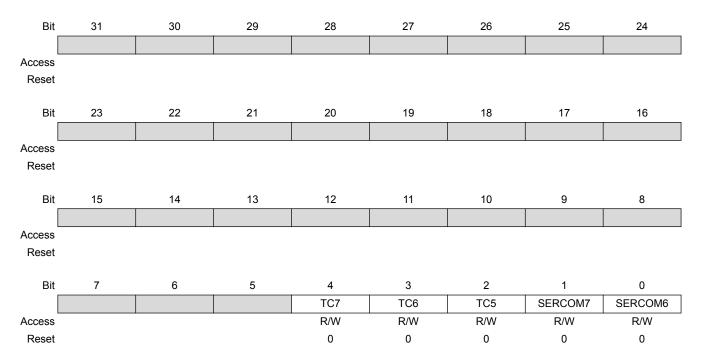

## 17.8.10 APBD Mask

Name:APBDMASKOffset:0x20Reset:0x00000000Property:PAC Write-Protection

## Bit 4 – TC7: TC7 APBD Mask Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBD clock for the TC7 is stopped. |

| 1     | The APBD clock for the TC7 is enabled. |

## Bit 3 – TC6: TC6 APBD Mask Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBD clock for the TC6 is stopped. |

| 1     | The APBD clock for the TC6 is enabled. |

## Bit 8 – DPLLLCKR: DPLL Lock Rise Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Rise Interrupt Enable bit, which disables the DPLL Lock Rise interrupt.

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Rise interrupt is disabled.                                                |

| 1     | The DPLL Lock Rise interrupt is enabled, and an interrupt request will be generated when |

|       | the DPLL Lock Rise Interrupt flag is set.                                                |

## Bit 4 – OSC48MRDY: OSC48M Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the OSC48M Ready Interrupt Enable bit, which disables the OSC48M Ready interrupt.

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The OSC48M Ready interrupt is disabled.                                                                                        |

| 1     | The OSC48M Ready interrupt is enabled, and an interrupt request will be generated when the OSC48M Ready Interrupt flag is set. |

## Bit 1 – CLKFAIL: Clock Failure Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the XOSC Clock Failure Interrupt Enable bit, which disables the XOSC Clock Failure interrupt.

| Value | Description                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC Clock Failure interrupt is disabled.                                                                                              |

| 1     | The XOSC Clock Failure interrupt is enabled, and an interrupt request will be generated when the XOSC Clock Failure Interrupt flag is set. |

## Bit 0 – XOSCRDY: XOSC Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the XOSC Ready Interrupt Enable bit, which disables the XOSC Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The XOSC Ready interrupt is disabled.                                                                                      |

| 1     | The XOSC Ready interrupt is enabled, and an interrupt request will be generated when the XOSC Ready Interrupt flag is set. |

#### 20.8.2 Interrupt Enable Set

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name:INTENSETOffset:0x04 [ID-00001eee]Reset:0x00000000Property:PAC Write-Protection

| Value   | Name    | Description                 |

|---------|---------|-----------------------------|

| 0xA     | DIV512  | CLK_RTC_CNT = GCLK_RTC/512  |

| 0xB     | DIV1024 | CLK_RTC_CNT = GCLK_RTC/1024 |

| 0xC-0xF | -       | Reserved                    |

## Bit 7 – MATCHCLR: Clear on Match

This bit defines if the counter is cleared or not on a match.

This bit is not synchronized.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The counter is not cleared on a Compare/Alarm 0 match |

| 1     | The counter is cleared on a Compare/Alarm 0 match     |

## Bits 3:2 – MODE[1:0]: Operating Mode

This bit group defines the operating mode of the RTC.

This bit is not synchronized.

| Value | Name    | Description            |

|-------|---------|------------------------|

| 0x0   | COUNT32 | Mode 0: 32-bit counter |

| 0x1   | COUNT16 | Mode 1: 16-bit counter |

| 0x2   | CLOCK   | Mode 2: Clock/calendar |

| 0x3   | -       | Reserved               |

## Bit 1 – ENABLE: Enable

Due to synchronization there is a delay between writing CTRLA.ENABLE and until the peripheral is enabled/disabled. The value written to CTRLA.ENABLE will read back immediately and the Enable bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                |

|-------|----------------------------|

| 0     | The peripheral is disabled |

| 1     | The peripheral is enabled  |

## Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the RTC (except DBGCTRL) to their initial state, and the RTC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay between writing CTRLA.SWRST and until the reset is complete. CTRLA.SWRST will be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is not reset operation ongoing |

| 1     | The reset operation is ongoing       |

## 24.8.2 Event Control in COUNT32 mode (CTRLA.MODE=0)

Name:CTRLOffset:0x00 [ID-00001ece]Reset:0x00X0Property:PAC Write-Protection, Enable-Protected

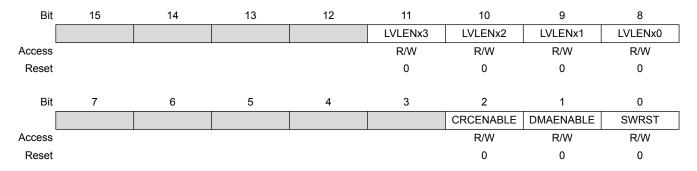

## Bits 8, 9, 10, 11 – LVLENx: Priority Level x Enable

When this bit is set, all requests with the corresponding level will be fed into the arbiter block. When cleared, all requests with the corresponding level will be ignored.

For details on arbitration schemes, refer to the Arbitration section.

These bits are not enable-protected.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | Transfer requests for Priority level x will not be handled. |

| 1     | Transfer requests for Priority level x will be handled.     |

#### Bit 2 – CRCENABLE: CRC Enable

Writing a '0' to this bit will disable the CRC calculation when the CRC Status Busy flag is cleared (CRCSTATUS. CRCBUSY). The bit is zero when the CRC is disabled.

Writing a '1' to this bit will enable the CRC calculation.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The CRC calculation is disabled. |

| 1     | The CRC calculation is enabled.  |

## Bit 1 – DMAENABLE: DMA Enable

Setting this bit will enable the DMA module.

Writing a '0' to this bit will disable the DMA module. When writing a '0' during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

This bit is not enable-protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

## Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

| Offset | Name | Bit Pos. |                |  |  |  |  |  |  |

|--------|------|----------|----------------|--|--|--|--|--|--|

| 0x2E   |      | 23:16    | PBLDATA[23:16] |  |  |  |  |  |  |

| 0x2F   |      | 31:24    | PBLDATA[31:24] |  |  |  |  |  |  |

## 27.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

## 27.8.1 Control A

Name:CTRLAOffset:0x00 [ID-00000b2c]Reset:0x0000Property:PAC Write-Protection

| Bit    | 15  | 14         | 13  | 12  | 11       | 10  | 9   | 8   |  |

|--------|-----|------------|-----|-----|----------|-----|-----|-----|--|

|        |     | CMDEX[7:0] |     |     |          |     |     |     |  |

| Access | R/W | R/W        | R/W | R/W | R/W      | R/W | R/W | R/W |  |

| Reset  | 0   | 0          | 0   | 0   | 0        | 0   | 0   | 0   |  |

|        |     |            |     |     |          |     |     |     |  |

| Bit    | 7   | 6          | 5   | 4   | 3        | 2   | 1   | 0   |  |

|        |     |            |     |     | CMD[6:0] |     |     |     |  |

| Access |     | R/W        | R/W | R/W | R/W      | R/W | R/W | R/W |  |

| Reset  |     | 0          | 0   | 0   | 0        | 0   | 0   | 0   |  |

## Bits 15:8 – CMDEX[7:0]: Command Execution

When this bit group is written to the key value 0xA5, the command written to CMD will be executed. If a value different from the key value is tried, the write will not be performed and the Programming Error bit in the Status register (STATUS.PROGE) will be set. PROGE is also set if a previously written command is not completed yet.

The key value must be written at the same time as CMD. If a command is issued through the APB bus on the same cycle as an AHB bus access, the AHB bus access will be given priority. The command will then be executed when the NVM block and the AHB bus are idle.

INTFLAG.READY must be '1' when the command is issued.

Bit 0 of the CMDEX bit group will read back as '1' until the command is issued.

Note: The NVM Address bit field in the Address register (ADDR.ADDR) uses 16-bit addressing.

## Bits 6:0 - CMD[6:0]: Command

These bits define the command to be executed when the CMDEX key is written.

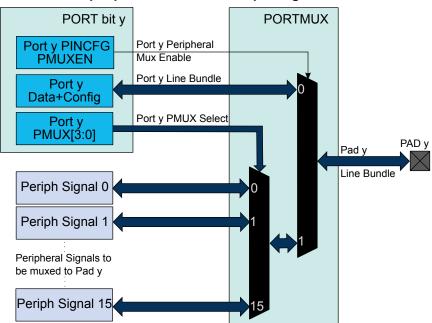

Figure 28-3. Overview of the peripheral functions multiplexing

The I/O pins of the device are controlled by PORT peripheral registers. Each port pin has a corresponding bit in the Data Direction (DIR) and Data Output Value (OUT) registers to enable that pin as an output and to define the output state.

The direction of each pin in a PORT group is configured by the DIR register. If a bit in DIR is set to '1', the corresponding pin is configured as an output pin. If a bit in DIR is set to '0', the corresponding pin is configured as an input pin.

When the direction is set as output, the corresponding bit in the OUT register will set the level of the pin. If bit y in OUT is written to '1', pin y is driven HIGH. If bit y in OUT is written to '0', pin y is driven LOW. Pin configuration can be set by Pin Configuration (PINCFGy) registers, with y=00, 01, ...31 representing the bit position.

The Data Input Value (IN) is set as the input value of a port pin with resynchronization to the PORT clock. To reduce power consumption, these input synchronizers are clocked only when system requires reading the input value. The value of the pin can always be read, whether the pin is configured as input or output. If the Input Enable bit in the Pin Configuration registers (PINCFGy.INEN) is '0', the input value will not be sampled.

In PORT, the Peripheral Multiplexer Enable bit in the PINCFGy register (PINCFGy.PMUXEN) can be written to '1' to enable the connection between peripheral functions and individual I/O pins. The Peripheral Multiplexing n (PMUXn) registers select the peripheral function for the corresponding pin. This will override the connection between the PORT and that I/O pin, and connect the selected peripheral signal to the particular I/O pin instead of the PORT line bundle.

## 28.6.2 Basic Operation

## 28.6.2.1 Initialization

After reset, all standard function device I/O pads are connected to the PORT with outputs tri-stated and input buffers disabled, even if there is no clock running.

However, specific pins, such as those used for connection to a debugger, may be configured differently, as required by their special function.

arbitration is lost during the transmission. In this case, a lost arbitration will prevent setting INTFLAG.SB. Instead, INTFLAG.MB will indicate a change in arbitration. Handling of lost arbitration is the same as for data bit transmission.

## Receiving Data Packets (SCLSM=1)

When INTFLAG.SB is set, the I<sup>2</sup>C master will already have received one data packet and transmitted an ACK or NACK, depending on CTRLB.ACKACT. At this point, CTRLB.ACKACT must be set to the correct value for the next ACK bit, and the transaction can continue by reading DATA and issuing a command if not in the smart mode.

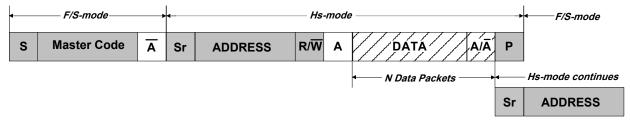

## High-Speed Mode

High-speed transfers are a multi-step process, see High Speed Transfer.

First, a master code (0b00001nnn, where 'nnn' is a unique master code) is transmitted in Full-speed mode, followed by a NACK since no slaveshould acknowledge. Arbitration is performed only during the Full-speed Master Code phase. The master code is transmitted by writing the master code to the address register (ADDR.ADDR) and writing the high-speed bit (ADDR.HS) to '0'.

After the master code and NACK have been transmitted, the master write interrupt will be asserted. In the meanwhile, the slave address can be written to the ADDR.ADDR register together with ADDR.HS=1. Now in High-speed mode, the master will generate a repeated start, followed by the slave address with RW-direction. The bus will remain in High-speed mode until a stop is generated. If a repeated start is desired, the ADDR.HS bit must again be written to '1', along with the new address ADDR.ADDR to be transmitted.

## Figure 33-8. High Speed Transfer

Transmitting in High-speed mode requires the I<sup>2</sup>C master to be configured in High-speed mode (CTRLA.SPEED=0x2) and the SCL clock stretch mode (CTRLA.SCLSM) bit set to '1'.

## 10-Bit Addressing

When 10-bit addressing is enabled by the Ten Bit Addressing Enable bit in the Address register (ADDR.TENBITEN=1) and the Address bit field ADDR.ADDR is written, the two address bytes will be transmitted, see 10-bit Address Transmission for a Read Transaction. The addressed slave acknowledges the two address bytes, and the transaction continues. Regardless of whether the transaction is a read or write, the master must start by sending the 10-bit address with the direction bit (ADDR.ADDR[0]) being zero.

If the master receives a NACK after the first byte, the write interrupt flag will be raised and the STATUS.RXNACK bit will be set. If the first byte is acknowledged by one or more slaves, then the master will proceed to transmit the second address byte and the master will first see the write interrupt flag after the second byte is transmitted. If the transaction direction is read-from-slave, the 10-bit address transmission must be followed by a repeated start and the first 7 bits of the address with the read/write bit equal to '1'.

| Bit    | 31       | 30  | 29  | 28           | 27  | 26  | 25        | 24     |

|--------|----------|-----|-----|--------------|-----|-----|-----------|--------|

|        |          |     |     |              |     |     | ]         |        |

| Access |          |     |     |              |     | R/W | R/W       | R/W    |

| Reset  |          |     |     |              |     | 0   | 0         | 0      |

|        |          |     |     |              |     |     |           |        |

| Bit    | 23       | 22  | 21  | 20           | 19  | 18  | 17        | 16     |

|        |          |     |     | ADDRMASK[6:0 | ]   |     |           |        |

| Access | R/W      | R/W | R/W | R/W          | R/W | R/W | R/W       |        |

| Reset  | 0        | 0   | 0   | 0            | 0   | 0   | 0         |        |

|        |          |     |     |              |     |     |           |        |

| Bit    | 15       | 14  | 13  | 12           | 11  | 10  | 9         | 8      |

|        | TENBITEN |     |     |              |     |     | ADDR[9:7] |        |

| Access | R/W      |     |     |              |     | R/W | R/W       | R/W    |

| Reset  | 0        |     |     |              |     | 0   | 0         | 0      |

|        |          |     |     |              |     |     |           |        |

| Bit    | 7        | 6   | 5   | 4            | 3   | 2   | 1         | 0      |

|        |          |     |     | ADDR[6:0]    |     |     |           | GENCEN |

| Access | R/W      | R/W | R/W | R/W          | R/W | R/W | R/W       | R/W    |

| Reset  | 0        | 0   | 0   | 0            | 0   | 0   | 0         | 0      |

#### Bits 26:17 – ADDRMASK[9:0]: Address Mask

These bits act as a second address match register, an address mask register or the lower limit of an address range, depending on the CTRLB.AMODE setting.

#### Bit 15 – TENBITEN: Ten Bit Addressing Enable

| Value | Description                          |

|-------|--------------------------------------|

| 0     | 10-bit address recognition disabled. |

| 1     | 10-bit address recognition enabled.  |

#### Bits 10:1 – ADDR[9:0]: Address

These bits contain the I<sup>2</sup>C slave address used by the slave address match logic to determine if a master has addressed the slave.

When using 7-bit addressing, the slave address is represented by ADDR[6:0].

When using 10-bit addressing (ADDR.TENBITEN=1), the slave address is represented by ADDR[9:0]

When the address match logic detects a match, INTFLAG.AMATCH is set and STATUS.DIR is updated to indicate whether it is a read or a write transaction.

#### Bit 0 – GENCEN: General Call Address Enable

A general call address is an address consisting of all-zeroes, including the direction bit (master write).

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | General call address recognition disabled. |

| 1     | General call address recognition enabled.  |

## 33.8.9 Data

| Value | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 0     | Last received CAN FD message did not have its BRS flag set.                                                                 |

| 1     | Last received CAN FD message had its BRS flag set. This bit is set together with RFDF, independent of acceptance filtering. |

#### Bit 11 – RESI: ESI flag of last received CAN FD Message

This field is cleared on read access.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | Last received CAN FD message did not have its ESI flag set. |

| 1     | Last received CAN FD message had its ESI flag set.          |

## Bits 10:8 – DLEC[2:0]: Data Last Error Code

Type of last error that occurred in the data phase of a CAN FD format frame with its BRS flag set. Coding is the same as for LEC. This field will be cleared to zero when a CAN FD format frame with its BRS flag set has been transferred (reception or transmission) without error.

## Bit 7 – BO: Bus\_Off Status

| Value | Description                  |

|-------|------------------------------|

| 0     | The CAN is not Bus_Off.      |

| 1     | The CAN is in Bus_Off state. |

#### Bit 6 – EW: Error Warning Status

|   | Value | Description                                                                  |

|---|-------|------------------------------------------------------------------------------|

| ſ | 0     | Both error counters are below the Error_Warning limit of 96.                 |

|   | 1     | At least one of the error counter has reached the Error_Warning limit of 96. |

#### Bit 5 – EP: Error Passive

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | The CAN is in the Error_Active state. It normally takes part in bus communication and sends |

|       | an active error flag when an error has been detected.                                       |

| 1     | The CAN is in the Error_Passive state.                                                      |

#### Bits 4:3 – ACT[1:0]: Activity

Monitors the module's CAN communication state.

| Value | Name | Description                                 |

|-------|------|---------------------------------------------|

| 0x0   | SYNC | Node is synchronizing on CAN communication. |

| 0x1   | IDLE | Node is neither receiver nor transmitter.   |

| 0x2   | RX   | Node is operating as receiver.              |

| 0x3   | TX   | Node is operating as transmitter.           |

## Bits 2:0 – LEC[2:0]: Last Error Code

The LEC indicates the type of the last error to occur on the CAN bus. This field will be cleared to '0' when a message has been transferred (reception or transmission) without error.

This field is set on read access.

# SAM C20/C21

| Bit    | 31 | 30 | 29   | 28     | 27   | 26     | 25   | 24   |

|--------|----|----|------|--------|------|--------|------|------|

|        |    |    |      |        |      |        |      |      |

| Access |    |    |      |        |      |        |      |      |

| Reset  |    |    |      |        |      |        |      |      |

|        |    |    |      |        |      |        |      |      |

| Bit    | 23 | 22 | 21   | 20     | 19   | 18     | 17   | 16   |

|        |    |    |      |        |      |        |      |      |

| Access |    |    | •    |        |      |        |      |      |

| Reset  |    |    |      |        |      |        |      |      |

|        |    |    |      |        |      |        |      |      |

| Bit    | 15 | 14 | 13   | 12     | 11   | 10     | 9    | 8    |

|        |    |    |      |        |      |        |      |      |

| Access |    |    |      |        |      |        |      |      |

| Reset  |    |    |      |        |      |        |      |      |

|        |    |    |      |        |      |        |      |      |

| Bit    | 7  | 6  | 5    | 4      | 3    | 2      | 1    | 0    |

|        |    |    | ANFS | S[1:0] | ANFE | E[1:0] | RRFS | RRFE |

| Access |    |    | R/W  | R/W    | R/W  | R/W    | R/W  | R/W  |

| Reset  |    |    | 0    | 0      | 0    | 0      | 0    | 0    |

## Bits 5:4 – ANFS[1:0]: Accept Non-matching Frames Standard

Defines how received messages with 11-bit IDs that do not match any element of the filter list are treated.

| Value  | Name   | Description          |

|--------|--------|----------------------|

| 0x0    | RXF0   | Accept in Rx FIFO 0. |

| 0x1    | RXF1   | Accept in Rx FIFO 1. |

| 0x2 or | REJECT | Reject               |

| 0x3    |        |                      |

## Bits 3:2 – ANFE[1:0]: Accept Non-matching Frames Extended

Defines how received messages with 29-bit IDs that do not match any element of the filter list are treated.

| Value  | Name   | Description          |

|--------|--------|----------------------|

| 0x0    | RXF0   | Accept in Rx FIFO 0. |

| 0x1    | RXF1   | Accept in Rx FIFO 1. |

| 0x2 or | REJECT | Reject               |

| 0x3    |        |                      |

#### Bit 1 – RRFS: Reject Remote Frames Standard

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | Filter remote frames with 11-bit standard IDs.     |

| 1     | Reject all remote frames with 11-bit standard IDs. |

#### Bit 0 – RRFE: Reject Remote Frames Extended

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | Filter remote frames with 29-bit extended IDs.     |

| 1     | Reject all remote frames with 29-bit extended IDS. |

#### 34.8.21 Standard ID Filter Configuration

This register is write-restricted and only writable if bit fields CCCR.CCE = 1 and CCCR.INIT = 1.

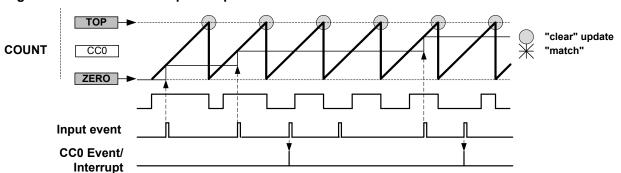

## Figure 35-16. Maximum Capture Operation with CC0 Initialized with ZERO Value

## 35.6.4 DMA Operation

The TC can generate the following DMA requests:

- Overflow (OVF): the request is set when an update condition (overflow, underflow or re-trigger) is detected, the request is cleared by hardware on DMA acknowledge.

- Match or Capture Channel x (MCx): for a compare channel, the request is set on each compare

match detection, the request is cleared by hardware on DMA acknowledge. For a capture channel,

the request is set when valid data is present in the CCx register, and cleared when CCx register is

read.

## 35.6.5 Interrupts

The TC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Match or Capture Channel x (MCx)

- Capture Overflow Error (ERR)

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the TC is reset. See INTFLAG for details on how to clear interrupt flags.

The TC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

## **Related Links**

Nested Vector Interrupt Controller

#### 35.6.6 Events

The TC can generate the following output events:

- Overflow/Underflow (OVF)

- Match or Capture Channel x (MCx)

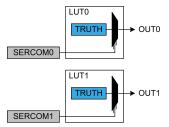

## Figure 37-11. SERCOM Input Selection

## **Related Links**

I/O Multiplexing and Considerations

PORT: IO Pin Controller

GCLK - Generic Clock Controller

AC – Analog Comparators

TC – Timer/Counter

TCC – Timer/Counter for Control Applications

SERCOM – Serial Communication Interface

I/O Multiplexing and Considerations

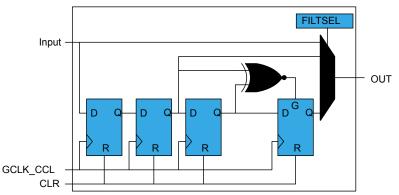

#### 37.6.2.5 Filter

By default, the LUT output is a combinatorial function of the LUT inputs. This may cause some short glitches when the inputs change value. These glitches can be removed by clocking through filters, if demanded by application needs.

The Filter Selection bits in LUT Control register (LUTCTRLx.FILTSEL) define the synchronizer or digital filter options. When a filter is enabled, the OUT output will be delayed by two to five GCLK cycles. One APB clock after the corresponding LUT is disabled, all internal filter logic is cleared. **Note:** Events used as LUT input will also be filtered, if the filter is enabled.

#### Figure 37-12. Filter

#### 37.6.2.6 Edge Detector

The edge detector can be used to generate a pulse when detecting a rising edge on its input. To detect a falling edge, the TRUTH table should be inverted.

The edge detector is enabled by writing '1' to the Edge Selection bit in LUT Control register (LUTCTRLx.EDGESEL). In order to avoid unpredictable behavior, either the filter or synchronizer must be enabled.

Edge detection is disabled by writing a '0' to LUTCTRLx.EDGESEL. After disabling a LUT, the corresponding internal Edge Detector logic is cleared one APB clock cycle later.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 38.8.2 Control B

Name:CTRLBOffset:0x01 [ID-0000120e]Reset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7 | 6 | 5 | 4 | 3 | 2   | 1             | 0   |

|--------|---|---|---|---|---|-----|---------------|-----|

|        |   |   |   |   |   |     | PRESCALER[2:0 | )]  |

| Access |   | • |   |   |   | R/W | R/W           | R/W |

| Reset  |   |   |   |   |   | 0   | 0             | 0   |

## Bits 2:0 – PRESCALER[2:0]: Prescaler Configuration

This field defines the ADC clock relative to the peripheral clock.

This field is not synchronized. For the slave ADC, these bits have no effect when the SLAVEEN bit is set (CTRLA.SLAVEEN= 1).

| Value | Name   | Description                     |

|-------|--------|---------------------------------|

| 0x0   | DIV2   | Peripheral clock divided by 2   |

| 0x1   | DIV4   | Peripheral clock divided by 4   |

| 0x2   | DIV8   | Peripheral clock divided by 8   |

| 0x3   | DIV16  | Peripheral clock divided by 16  |

| 0x4   | DIV32  | Peripheral clock divided by 32  |

| 0x5   | DIV64  | Peripheral clock divided by 64  |

| 0x6   | DIV128 | Peripheral clock divided by 128 |

| 0x7   | DIV256 | Peripheral clock divided by 256 |

#### 38.8.3 Reference Control

Name:REFCTRLOffset:0x02 [ID-0000120e]Reset:0x00Property:PAC Write-Protection, Enable-Protected

| Bit    | 7       | 6 | 5 | 4 | 3   | 2     | 1       | 0   |

|--------|---------|---|---|---|-----|-------|---------|-----|

|        | REFCOMP |   |   |   |     | REFSE | EL[3:0] |     |

| Access | R/W     |   |   |   | R/W | R/W   | R/W     | R/W |

| Reset  | 0       |   |   |   | 0   | 0     | 0       | 0   |

#### Bit 7 – REFCOMP: Reference Buffer Offset Compensation Enable

The gain error can be reduced by enabling the reference buffer offset compensation. This will decrease the input impedance and thus increase the start-up time of the reference.

Name:ANACTRLOffset:0x2C [ID-0000243d]Reset:0x00Property:PAC Write-Protection, Write-Synchronized.

| Bit    | 7       | 6      | 5 | 4   | 3   | 2             | 1   | 0   |

|--------|---------|--------|---|-----|-----|---------------|-----|-----|

|        | BUFTEST | ONCHOP |   |     |     | CTLSDADC[4:0] |     |     |

| Access | R/W     | R/W    |   | R/W | R/W | R/W           | R/W | R/W |

| Reset  | 0       | 0      |   | 0   | 0   | 0             | 0   | 0   |

## Bit 7 – BUFTEST: Buffer Test

#### Bit 6 – ONCHOP: ONCHOP

| Value | Description               |

|-------|---------------------------|

| 0     | No Chopper at SDADC input |

| 1     | Chopper at SDADC input    |

## Bits 4:0 – CTLSDADC[4:0]: CTLSDADC

SDADC Bias Current Control and used for Debugg/Characterization

## 39.8.22 Debug Control

Name:DBGCTRLOffset:0x2E [ID-0000243d]Reset:0x00Property:PAC Write-Protectedion

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

|--------|---|---|---|---|---|---|---|--------|

|        |   |   |   |   |   |   |   | DBGRUN |

| Access |   |   |   |   |   |   |   | R/W    |

| Reset  |   |   |   |   |   |   |   | 0      |

#### Bit 0 – DBGRUN: Debug Run

This bit is not reset by a software reset.

This bit controls the functionality when the CPU is halted by an external debugger.

This bit should be written only while a conversion is not ongoing.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The SDADC is halted when the CPU is halted by an external debugger.                  |

| 1     | The SDADC continues normal operation when the CPU is halted by an external debugger. |

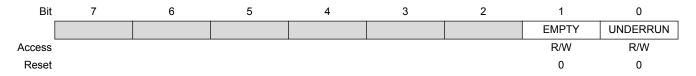

Writing a '1' to this bit will clear the Data Buffer Empty Interrupt Enable bit, which disables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

#### Bit 0 – UNDERRUN: Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer Underrun Interrupt Enable bit, which disables the Data Buffer Underrun interrupt.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Data Buffer Underrun interrupt is disabled. |

| 1     | The Data Buffer Underrun interrupt is enabled.  |

#### 41.8.5 Interrupt Enable Set

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

Name:INTENSETOffset:0x05 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection

#### Bit 1 – EMPTY: Data Buffer Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Empty Interrupt Enable bit, which enables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

#### Bit 0 – UNDERRUN: Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Underrun Interrupt Enable bit, which enables the Data Buffer Underrun interrupt.

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | The Data Buffer Underrun interrupt is disabled. |

| 1     | The Data Buffer Underrun interrupt is enabled.  |

#### 41.8.6 Interrupt Flag Status and Clear

# 45. Electrical Characteristics 85°C (SAM C20/C21 E/G/J)

## **Related Links**

Electrical Characteristics 105°C (SAM C20/C21 E/G/J)

## 45.1 Disclaimer

All typical values are measured at Ta = 25°C unless otherwise specified. All minimum and maximum values are valid across operating temperature and voltage unless otherwise specified.

This chapter only contains characteristics specific for SAM C20/C21 E/G/J.

## 45.2 Absolute Maximum Ratings

Stresses beyond those listed in the below table may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Table 45-1. Absolute maximum ratings

| Symbol               | Parameter                                           | Min.     | Max.                  | Units |

|----------------------|-----------------------------------------------------|----------|-----------------------|-------|

| V <sub>DD</sub>      | Power supply voltage                                | 0        | 6.1                   | V     |

| I <sub>VDD</sub>     | Current into a V <sub>DD</sub> pin                  | -        | 92                    | mA    |

| I <sub>GND</sub>     | Current out of a GND pin                            | -        | 130                   | mA    |

| V <sub>PIN</sub>     | Pin voltage with respect to GND and $V_{\text{DD}}$ | GND-0.6V | V <sub>DD</sub> +0.6V | V     |

| T <sub>STORAGE</sub> | Storage temperature                                 | -60      | 150                   | °C    |

**Caution:** This device is sensitive to electrostatic discharges (ESD). Improper handling may lead to permanent performance degradation or malfunctioning.

Handle the device following best practice ESD protection rules: Be aware that the human body can accumulate charges large enough to impair functionality or destroy the device.

**Caution:** In debugger cold-plugging mode, NVM erase operations are not protected by the BODVDD and BODCORE. NVM erase operation at supply voltages below specified minimum can cause corruption of NVM areas that are mandatory for correct device behavior.

## **Related Links**

**GPIO Clusters**

## 45.3 General Operating Ratings

The device must operate within the ratings listed in the table below in order for all other electrical characteristics and typical characteristics of the device to be valid.

| Symbol | Parameter                 | Conditions    | Min. | Тур. | Max  | Units   |

|--------|---------------------------|---------------|------|------|------|---------|

|        |                           | F = 4 MHz     | -    | -    | 20   |         |

|        |                           | F = 8 MHz     | -    | -    | 20   |         |

|        |                           | F = 16 MHz    | -    | -    | 20   |         |

|        |                           | F = 32 MHz    | -    | -    | 18   |         |

| ESR    | Crystal Equivalent Series | F = 0.455 MHz | -    | -    | 443  | Ω       |

|        | Resistance - SF = 3       | CL = 100pF    |      |      |      |         |

|        |                           | XOSC.GAIN = 0 |      |      |      |         |

|        |                           | F = 2MHz      | -    | -    | 383  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=0   |      |      |      |         |

|        |                           | F = 4MHz      | -    | _    | 218  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=1   |      |      |      |         |

|        |                           | F = 8MHz      | -    | -    | 114  |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=2   |      |      |      |         |

|        |                           | F = 16MHz     | _    | _    | 61   |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=3   |      |      |      |         |

|        |                           | F = 32MHz     | -    | _    | 41   |         |

|        |                           | CL=18pF       |      |      |      |         |

|        |                           | XOSC.GAIN=4   |      |      |      |         |

| Cxin   | Parasitic load capacitor  |               | -    | 5.9  | _    | pF      |

| Cxout  | _                         |               | -    | 3.1  | -    |         |

| Tstart | Startup time              | F = 2MHz      | -    | 12.3 | 35.3 | KCycles |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=0   |      |      |      |         |

|        |                           | F = 4MHz      | -    | 8.2  | 21.4 |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | XOSC.GAIN=1   |      |      |      |         |

|        |                           | F = 8MHz      | -    | 6.2  | 14.3 |         |

|        |                           | CL=20pF       |      |      |      |         |

|        |                           | •             |      |      |      |         |

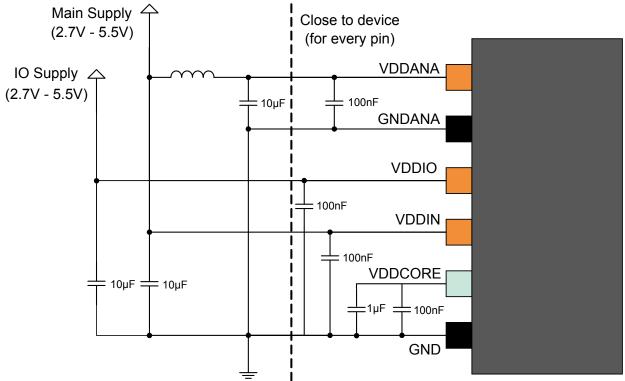

Table 49-1. Power Supply Connections, V<sub>DDCORE</sub> From Internal Regulator

Figure 49-2. Dual Power Supply Schematic

| Signal Name         | Recommended Pin Connection                                                                                                                                                           | Description                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| V <sub>DDIO</sub>   | 2.7V to 5.5V Decoupling/filtering capacitors $100nF^{(1)(2)}$ and $10\mu F^{(1)}$ Decoupling/filtering inductor $10\mu H^{(1)(3)}$                                                   | I/O supply voltage                               |

| V <sub>DDANA</sub>  | 2.7V to 5.5V Decoupling/filtering capacitors $100nF^{(1)(2)}$ and $10\mu F^{(1)}$ Ferrite bead <sup>(4)</sup> prevents the V <sub>DD</sub> noise interfering with V <sub>DDANA</sub> | Analog supply voltage                            |

| V <sub>DDIN</sub>   | 2.7V to 5.5V Decoupling/filtering capacitors $100nF^{(1)(2)}$ and $10\mu F^{(1)}$ Decoupling/filtering inductor $10\mu H^{(1)(3)}$                                                   | Digital supply voltage                           |

| V <sub>DDCORE</sub> | 1.1V to 1.3V typical Decoupling/filtering capacitors $100nF^{(1)(2)}\text{and }1\mu F^{(1)}$                                                                                         | Core supply voltage /<br>external decoupling pin |

| GND                 |                                                                                                                                                                                      | Ground                                           |

| GND <sub>ANA</sub>  |                                                                                                                                                                                      | Ground for the analog power domain               |

1. These values are only given as a typical example.