#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 52                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b, 3x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21j18a-mnt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# SAM C20/C21

| Offset | Name         | Bit Pos. |         |      |  |   |         |  |

|--------|--------------|----------|---------|------|--|---|---------|--|

| 0x0107 |              | 31:24    |         |      |  |   |         |  |

| 0x0108 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0109 | PCHCTRL34    | 15:8     |         |      |  |   |         |  |

| 0x010A | T ONO TREOT  | 23:16    |         |      |  |   |         |  |

| 0x010B |              | 31:24    |         |      |  |   |         |  |

| 0x010C |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x010D | PCHCTRL35    | 15:8     |         |      |  |   |         |  |

| 0x010E |              | 23:16    |         |      |  |   |         |  |

| 0x010F |              | 31:24    |         |      |  |   |         |  |

| 0x0110 | PCHCTRL36    | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0111 |              | 15:8     |         |      |  |   |         |  |

| 0x0112 |              | 23:16    |         |      |  |   |         |  |

| 0x0113 |              | 31:24    |         |      |  |   |         |  |

| 0x0114 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0115 | PCHCTRL37    | 15:8     |         |      |  |   |         |  |

| 0x0116 |              | 23:16    |         |      |  |   |         |  |

| 0x0117 |              | 31:24    |         |      |  |   |         |  |

| 0x0118 | PCHCTRL38    | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0119 |              | 15:8     |         |      |  |   |         |  |

| 0x011A |              | 23:16    |         |      |  |   |         |  |

| 0x011B |              | 31:24    |         |      |  |   |         |  |

| 0x011C | PCHCTRL39    | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x011D |              | 15:8     |         |      |  |   |         |  |

| 0x011E |              | 23:16    |         |      |  |   |         |  |

| 0x011F |              | 31:24    |         |      |  |   |         |  |

| 0x0120 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0121 | PCHCTRL40    | 15:8     |         |      |  |   |         |  |

| 0x0122 | T ONOTICE TO | 23:16    |         |      |  |   |         |  |

| 0x0123 |              | 31:24    |         |      |  |   |         |  |

| 0x0124 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0125 | PCHCTRL41    | 15:8     |         |      |  |   |         |  |

| 0x0126 | 1 OHOTTLEFT  | 23:16    |         |      |  |   |         |  |

| 0x0127 |              | 31:24    |         |      |  |   |         |  |

| 0x0128 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0129 | PCHCTRL42    | 15:8     |         |      |  |   |         |  |

| 0x012A | 1 CHOTILETZ  | 23:16    |         |      |  |   |         |  |

| 0x012B |              | 31:24    |         |      |  |   |         |  |

| 0x012C |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x012D | PCHCTRL43    | 15:8     |         |      |  |   |         |  |

| 0x012E | . CHOTILE    | 23:16    |         |      |  |   |         |  |

| 0x012F | -            | 31:24    |         |      |  |   |         |  |

| 0x0130 |              | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0131 | PCHCTRL44    | 15:8     |         |      |  |   |         |  |

| 0x0132 |              | 23:16    |         |      |  |   |         |  |

| 0x0133 |              | 31:24    |         |      |  |   |         |  |

| 0x0134 | PCHCTRL45    | 7:0      | WRTLOCK | CHEN |  | G | EN[3:0] |  |

| 0x0135 |              | 15:8     |         |      |  |   |         |  |

## 17.5.2 Power Management

The MCLK will operate in all sleep modes if a synchronous clock is required in these modes.

#### **Related Links**

PM - Power Manager

## 17.5.3 Clocks

The MCLK bus clock (CLK\_MCLK\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_MCLK\_APB can be found in the Peripheral Clock Masking section. If this clock is disabled, it can only be re-enabled by a reset.

The Generic Clock GCLK\_MAIN is required to generate the Main Clocks. GCLK\_MAIN is configured in the Generic Clock Controller, and can be re-configured by the user if needed.

#### **Related Links**

GCLK - Generic Clock Controller Peripheral Clock Masking

#### 17.5.3.1 Main Clock

The main clock GCLK\_MAIN is the common source for the synchronous clocks. This is fed into the common 8-bit prescaler that is used to generate synchronous clocks to the CPU, AHBx, and APBx modules.

## 17.5.3.2 CPU Clock

The CPU clock (CLK\_CPU) is routed to the CPU. Halting the CPU clock inhibits the CPU from executing instructions.

#### 17.5.3.3 APBx and AHBx Clock

The APBx clocks (CLK\_APBx) and the AHBx clocks (CLK\_AHBx) are the root clock source used by modules requiring a clock on the APBx and the AHBx bus. These clocks are always synchronous to the CPU clock, and can run even when the CPU clock is turned off in sleep mode. A clock gater is inserted after the common APB clock to gate any APBx clock of a module on APBx bus, as well as the AHBx clock.

#### 17.5.3.4 Clock Domains

The device has these synchronous clock domains:

• CPU synchronous clock domain (CPU Clock Domain). Frequency is f<sub>CPU</sub>.

See also the related links for the clock domain partitioning.

#### **Related Links**

Peripheral Clock Masking

## 17.5.4 DMA

Not applicable.

## 17.5.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the MCLK interrupt requires the Interrupt Controller to be configured first.

#### 17.5.6 Events

Not applicable.

In the case the application can recover the XOSC, the application can switch back to the XOSC clock by writing a '1' to Switch Back Enable bit in the Clock Failure Control register (XOSCCTRL.SWBACK). Once the XOSC clock is switched back, the Switch Back bit (XOSCCTRL.SWBACK) is cleared by hardware.

#### Prescaler

The CFD has an internal configurable prescaler to generate the safe clock from the OSC48M oscillator. The prescaler size allows to scale down the OSC48M oscillator so the safe clock frequency is not higher than the XOSC clock frequency monitored by the CFD. The division factor is 2^P, with P being the value of the CFD Prescaler bits in the CFD Prescaler Register (CFDPRESC.CFDPRESC).

## Example

For an external crystal oscillator at 0.4MHz and the OSC48M frequency at 16MHz, the CFDPRESC.CFDPRESC value should be set scale down by more than factor 16/0.4=80, e.g. to 128, for a safe clock of adequate frequency.

## Event

If the Event Output Enable bit in the Event Control register (EVCTRL.CFDEO) is set, the CFD clock failure will be output on the Event Output. When the CFD is switched to the safe clock, the CFD clock failure will not be output on the Event Output.

#### Sleep Mode

The CFD is halted depending on configuration of the XOSC and the peripheral clock request. For further details, refer to the Sleep Behavior table above. The CFD interrupt can be used to wake up the device from sleep modes.

## 20.6.4 48MHz Internal Oscillator (OSC48M) Operation

The OSC48M is an internal oscillator operating in open-loop mode and generating 48MHz frequency. The OSC48M frequency is selected by writing to the Division Factor field in the OSC48MDIV register (OSC48MDIV.DIV). OSC48M is enabled by writing '1' to the Oscillator Enable bit in the OSC48M Control register (OSC48MCTRL.ENABLE), and disabled by writing a '0' to this bit.

After enabling OSC48M, the OSC48M clock is output as soon as the oscillator is ready (STATUS.OSC48MRDY=1). User must ensure that the OSC48M is fully disabled before enabling it by reading STATUS.OSC48MRDY=0.

After reset, OSC48M is enabled and serves as the default clock source at 4MHz.

OSC48M will behave differently in different sleep modes based on the settings of OSC48MCTRL.RUNSTDBY, OSC48MCTRL.ONDEMAND, and OSC48MCTRL.ENABLE. If OSC48MCTRL.ENABLE=0, the OSC48M will be always stopped. For OSC48MCTRL.ENABLE=1, this table is valid:

#### Table 20-2. OSC48M Sleep Behavior

| CPU Mode       | OSC48MCTRL.RUN<br>STDBY | OSC48MCTRL.OND<br>EMAND | Sleep Behavior                 |

|----------------|-------------------------|-------------------------|--------------------------------|

| Active or Idle | -                       | 0                       | Always run                     |

| Active or Idle | -                       | 1                       | Run if requested by peripheral |

| Standby        | 1                       | 0                       | Always run                     |

This startup time can be configured by changing the Oscillator Start-Up Time bit group (OSC32K.STARTUP) in the OSC32K Control register. During the start-up time, the oscillator output is masked to ensure that no unstable clock propagates to the digital logic.

Once the external clock or crystal oscillator is stable and ready to be used as a clock source, the OSC32K Ready bit in the Status register is set (STATUS.OSC32KRDY=1). The transition of STATUS.OSC32KRDY from '0' to '1' generates an interrupt if the OSC32K Ready bit in the Interrupt Enable Set register is set (INTENSET.OSC32KRDY=1).

The OSC32K can be used as a source for Generic Clock Generators (GCLK) or for the Real-Time Counter (RTC). Before enabling the GCLK or the RTC module, the corresponding oscillator output must be enabled (OSC32K.EN32K or OSC32K.EN1K) in order to ensure proper operation. In the same way, the GCLK or RTC modules must be disabled before the clock selection is changed.

## **Related Links**

NVM Software Calibration Area Mapping RTC – Real-Time Counter Real-Time Counter Clock Selection

## 21.6.5 32KHz Ultra Low Power Internal Oscillator (OSCULP32K) Operation

The OSCULP32K provides a tunable, low-speed, and ultra-low-power clock source. The OSCULP32K is factory-calibrated under typical voltage and temperature conditions. The OSCULP32K should be preferred to the OSC32K whenever the power requirements are prevalent over frequency stability and accuracy.

The OSCULP32K is enabled by default after a power-on reset (POR) and will always run except during POR. The frequency of the OSCULP32K oscillator is controlled by the value in the 32KHz Ultra Low Power Internal Oscillator Calibration bits in the 32KHz Ultra Low Power Internal Oscillator Control register (OSCULP32K.CALIB). This data is used to compensate for process variations.

OSCULP32K.CALIB is automatically loaded from Flash Factory Calibration during start-up. The calibration value can be overridden by the user by writing to OSCULP32K.CALIB.

It is also possible to lock the OSCULP32K configuration by setting the Write Lock bit in the 32KHz Ultra Low Power Internal Oscillator Control register (OSCULP32K.WRTLOCK=1). If set, the OSCULP32K configuration is locked until a power-on reset (POR) is detected.

The OSCULP32K can be used as a source for Generic Clock Generators (GCLK) or for the Real-Time Counter (RTC). To ensure proper operation, the GCLK or RTC modules must be disabled before the clock selection is changed.

## **Related Links**

RTC – Real-Time Counter Real-Time Counter Clock Selection GCLK - Generic Clock Controller

## 21.6.6 Watchdog Timer Clock Selection

The Watchdog Timer (WDT) uses the internal 1.024kHz OSCULP32K output clock. This clock is running all the time and internally enabled when requested by the WDT module.

## **Related Links**

WDT – Watchdog Timer

| Valu | Ie | Description         |

|------|----|---------------------|

| 0    |    | BODVDD is disabled. |

| 1    |    | BODVDD is enabled.  |

## **Related Links**

Electrical Characteristics 85°C (SAM C20/C21 E/G/J) NVM User Row Mapping

## 22.8.6 Voltage Regulator System (VREG) Control

Name:VREGOffset:0x18 [ID-00001e33]Reset:0x00000000Property:PAC Write-Protection

| Bit    | 31 | 30       | 29 | 28 | 27 | 26 | 25     | 24 |

|--------|----|----------|----|----|----|----|--------|----|

|        |    |          |    |    |    |    |        |    |

| Access | R  | R        | R  | R  | R  | R  | R      | R  |

| Reset  | 0  | 0        | 0  | 0  | 0  | 0  | 0      | 0  |

|        |    |          |    |    |    |    |        |    |

| Bit    | 23 | 22       | 21 | 20 | 19 | 18 | 17     | 16 |

|        |    |          |    |    |    |    |        |    |

| Access | R  | R        | R  | R  | R  | R  | R      | R  |

| Reset  | 0  | 0        | 0  | 0  | 0  | 0  | 0      | 0  |

|        |    |          |    |    |    |    |        |    |

| Bit    | 15 | 14       | 13 | 12 | 11 | 10 | 9      | 8  |

|        |    |          |    |    |    |    |        |    |

| Access | R  | R        | R  | R  | R  | R  | R      | R  |

| Reset  | 0  | 0        | 0  | 0  | 0  | 0  | 0      | 0  |

|        |    |          |    |    |    |    |        |    |

| Bit    | 7  | 6        | 5  | 4  | 3  | 2  | 1      | 0  |

|        |    | RUNSTDBY |    |    |    |    | ENABLE |    |

| Access | R  | R/W      | R  | R  | R  | R  | R/W    | R  |

| Reset  | 0  | 0        | 0  | 0  | 0  | 0  | 0      | 0  |

## Bit 6 – RUNSTDBY: Run in Standby

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | The voltage regulator is in low power mode in Standby sleep mode. |

| 1     | The voltage regulator is in normal mode in Standby sleep mode.    |

#### Bit 1 – ENABLE: Enable

| Value | Description                        |

|-------|------------------------------------|

| 0     | The voltage regulator is disabled. |

| 1     | The voltage regulator is enabled.  |

## 22.8.7 Voltage References System (VREF) Control

Name:CTRLOffset:0x00 [ID-00001ece]Reset:0x00X0Property:PAC Write-Protection, Enable-Protected

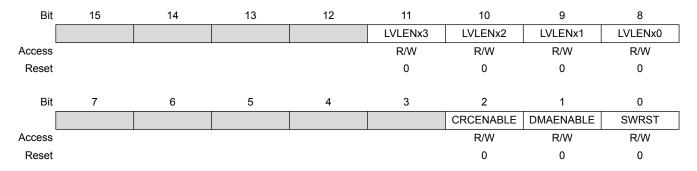

## Bits 8, 9, 10, 11 – LVLENx: Priority Level x Enable

When this bit is set, all requests with the corresponding level will be fed into the arbiter block. When cleared, all requests with the corresponding level will be ignored.

For details on arbitration schemes, refer to the Arbitration section.

These bits are not enable-protected.

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | Transfer requests for Priority level x will not be handled. |

| 1     | Transfer requests for Priority level x will be handled.     |

#### Bit 2 – CRCENABLE: CRC Enable

Writing a '0' to this bit will disable the CRC calculation when the CRC Status Busy flag is cleared (CRCSTATUS. CRCBUSY). The bit is zero when the CRC is disabled.

Writing a '1' to this bit will enable the CRC calculation.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The CRC calculation is disabled. |

| 1     | The CRC calculation is enabled.  |

### Bit 1 – DMAENABLE: DMA Enable

Setting this bit will enable the DMA module.

Writing a '0' to this bit will disable the DMA module. When writing a '0' during an ongoing transfer, the bit will not be cleared until the internal data transfer buffer is empty and the DMA transfer is aborted. The internal data transfer buffer will be empty once the ongoing burst transfer is completed.

This bit is not enable-protected.

| Value | Description                 |

|-------|-----------------------------|

| 0     | The peripheral is disabled. |

| 1     | The peripheral is enabled.  |

## Bit 0 – SWRST: Software Reset

Writing a '0' to this bit has no effect.

| Bit    | 31          | 30 | 29 | 28   | 27      | 26      | 25     | 24     |  |  |

|--------|-------------|----|----|------|---------|---------|--------|--------|--|--|

|        | BTCNT[15:8] |    |    |      |         |         |        |        |  |  |

| Access | R           | R  | R  | R    | R       | R       | R      | R      |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0       | 0      | 0      |  |  |

|        |             |    |    |      |         |         |        |        |  |  |

| Bit    | 23          | 22 | 21 | 20   | 19      | 18      | 17     | 16     |  |  |

|        |             |    |    | BTCN | IT[7:0] |         |        |        |  |  |

| Access | R           | R  | R  | R    | R       | R       | R      | R      |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0       | 0      | 0      |  |  |

|        |             |    |    |      |         |         |        |        |  |  |

| Bit    | 15          | 14 | 13 | 12   | 11      | 10      | 9      | 8      |  |  |

|        | ABUSY       |    |    |      |         | ID[4:0] |        |        |  |  |

| Access | R           |    |    | R    | R       | R       | R      | R      |  |  |

| Reset  | 0           |    |    | 0    | 0       | 0       | 0      | 0      |  |  |

|        |             |    |    |      |         |         |        |        |  |  |

| Bit    | 7           | 6  | 5  | 4    | 3       | 2       | 1      | 0      |  |  |

|        |             |    |    |      | LVLEXx  | LVLEXx  | LVLEXx | LVLEXx |  |  |

| Access |             |    |    |      | R       | R       | R      | R      |  |  |

| Reset  |             |    |    |      | 0       | 0       | 0      | 0      |  |  |

#### Bits 31:16 – BTCNT[15:0]: Active Channel Block Transfer Count

These bits hold the 16-bit block transfer count of the ongoing transfer. This value is stored in the active channel and written back in the corresponding Write-Back channel memory location when the arbiter grants a new channel access. The value is valid only when the active channel active busy flag (ABUSY) is set.

#### Bit 15 – ABUSY: Active Channel Busy

This bit is cleared when the active transfer count is written back in the write-back memory section.

This bit is set when the next descriptor transfer count is read from the write-back memory section.

#### Bits 12:8 – ID[4:0]: Active Channel ID

These bits hold the channel index currently stored in the active channel registers. The value is updated each time the arbiter grants a new channel transfer access request.

#### Bits 3,2,1,0 – LVLEXx: Level x Channel Trigger Request Executing [x=3..0]

This bit is set when a level-x channel trigger request is executing or pending.

This bit is cleared when no request is pending or being executed.

#### 25.8.15 Descriptor Memory Section Base Address

Name:BASEADDROffset:0x34Reset:0x00000000Property:PAC Write-Protection, Enable-Protected

Name: BTCNT Offset: 0x02 Property: -

| Bit    | 15 | 14 | 13 | 12   | 11      | 10 | 9 | 8 |

|--------|----|----|----|------|---------|----|---|---|

|        |    |    |    | BTCN | T[15:8] |    |   |   |

| Access |    |    |    |      |         |    |   |   |

| Reset  |    |    |    |      |         |    |   |   |

|        |    |    |    |      |         |    |   |   |

| Bit    | 7  | 6  | 5  | 4    | 3       | 2  | 1 | 0 |

|        |    |    |    | BTCN | T[7:0]  |    |   |   |

| Access |    |    |    |      |         |    |   |   |

Reset

## Bits 15:0 – BTCNT[15:0]: Block Transfer Count

This bit group holds the 16-bit block transfer count.

During a transfer, the internal counter value is decremented by one after each beat transfer. The internal counter is written to the corresponding write-back memory section for the DMA channel when the DMA channel loses priority, is suspended or gets disabled. The DMA channel can be disabled by a complete transfer, a transfer error or by software.

## 25.10.3 Block Transfer Source Address

The SRCADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

Name: SRCADDR Offset: 0x04 Property: - Issue an Erase Row command.

Note: The NVM Address bit field in the Address register (ADDR.ADDR) uses 16-bit addressing.

## 27.6.4.6 Lock and Unlock Region

These commands are used to lock and unlock regions as detailed in section Region Lock Bits.

## 27.6.4.7 Set and Clear Power Reduction Mode

The NVM Controller and block can be taken in and out of power reduction mode through the Set and Clear Power Reduction Mode commands. When the NVM Controller and block are in power reduction mode, the Power Reduction Mode bit in the Status register (STATUS.PRM) is set.

## 27.6.5 NVM User Configuration

The NVM user configuration resides in the auxiliary space. Refer to the Physical Memory Map of the device for calibration and auxiliary space address mapping.

The bootloader resides in the main array starting at offset zero. The allocated boot loader section is writeprotected.

| BOOTPROT [2:0]     | Rows Protected by BOOTPROT | Boot Loader Size in Bytes |

|--------------------|----------------------------|---------------------------|

| 0x7 <sup>(1)</sup> | None                       | 0                         |

| 0x6                | 2                          | 512                       |

| 0x5                | 4                          | 1024                      |

| 0x4                | 8                          | 2048                      |

| 0x3                | 16                         | 4096                      |

| 0x2                | 32                         | 8192                      |

| 0x1                | 64                         | 16384                     |

| 0x0                | 128                        | 32768                     |

#### Table 27-2. Boot Loader Size

**Note:** 1) Default value is 0x7.

The EEPROM[2:0] bits indicate the EEPROM size, see the table below. The EEPROM resides in the upper rows of the NVM main address space and is writable, regardless of the region lock status.

Table 27-3. EEPROM Size

| EEPROM[2:0] | Rows Allocated to EEPROM | EEPROM Size in Bytes |

|-------------|--------------------------|----------------------|

| 7           | None                     | 0                    |

| 6           | 1                        | 256                  |

| 5           | 2                        | 512                  |

| 4           | 4                        | 1024                 |

| 3           | 8                        | 2048                 |

| 2           | 16                       | 4096                 |

| 1           | 32                       | 8192                 |

| 0           | 64                       | 16384                |

If *even parity* is selected (CTRLB.PMODE=0), the parity bit of an outgoing frame is '1' if the data contains an odd number of bits that are '1', making the total number of '1' even.

If *odd parity* is selected (CTRLB.PMODE=1), the parity bit of an outgoing frame is '1' if the data contains an even number of bits that are '0', making the total number of '1' odd.

When parity checking is enabled, the parity checker calculates the parity of the data bits in incoming frames and compares the result with the parity bit of the corresponding frame. If a parity error is detected, the Parity Error bit in the Status register (STATUS.PERR) is set.

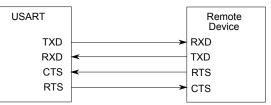

#### 31.6.3.2 Hardware Handshaking

The USART features an out-of-band hardware handshaking flow control mechanism, implemented by connecting the RTS and CTS pins with the remote device, as shown in the figure below.

#### Figure 31-7. Connection with a Remote Device for Hardware Handshaking

Hardware handshaking is only available in the following configuration:

- USART with internal clock (CTRLA.MODE=1),

- Asynchronous mode (CTRLA.CMODE=0),

- and Flow control pinout (CTRLA.TXPO=2).

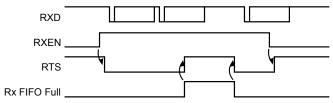

When the receiver is disabled or the receive FIFO is full, the receiver will drive the RTS pin high. This notifies the remote device to stop transfer after the ongoing transmission. Enabling and disabling the receiver by writing to CTRLB.RXEN will set/clear the RTS pin after a synchronization delay. When the receive FIFO goes full, RTS will be set immediately and the frame being received will be stored in the shift register until the receive FIFO is no longer full.

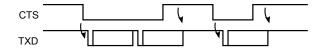

#### Figure 31-8. Receiver Behavior when Operating with Hardware Handshaking

The current CTS Status is in the STATUS register (STATUS.CTS). Character transmission will start only if STATUS.CTS=0. When CTS is set, the transmitter will complete the ongoing transmission and stop transmitting.

#### Figure 31-9. Transmitter Behavior when Operating with Hardware Handshaking

#### 31.6.3.3 IrDA Modulation and Demodulation

Transmission and reception can be encoded IrDA compliant up to 115.2 kb/s. IrDA modulation and demodulation work in the following configuration:

- IrDA encoding enabled (CTRLB.ENC=1),

- Asynchronous mode (CTRLA.CMODE=0),

| 000     | CCR Tx Buffer Element I |         | <sup>-</sup> Element | Frame Transmission            |

|---------|-------------------------|---------|----------------------|-------------------------------|

| BRSE    | FDOE                    | FDF     | BRS                  |                               |

| ignored | 0                       | ignored | ignored              | Classic CAN                   |

| 0       | 1                       | 0       | ignored              | Classic CAN                   |

| 0       | 1                       | 1       | ignored              | FD without bit rate switching |

| 1       | 1                       | 0       | ignored              | Classic CAN                   |

| 1       | 1                       | 1       | 0                    | FD without bit rate switching |

| 1       | 1                       | 1       | 1                    | FD with bit rate switching    |

| Table 34-6. | Possible | Configurations | for Frame | Transmission |

|-------------|----------|----------------|-----------|--------------|

|-------------|----------|----------------|-----------|--------------|

Note: AUTOSAR requires at least three Tx Queue Buffers and support of transmit cancellation

The Tx Handler starts a Tx scan to check for the highest priority pending Tx request (Tx Buffer with lowest Message ID) when the Tx Buffer Request Pending register TXBRP is updated, or when a transmission has been started.

## 34.6.6.1 Transmit Pause

The transmit pause feature is intended for use in CAN systems where the CAN message identifiers are (permanently) specified to specific values and cannot easily be changed. These message identifiers may have a higher CAN arbitration priority than other defined messages, while in a specific application their relative arbitration priority should be inverse. This may lead to a case where one ECU sends a burst of CAN messages that cause another ECU's CAN messages to be delayed because that other messages have a lower CAN arbitration priority.

If e.g. CAN ECU-1 has the transmit pause feature enabled and is requested by its application software to transmit four messages, it will, after the first successful message transmission, wait for two CAN bit times of bus idle before it is allowed to start the next requested message. If there are other ECUs with pending messages, those messages are started in the idle time, they would not need to arbitrate with the next message of ECU-1. After having received a message, ECU-1 is allowed to start its next transmission as soon as the received message releases the CAN bus.

The transmit pause feature is controlled by bit CCCR.TXP. If the bit is set, the CAN will, each time it has successfully transmitted a message, pause for two CAN bit times before starting the next transmission. This enables other CAN nodes in the network to transmit messages even if their messages have lower prior identifiers. Default is transmit pause disabled (CCCR.TXP = '0').

This feature looses up burst transmissions coming from a single node and it protects against "babbling idiot" scenarios where the application program erroneously requests too many transmissions.

#### 34.6.6.2 Dedicated Tx Buffers

Dedicated Tx Buffers are intended for message transmission under complete control of the CPU. Each Dedicated Tx Buffer is configured with a specific Message ID. In case that multiple Tx Buffers are configured with the same Message ID, the Tx Buffer with the lowest buffer number is transmitted first.

If the data section has been updated, a transmission is requested by an Add Request via TXBAR.ARn. The requested messages arbitrate internally with messages from an optional Tx FIFO or Tx Queue and externally with messages on the CAN bus, and are sent out according to their Message ID.

A Dedicated Tx Buffer allocates Element Size 32-bit words in the Message RAM (refer to table below). Therefore the start address of a dedicated Tx Buffer in the Message RAM is calculated by adding transmit buffer index (0...31) • Element Size to the Tx Buffer Start Address TXBC.TBSA.

#### Bit 26 – WDIL: Watchdog Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

## Bit 25 – BOL: Bus\_Off Status Interrupt Line

| Value | Description                                 |  |

|-------|---------------------------------------------|--|

| 0     | Interrupt assigned to CAN interrupt line 0. |  |

| 1     | Interrupt assigned to CAN interrupt line 1. |  |

#### Bit 24 – EWL: Error Warning Status Interrupt Line

| Value | Description                                 |  |

|-------|---------------------------------------------|--|

| 0     | Interrupt assigned to CAN interrupt line 0. |  |

| 1     | Interrupt assigned to CAN interrupt line 1. |  |

#### Bit 23 – EPL: Error Passive Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

## Bit 22 – ELOL: Error Logging Overflow Interrupt Line

| Valu | е | Description                                 |

|------|---|---------------------------------------------|

| 0    |   | Interrupt assigned to CAN interrupt line 0. |

| 1    |   | Interrupt assigned to CAN interrupt line 1. |

#### Bit 21 – BEUL: Bit Error Uncorrected Interrupt Line

| Value | Description                                 |  |

|-------|---------------------------------------------|--|

| 0     | Interrupt assigned to CAN interrupt line 0. |  |

| 1     | Interrupt assigned to CAN interrupt line 1. |  |

#### Bit 20 – BECL: Bit Error Corrected Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

#### Bit 19 – DRXL: Message stored to Dedicated Rx Buffer Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

#### Bit 18 – TOOL: Timeout Occurred Interrupt Line

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | Interrupt assigned to CAN interrupt line 0. |

| 1     | Interrupt assigned to CAN interrupt line 1. |

- R2 Bits 23:16 DB2[7:0]: Data Byte 2

- R2 Bits 15:8 DB1[7:0]: Data Byte 1

- R2 Bits 7:0 DB0[7:0]: Data Byte 0

- R3 Bits 31:24 DB7[7:0]: Data Byte 7

- R3 Bits 23:16 DB6[7:0]: Data Byte 6

- R3 Bits 15:8 DB5[7:0]: Data Byte 5

- R3 Bits 7:0 DB4[7:0]: Data Byte 4

...

- Rn Bits 31:24 DBm[7:0]: Data Byte m

- Rn Bits 23:16 DBm-1[7:0]: Data Byte m-1

- Rn Bits 15:8 DBm-2[7:0]: Data Byte m-2

- Rn Bits 7:0 DBm-3[7:0]: Data Byte m-3

**Warning:** Depending on the configuration of RXESC, between two and sixteen 32-bit words (Rn = 3 ... 17) are used for storage of a CAN message's data field.

## 34.9.3 Tx Buffer Element

The Tx Buffers section can be configured to hold dedicated Tx Buffers as well as a Tx FIFO / Tx Queue. In case that the Tx Buffers section is shared by dedicated Tx buffers and a Tx FIFO / Tx Queue, the dedicated Tx Buffers start at the beginning of the Tx Buffers section followed by the buffers assigned to the Tx FIFO or Tx Queue. The Tx Handler distinguishes between dedicated Tx Buffers and Tx FIFO / Tx Queue by evaluating the Tx Buffer configuration TXBC.TFQS and TXBC.NDTB. The element size can be configured for storage of CAN FD messages with up to 64 bytes data field via register TXESC.

|    | 31 | 3 | 29 | 28  | 27       | 26 | 25 | 24                        | 23 | 22       | 21    | 20   | 19     | 18 1  | 17 1 | 6 | 15 | 14 | 13 | 12   | 11    | 10 | 9 | 8 | 7        | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

|----|----|---|----|-----|----------|----|----|---------------------------|----|----------|-------|------|--------|-------|------|---|----|----|----|------|-------|----|---|---|----------|---|---|------|-------|---|---|---|

|    |    | 0 |    |     |          |    |    |                           |    |          |       |      |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

|    | Е  | х | R  |     |          |    |    |                           |    |          |       |      |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

| т0 | S  | Т | Т  |     |          |    |    |                           |    | ID[28:0] |       |      |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

|    | I  | D | R  |     |          |    |    |                           |    |          |       |      |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

|    |    |   |    |     |          |    |    |                           | Е  |          | F     | В    |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

| T1 |    |   |    | MM[ | 7:0]     |    |    |                           | F  |          | D     | R    | I      | DLC[3 | :0]  |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

|    |    |   |    |     |          |    |    |                           | С  |          | F     | S    |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

| T2 |    |   |    | DB3 | [7:0]    |    |    |                           |    |          |       | DB2  | [7:0]  |       |      |   |    |    |    | DB1  | [7:0] |    |   |   | DB0[7:0] |   |   |      |       |   |   |   |

| Т3 |    |   |    | DB7 | 7[7:0] D |    |    | DB6[7:0] DB5[7:0] DB4[7:0 |    |          | [7:0] | 0]   |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

|    |    |   |    |     |          |    |    |                           |    |          |       |      |        |       |      |   |    |    |    |      |       |    |   |   |          |   |   |      |       |   |   |   |

| Tn |    |   |    | DBm | [7:0]    |    |    |                           |    |          | 0     | DBm- | 1[7:0] |       |      |   |    |    | C  | )Bm- | 2[7:0 | ]  |   |   |          |   | [ | DBm- | 3[7:0 | ] |   |   |

## Table 34-9. Tx Buffer Element

T0 Bit 31 - ESI: Error State Indicator

0 : ESI bit in CAN FD format depends only on error passive flag.

1 : ESI bit in CAN FD format transmitted recessive.

**Note:** The ESI bit of the transmit buffer is OR'ed with the error passive flag to decide the value of the ESI bit in the transmitted FD frame. As required by the CAN FD protocol specification, an error

#### I/O Multiplexing and Considerations

## 35.5 **Product Dependencies**

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 35.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

#### **Related Links**

PORT: IO Pin Controller

#### 35.5.2 Power Management

This peripheral can continue to operate in any sleep mode where its source clock is running. The interrupts can wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

### **Related Links**

PM – Power Manager

## 35.5.3 Clocks

The TC bus clocks (CLK\_TCx\_APB) can be enabled and disabled in the Main Clock Module. The default state of CLK\_TCx\_APB can be found in the *Peripheral Clock Masking*.

The generic clocks (GCLK\_TCx) are asynchronous to the user interface clock (CLK\_TCx\_APB). Due to this asynchronicity, accessing certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

**Note:** Two instances of the TC may share a peripheral clock channel. In this case, they cannot be set to different clock frequencies. Refer to the peripheral clock channel mapping of the Generic Clock Controller (GCLK.PCHTRLm) to identify shared peripheral clocks.

## **Related Links**

PCHCTRL0, PCHCTRL1, PCHCTRL2, PCHCTRL3, PCHCTRL4, PCHCTRL5, PCHCTRL6, PCHCTRL7, PCHCTRL8, PCHCTRL9, PCHCTRL10, PCHCTRL11, PCHCTRL12, PCHCTRL13, PCHCTRL14, PCHCTRL15, PCHCTRL16, PCHCTRL17, PCHCTRL18, PCHCTRL19, PCHCTRL20, PCHCTRL21, PCHCTRL22, PCHCTRL23, PCHCTRL24, PCHCTRL25, PCHCTRL26, PCHCTRL27, PCHCTRL28, PCHCTRL29, PCHCTRL30, PCHCTRL31, PCHCTRL32, PCHCTRL33, PCHCTRL34, PCHCTRL35, PCHCTRL36, PCHCTRL37, PCHCTRL38, PCHCTRL39, PCHCTRL40, PCHCTRL41, PCHCTRL42, PCHCTRL43, PCHCTRL44, PCHCTRL45

Peripheral Clock Masking

## 35.5.4 DMA

The DMA request lines are connected to the DMA Controller (DMAC). In order to use DMA requests with this peripheral the DMAC must be configured first. Refer to *DMAC – Direct Memory Access Controller* for details.

## **Related Links**

DMAC - Direct Memory Access Controller

| Bit    | 31     | 30      | 29        | 28     | 27     | 26     | 25        | 24     |

|--------|--------|---------|-----------|--------|--------|--------|-----------|--------|

|        |        | FILTERV | /AL1[3:0] |        |        | FILTER | /AL0[3:0] |        |

| Access | R/W    | R/W     | R/W       | R/W    | R/W    | R/W    | R/W       | R/W    |

| Reset  | 0      | 0       | 0         | 0      | 0      | 0      | 0         | 0      |

|        |        |         |           |        |        |        |           |        |

| Bit    | 23     | 22      | 21        | 20     | 19     | 18     | 17        | 16     |

|        | INVENx | INVENx  | INVENx    | INVENx | INVENx | INVENx | INVENx    | INVENx |

| Access | R/W    | R/W     | R/W       | R/W    | R/W    | R/W    | R/W       | R/W    |

| Reset  | 0      | 0       | 0         | 0      | 0      | 0      | 0         | 0      |

|        |        |         |           |        |        |        |           |        |

| Bit    | 15     | 14      | 13        | 12     | 11     | 10     | 9         | 8      |

|        | NRVx   | NRVx    | NRVx      | NRVx   | NRVx   | NRVx   | NRVx      | NRVx   |

| Access | R/W    | R/W     | R/W       | R/W    | R/W    | R/W    | R/W       | R/W    |

| Reset  | 0      | 0       | 0         | 0      | 0      | 0      | 0         | 0      |

|        |        |         |           |        |        |        |           |        |

| Bit    | 7      | 6       | 5         | 4      | 3      | 2      | 1         | 0      |

|        | NREx   | NREx    | NREx      | NREx   | NREx   | NREx   | NREx      | NREx   |

| Access | R/W    | R/W     | R/W       | R/W    | R/W    | R/W    | R/W       | R/W    |

| Reset  | 0      | 0       | 0         | 0      | 0      | 0      | 0         | 0      |

#### Bits 31:28 – FILTERVAL1[3:0]: Non-Recoverable Fault Input 1 Filter Value

These bits define the filter value applied on TCE1 event input line. When the TCE1 event input line is configured as a synchronous event, this value must be 0x0.

#### Bits 27:24 – FILTERVAL0[3:0]: Non-Recoverable Fault Input 0 Filter Value

These bits define the filter value applied on TCE0 event input line. When the TCE0 event input line is configured as a synchronous event, this value must be 0x0.

#### Bits 23,22,21,20,19,18,17,16 – INVENx: Waveform Output x Inversion

These bits are used to select inversion on the output of channel x.

Writing a '1' to INVENx inverts output from WO[x].

Writing a '0' to INVENx disables inversion of output from WO[x].

#### Bits 15,14,13,12,11,10,9,8 – NRVx: NRVx Non-Recoverable State x Output Value

These bits define the value of the enabled override outputs, under non-recoverable fault condition.

#### Bits 7,6,5,4,3,2,1,0 – NREx: Non-Recoverable State x Output Enable

These bits enable the override of individual outputs by NRVx value, under non-recoverable fault condition.

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | Non-recoverable fault tri-state the output.          |

| 1     | Non-recoverable faults set the output to NRVx level. |

#### 36.8.8 Debug control

Register Synchronization

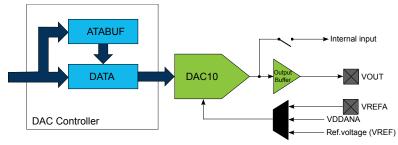

## 41. DAC – Digital-to-Analog Converter

## 41.1 Overview

The Digital-to-Analog Converter (DAC) converts a digital value to a voltage. The DAC has one channel with 10-bit resolution, and it is capable of converting up to 350,000 samples per second (350ksps).

## 41.2 Features

- DAC with 10-bit resolution

- Up to 350ksps conversion rate

- Hardware support for 14-bit using dithering

- Multiple trigger sources

- High-drive capabilities

- Output can be used as input to the Analog Comparator (AC), ADC or SDADC

- DMA support

## 41.3 Block Diagram

## Figure 41-1. DAC Block Diagram

## 41.4 Signal Description

| Signal Name | Туре          | Description        |  |  |  |

|-------------|---------------|--------------------|--|--|--|

| VOUT        | Analog output | DAC output         |  |  |  |

| VREFA       | Analog input  | External reference |  |  |  |

## **Related Links**

I/O Multiplexing and Considerations

## 41.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

## 41.5.1 I/O Lines

Using the DAC Controller's I/O lines requires the I/O pins to be configured using the port configuration (PORT).

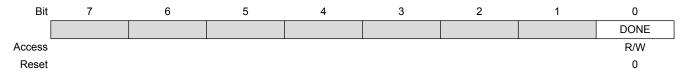

Name:INTENSETOffset:0x09 [ID-00000e03]Reset:0x00Property:PAC Write-Protection

## Bit 0 – DONE: Measurement Done Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Measurement Done Interrupt Enable bit, which enables the Measurement Done interrupt.

| Value | Description                                 |

|-------|---------------------------------------------|

| 0     | The Measurement Done interrupt is disabled. |

| 1     | The Measurement Done interrupt is enabled.  |

## 44.8.6 Interrupt Flag Status and Clear

| Name:            | INTFLAG            |

|------------------|--------------------|

| Offset:          | 0x0A [ID-00000e03] |

| Reset:           | 0x00               |

| <b>Property:</b> | -                  |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|---|---|---|---|---|---|---|------|

|        |   |   |   |   |   |   |   | DONE |

| Access |   |   |   |   |   |   |   | R/W  |

| Reset  |   |   |   |   |   |   |   | 0    |

## Bit 0 – DONE: Mesurement Done

This flag is cleared by writing a '1' to it.

This flag is set when the STATUS.BUSY bit has a one-to-zero transition.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the DONE interrupt flag.

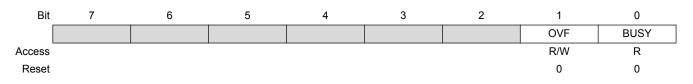

#### 44.8.7 Status

Name:

STATUS

Offset:

0x0B [ID-00000e03]

Reset:

0x00

Property:

–

#### Bit 1 – OVF: Sticky Count Value Overflow

This bit is cleared by writing a '1' to it.

This bit is set when an overflow condition occurs to the value counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the OVF status.

#### Bit 0 – BUSY: FREQM Status

| Value | Description                       |

|-------|-----------------------------------|

| 0     | No ongoing frequency measurement. |

| 1     | Frequency measurement is ongoing. |

### 44.8.8 Synchronization Busy

| Name:            | SYNCBUSY           |

|------------------|--------------------|

| Offset:          | 0x0C [ID-00000e03] |

| Reset:           | 0x0000000          |

| <b>Property:</b> | -                  |

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25     | 24    |

|--------|----|----|----|----|----|----|--------|-------|

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 23 | 22 | 21 | 20 | 19 | 18 | 17     | 16    |

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8     |

|        |    |    |    |    |    |    |        |       |

| Access |    |    |    |    |    |    |        |       |

| Reset  |    |    |    |    |    |    |        |       |

|        |    |    |    |    |    |    |        |       |

| Bit    | 7  | 6  | 5  | 4  | 3  | 2  | 1      | 0     |

|        |    |    |    |    |    |    | ENABLE | SWRST |

| Access |    |    |    |    |    |    | R      | R     |

| Reset  |    |    |    |    |    |    | 0      | 0     |

## Bit 1 – ENABLE: Enable

This bit is cleared when the synchronization of CTRLA.ENABLE is complete.

This bit is set when the synchronization of CTRLA.ENABLE is started.

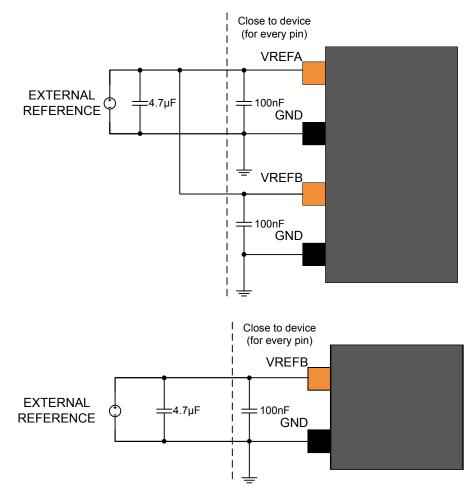

Figure 49-4. External Analog Reference Schematic With One Reference

| Signal Name | Recommended Pin Connection                                                     | Description                                           |  |  |  |

|-------------|--------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| VREFA       | 2.0V to $V_{DDANA}$ - 0.6V for ADC                                             | External reference from VREFA pin on the analog port. |  |  |  |

|             | 1.0V to V <sub>DDANA</sub> - 0.6V for DAC                                      |                                                       |  |  |  |

|             | Decoupling/filtering capacitors: 100nF <sup>(1)(2)</sup> and 4.7 $\mu F^{(1)}$ |                                                       |  |  |  |

| VREFB       | 1.0V to 5.5V for SDADC                                                         | External reference from VREFB                         |  |  |  |

|             | Decoupling/filtering capacitors: $100nF^{(1)(2)}$ and $4.7\mu F^{(1)}$         | pin on the analog port.                               |  |  |  |

| GND         |                                                                                | Ground                                                |  |  |  |

## Note:

- 1. These values are given as a typical example.

- 2. Decoupling capacitor should be placed close to the device for each supply pin pair in the signal group.