#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                           |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, WDT                                      |

| Number of I/O              | 84                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 20x12b, 3x16b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-TQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamc21n18a-ant |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 50.6. Rev H - 05/2016                          |

|------------------------------------------------|

| 50.7. Rev G - 04/2015                          |

| 50.8. Rev F - 02/2015                          |

| 50.9. Rev E - 12/2015                          |

| 50.10. Rev D - 09/2015                         |

| 50.11. Rev C - 09/2015                         |

| 50.12. Rev B - 06/2015                         |

| 50.13. Rev A - 04/2015 1102                    |

| The Microchip Web Site1103                     |

| Customer Change Notification Service1103       |

| Customer Support1103                           |

| Product Identification System                  |

| Microchip Devices Code Protection Feature 1104 |

| Legal Notice1104                               |

| Trademarks1105                                 |

| Quality Management System Certified by DNV1105 |

| Worldwide Sales and Service                    |

# PM – Power Manager

# 11.4.3 Clocks

The PAC bus clock (CLK\_PAC\_APB) can be enabled and disabled in the Main Clock module. The default state of CLK\_PAC\_APB can be found in the related links.

# Related Links

MCLK – Main Clock Peripheral Clock Masking

# 11.4.4 DMA

Not applicable.

# 11.4.5 Interrupts

The interrupt request line is connected to the Interrupt Controller. Using the PAC interrupt requires the Interrupt Controller to be configured first.

# Table 11-1. Interrupt Lines

| Instances | NVIC Line |

|-----------|-----------|

| PAC       | PACERR    |

# **Related Links**

Nested Vector Interrupt Controller

# 11.4.6 Events

The events are connected to the Event System, which may need configuration.

# Related Links

EVSYS – Event System

# 11.4.7 Debug Operation

When the CPU is halted in debug mode, write protection of all peripherals is disabled and the PAC continues normal operation.

# 11.4.8 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

- Write Control (WRCTRL) register

- AHB Slave Bus Interrupt Flag Status and Clear (INTFLAGAHB) register

- Peripheral Interrupt Flag Status and Clear n (INTFLAG A/B/C...) registers

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

# 11.5 Functional Description

# 11.5.1 Principle of Operation

The Peripheral Access Control module allows the user to set a write protection on peripheral modules and generate an interrupt in case of a peripheral access violation. The peripheral's protection can be set,

- 2.3. Erases the lock row, removing the NVMCTRL security bit protection.

- 3. Check for completion by polling STATUSA.DONE (read as '1' when completed).

- 4. Reset the device to let the NVMCTRL update the fuses.

# 13.8 Programming

Programming the Flash or RAM memories is only possible when the device is not protected by the NVMCTRL security bit. The programming procedure is as follows:

- At power up, RESET is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold (refer to Powe-On Reset (POR) characteristics). The system continues to be held in this static state until the internally regulated supplies have reached a safe operating state.

- 2. The PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- 3. The debugger maintains a low level on SWCLK. RESET is released, resulting in a debugger Cold-Plugging procedure.

- 4. The debugger generates a clock signal on the SWCLK pin, the Debug Access Port (DAP) receives a clock.

- 5. The CPU remains in Reset due to the Cold-Plugging procedure; meanwhile, the rest of the system is released.

- 6. A Chip-Erase is issued to ensure that the Flash is fully erased prior to programming.

- 7. The debugger then configures the NVIC to catch the Cortex-M4 core reset vector fetch. For more information on how to program the NVIC, refer to the ARMv7-M Architecture Reference Manual.

- 8. Release the "CPU reset extension" phase by writing a '1' to the Status A register CPU Reset Phase Extension bit (STATUSA.CRSTEXT).

- 9. Programming is available through the AHB-AP.

- 10. After the operation is completed, the chip can be restarted either by asserting RESET or toggling power. Make sure that the SWCLK pin is high when releasing RESET to prevent extending the CPU reset.

# **Related Links**

Electrical Characteristics 85°C (SAM C20/C21 E/G/J) NVMCTRL – Non-Volatile Memory Controller Security Bit

# 13.9 Intellectual Property Protection

Intellectual property protection consists of restricting access to internal memories from external tools when the device is protected, and this is accomplished by setting the NVMCTRL security bit. This protected state can be removed by issuing a Chip-Erase (refer to Chip Erase). When the device is protected, read/write accesses using the AHB-AP are limited to the DSU address range and DSU commands are restricted. When issuing a Chip-Erase, sensitive information is erased from volatile memory and Flash.

The DSU implements a security filter that monitors the AHB transactions inside the DAP. If the device is protected, then AHB-AP read/write accesses outside the DSU external address range are discarded, causing an error response that sets the ARM AHB-AP sticky error bits (refer to the ARM Debug Interface v5 Architecture Specification on http://www.arm.com).

# 13.12 Register Summary

| Offset | Name     | Bit Pos. |             |                     |           |             |               |         |         |       |  |  |

|--------|----------|----------|-------------|---------------------|-----------|-------------|---------------|---------|---------|-------|--|--|

| 0x00   | CTRL     | 7:0      |             |                     |           | CE          | MBIST         |         | CRC     | SWRST |  |  |

| 0x01   | STATUSA  | 7:0      |             |                     |           | PERR        | FAIL          | BERR    | CRSTEXT | DONE  |  |  |

| 0x02   | STATUSB  | 7:0      |             |                     |           | HPE         | DCCDx         | DCCDx   | DBGPRES | PROT  |  |  |

| 0x03   | Reserved |          |             |                     |           |             |               |         |         |       |  |  |

| 0x04   |          | 7:0      |             | ADDR[5:0] AMOD[1:0] |           |             |               |         |         |       |  |  |

| 0x05   | ADDR     | 15:8     | ADDR[13:6]  |                     |           |             |               |         |         |       |  |  |

| 0x06   | ADDR     | 23:16    |             | ADDR[21:14]         |           |             |               |         |         |       |  |  |

| 0x07   |          | 31:24    |             | ADDR[29:22]         |           |             |               |         |         |       |  |  |

| 0x08   |          | 7:0      |             |                     | LENG      | TH[5:0]     |               |         |         |       |  |  |

| 0x09   | LENGTH   | 15:8     |             |                     |           | LENG        | FH[13:6]      |         |         |       |  |  |

| 0x0A   | LENGTH   | 23:16    |             |                     |           | LENGT       | H[21:14]      |         |         |       |  |  |

| 0x0B   |          | 31:24    |             |                     |           | LENGT       | H[29:22]      |         |         |       |  |  |

| 0x0C   |          | 7:0      |             |                     |           | DAT         | A[7:0]        |         |         |       |  |  |

| 0x0D   | DATA     | 15:8     |             |                     |           | DATA        | A[15:8]       |         |         |       |  |  |

| 0x0E   | DAIA     | 23:16    |             |                     |           | DATA        | [23:16]       |         |         |       |  |  |

| 0x0F   |          | 31:24    |             |                     |           | DATA        | [31:24]       |         |         |       |  |  |

| 0x10   |          | 7:0      |             |                     |           | DAT         | A[7:0]        |         |         |       |  |  |

| 0x11   | DCC0     | 15:8     |             |                     |           | DATA        | A[15:8]       |         |         |       |  |  |

| 0x12   |          | 23:16    |             | DATA[23:16]         |           |             |               |         |         |       |  |  |

| 0x13   |          | 31:24    |             |                     |           | DATA        | [31:24]       |         |         |       |  |  |

| 0x14   |          | 7:0      |             | DATA[7:0]           |           |             |               |         |         |       |  |  |

| 0x15   | DCC1     | 15:8     |             | DATA[15:8]          |           |             |               |         |         |       |  |  |

| 0x16   | 2001     | 23:16    |             | DATA[23:16]         |           |             |               |         |         |       |  |  |

| 0x17   |          | 31:24    |             |                     |           | DATA        | [31:24]       |         |         |       |  |  |

| 0x18   |          | 7:0      |             |                     |           | DEVS        | EL[7:0]       |         |         |       |  |  |

| 0x19   | DID      | 15:8     |             | DIE                 | E[3:0]    |             | REVISION[3:0] |         |         |       |  |  |

| 0x1A   |          | 23:16    | FAMILY[0:0] |                     |           |             | SERIE         | ES[5:0] |         |       |  |  |

| 0x1B   |          | 31:24    |             | PROCES              | SSOR[3:0] | FAMILY[4:1] |               |         |         |       |  |  |

| 0x1C   |          |          |             |                     |           |             |               |         |         |       |  |  |

|        | Reserved |          |             |                     |           |             |               |         |         |       |  |  |

| 0x0FFF |          |          |             |                     |           |             |               |         |         | 55550 |  |  |

| 0x1000 |          | 7:0      |             | 4000                |           |             |               |         | FMT     | EPRES |  |  |

| 0x1001 | ENTRY0   | 15:8     |             | ADDC                | 0FF[3:0]  |             |               |         |         |       |  |  |

| 0x1002 |          | 23:16    |             |                     |           |             | FF[11:4]      |         |         |       |  |  |

| 0x1003 |          | 31:24    |             |                     |           | ADDOF       | F[19:12]      |         | <b></b> |       |  |  |

| 0x1004 |          | 7:0      |             |                     |           |             |               |         | FMT     | EPRES |  |  |

| 0x1005 | ENTRY1   | 15:8     |             | ADDC                | 0FF[3:0]  | 4000        |               |         |         |       |  |  |

| 0x1006 |          | 23:16    |             |                     |           |             | FF[11:4]      |         |         |       |  |  |

| 0x1007 |          | 31:24    |             |                     |           |             | F[19:12]      |         |         |       |  |  |

| 0x1008 |          | 7:0      |             |                     |           |             | D[7:0]        |         |         |       |  |  |

| 0x1009 | END      | 15:8     |             |                     |           |             | [15:8]        |         |         |       |  |  |

| 0x100A |          | 23:16    |             |                     |           |             | 23:16]        |         |         |       |  |  |

| 0x100B |          | 31:24    |             |                     |           | END[        | 31:24]        |         |         |       |  |  |

| 0x100C | Reserved |          |             |                     |           |             |               |         |         |       |  |  |

# SAM C20/C21

| Bit    | 31 | 30 | 29 | 28        | 27                                    | 26      | 25       | 24       |

|--------|----|----|----|-----------|---------------------------------------|---------|----------|----------|

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 23 | 22 | 21 | 20        | 19                                    | 18      | 17       | 16       |

|        |    |    |    |           |                                       |         |          |          |

| Access |    |    |    |           |                                       |         |          |          |

| Reset  |    |    |    |           |                                       |         |          |          |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 15 | 14 | 13 | 12        | 11                                    | 10      | 9        | 8        |

|        |    |    |    |           | DPLLLDRTO                             | DPLLLTO | DPLLLCKF | DPLLLCKR |

| Access |    |    |    |           | R/W                                   | R/W     | R/W      | R/W      |

| Reset  |    |    |    |           | 0                                     | 0       | 0        | 0        |

|        |    |    |    |           |                                       |         |          |          |

| Bit    | 7  | 6  | 5  | 4         | 3                                     | 2       | 1        | 0        |

|        |    |    |    | OSC48MRDY |                                       |         | CLKFAIL  | XOSCRDY  |

| Access |    | •  | •  | R/W       | · · · · · · · · · · · · · · · · · · · |         | R/W      | R/W      |

| Reset  |    |    |    | 0         |                                       |         | 0        | 0        |

# Bit 11 – DPLLLDRTO: DPLL Loop Divider Ratio Update Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Loop Divider Ratio Update Complete Interrupt Enable bit, which disables the DPLL Loop Divider Ratio Update Complete interrupt.

| Value | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Loop Divider Ratio Update Complete interrupt is disabled.                                                                                                                   |

| 1     | The DPLL Loop Divider Ratio Update Complete interrupt is enabled, and an interrupt request will be generated when the DPLL Loop Divider Ratio Update Complete Interrupt flag is set. |

# Bit 10 – DPLLLTO: DPLL Lock Timeout Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Timeout Interrupt Enable bit, which disables the DPLL Lock Timeout interrupt.

| Value | Description                                                                                                                              |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Timeout interrupt is disabled.                                                                                             |

| 1     | The DPLL Lock Timeout interrupt is enabled, and an interrupt request will be generated when the DPLL Lock Timeout Interrupt flag is set. |

# Bit 9 – DPLLLCKF: DPLL Lock Fall Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the DPLL Lock Fall Interrupt Enable bit, which disables the DPLL Lock Fall interrupt.

| Value | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| 0     | The DPLL Lock Fall interrupt is disabled.                                                    |

| 1     | The DPLL Lock Fall interrupt is enabled, and an interrupt request will be generated when the |

|       | DPLL Lock Fall Interrupt flag is set.                                                        |

# 21. OSC32KCTRL – 32KHz Oscillators Controller

# 21.1 Overview

The 32KHz Oscillators Controller (OSC32KCTRL) provides a user interface to the 32.768kHz oscillators: XOSC32K, OSC32K, and OSCULP32K.

The OSC32KCTRL sub-peripherals can be enabled, disabled, calibrated, and monitored through interface registers.

All sub-peripheral statuses are collected in the Status register (STATUS). They can additionally trigger interrupts upon status changes via the INTENSET, INTENCLR, and INTFLAG registers.

# 21.2 Features

- 32.768kHz Crystal Oscillator (XOSC32K)

- Programmable start-up time

- Crystal or external input clock on XIN32 I/O

- Clock failure detection with safe clock switch

- Clock failure event output

- 32.768kHz High Accuracy Internal Oscillator (OSC32K)

- Frequency fine tuning

- Programmable start-up time

- 32.768kHz Ultra Low Power Internal Oscillator (OSCULP32K)

- Ultra low power, always-on oscillator

- Frequency fine tuning

- Calibration value loaded from Flash factory calibration at reset

- 1.024kHz clock outputs available

# 21.5.3 Clocks

The OSC32KCTRL gathers controls for all 32KHz oscillators and provides clock sources to the Generic Clock Controller (GCLK), Real-Time Counter (RTC), and Watchdog Timer (WDT).

The available clock sources are: XOSC32K, OSC32K, and OSCULP32K.

The OSC32KCTRL bus clock (CLK\_OSC32KCTRL\_APB) can be enabled and disabled in the Main Clock module (MCLK).

### **Related Links**

Peripheral Clock Masking

# 21.5.4 Interrupts

The interrupt request lines are connected to the interrupt controller. Using the OSC32KCTRL interrupts requires the interrupt controller to be configured first.

#### **Related Links**

Nested Vector Interrupt Controller

# 21.5.5 Events

The events of this peripheral are connected to the Event System.

# **Related Links**

EVSYS - Event System

# 21.5.6 Debug Operation

When the CPU is halted in debug mode, OSC32KCTRL will continue normal operation. If OSC32KCTRL is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 21.5.7 Register Access Protection

All registers with write-access can be write-protected optionally by the Peripheral Access Controller (PAC), except for the following registers:

Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

### **Related Links**

PAC - Peripheral Access Controller

# 21.5.8 Analog Connections

The external 32.768kHz crystal must be connected between the XIN32 and XOUT32 pins, along with any required load capacitors. For details on recommended oscillator characteristics and capacitor load, refer to the related links.

#### **Related Links**

Electrical Characteristics 85°C (SAM C20/C21 E/G/J)

# 21.5.9 Calibration

The OSC32K calibration value from the production test must be loaded from the NVM Software Calibration Area into the OSC32K register (OSC32K.CALIB) by software to achieve specified accuracy.

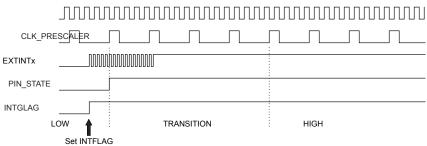

# Figure 26-3. EXTINT Pin Synchronous Debouncing (Rising Edge)

In the synchronous edge detection mode, the EIC clock is required. The synchronous edge detection mode can be used in Idle and Standby sleep modes.

**Asynchronous edge detection** In this mode, the external interrupt (EXTINT) pin directly drives an asynchronous edges detector which triggers any rising or falling edge on the pin:

- 1. Any edge detected that indicates a transition from the current valid pin state will immediately set the valid pin state PINSTATE.PINSTATE[x] to the detected level.

- 2. The external interrupt flag (INTFLAG.EXTINT[x] is immediately changed.

- 3. The edge detector will then be idle until no other rising or falling edge transition is detected during 4 consecutive ticks of the low frequency clock.

- 4. Any rising or falling edge transition detected during the idle state will return the transition counter to 0.

- 5. After 4 consecutive ticks of the low frequency clock without bounce detected, the edge detector is ready for a new detection.

# Figure 26-4. EXTINT Pin Asynchronous Debouncing (Rising Edge)

In this mode, the EIC clock is requested. The asynchronous edge detection mode can be used in Idle and Standby sleep modes.

# 26.6.5 DMA Operation

Not applicable.

# 26.6.6 Interrupts

The EIC has the following interrupt sources:

- External interrupt pins (EXTINTx). See Basic Operation.

- Non-maskable interrupt pin (NMI). See Additional Features.

Each interrupt source has an associated interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when an interrupt condition occurs (NMIFLAG for NMI). Each interrupt, except NMI, can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

© 2017 Microchip Technology Inc.

# PAC - Peripheral Access Controller

# 28.5.9 Analog Connections

Analog functions are connected directly between the analog blocks and the I/O pads using analog buses. However, selecting an analog peripheral function for a given pin will disable the corresponding digital features of the pad.

# 28.6 Functional Description

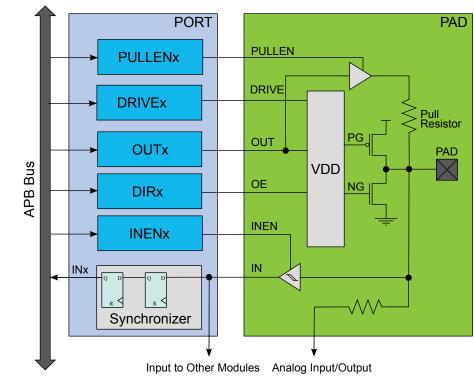

# Figure 28-2. Overview of the PORT

# 28.6.1 Principle of Operation

Each PORT group of up to 32 pins is controlled by the registers in PORT, as described in the figure. These registers in PORT are duplicated for each PORT group, with increasing base addresses. The number of PORT groups may depend on the package/number of pins.

| Bit    | 31        | 30 | 29 | 28   | 27    | 26 | 25 | 24 |  |

|--------|-----------|----|----|------|-------|----|----|----|--|

|        | IN[31:24] |    |    |      |       |    |    |    |  |

| Access | R         | R  | R  | R    | R     | R  | R  | R  |  |

| Reset  | 0         | 0  | 0  | 0    | 0     | 0  | 0  | 0  |  |

|        |           |    |    |      |       |    |    |    |  |

| Bit    | 23        | 22 | 21 | 20   | 19    | 18 | 17 | 16 |  |

|        |           |    |    | IN[2 | 3:16] |    |    |    |  |

| Access | R         | R  | R  | R    | R     | R  | R  | R  |  |

| Reset  | 0         | 0  | 0  | 0    | 0     | 0  | 0  | 0  |  |

|        |           |    |    |      |       |    |    |    |  |

| Bit    | 15        | 14 | 13 | 12   | 11    | 10 | 9  | 8  |  |

|        |           |    |    | IN[1 | 5:8]  |    |    |    |  |

| Access | R         | R  | R  | R    | R     | R  | R  | R  |  |

| Reset  | 0         | 0  | 0  | 0    | 0     | 0  | 0  | 0  |  |

|        |           |    |    |      |       |    |    |    |  |

| Bit    | 7         | 6  | 5  | 4    | 3     | 2  | 1  | 0  |  |

|        |           |    |    | IN[  | 7:0]  |    |    |    |  |

| Access | R         | R  | R  | R    | R     | R  | R  | R  |  |

| Reset  | 0         | 0  | 0  | 0    | 0     | 0  | 0  | 0  |  |

# Bits 31:0 - IN[31:0]: PORT Data Input Value

These bits are cleared when the corresponding I/O pin input sampler detects a logical low level on the input pin.

These bits are set when the corresponding I/O pin input sampler detects a logical high level on the input pin.

# 28.9.10 Control

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

Name:CTRLOffset:0x24Reset:0x00000000Property:PAC Write-Protection

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

# 31.8.1 Control A

Name: CTRLA Offset: 0x00 Reset: 0x0000000 Property: PAC Write-Protection, Enable-Protected

| Bit    | 31       | 30         | 29   | 28     | 27        | 26   | 25     | 24     |  |

|--------|----------|------------|------|--------|-----------|------|--------|--------|--|

|        |          | DORD       | CPOL | CMODE  |           | FORM | Л[3:0] |        |  |

| Access |          | R/W        | R/W  | R/W    | R/W       | R/W  | R/W    | R/W    |  |

| Reset  |          | 0          | 0    | 0      | 0         | 0    | 0      | 0      |  |

|        |          |            |      |        |           |      |        |        |  |

| Bit    | 23       | 22         | 21   | 20     | 19        | 18   | 17     | 16     |  |

|        | SAMF     | PA[1:0]    | RXP  | D[1:0] |           |      | TXPC   | D[1:0] |  |

| Access | R/W      | R/W        | R/W  | R/W    |           |      | R/W    | R/W    |  |

| Reset  | 0        | 0          | 0    | 0      |           |      | 0      | 0      |  |

|        |          |            |      |        |           |      |        |        |  |

| Bit    | 15       | 14         | 13   | 12     | 11        | 10   | 9      | 8      |  |

|        |          | SAMPR[2:0] |      |        |           |      |        | IBON   |  |

| Access | R/W      | R/W        | R/W  |        |           |      |        | R      |  |

| Reset  | 0        | 0          | 0    |        |           |      |        | 0      |  |

|        |          |            |      |        |           |      |        |        |  |

| Bit    | 7        | 6          | 5    | 4      | 3         | 2    | 1      | 0      |  |

|        | RUNSTDBY |            |      |        | MODE[2:0] |      | ENABLE | SWRST  |  |

| Access | R/W      |            |      | R/W    | R/W       | R/W  | R/W    | R/W    |  |

| Reset  | 0        |            |      | 0      | 0         | 0    | 0      | 0      |  |

#### Bit 30 – DORD: Data Order

This bit selects the data order when a character is shifted out from the Data register.

This bit is not synchronized.

| Value | Description               |

|-------|---------------------------|

| 0     | MSB is transmitted first. |

| 1     | LSB is transmitted first. |

#### Bit 29 – CPOL: Clock Polarity

This bit selects the relationship between data output change and data input sampling in synchronous mode.

This bit is not synchronized.

# Bit 4 – CTSIC: Clear to Send Input Change

This flag is cleared by writing a '1' to it.

This flag is set when a change is detected on the CTS pin.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

# Bit 3 – RXS: Receive Start

This flag is cleared by writing '1' to it.

This flag is set when a start condition is detected on the RxD line and start-of-frame detection is enabled (CTRLB.SFDE is '1').

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Start interrupt flag.

# Bit 2 – RXC: Receive Complete

This flag is cleared by reading the Data register (DATA) or by disabling the receiver.

This flag is set when there are unread data in DATA.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

# Bit 1 – TXC: Transmit Complete

This flag is cleared by writing '1' to it or by writing new data to DATA.

This flag is set when the entire frame in the transmit shift register has been shifted out and there are no new data in DATA.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

# Bit 0 – DRE: Data Register Empty

This flag is cleared by writing new data to DATA.

This flag is set when DATA is empty and ready to be written.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

#### 31.8.9 Status

Name: STATUS Offset: 0x1A Reset: 0x0000 Property: -

# 32.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16-, and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers require synchronization when read and/or written. Synchronization is denoted by the "Read-Synchronized" and/or "Write-Synchronized" property in each individual register description.

Refer to Synchronization

Some registers are enable-protected, meaning they can only be written when the module is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

Refer to Register Access Protection.

# 32.8.1 Control A

Name:CTRLAOffset:0x00 [ID-00000e74]Reset:0x00000000Property:PAC Write-Protection, Enable-Protected, Write-Synchronized

| Bit    | 31       | 30   | 29   | 28     | 27        | 26  | 25     | 24     |

|--------|----------|------|------|--------|-----------|-----|--------|--------|

|        |          | DORD | CPOL | CPHA   | FORM      |     | V[3:0] |        |

| Access |          | R/W  | R/W  | R/W    | R/W       | R/W | R/W    | R/W    |

| Reset  |          | 0    | 0    | 0      | 0         | 0   | 0      | 0      |

|        |          |      |      |        |           |     |        |        |

| Bit    | 23       | 22   | 21   | 20     | 19        | 18  | 17     | 16     |

|        |          |      | DIPC | D[1:0] |           |     | DOPO   | D[1:0] |

| Access |          |      | R/W  | R/W    |           |     | R/W    | R/W    |

| Reset  |          |      | 0    | 0      |           |     | 0      | 0      |

|        |          |      |      |        |           |     |        |        |

| Bit    | 15       | 14   | 13   | 12     | 11        | 10  | 9      | 8      |

|        |          |      |      |        |           |     |        | IBON   |

| Access |          |      |      |        |           |     |        | R/W    |

| Reset  |          |      |      |        |           |     |        | 0      |

|        |          |      |      |        |           |     |        |        |

| Bit    | 7        | 6    | 5    | 4      | 3         | 2   | 1      | 0      |

|        | RUNSTDBY |      |      |        | MODE[2:0] |     | ENABLE | SWRST  |

| Access | R/W      |      |      | R/W    | R/W       | R/W | R/W    | R/W    |

| Reset  | 0        |      |      | 0      | 0         | 0   | 0      | 0      |

# Bit 30 – DORD: Data Order

This bit selects the data order when a character is shifted out from the shift register.

This bit is not synchronized.

| TXESC.TBDS[2:0] | Data Field [bytes] | Element Size [RAM words] |

|-----------------|--------------------|--------------------------|

| 000             | 8                  | 4                        |

| 001             | 12                 | 5                        |

| 010             | 16                 | 6                        |

| 011             | 20                 | 7                        |

| 100             | 24                 | 8                        |

| 101             | 32                 | 10                       |

| 110             | 48                 | 14                       |

| 111             | 64                 | 18                       |

Table 34-7. Tx Buffer / FIFO / Queue Element Size

# 34.6.6.3 Tx FIFO

Tx FIFO operation is configured by programming TXBC.TFQM to '0'. Messages stored in the Tx FIFO are transmitted starting with the message referenced by the Get Index TXFQS.TFGI. After each transmission the Get Index is incremented cyclically until the Tx FIFO is empty. The Tx FIFO enables transmission of messages with the same Message ID from different Tx Buffers in the order these messages have been written to the Tx FIFO. The CAN calculates the Tx FIFO Free Level TXFQS.TFFL as difference between Get and Put Index. It indicates the number of available (free) Tx FIFO elements.

New transmit messages have to be written to the Tx FIFO starting with the Tx Buffer referenced by the Put Index TXFQS.TFQPI. An Add Request increments the Put Index to the next free Tx FIFO element. When the Put Index reaches the Get Index, Tx FIFO Full (TXFQS.TFQF = '1') is signaled. In this case no further messages should be written to the Tx FIFO until the next message has been transmitted and the Get Index has been incremented.

When a single message is added to the Tx FIFO, the transmission is requested by writing a '1' to the TXBAR bit related to the Tx Buffer referenced by the Tx FIFO's Put Index.

When multiple (n) messages are added to the Tx FIFO, they are written to n consecutive Tx Buffers starting with the Put Index. The transmissions are then requested via TXBAR. The Put Index is then cyclically incremented by n. The number of requested Tx buffers should not exceed the number of free Tx Buffers as indicated by the Tx FIFO Free Level.

When a transmission request for the Tx Buffer referenced by the Get Index is canceled, the Get Index is incremented to the next Tx Buffer with pending transmission request and the Tx FIFO Free Level is recalculated. When transmission cancellation is applied to any other Tx Buffer, the Get Index and the FIFO Free Level remain unchanged.

A Tx FIFO element allocates Element Size 32-bit words in the Message RAM (refer to Table 34-7). Therefore the start address of the next available (free) Tx FIFO Buffer is calculated by adding Tx FIFO/ Queue Put Index TXFQS.TFQPI (0...31) • Element Size to the Tx Buffer Start Address TXBC.TBSA.

#### 34.6.6.4 Tx Queue

Tx Queue operation is configured by programming TXBC.TFQM to '1'. Messages stored in the Tx Queue are transmitted starting with the message with the lowest Message ID (highest priority). In case that multiple Queue Buffers are configured with the same Message ID, the Queue Buffer with the lowest buffer number is transmitted first.

New messages have to be written to the Tx Buffer referenced by the Put Index TXFQS.TFQPI. An Add Request cyclically increments the Put Index to the next free Tx Buffer. In case that the Tx Queue is full

# SAM C20/C21

| Offset | Name   | Bit Pos. |       |        |           |       |                |            |           |       |

|--------|--------|----------|-------|--------|-----------|-------|----------------|------------|-----------|-------|

| 0xB6   |        | 23:16    |       |        |           | -     | F1P            | I[5:0]     |           |       |

| 0xB7   |        | 31:24    | DMS   | S[1:0] |           |       |                |            | RF1L      | F1F   |

| 0xB8   |        | 7:0      |       |        |           |       | F1A            | l[5:0]     |           |       |

| 0xB9   | RXF1A  | 15:8     |       |        |           |       |                |            |           |       |

| 0xBA   |        | 23:16    |       |        |           |       |                |            |           |       |

| 0xBB   |        | 31:24    |       |        |           |       |                |            |           |       |

| 0xBC   |        | 7:0      |       |        | F1DS[2:0] |       |                |            | F0DS[2:0] |       |

| 0xBD   | RXESC  | 15:8     |       |        |           |       |                |            | RBDS[2:0] |       |

| 0xBE   | TOLEGO | 23:16    |       |        |           |       |                |            |           |       |

| 0xBF   |        | 31:24    |       |        |           |       |                |            |           |       |

| 0xC0   |        | 7:0      |       |        |           | TBS   | <b>A</b> [7:0] |            |           |       |

| 0xC1   | ТХВС   | 15:8     |       |        |           | TBSA  | [15:8]         |            |           |       |

| 0xC2   |        | 23:16    |       |        |           |       | NDT            | B[5:0]     |           |       |

| 0xC3   |        | 31:24    |       | TFQM   |           |       | TFQ            | S[5:0]     |           |       |

| 0xC4   |        | 7:0      |       |        |           |       | TFF            | L[5:0]     |           |       |

| 0xC5   | TXFQS  | 15:8     |       |        |           |       |                | TFGI[4:0]  |           |       |

| 0xC6   |        | 23:16    |       |        | TFQF      |       |                | TFQPI[4:0] |           |       |

| 0xC7   |        | 31:24    |       |        |           |       |                |            |           |       |

| 0xC8   |        | 7:0      |       |        |           |       |                |            | TBDS[2:0] |       |

| 0xC9   | TXESC  | 15:8     |       |        |           |       |                |            |           |       |

| 0xCA   | TALGO  | 23:16    |       |        |           |       |                |            |           |       |

| 0xCB   |        | 31:24    |       |        |           |       |                |            |           |       |

| 0xCC   |        | 7:0      | TRPn  | TRPn   | TRPn      | TRPn  | TRPn           | TRPn       | TRPn      | TRPn  |

| 0xCD   | TXBRP  | 15:8     | TRPn  | TRPn   | TRPn      | TRPn  | TRPn           | TRPn       | TRPn      | TRPn  |

| 0xCE   | TADILE | 23:16    | TRPn  | TRPn   | TRPn      | TRPn  | TRPn           | TRPn       | TRPn      | TRPn  |

| 0xCF   |        | 31:24    | TRPn  | TRPn   | TRPn      | TRPn  | TRPn           | TRPn       | TRPn      | TRPn  |

| 0xD0   |        | 7:0      | ARn   | ARn    | ARn       | ARn   | ARn            | ARn        | ARn       | ARn   |

| 0xD1   | TXBAR  | 15:8     | ARn   | ARn    | ARn       | ARn   | ARn            | ARn        | ARn       | ARn   |

| 0xD2   | TADAK  | 23:16    | ARn   | ARn    | ARn       | ARn   | ARn            | ARn        | ARn       | ARn   |

| 0xD3   |        | 31:24    | ARn   | ARn    | ARn       | ARn   | ARn            | ARn        | ARn       | ARn   |

| 0xD4   |        | 7:0      | CRn   | CRn    | CRn       | CRn   | CRn            | CRn        | CRn       | CRn   |

| 0xD5   | TXBCR  | 15:8     | CRn   | CRn    | CRn       | CRn   | CRn            | CRn        | CRn       | CRn   |

| 0xD6   | INDUR  | 23:16    | CRn   | CRn    | CRn       | CRn   | CRn            | CRn        | CRn       | CRn   |

| 0xD7   |        | 31:24    | CRn   | CRn    | CRn       | CRn   | CRn            | CRn        | CRn       | CRn   |

| 0xD8   |        | 7:0      | TOn   | TOn    | TOn       | TOn   | TOn            | TOn        | TOn       | TOn   |

| 0xD9   | ТХВТО  | 15:8     | TOn   | TOn    | TOn       | TOn   | TOn            | TOn        | TOn       | TOn   |

| 0xDA   | TADIO  | 23:16    | TOn   | TOn    | TOn       | TOn   | TOn            | TOn        | TOn       | TOn   |

| 0xDB   |        | 31:24    | TOn   | TOn    | TOn       | TOn   | TOn            | TOn        | TOn       | TOn   |

| 0xDC   |        | 7:0      | CFn   | CFn    | CFn       | CFn   | CFn            | CFn        | CFn       | CFn   |

| 0xDD   | TXBCF  | 15:8     | CFn   | CFn    | CFn       | CFn   | CFn            | CFn        | CFn       | CFn   |

| 0xDE   | INDUF  | 23:16    | CFn   | CFn    | CFn       | CFn   | CFn            | CFn        | CFn       | CFn   |

| 0xDF   |        | 31:24    | CFn   | CFn    | CFn       | CFn   | CFn            | CFn        | CFn       | CFn   |

| 0xE0   |        | 7:0      | TIEn  | TIEn   | TIEn      | TIEn  | TIEn           | TIEn       | TIEn      | TIEn  |

| 0xE1   | TXBTIE | 15:8     | TIEn  | TIEn   | TIEn      | TIEn  | TIEn           | TIEn       | TIEn      | TIEn  |

| 0xE2   | INDIIE | 23:16    | TIEn  | TIEn   | TIEn      | TIEn  | TIEn           | TIEn       | TIEn      | TIEn  |

| 0xE3   |        | 31:24    | TIEn  | TIEn   | TIEn      | TIEn  | TIEn           | TIEn       | TIEn      | TIEn  |

| 0xE4   | TXBCIE | 7:0      | CFIEn | CFIEn  | CFIEn     | CFIEn | CFIEn          | CFIEn      | CFIEn     | CFIEn |

# 35.7.1 Register Summary - 8-bit Mode

| Offset   | Name      | Bit Pos. |          |          |        |           |          |         |             |          |

|----------|-----------|----------|----------|----------|--------|-----------|----------|---------|-------------|----------|

| 0x00     |           | 7:0      | ONDEMAND | RUNSTDBY | PRESCS | SYNC[1:0] | MOD      | E[1:0]  | ENABLE      | SWRST    |

| 0x01     |           | 15:8     |          |          |        |           | ALOCK    | P       | RESCALER[2: | 0]       |

| 0x02     | CTRLA     | 23:16    |          |          | COPEN1 | COPEN0    |          |         | CAPTEN1     | CAPTEN0  |

| 0x03     |           | 31:24    |          |          |        | CAPTMO    | DE1[1:0] |         | CAPTMC      | DE0[1:0] |

| 0x04     | CTRLBCLR  | 7:0      |          | CMD[2:0] |        |           |          | ONESHOT | LUPD        | DIR      |

| 0x05     | CTRLBSET  | 7:0      |          | CMD[2:0] |        |           |          | ONESHOT | LUPD        | DIR      |

| 0x06     | EVCTRL    | 7:0      |          |          | TCEI   | TCINV     |          |         | EVACT[2:0]  |          |

| 0x07     | EVOINE    | 15:8     |          |          | MCEOx  | MCEOx     |          |         |             | OVFEO    |

| 0x08     | INTENCLR  | 7:0      |          |          |        | MCx       |          |         | ERR         | OVF      |

| 0x09     | INTENSET  | 7:0      |          |          |        | MCx       |          |         | ERR         | OVF      |

| 0x0A     | INTFLAG   | 7:0      |          |          |        | MCx       |          |         | ERR         | OVF      |

| 0x0B     | STATUS    | 7:0      |          |          |        | CCBUFVx   | PERBUFV  |         | SLAVE       | STOP     |

| 0x0C     | WAVE      | 7:0      |          |          |        |           |          |         | WAVEG       | GEN[1:0] |

| 0x0D     | DRVCTRL   | 7:0      |          |          |        |           |          |         |             | INVENx   |

| 0x0E     | Reserved  |          |          |          |        |           |          |         |             |          |

| 0x0F     | DBGCTRL   | 7:0      |          |          |        |           |          |         |             | DBGRUN   |

| 0x10     |           | 7:0      |          | CCx      | PER    | COUNT     | STATUS   | CTRLB   | ENABLE      | SWRST    |

| 0x11     | SYNCBUSY  | 15:8     |          |          |        |           |          |         |             |          |

| 0x12     | 011102001 | 23:16    |          |          |        |           |          |         |             |          |

| 0x13     |           | 31:24    |          |          |        |           |          |         |             |          |

| 0x14     | COUNT     | 7:0      |          |          |        | COUN      | NT[7:0]  |         |             |          |

| 0x15     |           |          |          |          |        |           |          |         |             |          |

| <br>0x1A | Reserved  |          |          |          |        |           |          |         |             |          |

| 0x1B     | PER       | 7:0      |          |          |        | PER       | R[7:0]   |         |             |          |

| 0x1C     | CC0       | 7:0      |          |          |        |           | [7:0]    |         |             |          |

| 0x1D     | CC1       | 7:0      |          |          |        |           | [7:0]    |         |             |          |

| 0x1E     |           |          |          |          |        |           |          |         |             |          |

| <br>0x2E | Reserved  |          |          |          |        |           |          |         |             |          |

| 0x2F     | PERBUF    | 7:0      |          |          |        | PERB      | UF[7:0]  |         |             |          |

| 0x30     | CCBUF0    | 7:0      |          |          |        | CCBL      | JF[7:0]  |         |             |          |

| 0x31     | CCBUF1    | 7:0      |          |          |        |           | JF[7:0]  |         |             |          |

# 35.7.1.1 Control A

Name:CTRLAOffset:0x00Reset:0x00000000Property:PAC Write-Protection, Write-Synchronized, Enable-Protected

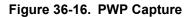

The TCC can perform two input captures and restart the counter on one of the edges. This enables the TCC to measure the pulse-width and period and to characterize the frequency *f* and *dutyCycle* of an input signal:

$$f = \frac{1}{T}$$

,  $dutyCycle = \frac{t_p}{T}$

Selecting PWP or PPW in the Timer/Counter Event Input 1 Action bit group in the Event Control register (EVCTRL.EVACT1) enables the TCC to perform one capture action on the rising edge and the other one on the falling edge. When using PPW (period and pulse-width) event action, period T will be captured into CC0 and the pulse-width  $t_p$  into CC1. The PWP (Pulse-width and Period) event action offers the same functionality, but T will be captured into CC1 and  $t_p$  into CC0.

The Timer/Counter Event x Invert Enable bit in Event Control register (EVCTRL.TCEINVx) is used for event source x to select whether the wraparound should occur on the rising edge or the falling edge. If EVCTRL.TCEINVx=1, the wraparound will happen on the falling edge.

The corresponding capture is done only if the channel is enabled in capture mode (CTRLA.CPTENx=1). If not, the capture action will be ignored and the channel will be enabled in compare mode of operation. When only one of these channel is required, the other channel can be used for other purposes.

The TCC can detect capture overflow of the input capture channels: When a new capture event is detected while the INTFLAG.MCx is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

**Note:** When up-counting (CTRLBSET.DIR=0), counter values lower than 1 cannot be captured in Capture Minimum mode (FCTRLn.CAPTURE=CAPTMIN). To capture the full range including value 0, the TCC must be configured in down-counting mode (CTRLBSET.DIR=0).

**Note:** In dual-slope PWM operation, and when TOP is lower than MAX/2, the CCx MSB captures the CTRLB.DIR state to identify the ramp on which the capture has been done. For rising ramps CCx[MSB] is zero, for falling ramps CCx[MSB]=1.

# 36.6.3 Additional Features

# 36.6.3.1 One-Shot Operation

When one-shot is enabled, the counter automatically stops on the next counter overflow or underflow condition. When the counter is stopped, the Stop bit in the Status register (STATUS.STOP) is set and the waveform outputs are set to the value defined by DRVCTRL.NREx and DRVCTRL.NRVx.

Name:EVCTRLOffset:0x02 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1       | 0       |

|--------|---|---|---|---|---|-------|---------|---------|

|        |   |   |   |   |   | INVEI | EMPTYEO | STARTEI |

| Access |   |   |   |   |   | R/W   | R/W     | R/W     |

| Reset  |   |   |   |   |   | 0     | 0       | 0       |

# Bit 2 – INVEI: Enable Inversion Data Buffer Empty Event Output

This bit defines the edge detection of the input event for STARTEI.

| Value | Description   |

|-------|---------------|

| 0     | Rising edge.  |

| 1     | Falling edge. |

# Bit 1 – EMPTYEO: Data Buffer Empty Event Output

This bit indicates whether or not the Data Buffer Empty event is enabled and will be generated when the Data Buffer register is empty.

| Value | Description                                                    |

|-------|----------------------------------------------------------------|

| 0     | Data Buffer Empty event is disabled and will not be generated. |

| 1     | Data Buffer Empty event is enabled and will be generated.      |

# Bit 0 – STARTEI: Start Conversion Event Input

This bit indicates whether or not the Start Conversion event is enabled and data are loaded from the Data Buffer register to the Data register upon event reception.

| Value | Description                                                   |

|-------|---------------------------------------------------------------|

| 0     | A new conversion will not be triggered on any incoming event. |

| 1     | A new conversion will be triggered on any incoming event.     |

# 41.8.4 Interrupt Enable Clear

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

Name:INTENCLROffset:0x04 [ID-00000bc7]Reset:0x00Property:PAC Write-Protection

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | EMPTY | UNDERRUN |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

# Bit 1 – EMPTY: Data Buffer Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Write-protection does not apply to accesses through an external debugger.

### **Related Links**

PAC - Peripheral Access Controller

# 44.6 Functional Description

# 44.6.1 Principle of Operation

FREQM counts the number of periods of the measured clock (GCLK\_FREQM\_MSR) with respect to the reference clock (GCLK\_FREQM\_REF). The measurement is done for a period of REFNUM/ $f_{CLK_REF}$  and stored in the Value register (VALUE.VALUE). REFNUM is the number of Reference clock cycles selected in the Configuration A register (CFGA.REFNUM).

The frequency of the measured clock,  $f_{\rm CLK\ MSR}$ , is calculated by

$f_{\text{CLK}_{\text{MSR}}} = \left(\frac{\text{VALUE}}{\text{REFNUM}}\right) f_{\text{CLK}_{\text{REF}}}$

# 44.6.2 Basic Operation

# 44.6.2.1 Initialization

Before enabling FREQM, the device and peripheral must be configured:

• Each of the generic clocks (GCLK\_FREQM\_REF and GCLK\_FREQM\_MSR) must be configured and enabled.

**Important:** The reference clock must be slower than the measurement clock.

• Write the number of Reference clock cycles for which the measurement is to be done in the Configuration A register (CFGA.REFNUM). This must be a non-zero number.

The following register is enable-protected, meaning that it can only be written when the FREQM is disabled (CTRLA.ENABLE=0):

Configuration A register (CFGA)

Enable-protection is denoted by the "Enable-Protected" property in the register description.

#### **Related Links**

GCLK - Generic Clock Controller

# 44.6.2.2 Enabling, Disabling and Resetting

The FREQM is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The peripheral is disabled by writing CTRLA.ENABLE=0.

The FREQM is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). On software reset, all registers in the FREQM will be reset to their initial state, and the FREQM will be disabled.

Then ENABLE and SWRST bits are write-synchronized.

#### **Related Links**

Synchronization

| Symbol | Parameters                         | Conditions (2) | Min  | Тур  | Max  | Unit |  |

|--------|------------------------------------|----------------|------|------|------|------|--|

| ENOB   | Effective Number Of Bits           | Ext ref = 1.2V | 13.5 | 14.2 | 14.4 | dB   |  |

|        |                                    | Int Ref = 5.5V | 11   | 11.2 | 11.4 |      |  |

| DR     | Dynamic Range                      | Ext ref = 1.2V | 89   | 91   | 92   | dB   |  |

|        |                                    | Int Ref = 5.5V | 83   | 92   | 96   |      |  |

| SNR    | Signal to Noise Ratio              | Ext ref = 1.2V | 84   | 88   | 89   | dB   |  |

|        |                                    | Int Ref = 5.5V | 77   | 79   | 80   |      |  |

| SINAD  | Signal to Noise + Distortion Ratio | Ext ref = 1.2V | 83   | 87   | 89   | dB   |  |

|        |                                    | Int Ref = 5.5V | 68   | 69   | 71   |      |  |

| THD    | Total Harmonic Distortion          | Ext ref = 1.2V | -105 | -100 | -92  | dB   |  |

|        |                                    | Int Ref = 5.5V | -70  | -69  | -69  |      |  |

Table 45-24. SDADC AC Performance: : Differential Input Mode<sup>(1)</sup>

- 1. These are based on characterization.

- 2. OSR=256

# Table 45-25. Power consumption <sup>(1)</sup>

| Symbol        | Parameters           | Conditions                                                                              | Та                   | Тур. | Max | Units |

|---------------|----------------------|-----------------------------------------------------------------------------------------|----------------------|------|-----|-------|

| IDD<br>VDDANA | Power<br>consumption | CTLSDADC=0x0 External Ref -<br>VCCANA = 5.5V Vref = 2V Ref buf on<br>SCLK_SDADC = 6 MHz | Max 85°C<br>Typ 25°C | 588  | 658 | μA    |

|               |                      | CTLSDADC=0x0 Internal Ref -<br>VDDANA=Vref= 5.5V Ref buf off<br>SCLK_SDADC = 6 MHz      | -                    | 552  | 608 |       |

1. These are based on characterization.

# 45.10.6 Digital to Analog Converter (DAC) Characteristics Table 45-26. Operating Conditions<sup>(1)</sup>

| Symbol | Parameters                   | Conditions     | Min  | Тур       | Мах           | Unit |

|--------|------------------------------|----------------|------|-----------|---------------|------|

| RES    | Input resolution             |                | -    | -         | 10            | Bits |

| VDDANA | Analog supply voltage        |                | 2.7  | -         | 5.5           | V    |

| AVREF  | External reference voltage   |                | 1    | -         | VDDANA - 0.6  | V    |

|        | Internal reference voltage 1 | VREF.SEL = 0x0 | -    | 1.024     | -             | V    |

|        |                              | VREF.SEL = 0x2 | -    | 2.048     | -             |      |

|        |                              | VREF.SEL = 0x3 | -    | 4.096 (2) | -             |      |

|        | Internal reference voltage 2 |                | -    | VDDANA    | -             | V    |

|        | Linear output voltage range  |                | 0.05 | -         | VDDANA - 0.05 | V    |