Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

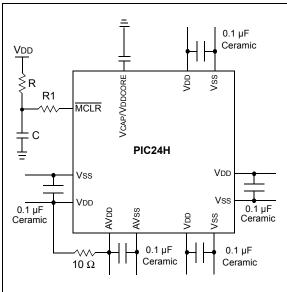

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including MCUs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP/VDDCORE pin, which is used to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 24.0** "Electrical Characteristics" for additional information.

The placement of this capacitor should be close to the VCAP/VDDCORE. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 21.2** "**On-Chip Voltage Regulator**" for details.

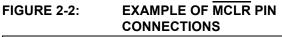

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor to Vss on unused pins and drive the output to logic low.

### TABLE 4-17: DMA REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|-----------|--------|--------|--------|--------|--------|--------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| DMA5PAD   | 03C4 |        |           |        |        |        |        |        | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA5CNT   | 03C6 |        | _         | _      | _      | _      | _      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA6CON   | 03C8 | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | _      | _      | _         | _      | AMOD   | E<1:0> | _         | _      | MODE   | <1:0>  | 0000          |

| DMA6REQ   | 03CA | FORCE  | _         | _      | _      | _      | _      | _      | _      | _         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA6STA   | 03CC |        | STA<15:0> |        |        |        |        |        |        |           |        | 0000   |        |           |        |        |        |               |

| DMA6STB   | 03CE |        | STB<15:0> |        |        |        |        |        |        |           |        | 0000   |        |           |        |        |        |               |

| DMA6PAD   | 03D0 |        | PAD<15:0> |        |        |        |        |        |        |           | 0000   |        |        |           |        |        |        |               |

| DMA6CNT   | 03D2 | _      | _         | _      | _      | _      | _      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN   | SIZE      | DIR    | HALF   | NULLW  | -      | _      | _      | _         | _      | AMOD   | E<1:0> | —         | —      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE  |           | _      | _      | _      | -      | _      | _      | -         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |        |           | •      | •      | •      |        |        | S      | TA<15:0>  | •      |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |        |           |        |        |        |        |        | S      | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |        |           |        |        |        |        |        | P      | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | _      | —         | —      | —      | _      | —      |        |        |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7 | PWCOL6    | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 | _      | _         | _      | _      |        | LSTCH  | 1<3:0> |        | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000          |

| DSADR     | 03E4 |        |           |        |        | •      |        |        | DS     | ADR<15:0> | •      | 1      |        |           | 1      |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

PIC24HJXXXGPX06/X08/X10

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 **CNIF:** Input Change Notification Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <b>CNIE:</b> Input Change Notification Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                        |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul>                                         |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                                                                   |

- 1 = Interrupt request enabled

- 0 = Interrupt request on abled

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0           | R/W-0                                                                                        | U-0                                                                                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| T6IE            | DMA4IE                                                                                       | —                                                                                              | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |  |  |

| bit 15          |                                                                                              |                                                                                                |                  |                  |                  |                 | bit 8   |  |  |  |  |  |

|                 |                                                                                              |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| R/W-0           | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

| IC5IE           | IC4IE                                                                                        | IC3IE                                                                                          | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |  |  |

| bit 7           |                                                                                              |                                                                                                |                  |                  |                  |                 | bit 0   |  |  |  |  |  |

| Legend:         |                                                                                              |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| R = Readable    | bit                                                                                          | W = Writable                                                                                   | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |  |  |

| -n = Value at F | POR                                                                                          | '1' = Bit is set                                                                               |                  | '0' = Bit is cle |                  | x = Bit is unki | nown    |  |  |  |  |  |

|                 |                                                                                              |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 15          | T6IE: Timer6                                                                                 | Interrupt Enab                                                                                 | le bit           |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable                                                                                  |                  |                  |                  |                 |         |  |  |  |  |  |

|                 | •                                                                                            | Interrupt request not enabled IA4IE: DMA Channel 4 Data Transfer Complete Interrupt Enable bit |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 14          |                                                                                              |                                                                                                |                  | Complete Interr  | rupt Enable bit  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable<br>equest not ena                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 13          | -                                                                                            | ted: Read as '                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 12          | -                                                                                            | ut Compare Ch                                                                                  |                  | upt Enable bit   |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable                                                                                  |                  |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest not ena                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 11          | •                                                                                            | <b>DC7IE:</b> Output Compare Channel 7 Interrupt Enable bit<br>= Interrupt request enabled     |                  |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable<br>equest not ena                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 10          | -                                                                                            | •                                                                                              |                  | upt Enable bit   |                  |                 |         |  |  |  |  |  |

|                 | •                                                                                            | C6IE: Output Compare Channel 6 Interrupt Enable bit<br>= Interrupt request enabled             |                  |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest not ena                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 9           | OC5IE: Output Compare Channel 5 Interrupt Enable bit                                         |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

|                 | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ul> |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 8           | -                                                                                            | -                                                                                              |                  | Enabla bit       |                  |                 |         |  |  |  |  |  |

|                 | IC6IE: Input Capture Channel 6 Interrupt Enable bit<br>1 = Interrupt request enabled         |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest not ena                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 7           | IC5IE: Input C                                                                               | Capture Chann                                                                                  | el 5 Interrupt I | Enable bit       |                  |                 |         |  |  |  |  |  |

|                 | •                                                                                            | equest enable                                                                                  |                  |                  |                  |                 |         |  |  |  |  |  |

| 1.1.0           | -                                                                                            | equest not ena                                                                                 |                  | <b>-</b>         |                  |                 |         |  |  |  |  |  |

| bit 6           |                                                                                              | Capture Chann                                                                                  | •                | Enable bit       |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable<br>equest not ena                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 5           |                                                                                              | Capture Chann                                                                                  |                  | Enable bit       |                  |                 |         |  |  |  |  |  |

|                 | 1 = Interrupt r                                                                              | equest enable                                                                                  | d                |                  |                  |                 |         |  |  |  |  |  |

|                 | •                                                                                            | equest not ena                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 4           |                                                                                              |                                                                                                |                  | Complete Interr  | rupt Enable bit  |                 |         |  |  |  |  |  |

|                 |                                                                                              | equest enable<br>equest not ena                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

| bit 3           |                                                                                              | Event Interrup                                                                                 |                  |                  |                  |                 |         |  |  |  |  |  |

|                 |                                                                                              |                                                                                                |                  |                  |                  |                 |         |  |  |  |  |  |

|                 | 1 = Interrupt r                                                                              | equest enable                                                                                  | d                |                  |                  |                 |         |  |  |  |  |  |

#### REGISTER 7-23: IPC8: INTERRUPT PRIORITY CONTROL REGISTER 8

| U-0           | R/W-1                                                                                                                       | R/W-0                                                                 | R/W-0 | U-0              | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------|------------------|----------------|-----------------|-------|--|--|--|--|--|--|

|               |                                                                                                                             | C1IP<2:0>                                                             |       |                  |                | C1RXIP<2:0>     |       |  |  |  |  |  |  |

| bit 15        |                                                                                                                             |                                                                       |       |                  |                |                 | bit   |  |  |  |  |  |  |

| U-0           | R/W-1                                                                                                                       | R/W-0                                                                 | R/W-0 | U-0              | R/W-1          | R/W-0           | R/W-0 |  |  |  |  |  |  |

|               | N/W-1                                                                                                                       | SPI2IP<2:0>                                                           | N/W-0 | <u> </u>         | N/ VV- 1       | SPI2EIP<2:0>    | N/W-U |  |  |  |  |  |  |

| bit 7         |                                                                                                                             | 0                                                                     |       |                  |                | 0               | bit   |  |  |  |  |  |  |

| Legend:       |                                                                                                                             |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                       | W = Writable I                                                        | oit   | U = Unimpler     | mented bit, re | ad as '0'       |       |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                         | '1' = Bit is set                                                      |       | '0' = Bit is cle | ared           | x = Bit is unkn | own   |  |  |  |  |  |  |

| bit 15        | Unimpleme                                                                                                                   | nted: Read as 'o                                                      | )'    |                  |                |                 |       |  |  |  |  |  |  |

| bit 14-12     | -                                                                                                                           | ECAN1 Event In                                                        |       | ty bits          |                |                 |       |  |  |  |  |  |  |

|               | 111 = Interru                                                                                                               | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               |                                                                                                                             | upt is priority 1                                                     |       |                  |                |                 |       |  |  |  |  |  |  |

|               |                                                                                                                             | upt source is disa                                                    |       |                  |                |                 |       |  |  |  |  |  |  |

| bit 11        | -                                                                                                                           | nted: Read as 'o                                                      |       |                  |                |                 |       |  |  |  |  |  |  |

| bit 10-8      | C1RXIP<2:0>: ECAN1 Receive Data Ready Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           | unt in uniquity of                                                    |       |                  |                |                 |       |  |  |  |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                         |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

| bit 7         |                                                                                                                             | nted: Read as '0                                                      |       |                  |                |                 |       |  |  |  |  |  |  |

| bit 6-4       | -                                                                                                                           |                                                                       |       | v bits           |                |                 |       |  |  |  |  |  |  |

|               | SPI2IP<2:0>: SPI2 Event Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)               |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               |                                                                                                                             | upt is priority 1<br>upt source is disa                               | abled |                  |                |                 |       |  |  |  |  |  |  |

| bit 3         |                                                                                                                             | nted: Read as '0                                                      |       |                  |                |                 |       |  |  |  |  |  |  |

| bit 2-0       | -                                                                                                                           | 0>: SPI2 Error In                                                     |       | tv bits          |                |                 |       |  |  |  |  |  |  |

|               |                                                                                                                             | upt is priority 7 (I                                                  | -     | -                |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | •                                                                                                                           |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

|               | 001 = Interru                                                                                                               | upt is priority 1                                                     |       |                  |                |                 |       |  |  |  |  |  |  |

|               | 000 = Interru                                                                                                               |                                                                       |       |                  |                |                 |       |  |  |  |  |  |  |

| U-0           | R/W-1                                                                                     | R/W-0                                  | R/W-0   | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------|----------------------------------------|---------|------------------|------------------|-----------------|---------|--|--|--|--|--|

| _             |                                                                                           | IC5IP<2:0>                             |         |                  |                  | IC4IP<2:0>      |         |  |  |  |  |  |

| bit 15        |                                                                                           |                                        |         |                  |                  |                 | bit 8   |  |  |  |  |  |

| U-0           | R/W-1                                                                                     | R/W-0                                  | R/W-0   | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|               | 10.00-1                                                                                   | IC3IP<2:0>                             | 10,00-0 |                  | 10.00-1          | DMA3IP<2:0>     | 10.00-0 |  |  |  |  |  |

| bit 7         |                                                                                           |                                        |         |                  |                  |                 | bit C   |  |  |  |  |  |

| Legend:       |                                                                                           |                                        |         |                  |                  |                 |         |  |  |  |  |  |

| R = Readabl   | e bit                                                                                     | W = Writable                           | bit     | U = Unimple      | mented bit, re   | ad as '0'       |         |  |  |  |  |  |

| -n = Value at | POR                                                                                       | '1' = Bit is set                       |         | '0' = Bit is cle | eared            | x = Bit is unkn | own     |  |  |  |  |  |

| bit 15        | Unimpleme                                                                                 | ented: Read as 'o                      | o'      |                  |                  |                 |         |  |  |  |  |  |

| bit 14-12     |                                                                                           | : Input Capture C                      |         | • •              | oits             |                 |         |  |  |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt) .</pre>                   |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               |                                                                                           | upt is priority 1<br>upt source is dis | ablad   |                  |                  |                 |         |  |  |  |  |  |

| bit 11        |                                                                                           | -                                      |         |                  |                  |                 |         |  |  |  |  |  |

| bit 10-8      | Unimplemented: Read as '0'<br>IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits |                                        |         |                  |                  |                 |         |  |  |  |  |  |

| 511 10-0      | 111 = Interrupt is priority 7 (highest priority interrupt)                                |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •<br>001 = Interrupt is priority 1                                                        |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               |                                                                                           | upt source is dis                      | abled   |                  |                  |                 |         |  |  |  |  |  |

| bit 7         | Unimpleme                                                                                 | ented: Read as 'o                      | כ'      |                  |                  |                 |         |  |  |  |  |  |

| bit 6-4       |                                                                                           | : Input Capture C                      |         | • •              | oits             |                 |         |  |  |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                     |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               |                                                                                           | upt is priority 1<br>upt source is dis | ablad   |                  |                  |                 |         |  |  |  |  |  |

| bit 3         |                                                                                           | ented: Read as '                       |         |                  |                  |                 |         |  |  |  |  |  |

| bit 2-0       | -                                                                                         | 0>: DMA Channe                         |         | nsfer Complete   | - Interrunt Pric | ority hits      |         |  |  |  |  |  |

| 511 2 0       |                                                                                           | upt is priority 7 (I                   |         |                  |                  | inty bito       |         |  |  |  |  |  |

|               | •                                                                                         |                                        | 0       |                  |                  |                 |         |  |  |  |  |  |

|               | •                                                                                         |                                        |         |                  |                  |                 |         |  |  |  |  |  |

|               | 001 = Interr                                                                              | upt is priority 1                      |         |                  |                  |                 |         |  |  |  |  |  |

|               | 000 = Interr                                                                              |                                        |         |                  |                  |                 |         |  |  |  |  |  |

### REGISTER 7-24: IPC9: INTERRUPT PRIORITY CONTROL REGISTER 9

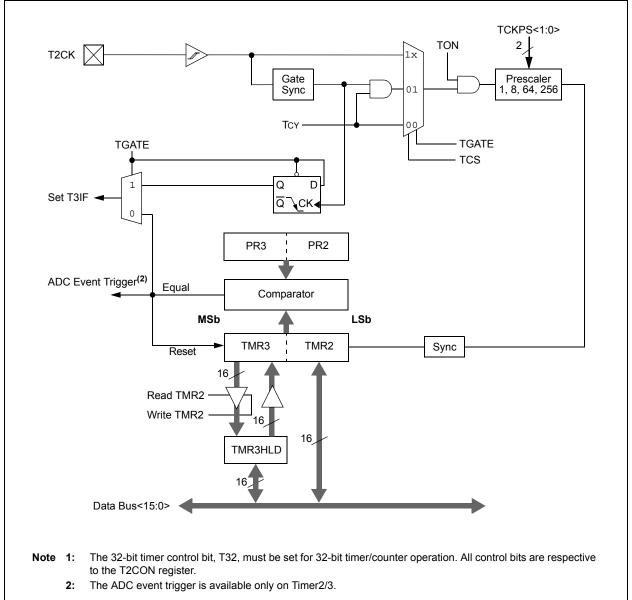

A block diagram for a 32-bit timer pair (Timer4/5) example is shown in Figure 13-1 and a timer (Timer4) operating in 16-bit mode example is shown in Figure 13-2.

**Note:** Only Timer2 and Timer3 can trigger a DMA data transfer.

NOTES:

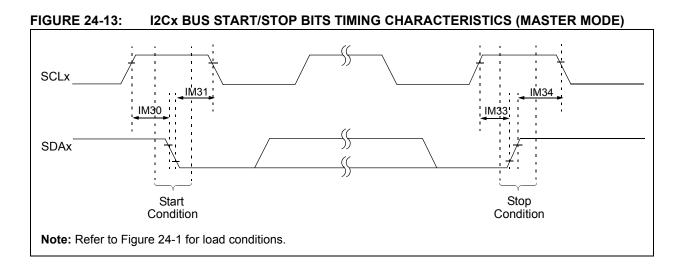

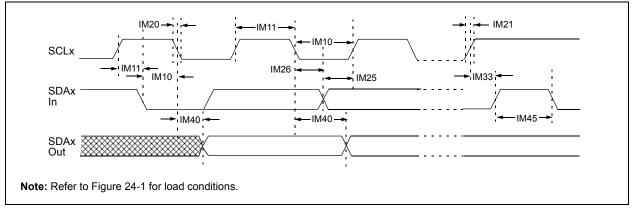

## 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70235), which is available from the Microchip website (www.microchip.com).

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The PIC24HJXXXGPX06/X08/X10 devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation.

- I<sup>2</sup>C Slave mode supports 7 and 10-bit address.

- I<sup>2</sup>C Master mode supports 7 and 10-bit address.

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly.

## 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $l^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation with 7 or 10-bit address

For details about the communication sequence in each of these modes, please refer to the *"PIC24H Family Reference Manual"*.

## 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0 HSC | R-0 HSC | U-0 | U-0 | U-0 | R/C-0 HS | R-0 HSC | R-0 HSC |

|---------|---------|-----|-----|-----|----------|---------|---------|

| ACKSTAT | TRSTAT  | —   | _   | —   | BCL      | GCSTAT  | ADD10   |

| bit 15  |         |     |     |     |          |         | bit 8   |

| R/C-0 HS | R/C-0 HS | R-0 HSC | R/C-0 HSC | R/C-0 HSC | R-0 HSC | R-0 HSC | R-0 HSC |

|----------|----------|---------|-----------|-----------|---------|---------|---------|

| IWCOL    | I2COV    | D_A     | Р         | S         | R_W     | RBF     | TBF     |

| bit 7    |          |         |           |           |         |         | bit 0   |

| Legend:           | U = Unimplemented b | oit, read as '0'     | C = Clear only bit         |

|-------------------|---------------------|----------------------|----------------------------|

| R = Readable bit  | W = Writable bit    | HS = Set in hardware | HSC = Hardware set/cleared |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown         |

| <b>ACKSTAT:</b> Acknowledge Status bit (when operation) (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = NACK received from slave</li> <li>0 = ACK received from slave</li> </ul>                                                                                                                                        |

| Hardware set or clear at end of slave Acknowledge.                                                                                                                                                                           |

| <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                                      |

| <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul> |

| Unimplemented: Read as '0'                                                                                                                                                                                                   |

| BCL: Master Bus Collision Detect bit                                                                                                                                                                                         |

| <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> </ul>                                                                                                                |

| Hardware set at detection of bus collision.                                                                                                                                                                                  |

| GCSTAT: General Call Status bit                                                                                                                                                                                              |

| <ul> <li>1 = General call address was received</li> <li>0 = General call address was not received</li> </ul>                                                                                                                 |

| Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                                                                                    |

| ADD10: 10-Bit Address Status bit                                                                                                                                                                                             |

| 1 = 10-bit address was matched<br>0 = 10-bit address was not matched                                                                                                                                                         |

| Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                                                                               |

| IWCOL: Write Collision Detect bit                                                                                                                                                                                            |

| 1 = An attempt to write the I2CxTRN register failed because the $I^2C$ module is busy<br>0 = No collision                                                                                                                    |

| Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).                                                                                                                                             |

| I2COV: Receive Overflow Flag bit                                                                                                                                                                                             |

| <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                                                                           |

| Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                                                |

| <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                      |

| 1 = Indicates that the last byte received was data                                                                                                                                                                           |

| <ul> <li>Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul>                                                       |

| P: Stop bit                                                                                                                                                                                                                  |

| 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                         |

| 0 = Stop bit was not detected last                                                                                                                                                                                           |

| Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                           |

|                                                                                                                                                                                                                              |

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                                                                                                                                | R/W-0                             | R/W-0               | R/W-0                           | U-0               | R/W-0                  | R/W-0           |  |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|---------------------------------|-------------------|------------------------|-----------------|--|--|--|

| UARTEN <sup>(1)</sup> |                                                                                                                                                                                    | USIDL                             | IREN <sup>(2)</sup> | RTSMD                           |                   | UEN                    | <1:0>           |  |  |  |

| bit 15                |                                                                                                                                                                                    |                                   |                     |                                 |                   |                        | bit 8           |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     |                                 |                   |                        |                 |  |  |  |

| R/W-0 HC              | R/W-0                                                                                                                                                                              | R/W-0 HC                          | R/W-0               | R/W-0                           | R/W-0             | R/W-0                  | R/W-0           |  |  |  |

| WAKE                  | LPBACK                                                                                                                                                                             | ABAUD                             | URXINV              | BRGH                            | PDSE              | _<1:0>                 | STSEL           |  |  |  |

| bit 7                 |                                                                                                                                                                                    |                                   |                     |                                 |                   |                        | bit C           |  |  |  |

| Legend:               |                                                                                                                                                                                    | HC = Hardwa                       | ro cloared          |                                 |                   |                        |                 |  |  |  |

| R = Readable          | hit                                                                                                                                                                                | W = Writable                      |                     | LI – Unimplo                    | mented bit, read  |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     | $0^{\circ} = \text{Bit is cle}$ |                   |                        |                 |  |  |  |

| -n = Value at F       | 'UR                                                                                                                                                                                | '1' = Bit is set                  |                     |                                 | ared              | x = Bit is unkr        | IOWN            |  |  |  |

| bit 15                | UARTEN: UA                                                                                                                                                                         | RTx Enable bi                     | <sub>t</sub> (1)    |                                 |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     | e controlled by                 | UARTx as defi     | ned by UEN<1:          | :0>             |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     |                                 | y port latches; U |                        |                 |  |  |  |

| bit 14                | Unimplemen                                                                                                                                                                         | ted: Read as '                    | 0'                  |                                 |                   |                        |                 |  |  |  |

| bit 13                | USIDL: Stop                                                                                                                                                                        | in Idle Mode bi                   | t                   |                                 |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    | ue module ope                     |                     |                                 | dle mode          |                        |                 |  |  |  |

| h:: 40                |                                                                                                                                                                                    | module opera                      |                     |                                 |                   |                        |                 |  |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup><br>1 = IrDA <sup>®</sup> encoder and decoder enabled                                                         |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    | coder and dec                     |                     |                                 |                   |                        |                 |  |  |  |

| bit 11                | RTSMD: Mod                                                                                                                                                                         | le Selection for                  | UxRTS Pin b         | it                              |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    | in in Simplex n<br>in in Flow Con |                     |                                 |                   |                        |                 |  |  |  |

| bit 10                | Unimplemen                                                                                                                                                                         | ted: Read as '                    | 0'                  |                                 |                   |                        |                 |  |  |  |

| bit 9-8               | UEN<1:0>: UARTx Enable bits                                                                                                                                                        |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       | 11 = UxTX, UxRX and BCLK pins are enabled and used; UxCTS pin controlled by port latches                                                                                           |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       | 10 = UxTX, UxRX, $\overline{\text{UxCTS}}$ and $\overline{\text{UxRTS}}$ pins are enabled and used                                                                                 |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       | 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches<br>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       | port latcl                                                                                                                                                                         |                                   |                     |                                 |                   |                        | lolled by       |  |  |  |

| bit 7                 | WAKE: Wake                                                                                                                                                                         | up on Start bi                    | t Detect Durin      | g Sleep Mode                    | Enable bit        |                        |                 |  |  |  |

|                       | <b>WAKE:</b> Wake-up on Start bit Detect During Sleep Mode Enable bit<br>1 = UARTx will continue to sample the UxRX pin; interrupt generated on falling edge; bit cleared          |                                   |                     |                                 |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    | are on following                  | g rising edge       |                                 |                   |                        |                 |  |  |  |

|                       | 0 = No wake                                                                                                                                                                        | •                                 |                     |                                 |                   |                        |                 |  |  |  |

| bit 6                 |                                                                                                                                                                                    | RTx Loopback                      |                     | bit                             |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    | oopback mode<br>k mode is disal   |                     |                                 |                   |                        |                 |  |  |  |

| bit 5                 | -                                                                                                                                                                                  | -Baud Enable                      |                     |                                 |                   |                        |                 |  |  |  |

|                       | 1 = Enable b                                                                                                                                                                       | aud rate meas                     | urement on th       |                                 | er – requires re  | ception of a Sy        | nc field (0x55) |  |  |  |

|                       |                                                                                                                                                                                    | ny data; cleared<br>e measuremen  |                     | •                               | on                |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     |                                 | amily Referenc    | e <i>Manual"</i> for i | nformation or   |  |  |  |

| en                    | abling the UAR                                                                                                                                                                     | T module for re                   | eceive or trans     | smit operation.                 |                   |                        |                 |  |  |  |

|                       |                                                                                                                                                                                    |                                   |                     |                                 |                   |                        |                 |  |  |  |

#### 2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 19-2: CiCTRL2: ECAN™ MODULE CONTROL REGISTER 2

| U-0             | U-0                | U-0                                                   | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |  |  |  |

|-----------------|--------------------|-------------------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|--|

| _               | —                  | —                                                     | _              | —                | —                | —               | —     |  |  |  |  |  |

| bit 15          |                    |                                                       |                |                  |                  |                 | bit 8 |  |  |  |  |  |

|                 |                    |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

| U-0             | U-0                | U-0                                                   | R-0            | R-0              | R-0              | R-0             | R-0   |  |  |  |  |  |

| —               | —                  | —                                                     | DNCNT<4:0>     |                  |                  |                 |       |  |  |  |  |  |

| bit 7           |                    |                                                       |                |                  |                  |                 | bit 0 |  |  |  |  |  |

|                 |                    |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

| Legend:         |                    |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

| R = Readable    | bit                | W = Writable                                          | bit            | U = Unimpler     | mented bit, read | as '0'          |       |  |  |  |  |  |

| -n = Value at F | POR                | '1' = Bit is set                                      |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

|                 |                    |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

| bit 15-5        | Unimplemen         | ted: Read as '                                        | כ'             |                  |                  |                 |       |  |  |  |  |  |

| bit 4-0         | DNCNT<4:0>         | •: DeviceNet™                                         | Filter Bit Num | ber bits         |                  |                 |       |  |  |  |  |  |

|                 | 10010-1111         | 1 = Invalid sele                                      | ection         |                  |                  |                 |       |  |  |  |  |  |

|                 | 10001 <b>= Com</b> | 10001 = Compare up to data byte 3, bit 6 with EID<17> |                |                  |                  |                 |       |  |  |  |  |  |

|                 | •                  |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

|                 | •                  |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

|                 | •                  |                                                       |                |                  |                  |                 |       |  |  |  |  |  |

|                 |                    | npare up to data<br>not compare da                    |                | with EID<0>      |                  |                 |       |  |  |  |  |  |

#### REGISTER 19-22: CiRXFUL1: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                             |                    |

|-------------------|--------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits