Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp206t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, which is available from the Microchip website (www.microchip.com).

## 2.1 Basic Connection Requirements

Getting started with the PIC24HJXXXGPX06/X08/X10 family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors") • VCAP/VDDCORE

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss    | pins | mu  | st be |

|-------|-------|---------|-------|---------|------|-----|-------|

|       | conn  | ected   | indep | endent  | of   | the | ADC   |

|       | volta | ge refe | rence | source. |      |     |       |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| IADLE 4  | -7. 1       | INFUIC |                          |        |        |        |           |       |                                      |                |             |       |       |       |       |          |       |               |

|----------|-------------|--------|--------------------------|--------|--------|--------|-----------|-------|--------------------------------------|----------------|-------------|-------|-------|-------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8                                | Bit 7          | Bit 6       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF   | 0140        |        |                          |        |        |        |           |       | Input 1 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _      | _                        | ICSIDL | _      | _      | _         | _     | - ICTMR ICI<1:0> ICOV ICBNE ICM<2:0> |                |             |       |       |       |       |          | 0000  |               |

| IC2BUF   | 0144        |        |                          |        |        |        |           |       | Input 2 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | XXXX          |

| IC2CON   | 0146        | _      | _                        | ICSIDL | _      | _      | _         | _     | _                                    | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |        | Input 3 Capture Register |        |        |        |           |       |                                      |                |             |       |       | xxxx  |       |          |       |               |

| IC3CON   | 014A        | _      | _                        | ICSIDL | —      | _      | _         | _     |                                      | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |        |                          |        |        |        |           |       | Input 4 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | XXXX          |

| IC4CON   | 014E        | _      | _                        | ICSIDL | _      | _      | _         | _     | _                                    | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |        |                          |        |        |        |           |       | Input 5 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | XXXX          |

| IC5CON   | 0152        | _      | _                        | ICSIDL | _      | _      | _         | _     | _                                    | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |        |                          |        |        |        |           |       | Input 6 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | XXXX          |

| IC6CON   | 0156        | _      | _                        | ICSIDL | _      | _      | _         | _     | _                                    | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |        |                          |        |        |        |           |       | Input 7 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | XXXX          |

| IC7CON   | 015A        | _      |                          | ICSIDL | —      | _      | —         | _     |                                      | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |        |                          |        |        |        |           |       | Input 8 Ca                           | pture Regis    | ter         |       |       |       |       |          |       | xxxx          |

| IC8CON   | 015E        | —      | _                        | ICSIDL | —      | _      | _         | _     |                                      | ICTMR          | ICI<        | :1:0> | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| Logondy  |             |        | Deed                     |        |        |        | Desetualu |       | wn in hovo                           | de alus al fau | ماء ماد الم |       |       |       |       |          |       |               |

#### TABLE 4-7: INPUT CAPTURE REGISTER MAP

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-17: DMA REGISTER MAP (CONTINUED)

| File Name | Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                | Bit 7     | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|----------------------|--------|--------|--------|--------|--------|----------------------|-----------|--------|--------|--------|-----------|--------|--------|--------|---------------|

| DMA5PAD   | 03C4 |        |                      |        |        |        |        |        | P                    | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA5CNT   | 03C6 |        | _                    | _      | _      | _      | _      |        |                      |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA6CON   | 03C8 | CHEN   | SIZE                 | DIR    | HALF   | NULLW  | _      | _      | AMODE<1:0> MODE<1:0> |           |        |        |        |           |        | 0000   |        |               |

| DMA6REQ   | 03CA | FORCE  | FORCE IRQSEL<6:0> 00 |        |        |        |        |        |                      |           |        | 0000   |        |           |        |        |        |               |

| DMA6STA   | 03CC |        | STA<15:0>            |        |        |        |        |        |                      |           |        |        |        | 0000      |        |        |        |               |

| DMA6STB   | 03CE |        | STB<15:0>            |        |        |        |        |        |                      |           |        |        |        | 0000      |        |        |        |               |

| DMA6PAD   | 03D0 |        | PAD<15:0>            |        |        |        |        |        |                      |           |        |        | 0000   |           |        |        |        |               |

| DMA6CNT   | 03D2 | _      | _                    | _      | _      | _      | _      |        |                      |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMA7CON   | 03D4 | CHEN   | SIZE                 | DIR    | HALF   | NULLW  | -      |        | _                    | _         | _      | AMOD   | E<1:0> | —         | _      | MODE   | <1:0>  | 0000          |

| DMA7REQ   | 03D6 | FORCE  |                      | _      | _      | _      | -      |        | _                    | -         |        |        | I      | RQSEL<6:0 | >      |        |        | 0000          |

| DMA7STA   | 03D8 |        |                      | •      | •      | •      |        |        | S                    | TA<15:0>  | •      |        |        |           |        |        |        | 0000          |

| DMA7STB   | 03DA |        |                      |        |        |        |        |        | S                    | TB<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7PAD   | 03DC |        |                      |        |        |        |        |        | P                    | AD<15:0>  |        |        |        |           |        |        |        | 0000          |

| DMA7CNT   | 03DE | _      | —                    | —      | —      | _      | —      |        |                      |           |        | CNT    | <9:0>  |           |        |        |        | 0000          |

| DMACS0    | 03E0 | PWCOL7 | PWCOL6               | PWCOL5 | PWCOL4 | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0               | XWCOL7    | XWCOL6 | XWCOL5 | XWCOL4 | XWCOL3    | XWCOL2 | XWCOL1 | XWCOL0 | 0000          |

| DMACS1    | 03E2 | _      | _                    | _      | _      |        | LSTCH  | 1<3:0> |                      | PPST7     | PPST6  | PPST5  | PPST4  | PPST3     | PPST2  | PPST1  | PPST0  | 0000          |

| DSADR     | 03E4 |        |                      |        |        | •      |        |        | DS                   | ADR<15:0> | •      | 1      |        |           | 1      |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

PIC24HJXXXGPX06/X08/X10

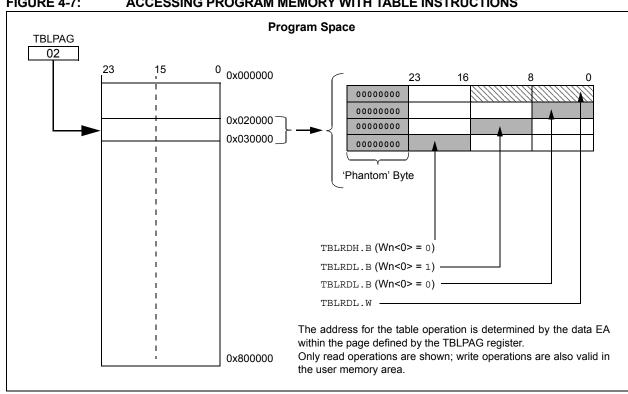

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE **INSTRUCTIONS**

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it 1. maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

2. TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### FIGURE 4-7: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

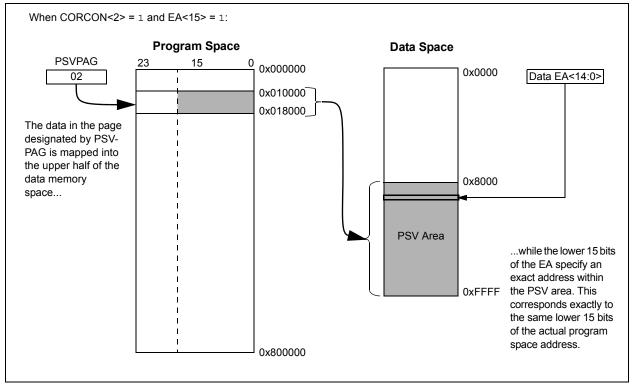

#### 4.4.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-8), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

### FIGURE 4-8: PROGRAM SPACE VISIBILITY OPERATION

| FIGURE 7-1: | PIC24HJXXXGPX06/X08/X10 INTERRUPT VECTOR TABLE |

|-------------|------------------------------------------------|

|             |                                                |

|                                   |                                          | ]              |                                                        |

|-----------------------------------|------------------------------------------|----------------|--------------------------------------------------------|

|                                   | Reset – GOTO Instruction                 | 0x000000       |                                                        |

|                                   | Reset – GOTO Address                     | 0x000002       |                                                        |

|                                   | Reserved                                 | 0x000004       |                                                        |

|                                   | Oscillator Fail Trap Vector              | -              |                                                        |

|                                   | Address Error Trap Vector                | -              |                                                        |

|                                   | Stack Error Trap Vector                  | -              |                                                        |

|                                   | Math Error Trap Vector                   | -              |                                                        |

|                                   | DMA Error Trap Vector                    | -              |                                                        |

|                                   | Reserved                                 | -              |                                                        |

|                                   | Reserved                                 |                | 1                                                      |

|                                   | Interrupt Vector 0                       | 0x000014       |                                                        |

|                                   | Interrupt Vector 1                       | -              |                                                        |

|                                   | ~                                        | -              |                                                        |

|                                   | ~                                        | -              |                                                        |

|                                   | -<br>Interrupt Vector 52                 | 0x00007C       |                                                        |

|                                   | Interrupt Vector 52                      | 0x00007C       | Interrupt Vector Table (IVT) <sup>(1)</sup>            |

| ≥                                 | Interrupt Vector 54                      | 0x00007L       |                                                        |

| orit                              |                                          | 0x000080       |                                                        |

| Pri                               | ~                                        |                |                                                        |

| fer                               | ~                                        |                |                                                        |

| Ö                                 | Interrupt Vector 116                     | 0x0000FC       |                                                        |

| Decreasing Natural Order Priority | Interrupt Vector 117                     | 0x0000FE       | 1                                                      |

| atur                              | Reserved                                 | 0x000100       |                                                        |

| N N                               | Reserved                                 | 0x000102       |                                                        |

| ing                               | Reserved                                 |                |                                                        |

| sas                               | Oscillator Fail Trap Vector              |                |                                                        |

| cre                               | Address Error Trap Vector                |                |                                                        |

| De                                | Stack Error Trap Vector                  |                |                                                        |

|                                   | Math Error Trap Vector                   |                |                                                        |

|                                   | DMA Error Trap Vector                    |                |                                                        |

|                                   | Reserved                                 |                |                                                        |

|                                   | Reserved                                 |                |                                                        |

|                                   | Interrupt Vector 0                       | 0x000114       |                                                        |

|                                   | Interrupt Vector 1                       |                |                                                        |

|                                   | ~                                        |                |                                                        |

|                                   | ~                                        |                |                                                        |

|                                   | ~                                        |                | Alternate Interrupt Vector Table (AIVT) <sup>(1)</sup> |

|                                   | Interrupt Vector 52                      | 0x00017C       |                                                        |

|                                   | Interrupt Vector 53                      | 0x00017E       |                                                        |

|                                   | Interrupt Vector 54                      | 0x000180       |                                                        |

|                                   | ~                                        | -              |                                                        |

|                                   | ~                                        | -              |                                                        |

|                                   |                                          |                |                                                        |

|                                   | Interrupt Vector 116                     |                |                                                        |

| *                                 | Interrupt Vector 117                     | 0x0001FE       |                                                        |

| •                                 | Start of Code                            | 0x000200       |                                                        |

|                                   |                                          |                |                                                        |

|                                   |                                          |                |                                                        |

| Note                              | 1: See Table 7-1 for the list of impleme | nted interrupt | vectors.                                               |

|                                   |                                          |                |                                                        |

|                                   |                                          |                |                                                        |

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IF:</b> Output Compare Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IF:</b> Input Capture Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred  |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                     |

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit                               |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Enable bit                                                   |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0           | R/W-0           | R/W-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0            |

|-----------------|-----------------|-----------------------------------|----------------|------------------|------------------|-----------------|------------------|

| U2TXIE          | U2RXIE          | INT2IE                            | T5IE           | T4IE             | OC4IE            | OC3IE           | DMA2IE           |

| bit 15          |                 |                                   |                |                  |                  |                 | bit 8            |

|                 | DAMA            | <b>DMU</b> O                      | <b>D</b> 444 0 | <b>DMUO</b>      |                  | DAVA            | DAMO             |

| R/W-0           | R/W-0           | R/W-0                             | R/W-0          | R/W-0            | U-0              | R/W-0           | R/W-0            |

| IC8IE<br>bit 7  | IC7IE           | AD2IE                             | INT1IE         | CNIE             |                  | MI2C1IE         | SI2C1IE<br>bit 0 |

|                 |                 |                                   |                |                  |                  |                 | bit 0            |

| Legend:         |                 |                                   |                |                  |                  |                 |                  |

| R = Readable    | bit             | W = Writable                      | bit            | U = Unimpler     | mented bit, read | d as '0'        |                  |

| -n = Value at F | POR             | '1' = Bit is set                  |                | '0' = Bit is cle | ared             | x = Bit is unkr | iown             |

|                 |                 |                                   |                |                  |                  |                 |                  |

| bit 15          |                 | RT2 Transmitte                    | -              | able bit         |                  |                 |                  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |                  |

| bit 14          |                 | RT2 Receiver li                   |                | le hit           |                  |                 |                  |

|                 |                 | request enable                    | •              |                  |                  |                 |                  |

|                 | 0 = Interrupt r | request not ena                   | abled          |                  |                  |                 |                  |

| bit 13          |                 | rnal Interrupt 2                  |                |                  |                  |                 |                  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |                  |

| bit 12          | •               | Interrupt Enab                    |                |                  |                  |                 |                  |

|                 |                 | request enable                    |                |                  |                  |                 |                  |

|                 | 0 = Interrupt r | request not ena                   | abled          |                  |                  |                 |                  |

| bit 11          |                 | Interrupt Enab                    |                |                  |                  |                 |                  |

|                 | •               | request enable<br>request not ena |                |                  |                  |                 |                  |

| bit 10          | -               | ut Compare Ch                     |                | upt Enable bit   |                  |                 |                  |

|                 | •               | request enable                    |                |                  |                  |                 |                  |

|                 | 0 = Interrupt r | request not ena                   | abled          |                  |                  |                 |                  |

| bit 9           |                 | ut Compare Ch                     |                | upt Enable bit   |                  |                 |                  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |                  |

| bit 8           |                 | A Channel 2 D                     |                | Complete Interr  | unt Enable hit   |                 |                  |

| bit 0           |                 | request enable                    |                |                  |                  |                 |                  |

|                 |                 | request not ena                   |                |                  |                  |                 |                  |

| bit 7           | IC8IE: Input C  | Capture Chann                     | el 8 Interrupt | Enable bit       |                  |                 |                  |

|                 |                 | request enable<br>request not ena |                |                  |                  |                 |                  |

| bit 6           |                 | Capture Chann                     |                | Enable bit       |                  |                 |                  |

|                 | -               | request enable                    | -              |                  |                  |                 |                  |

|                 |                 | request not ena                   |                |                  |                  |                 |                  |

| bit 5           | AD2IE: ADC2     | 2 Conversion C                    | omplete Inter  | rupt Enable bit  |                  |                 |                  |

|                 | •               | request enable                    |                |                  |                  |                 |                  |

| hit 4           | -               | request not ena                   |                |                  |                  |                 |                  |

| bit 4           | 1 = Interrupt r | rnal Interrupt 1                  |                |                  |                  |                 |                  |

|                 |                 | naniaet anabia                    | n              |                  |                  |                 |                  |

# 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, PIC24HJXXXGPX06/X08/X10 devices have a safe-guard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 21.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

#### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70227) in the "PIC24H Family Reference Manual" for details.

# 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

If an oscillator failure occurs, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

# 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 10. "I/O Ports" (DS70230), which is available from the Microchip website (www.microchip.com).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

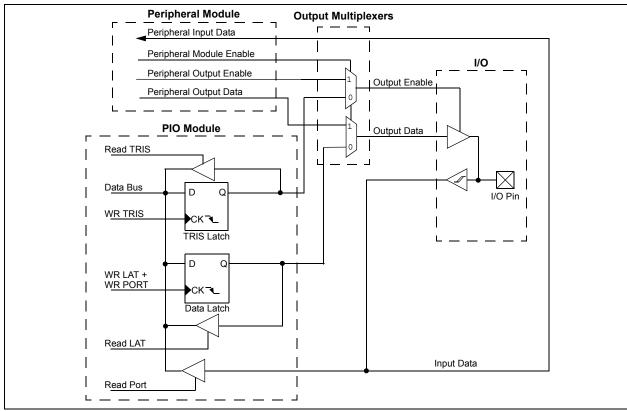

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

**Note:** The voltage on a digital input pin can be between -0.3V to 5.6V.

### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

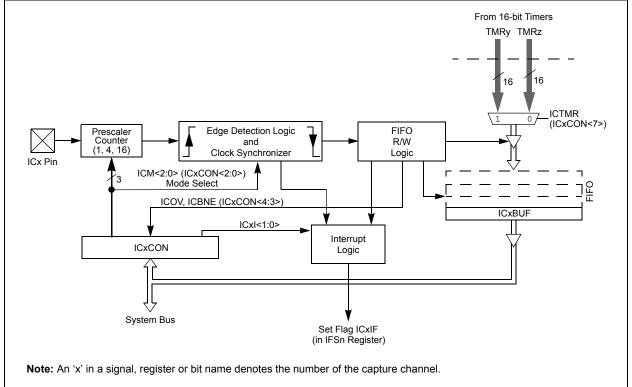

## 14.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 12. *"Input Capture"* (DS70248), which is available from the Microchip website (www.microchip.com).

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The PIC24HJXXXGPX06/X08/X10 devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes

Capture timer value on every falling edge of

input at ICx pin

- -Capture timer value on every rising edge of input at ICx pin

- 2. Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes

- -Capture timer value on every 4th rising edge of input at ICx pin

- -Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

**Note:** Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to 1 (ICI<1:0> = 00).

| R/W-0          | R/W-0                                                                                                                                                                                                                                                                                                          | R/W-0                                                    | U-0         | U-0               | U-0             | U-0                | U-0   |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------|-------------------|-----------------|--------------------|-------|--|--|--|--|

| FRMEN          | SPIFSD                                                                                                                                                                                                                                                                                                         | FRMPOL                                                   | _           | —                 | —               | —                  | —     |  |  |  |  |

| bit 15         |                                                                                                                                                                                                                                                                                                                |                                                          |             |                   |                 |                    | bit 8 |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                |                                                          |             |                   |                 |                    |       |  |  |  |  |

| U-0            | U-0                                                                                                                                                                                                                                                                                                            | U-0                                                      | U-0         | U-0               | U-0             | R/W-0              | U-0   |  |  |  |  |

| —              | —                                                                                                                                                                                                                                                                                                              |                                                          | _           | —                 | —               | FRMDLY             | —     |  |  |  |  |

| bit 7          |                                                                                                                                                                                                                                                                                                                |                                                          |             |                   |                 |                    | bit 0 |  |  |  |  |

|                |                                                                                                                                                                                                                                                                                                                |                                                          |             |                   |                 |                    |       |  |  |  |  |

| Legend:        |                                                                                                                                                                                                                                                                                                                |                                                          |             |                   |                 |                    |       |  |  |  |  |

| R = Readabl    | e bit                                                                                                                                                                                                                                                                                                          | W = Writable I                                           | oit         | U = Unimplen      | nented bit, rea | ad as '0'          |       |  |  |  |  |

| -n = Value at  | POR                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                         |             | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |  |  |  |

| bit 14         | FRMEN: Framed SPIx Support bit <ol> <li>Framed SPIx support enabled (SSx pin used as frame sync pulse input/output)</li> <li>Framed SPIx support disabled</li> <li>SPIFSD: Frame Sync Pulse Direction Control bit</li> <li>Frame sync pulse input (slave)</li> <li>Frame sync pulse output (master)</li> </ol> |                                                          |             |                   |                 |                    |       |  |  |  |  |

| bit 13         | 1 = Frame sy                                                                                                                                                                                                                                                                                                   | ame Sync Pulse<br>nc pulse is activ<br>nc pulse is activ | ve-high     |                   |                 |                    |       |  |  |  |  |

| bit 12-2       | Unimplemen                                                                                                                                                                                                                                                                                                     | ted: Read as 'o                                          | )'          |                   |                 |                    |       |  |  |  |  |

| bit 1<br>bit 0 | <ul> <li>FRMDLY: Frame Sync Pulse Edge Select bit</li> <li>1 = Frame sync pulse coincides with first bit clock</li> <li>0 = Frame sync pulse precedes first bit clock</li> <li>Unimplemented: Read as '0'</li> <li>This bit must not be set to '1' by the user application.</li> </ul>                         |                                                          |             |                   |                 |                    |       |  |  |  |  |

|                | i his dit must                                                                                                                                                                                                                                                                                                 | not be set to '1'                                        | by the user | application.      |                 |                    |       |  |  |  |  |

#### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

NOTES:

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                      | R/W-0                             | R/W-0                                                                                                                     | R/W-0                           | U-0               | R/W-0                  | R/W-0           |

|-----------------------|--------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------------|-----------------|

| UARTEN <sup>(1)</sup> |                          | USIDL                             | IREN <sup>(2)</sup>                                                                                                       | RTSMD                           |                   | UEN                    | <1:0>           |

| bit 15                |                          |                                   |                                                                                                                           |                                 |                   |                        | bit 8           |

|                       |                          |                                   |                                                                                                                           |                                 |                   |                        |                 |

| R/W-0 HC              | R/W-0                    | R/W-0 HC                          | R/W-0                                                                                                                     | R/W-0                           | R/W-0             | R/W-0                  | R/W-0           |

| WAKE                  | LPBACK                   | ABAUD                             | URXINV                                                                                                                    | BRGH                            | PDSE              | _<1:0>                 | STSEL           |

| bit 7                 |                          |                                   |                                                                                                                           |                                 |                   |                        | bit C           |

| Legend:               |                          | HC = Hardwa                       | ro cloared                                                                                                                |                                 |                   |                        |                 |

| R = Readable          | hit                      | W = Writable                      |                                                                                                                           | LI – Unimplo                    | mented bit, read  |                        |                 |

|                       |                          |                                   |                                                                                                                           | $0^{\circ} = \text{Bit is cle}$ |                   |                        |                 |

| -n = Value at F       | 'UR                      | '1' = Bit is set                  |                                                                                                                           |                                 | ared              | x = Bit is unkr        | IOWN            |

| bit 15                | UARTEN: UA               | RTx Enable bi                     | <sub>t</sub> (1)                                                                                                          |                                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           | e controlled by                 | UARTx as defi     | ned by UEN<1:          | :0>             |

|                       |                          |                                   |                                                                                                                           |                                 | y port latches; U |                        |                 |

| bit 14                | Unimplemen               | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |

| bit 13                | USIDL: Stop              | in Idle Mode bi                   | t                                                                                                                         |                                 |                   |                        |                 |

|                       |                          | ue module ope                     |                                                                                                                           |                                 | dle mode          |                        |                 |

| h:: 40                |                          | module opera                      |                                                                                                                           |                                 |                   |                        |                 |

| bit 12                |                          | Encoder and D coder and dec       |                                                                                                                           | e dit'-'                        |                   |                        |                 |

|                       |                          | coder and dec                     |                                                                                                                           |                                 |                   |                        |                 |

| bit 11                | RTSMD: Mod               | le Selection for                  | UxRTS Pin b                                                                                                               | it                              |                   |                        |                 |

|                       |                          | in in Simplex n<br>in in Flow Con |                                                                                                                           |                                 |                   |                        |                 |

| bit 10                | Unimplemen               | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |

| bit 9-8               | <b>UEN&lt;1:0&gt;:</b> ∪ | ARTx Enable I                     | oits                                                                                                                      |                                 |                   |                        |                 |

|                       | 11 = UxTX, U             | xRX and BCL                       | <pins are="" ena<="" td=""><td>bled and used</td><td>I; UxCTS pin co</td><td>ntrolled by port</td><td>latches</td></pins> | bled and used                   | I; UxCTS pin co   | ntrolled by port       | latches         |

|                       |                          | xRX, UxCTS a                      |                                                                                                                           |                                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 | ed; UxCTS pin c   |                        |                 |

|                       | port latcl               |                                   |                                                                                                                           |                                 |                   |                        | lolled by       |

| bit 7                 | WAKE: Wake               | up on Start bi                    | t Detect Durin                                                                                                            | g Sleep Mode                    | Enable bit        |                        |                 |

|                       | 1 = UARTx w              | /ill continue to                  | sample the Ux                                                                                                             | RX pin; interro                 | upt generated o   | n falling edge; l      | oit cleared     |

|                       |                          | are on following                  | g rising edge                                                                                                             |                                 |                   |                        |                 |

|                       | 0 = No wake              | •                                 |                                                                                                                           |                                 |                   |                        |                 |

| bit 6                 |                          | RTx Loopback                      |                                                                                                                           | bit                             |                   |                        |                 |

|                       |                          | oopback mode<br>k mode is disal   |                                                                                                                           |                                 |                   |                        |                 |

| bit 5                 | -                        | -Baud Enable                      |                                                                                                                           |                                 |                   |                        |                 |

|                       | 1 = Enable b             | aud rate meas                     | urement on th                                                                                                             |                                 | er – requires re  | ception of a Sy        | nc field (0x55) |

|                       |                          | ny data; cleared<br>e measuremen  |                                                                                                                           | •                               | on                |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 | amily Referenc    | e <i>Manual"</i> for i | nformation or   |

| en                    | abling the UAR           | T module for re                   | eceive or trans                                                                                                           | smit operation.                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 |                   |                        |                 |

#### 2: This feature is only available for the 16x BRG mode (BRGH = 0).

NOTES:

#### REGISTER 20-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | U-0        | U-0   | U-0   |  |  |

|----------------------------------------------------------------------|-----|------------------|-----|------------------|------------|-------|-------|--|--|

| —                                                                    | —   | —                | —   | —                | _          | —     | —     |  |  |

| bit 15                                                               |     |                  |     |                  |            |       | bit 8 |  |  |

|                                                                      |     |                  |     |                  |            |       |       |  |  |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | R/W-0      | R/W-0 | R/W-0 |  |  |

| —                                                                    | —   | —                | —   | —                | DMABL<2:0> |       |       |  |  |

| bit 7                                                                | •   |                  |     |                  |            |       | bit 0 |  |  |

|                                                                      |     |                  |     |                  |            |       |       |  |  |

| Legend:                                                              |     |                  |     |                  |            |       |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                  |            |       |       |  |  |

| -n = Value at P                                                      | POR | '1' = Bit is set |     | '0' = Bit is cle |            |       |       |  |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

### 24.1 DC Characteristics

| Characteristic | VDD Range  | Temp Range     | Max MIPS                |

|----------------|------------|----------------|-------------------------|

| onaracteristic | (in Volts) | (in °C)        | PIC24HJXXXGPX06/X08/X10 |

|                | 3.0-3.6V   | -40°C to +85°C | 40                      |

#### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

#### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 |    | Min           | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|-----|------|------|

| Industrial Temperature Devices                                                                                                                                                         |    |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   |    | -40           | _   | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA | -40           | _   | +85  | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ |    | Pint + Pi/o   |     | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                      |    | (TJ — ΤΑ)/θJΑ |     |      | W    |

#### TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        |     | Тур | Мах | Unit | Notes |

|-------------------------------------------------------|-----|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja | 40  |     | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θја | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја | 40  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.