Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D-t-!l-                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Details                    |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| perating Temperature       | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp210-i-pf |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506/510/610 DEVICES ONLY **TABLE 4-20:**

| File Name  | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10                        | Bit 9    | Bit 8      | Bit 7                         | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|---------------|--------|-----------|--------|--------|--------|-------------------------------|----------|------------|-------------------------------|----------|--------|-------|-------|--------|--------|--------|---------------|

|            | 0400-<br>041E |        | •         | •      |        |        |                               |          | See defini | tion when V                   | /IN = x  |        |       |       | •      |        |        |               |

| C1BUFPNT1  | 0420          |        | F3BF      | P<3:0> |        |        | F2BI                          | P<3:0>   |            | F1BP<3:0> F0BP<3:0>           |          |        |       |       |        |        | 0000   |               |

| C1BUFPNT2  | 0422          |        | F7BF      | P<3:0> |        |        | F6BI                          | P<3:0>   |            |                               | F5BP     | <3:0>  |       |       | F4BP   | <3:0>  |        | 0000          |

| C1BUFPNT3  | 0424          |        | F11BI     | P<3:0> |        |        | F10B                          | P<3:0>   |            |                               | F9BP     | <3:0>  |       |       | F8BP   | <3:0>  |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B      | P<3:0> |        |        | F14B                          | P<3:0>   |            |                               | F13BF    | P<3:0> |       |       | F12BF  | P<3:0> |        | 0000          |

| C1RXM0SID  | 0430          |        | SID<10:3> |        |        |        |                               | SID<2:0> |            | _                             | MIDE     | _      | EID<  | 7:16> | xxxx   |        |        |               |

| C1RXM0EID  | 0432          |        | EID<15:8> |        |        |        |                               |          |            | EID<                          | 7:0>     |        |       |       | xxxx   |        |        |               |

| C1RXM1SID  | 0434          |        | SID<10:3> |        |        |        | SID<2:0>                      |          | _          | MIDE                          | _        | EID<   | 7:16> | xxxx  |        |        |        |               |

| C1RXM1EID  | 0436          |        | EID<15:8> |        |        |        |                               |          |            | EID<                          | 7:0>     |        |       |       | xxxx   |        |        |               |

| C1RXM2SID  | 0438          |        | SID<10:3> |        |        |        |                               | SID<2:0> |            | _                             | MIDE     | _      | EID<  | 7:16> | xxxx   |        |        |               |

| C1RXM2EID  | 043A          |        | EID<15:8> |        |        |        |                               |          | EID<       | 7:0>                          |          |        |       | xxxx  |        |        |        |               |

| C1RXF0SID  | 0440          |        | SID<10:3> |        |        |        |                               | SID<2:0> |            | _                             | EXIDE    | _      | EID<  | 7:16> | xxxx   |        |        |               |

| C1RXF0EID  | 0442          |        | EID<15:8> |        |        |        | EID<7:0>                      |          |            |                               |          |        |       | xxxx  |        |        |        |               |

| C1RXF1SID  | 0444          |        | SID<10:3> |        |        |        |                               | SID<2:0> |            | _                             | EXIDE    | _      | EID<  | 7:16> | xxxx   |        |        |               |

| C1RXF1EID  | 0446          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF2SID  | 0448          |        | SID<10:3> |        |        |        | SID<2:0>                      |          | _          | EXIDE                         | _        | EID<   | 7:16> | xxxx  |        |        |        |               |

| C1RXF2EID  | 044A          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF3SID  | 044C          |        |           |        | SID<   | :10:3> |                               |          |            |                               | SID<2:0> |        | _     | EXIDE | _      | EID<   | 7:16>  | xxxx          |

| C1RXF3EID  | 044E          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF4SID  | 0450          |        |           |        | SID<   | :10:3> |                               |          |            | SID<2:0> — EXIDE — EID<17:16> |          |        |       |       | 7:16>  | xxxx   |        |               |

| C1RXF4EID  | 0452          |        |           |        | EID<   | :15:8> |                               |          |            | EID<7:0>                      |          |        |       |       |        | xxxx   |        |               |

| C1RXF5SID  | 0454          |        |           |        | SID<   | :10:3> |                               |          |            | SID<2:0> — EXIDE — EID<17:    |          |        |       |       | 7:16>  | xxxx   |        |               |

| C1RXF5EID  | 0456          |        |           |        | EID<   | :15:8> |                               |          |            | EID<7:0>                      |          |        |       |       |        |        | xxxx   |               |

| C1RXF6SID  | 0458          |        |           |        | SID<   | :10:3> |                               |          |            |                               | SID<2:0> |        | _     | EXIDE | _      | EID<   | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF7SID  | 045C          |        |           |        | SID<   | :10:3> |                               |          |            |                               | SID<2:0> |        | _     | EXIDE | _      | EID<   | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF8SID  | 0460          |        |           |        | SID<   | :10:3> |                               |          |            |                               | SID<2:0> |        | _     | EXIDE | _      | EID<   | 7:16>  | xxxx          |

| C1RXF8EID  | 0462          |        |           |        | EID<   | :15:8> |                               |          |            |                               |          |        | EID<  | 7:0>  |        |        |        | xxxx          |

| C1RXF9SID  | 0464          |        | SID<10:3> |        |        |        | SID<2:0>                      |          | _          | EXIDE                         | _        | EID<   | 7:16> | xxxx  |        |        |        |               |

| C1RXF9EID  | 0466          |        | EID<15:8> |        |        |        |                               |          |            | EID<                          | 7:0>     |        |       |       | xxxx   |        |        |               |

| C1RXF10SID | 0468          |        | SID<10:3> |        |        |        | SID<2:0> — EXIDE — EID<17:16> |          |            |                               |          |        | 7:16> | xxxx  |        |        |        |               |

| C1RXF10EID | 046A          |        | EID<15:8> |        |        |        |                               | EID<7:0> |            |                               |          |        |       | xxxx  |        |        |        |               |

| C1RXF11SID | 046C          |        |           |        | SID<   | :10:3> |                               |          |            | SID<2:0> — EXIDE — EID<17:16> |          |        |       |       | 17:16> | xxxx   |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

# 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the page (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Perform a dummy table write operation (TBLWTL) to any address within the page that needs to be erased.

- d) Write 0x55 to NVMKEY.

- e) Write 0xAA to NVMKEY.

- f) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

### **EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE**

```

; Set up NVMCON for block erase operation

MOV

#0x4042, W0

MOV

WO, NVMCON

; Initialize NVMCON

; Init pointer to row to be ERASED

VOM

#tblpage(PROG ADDR), W0

; Initialize PM Page Boundary SFR

WO, TBLPAG

#tbloffset(PROG ADDR), W0

; Initialize in-page EA<15:0> pointer

TBLWTL WO, [WO]

; Set base address of erase block

; Block all interrupts with priority <7

DISI

#5

; for next 5 instructions

MOV

#0x55, W0

WO, NVMKEY

; Write the 55 key

MOV

MOV

#0xAA, W1

MOV

W1, NVMKEY

; Write the AA key

NVMCON, #WR

BSET

: Start the erase sequence

NOP

; Insert two NOPs after the erase

NOP

: command is asserted

```

Note:

A program memory page erase operation is set up by performing a dummy table write (TBLWTL) operation to any address within the page. This methodology is different from the page erase operation on dsPIC30F/33F devices in which the erase page was selected using a dedicated pair of registers (NVMADRU and NVMADR).

### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1 | R/W-0     | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|-----------|-------|-----|-------|------------|-------|

| _      |       | T1IP<2:0> |       | _   |       | OC1IP<2:0> |       |

| bit 15 |       |           |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0       | R/W-0 |

|-------|-------|------------|-------|-----|-------|-------------|-------|

| _     |       | IC1IP<2:0> |       | _   |       | INT0IP<2:0> |       |

| bit 7 |       |            |       |     |       |             | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 T1IP<2:0>: Timer1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

. . .

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 **INT0IP<2:0>:** External Interrupt 0 Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

### REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0    | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-------|------------|-------|-----|-------|------------|-------|

| _      |       | OC7IP<2:0> |       | _   |       | OC6IP<2:0> |       |

| bit 15 |       |            |       |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|-------|-------|------------|-------|-----|-------|------------|-------|

| _     |       | OC5IP<2:0> |       | _   |       | IC6IP<2:0> |       |

| bit 7 |       |            |       |     |       |            | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14-12 OC7IP<2:0>: Output Compare Channel 7 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 Unimplemented: Read as '0'

bit 10-8 OC6IP<2:0>: Output Compare Channel 6 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 OC5IP<2:0>: Output Compare Channel 5 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 Unimplemented: Read as '0'

bit 2-0 IC6IP<2:0>: Input Capture Channel 6 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

### REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

bit 1 LPOSCEN: Secondary (LP) Oscillator Enable bit

1 = Enable secondary oscillator0 = Disable secondary oscillator

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Request oscillator switch to selection specified by NOSC<2:0> bits

0 = Oscillator switch is complete

**Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator"** (DS70227) in the *"PIC24H Family Reference Manual"* (available from the Microchip website) for details.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

### REGISTER 13-2: TyCON (T3CON, T5CON, T7CON OR T9CON) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL <sup>(2)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0                     | R/W-0 | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|---------------------------|-------|-----|-----|----------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS<1:0> <sup>(1)</sup> |       | _   | _   | TCS <sup>(1,3)</sup> | _     |

| bit 7 |                      |                           |       |     |     |                      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timery On bit<sup>(1)</sup>

1 = Starts 16-bit Timery

0 = Stops 16-bit Timery

bit 14 Unimplemented: Read as '0'

bit 13 **TSIDL:** Stop in Idle Mode bit<sup>(2)</sup>

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 **TGATE**: Timery Gated Time Accumulation Enable bit<sup>(1)</sup>

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation enabled

0 = Gated time accumulation disabled

bit 5-4 TCKPS<1:0>: Timer3 Input Clock Prescale Select bits<sup>(1)</sup>

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timery Clock Source Select bit (1,3)

1 = External clock from pin TyCK (on the rising edge)

0 = Internal clock (FCY)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When 32-bit operation is enabled (T2CON<3> = 1), these bits have no effect on Timery operation; all timer functions are set through T2CON.

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available for all timers. Refer to the "Pin Diagrams" section for the available pins.

### REGISTER 15-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| _      | _   | OCSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|-------|-----|-----|---------|--------|-------|----------|-------|

| _     | _   | _   | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7 |     |     |         |        |       |          | bit 0 |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13 OCSIDL: Stop Output Compare in Idle Mode Control bit

1 = Output Compare x halts in CPU Idle mode

0 = Output Compare x continues to operate in CPU Idle mode

bit 12-5 Unimplemented: Read as '0'

bit 4 OCFLT: PWM Fault Condition Status bit

1 = PWM Fault condition has occurred (cleared in hardware only)

0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111)

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for Compare x

0 = Timer2 is the clock source for Compare x

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx, Fault pin enabled

110 = PWM mode on OCx, Fault pin disabled

101 = Initialize OCx pin low, generate continuous output pulses on OCx pin

100 = Initialize OCx pin low, generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high, compare event forces OCx pin low

001 = Initialize OCx pin low, compare event forces OCx pin high

000 = Output compare channel is disabled

### REGISTER 16-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|-----|-----|-----|-----|-------|

| SPIEN  | _   | SPISIDL | _   | _   | _   | _   | _     |

| bit 15 |     |         |     |     |     |     | bit 8 |

| U-0   | R/C-0  | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    |

|-------|--------|-----|-----|-----|-----|--------|--------|

| _     | SPIROV | _   | _   | _   | _   | SPITBF | SPIRBF |

| bit 7 |        |     |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                                    |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15 SPIEN: SPIx Enable bit

1 = Enables module and configures SCKx, SDOx, SDIx and SSx as serial port pins

0 = Disables module

bit 14 **Unimplemented:** Read as '0' bit 13 **SPISIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 5-2

bit 6 SPIROV: Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded. The user software has not read the

previous data in the SPIxBUF register 0 = No overflow has occurred

Unimplemented: Read as '0'

bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit not yet started, SPIxTXB is full0 = Transmit started, SPIxTXB is empty

Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.

Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive complete, SPIxRXB is full

0 = Receive is not complete, SPIxRXB is empty

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.

Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.

NOTES:

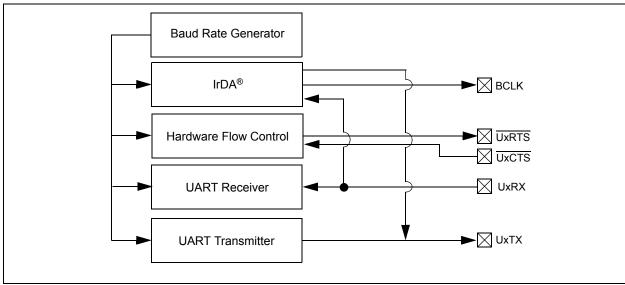

# 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 17. "UART" (DS70232), which is available from the

Microchip website (www.microchip.com).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJXXXGPX06/X08/X10 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins and also includes an IrDA® encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 1 Mbps to 15 bps at 16x mode at 40 MIPS

- Baud rates ranging from 4 Mbps to 61 bps at 4x mode at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- · Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- · A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of the key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

### FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

- **Note 1:** Both UART1 and UART2 can trigger a DMA data transfer. If U1TX, U1RX, U2TX or U2RX is selected as a DMA IRQ source, a DMA transfer occurs when the U1TXIF, U1RXIF, U2TXIF or U2RXIF bit gets set as a result of a UART1 or UART2 transmission or reception.

- 2: If DMA transfers are required, the UART TX/RX FIFO buffer must be set to a size of 1 byte/word (i.e., UTXISEL<1:0> = 00 and URXISEL<1:0> = 00).

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) 1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect 0 = Address Detect mode disabled bit 4 RIDLE: Receiver Idle bit (read-only) 1 = Receiver is Idle 0 = Receiver is active bit 3 **PERR:** Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected bit 2 **FERR:** Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit (read/clear only) 1 = Receive buffer has overflowed  $0 = \text{Receive buffer has not overflowed. Clearing a previously set OERR bit } (1 \rightarrow 0 \text{ transition}) \text{ will reset}$ the receiver buffer and the UxRSR to the empty state bit 0 URXDA: Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

- Note 1: Refer to Section 17. "UART" (DS70232) in the "PIC24H Family Reference Manual" for information on enabling the UART module for transmit operation.

### REGISTER 19-9: CiCFG1: ECAN™ MODULE BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|----------|-------|-------|-------|-------|-------|

| SJW   | <1:0> | BRP<5:0> |       |       |       |       |       |

| bit 7 |       | •        |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-6 **SJW<1:0>:** Synchronization Jump Width bits

11 = Length is 4 x TQ 10 = Length is 3 x TQ 01 = Length is 2 x TQ 00 = Length is 1 x TQ

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

11 1111 = TQ = 2 x 64 x 1/FCAN

•

00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN 00 0000 = TQ = 2 x 1 x 1/FCAN

### REGISTER 20-2: ADxCON2: ADCx CONTROL REGISTER 2 (where x = 1 or 2)

| R/W-0     | R/W-0 | R/W-0 | U-0 | U-0   | R/W-0 | R/W-0  | R/W-0 |

|-----------|-------|-------|-----|-------|-------|--------|-------|

| VCFG<2:0> |       | _     | _   | CSCNA | CHPS  | S<1:0> |       |

| bit 15    |       |       |     |       |       |        | bit 8 |

| R-0   | U-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----------|-------|-------|-------|-------|

| BUFS  | _   |       | SMPI<3:0> |       |       |       | ALTS  |

| bit 7 |     |       |           |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-13 VCFG<2:0>: Converter Voltage Reference Configuration bits

|     | VREF+          | VREF-          |

|-----|----------------|----------------|

| 000 | AVDD           | AVss           |

| 001 | External VREF+ | AVss           |

| 010 | AVDD           | External VREF- |

| 011 | External VREF+ | External VREF- |

| 1xx | AVDD           | AVss           |

bit 12-11 Unimplemented: Read as '0'

bit 10 CSCNA: Scan Input Selections for CH0+ during Sample A bit

1 = Scan inputs

0 = Do not scan inputs

bit 9-8 CHPS<1:0>: Selects Channels Utilized bits

When AD12B = 1, CHPS<1:0> is: U-0, Unimplemented, Read as '0'

1x = Converts CH0, CH1, CH2 and CH3

01 = Converts CH0 and CH1

00 = Converts CH0

bit 7 **BUFS:** Buffer Fill Status bit (only valid when BUFM = 1)

1 = ADC is currently filling second half of buffer, user should access data in first half

0 = ADC is currently filling first half of buffer, user should access data in second half

bit 6 Unimplemented: Read as '0'

bit 5-2 SMPI<3:0>: Selects Increment Rate for DMA Addresses bits or number of sample/conversion operations per interrupt

1111 = Increments the DMA address or generates interrupt after completion of every 16th sample/conversion operation

1110 = Increments the DMA address or generates interrupt after completion of every 15th sample/conversion operation

0001 = Increments the DMA address or generates interrupt after completion of every 2nd sample/conversion operation

0000 = Increments the DMA address or generates interrupt after completion of every sample/conversion operation

bit 1 BUFM: Buffer Fill Mode Select bit

1 = Starts filling first half of buffer on first interrupt and second half of buffer on next interrupt

0 = Always starts filling buffer from the beginning

bit 0 **ALTS:** Alternate Input Sample Mode Select bit

1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

0 = Always uses channel input selects for Sample A

### 24.1 DC Characteristics

### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | V <sub>DD</sub> Range | Temp Range     | Max MIPS                |

|----------------|-----------------------|----------------|-------------------------|

| Characteristic | (in Volts)            | (in °C)        | PIC24HJXXXGPX06/X08/X10 |

|                | 3.0-3.6V              | -40°C to +85°C | 40                      |

### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                       | Symbol | Min         | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| Industrial Temperature Devices                                                                                                                                                               |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                         | TJ     | -40         | _           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                          | TA     | -40         | _           | +85  | °C   |

| Power Dissipation: Internal chip power dissipation: $PINT = VDD \ x \ (IDD - \Sigma \ IOH)$ I/O Pin Power Dissipation: $I/O = \Sigma \ (\{VDD - VOH\} \ x \ IOH) + \Sigma \ (VOL \ x \ IOL)$ | Pb     | PINT + PI/O |             | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                            | PDMAX  | (           | ΓJ — ΤΑ)/θJ | A    | W    |

### **TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS**

| Characteristic                                        | Symbol      | Тур | Max | Unit | Notes |

|-------------------------------------------------------|-------------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | hetaJA      | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | $\theta$ JA | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | $\theta$ JA | 40  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

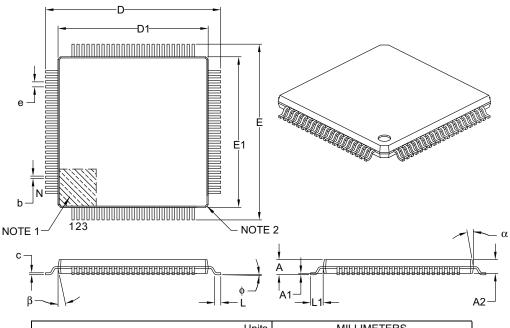

### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     | MILLIMETERS |           |      |  |

|--------------------------|-----------|-------------|-----------|------|--|

| Dimensi                  | on Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          | N         |             | 100       |      |  |

| Lead Pitch               | е         |             | 0.40 BSC  |      |  |

| Overall Height           | Α         | _           | _         | 1.20 |  |

| Molded Package Thickness | A2        | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1        | 0.05        | _         | 0.15 |  |

| Foot Length              | L         | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1        |             | 1.00 REF  |      |  |

| Foot Angle               | ф         | 0°          | 3.5°      | 7°   |  |

| Overall Width            | Е         |             | 14.00 BSC |      |  |

| Overall Length           | D         |             | 14.00 BSC |      |  |

| Molded Package Width     | E1        |             | 12.00 BSC |      |  |

| Molded Package Length    | D1        |             | 12.00 BSC |      |  |

| Lead Thickness           | С         | 0.09        | _         | 0.20 |  |

| Lead Width               | b         | 0.13        | 0.18      | 0.23 |  |

| Mold Draft Angle Top     | α         | 11°         | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β         | 11°         | 12°       | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- $2. \ \ Chamfers \ at \ corners \ are \ optional; \ size \ may \ vary.$

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

NOTES:

### APPENDIX A: REVISION HISTORY

### Revision A (February 2006)

· Initial release of this document

### Revision B (March 2006)

- Updated the Configuration Bits Description table (Table 20-1)

- · Updated registers and register maps

- Updated Section 15.0 "Serial Peripheral Interface (SPI)"

- Updated Section 23.0 "Electrical Characteristics"

- · Updated pinout diagrams

- Additional minor corrections throughout document text

### Revision C (May 2006)

- Updated Section 23.0 "Electrical Characteristics"

- Updated the Configuration Bits Description table (Table 20-1)

- Additional minor corrections throughout document text

### Revision D (July 2006)

- Added FBS and FSS Device Configuration registers (see Table 20-1) and corresponding bit field descriptions (see Table 20-2). These added registers replaced the former RESERVED1 and RESERVED2 registers.

- Added INTTREG Interrupt Control and Status register. (See Section 6.3 "Interrupt Control and Status Registers". See also Register 6-33.)

- Added Core Registers BSRAM and SSRAM (see Section 3.2.7 "Data Ram Protection Feature")

- Clarified Fail-Safe Clock Monitor operation (see Section 8.3 "Fail-Safe Clock Monitor (FSCM)")

- Updated COSC<2:0> and NOSC<2:0> bit configurations in OSCCON register (see Register 8-1)

- Updated CLKDIV register bit configurations (see Register 8-2)

- Added Word Write Cycle Time parameter (Tww) to Program Flash Memory (see Table 23-12)

- Noted exceptions to Absolute Maximum Ratings on I/O pin output current (see Section 23.0 "Electrical Characteristics")

- Added ADC2 Event Trigger for Timer4/5 (Section 12.0 "Timer2/3, Timer4/5, Timer6/7 and Timer8/9")

- Corrected mislabeled I2COV bit in I2CxSTAT register (see Register 16-2)

- Removed AD26a, AD27a, AD28a, AD26b, AD27b and AD28b from Table 23-34 (ADC Module)

- Revised Table 23-36 (AD63)

### Revision F (June 2007)

- Changed document name from PIC24H Family Data Sheet to PIC24HJXXXGPX06/X08/X10 Data Sheet, which resulted in revision change from E to F prior to publication.

- Updated Section 23.0 "Electrical Characteristics"

- Additional minor corrections throughout document text

### **INDEX**

| A                                         |     | D                                               |       |

|-------------------------------------------|-----|-------------------------------------------------|-------|

| AC Characteristics                        | 242 | Data Address Space                              | 27    |

| Internal RC Accuracy                      | 244 | Alignment                                       |       |

| Load Conditions                           |     | Memory Map for PIC24HJXXXGPX06/X08/X10 De       |       |

| ADC Module                                |     | with 16 KB RAM                                  |       |

| ADC1 Register Map                         | 38  | Memory Map for PIC24HJXXXGPX06/X08/X10 De       |       |

| ADC2 Register Map                         |     | with 8 KB RAM                                   |       |

| Alternate Interrupt Vector Table (AIVT)   |     | Near Data Space                                 |       |

| Analog-to-Digital Converter               |     | Software Stack                                  |       |

| DMA                                       |     | Width                                           |       |

| Initialization                            |     | DC Characteristics                              |       |

| Key Features                              |     | I/O Pin Input Specifications                    |       |

| Arithmetic Logic Unit (ALU)               |     | I/O Pin Output Specifications                   |       |

| Assembler                                 |     | Idle Current (IDOZE)                            |       |

| MPASM Assembler                           | 230 | Idle Current (IDLE)                             |       |

| Automatic Clock Stretch                   |     | Operating Current (IDD)                         |       |

| ratoriatio ciock di ctori                 |     | Power-Down Current (IPD)                        |       |

| В                                         |     | Program Memory                                  |       |

| Block Diagrams                            |     | Temperature and Voltage Specifications          |       |

| 16-bit Timer1 Module                      | 141 | Development Support                             |       |

| ADC1 Module                               |     | DMA Module                                      | 220   |

| Connections for On-Chip Voltage Regulator |     | DMA Register Map                                | 30    |

| ECAN Module                               |     | DMAC Registers                                  |       |

| Input Capture                             |     | DMAXCNT                                         |       |

| Output Compare                            |     | DMAxCON                                         |       |

| PIC24H                                    |     | DMAXPAD                                         |       |

| PIC24H CPU Core                           |     |                                                 |       |

| PIC24H Oscillator System Diagram          |     | DMAxREQ<br>DMAxSTA                              |       |

| PIC24H PLL                                |     |                                                 |       |

| Reset System                              |     | DMAxSTB                                         | 112   |

| Shared Port Structure                     |     | E                                               |       |

| SPI                                       |     | ECAN Module                                     |       |

| Timer2 (16-bit)                           |     | CiFMSKSEL2 register                             | 103   |

| Timer2 (10-bit)                           |     | ECAN1 Register Map (C1CTRL1.WIN = 0 or 1)       |       |

| UART                                      |     | ECAN1 Register Map (C1CTRL1.WIN = 0 of 1)       |       |

| Watchdog Timer (WDT)                      |     | ECAN1 Register Map (C1CTRL1.WIN = 1)            |       |

| Wateridog Timer (WDT)                     | 219 | ECAN2 Register Map (C2CTRL1.WIN = 0 or 1)       |       |

| C                                         |     | ECAN2 Register Map (C2CTRL1.WIN = 0 of 1)       |       |

| C Compilers                               |     | ECAN2 Register Map (C2CTRL1.WIN = 1)            |       |

| MPLAB C18                                 | 230 | Frame Types                                     |       |

| MPLAB C30                                 |     | Modes of Operation                              |       |

| Clock Switching                           |     | Overview                                        |       |

| Enabling                                  |     | ECAN Registers                                  | 170   |

| Sequence                                  |     | Filter 15-8 Mask Selection Register (CiFMSKSEL2 | 1 103 |

| Code Examples                             |     | Electrical Characteristics                      |       |

| Erasing a Program Memory Page             | 60  | AC                                              |       |

| Initiating a Programming Sequence         |     | Enhanced CAN Module                             |       |

| Loading Write Buffers                     |     | Equations                                       | 170   |

| Port Write/Read                           |     | Device Operating Frequency                      | 122   |

| PWRSAV Instruction Syntax                 |     | FOSC Calculation                                |       |

| Code Protection                           |     | XT with PLL Mode Example                        |       |

| Configuration Bits                        | •   | Errata                                          |       |

| Description (Table)                       |     | Litala                                          | 10    |

| Configuration Register Map                |     | F                                               |       |

| Configuring Analog Port Pins              |     | Flash Program Memory                            | 57    |

| CPU                                       | 170 | Control Registers                               |       |

| Control Register                          | 21  | Operations                                      |       |

| CPU Clocking System                       |     | Programming Algorithm                           |       |

| PLL Configuration                         |     | RTSP Operation                                  |       |

| Selection                                 |     | Table Instructions                              |       |

| Sources                                   |     | Flexible Configuration                          |       |

| Customer Change Notification Service      |     | FSCM                                            | 213   |

| Customer Support                          |     | Delay for Crystal and PLL Clock Sources         | 66    |

| Casternor Cupport                         | 201 | Device Resets                                   |       |

|                                           |     | DOTIOO 1 100010                                 | 00    |

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511

Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-572-9526 Fax: 886-3-572-6459

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828

Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

02/04/09