Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                           |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

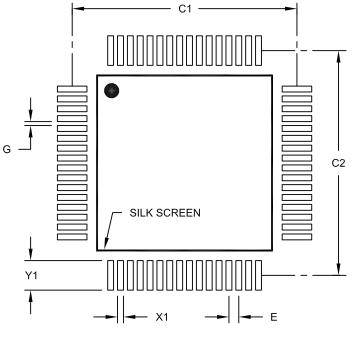

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp210t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC24HJXXXGPX06/X08/X10

#### SR: CPU STATUS REGISTER **REGISTER 3-1:** U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 DC bit 15 bit 8 R/W-0<sup>(1)</sup> R/W-0<sup>(2)</sup> R/W-0<sup>(2)</sup> R-0 R/W-0 R/W-0 R/W-0 R/W-0 IPL<2:0>(2) RA Ν OV Ζ С bit 7 bit 0 Leaend: C = Clear only bit U = Unimplemented bit, read as '0' R = Readable bit S = Set only bit W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-9 Unimplemented: Read as '0' bit 8 DC: MCU ALU Half Carry/Borrow bit 1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred 0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup> bit 7-5 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8) bit 4 **RA:** REPEAT Loop Active bit 1 = REPEAT loop in progress 0 = REPEAT loop not in progress bit 3 N: MCU ALU Negative bit 1 = Result was negative 0 = Result was non-negative (zero or positive) bit 2 OV: MCU ALU Overflow bit This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state. 1 = Overflow occurred for signed arithmetic (in this arithmetic operation) 0 = No overflow occurred Z: MCU ALU Zero bit bit 1 1 = An operation which affects the Z bit has set it at some time in the past 0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result) bit 0 C: MCU ALU Carry/Borrow bit 1 = A carry-out from the Most Significant bit (MSb) of the result occurred 0 = No carry-out from the Most Significant bit of the result occurred Note 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

2: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

# TABLE 4-15: ADC1 REGISTER MAP

| File Name               | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3   | Bit 2     | Bit 1    | Bit 0   | All<br>Resets |

|-------------------------|---------------|--------|-----------|--------|---------|--------|-----------|---------|----------|----------|-----------|--------|--------|---------|-----------|----------|---------|---------------|

| ADC1BUF0                | 0300          |        |           |        |         |        |           |         | ADC Data | Buffer 0 |           |        |        |         |           |          |         | xxxx          |

| AD1CON1                 | 0320          | ADON   | _         | ADSIDL | ADDMABM | _      | AD12B     | FOR     | M<1:0>   | :        | SSRC<2:0> | •      | _      | SIMSAM  | ASAM      | SAMP     | DONE    | 0000          |

| AD1CON2                 | 0322          |        | VCFG<2:0> | >      | —       | —      | CSCNA     | CHP     | S<1:0>   | BUFS     |           |        | SMPI   | <3:0>   |           | BUFM     | ALTS    | 0000          |

| AD1CON3                 | 0324          | ADRC   | —         | _      |         | S      | AMC<4:0>  |         |          |          |           |        | ADCS   | \$<7:0> |           |          |         | 0000          |

| AD1CHS123               | 0326          | —      | _         | _      | —       | —      | CH123N    | NB<1:0> | CH123SB  | —        |           | —      |        | —       | CH123     | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0                 | 0328          | CH0NB  | —         | _      |         | CI     | H0SB<4:0> | •       |          | CH0NA    |           | —      |        | (       | CH0SA<4:( | )>       |         | 0000          |

| AD1PCFGH <sup>(1)</sup> | 032A          | PCFG31 | PCFG30    | PCFG29 | PCFG28  | PCFG27 | PCFG26    | PCFG25  | PCFG24   | PCFG23   | PCFG22    | PCFG21 | PCFG20 | PCFG19  | PCFG18    | PCFG17   | PCFG16  | 0000          |

| AD1PCFGL                | 032C          | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10    | PCFG9   | PCFG8    | PCFG7    | PCFG6     | PCFG5  | PCFG4  | PCFG3   | PCFG2     | PCFG1    | PCFG0   | 0000          |

| AD1CSSH <sup>(1)</sup>  | 032E          | CSS31  | CSS30     | CSS29  | CSS28   | CSS27  | CSS26     | CSS25   | CSS24    | CSS23    | CSS22     | CSS21  | CSS20  | CSS19   | CSS18     | CSS17    | CSS16   | 0000          |

| AD1CSSL                 | 0330          | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10     | CSS9    | CSS8     | CSS7     | CSS6      | CSS5   | CSS4   | CSS3    | CSS2      | CSS1     | CSS0    | 0000          |

| AD1CON4                 | 0332          | —      | _         | _      | —       | —      |           |         | —        | —        |           | —      |        | —       |           | DMABL<2: | 0>      | 0000          |

| Reserved                | 0334-<br>033E | —      |           | —      | _       | _      | _         | _       | _        | _        | _         | —      | _      | _       | _         | _        | _       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

#### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr          | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8    | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|---------------|--------|-----------|--------|---------|--------|----------|---------|----------|----------|----------|-------|-------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340          |        |           |        |         |        |          |         | ADC Data | Buffer 0 |          |       |       |        |        |          |         | xxxx          |

| AD2CON1   | 0360          | ADON   | -         | ADSIDL | ADDMABM | _      | AD12B    | FOR     | M<1:0>   | :        | SSRC<2:0 | >     | _     | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362          | ١      | VCFG<2:0> | >      | _       | _      | CSCNA    | CHP     | S<1:0>   | BUFS     | _        |       | SMPI  | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364          | ADRC   | -         | _      |         | S      | AMC<4:0> |         |          |          |          |       | ADC   | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366          | _      | -         | _      | _       | _      | CH123N   | IB<1:0> | CH123SB  | _        | _        | _     | _     | _      | CH123N | IA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368          | CH0NB  | -         | _      | _       |        | CH0S     | B<3:0>  |          | CH0NA    | _        | _     | _     |        | CH0S   | A<3:0>   |         | 0000          |

| Reserved  | 036A          | _      | -         | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _      | _        | _       | 0000          |

| AD2PCFGL  | 036C          | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11 | PCFG10   | PCFG9   | PCFG8    | PCFG7    | PCFG6    | PCFG5 | PCFG4 | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E          | _      |           | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | _      | _        | _       | 0000          |

| AD2CSSL   | 0370          | CSS15  | CSS14     | CSS13  | CSS12   | CSS11  | CSS10    | CSS9    | CSS8     | CSS7     | CSS6     | CSS5  | CSS4  | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372          | _      |           | _      | _       | _      | _        | _       | _        | _        | _        | _     | _     | _      | I      | DMABL<2: | 0>      | 0000          |

| Reserved  | 0374-<br>037E | —      | —         | _      | —       | _      | —        | _       | —        | _        | _        | —     | _     | —      | _      | —        | —       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| IABLE 4-2  | ABLE 4-21: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 OR 1 FOR PIC24HJ256GP610 DEVICES ONLY |         |          |         |         |         |           |          |        |          |          |        |         |           |                   |          |        |               |

|------------|------------------------------------------------------------------------------------------|---------|----------|---------|---------|---------|-----------|----------|--------|----------|----------|--------|---------|-----------|-------------------|----------|--------|---------------|

| File Name  | Addr                                                                                     | Bit 15  | Bit 14   | Bit 13  | Bit 12  | Bit 11  | Bit 10    | Bit 9    | Bit 8  | Bit 7    | Bit 6    | Bit 5  | Bit 4   | Bit 3     | Bit 2             | Bit 1    | Bit 0  | All<br>Resets |

| C2CTRL1    | 0500                                                                                     | _       | _        | CSIDL   | ABAT    | -       | RI        | EQOP<2:0 | >      | OPN      | /ODE<2:0 | >      | —       | CANCAP    | —                 | _        | WIN    | 0480          |

| C2CTRL2    | 0502                                                                                     | _       | _        | _       | _       | _       | _         | _        | _      | _        | _        | _      |         | C         | NCNT<4:0          | )>       |        | 0000          |

| C2VEC      | 0504                                                                                     | _       | _        | _       |         | FI      | LHIT<4:0> |          |        | _        |          |        |         | ICODE<6:0 | )>                |          |        | 0000          |

| C2FCTRL    | 0506                                                                                     | C       | MABS<2:0 | >       | _       | _       | _         | _        | _      | —        | _        | —      |         |           | FSA<4:0>          |          |        | 0000          |

| C2FIFO     | 0508                                                                                     | _       | _        |         |         | FBP<5   | :0>       |          |        | _        | _        |        |         | FNRE      | 3<5:0>            |          |        | 0000          |

| C2INTF     | 050A                                                                                     | _       | _        | TXBO    | TXBP    | RXBP    | TXWAR     | RXWAR    | EWARN  | IVRIF    | WAKIF    | ERRIF  | _       | FIFOIF    | RBOVIF            | RBIF     | TBIF   | 0000          |

| C2INTE     | 050C                                                                                     | _       | _        | _       | _       | _       | _         | _        | _      | IVRIE    | WAKIE    | ERRIE  | _       | FIFOIE    | RBOVIE            | RBIE     | TBIE   | 0000          |

| C2EC       | 050E                                                                                     |         |          |         | TERRCN  | Γ<7:0>  |           |          |        |          |          |        | RERRCI  | NT<7:0>   |                   |          |        | 0000          |

| C2CFG1     | 0510                                                                                     | _       | _        | _       | _       | _       | _         | _        | _      | SJW<1    | 1:0>     |        |         | BRP       | <5:0>             |          |        | 0000          |

| C2CFG2     | 0512                                                                                     | _       | WAKFIL   | _       | _       | _       | SE        | G2PH<2:0 | )>     | SEG2PHTS | SAM      | SI     | EG1PH<2 | :0>       | P                 | RSEG<2:0 | )>     | 0000          |

| C2FEN1     | 0514                                                                                     | FLTEN15 | FLTEN14  | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10   | FLTEN9   | FLTEN8 | FLTEN7   | FLTEN6   | FLTEN5 | FLTEN4  | FLTEN3    | FLTEN2            | FLTEN1   | FLTEN0 | FFFF          |

| C2FMSKSEL1 | 0518                                                                                     | F7MSH   | <1:0>    | F6MSI   | <<1:0>  | F5MSł   | <1:0>     | F4MSI    | <<1:0> | F3MSK<   | <1:0>    | F2MS   | <1:0>   | F1MSI     | <<1:0>            | F0MS     | K<1:0> | 0000          |

| C2FMSKSEL2 | 051A                                                                                     | F15MS   | K<1:0>   | F14MS   | K<1:0>  | F13MS   | K<1:0>    | F12MS    | K<1:0> | F11MSK   | <1:0>    | F10MS  | K<1:0>  | F9MSI     | <b>&lt;</b> <1:0> | F8MS     | K<1:0> | 0000          |

#### TABLE 4-21: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 OR 1 FOR PIC24HJ256GP610 DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-22: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 FOR PIC24HJ256GP610 DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14      | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9   | Bit 8       | Bit 7     | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-------------|-------------|------------|------------|---------|---------|-------------|-----------|-------------|-------------|------------|------------|---------|---------|---------|---------------|

|           | 0500-<br>051E |         |             |             |            |            |         | See     | edefinition | when WIN  | = x         |             |            |            |         |         |         |               |

| C2RXFUL1  | 0520          | RXFUL15 | RXFUL14     | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9  | RXFUL8      | RXFUL7    | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C2RXFUL2  | 0522          | RXFUL31 | RXFUL30     | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25 | RXFUL24     | RXFUL23   | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C2RXOVF1  | 0528          | RXOVF15 | RXOVF14     | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF09 | RXOVF08     | RXOVF7    | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C2RXOVF2  | 052A          | RXOVF31 | RXOVF30     | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25 | RXOVF24     | RXOVF23   | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C2TR01CON | 0530          | TXEN1   | TX<br>ABAT1 | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PF   | RI<1:0>     | TXEN0     | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C2TR23CON | 0532          | TXEN3   | TX<br>ABAT3 | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF   | RI<1:0>     | TXEN2     | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C2TR45CON | 0534          | TXEN5   | TX<br>ABAT5 | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF   | 81<1:0>     | TXEN4     | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C2TR67CON | 0536          | TXEN7   | TX<br>ABAT7 | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PF   | RI<1:0>     | TXEN6     | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C2RXD     | 0540          |         |             |             | •          |            |         |         | Recieved    | Data Word |             |             |            |            |         |         |         | xxxx          |

| C2TXD     | 0542          |         |             |             |            |            |         |         | Transmit I  | Data Word |             |             |            |            |         |         |         | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

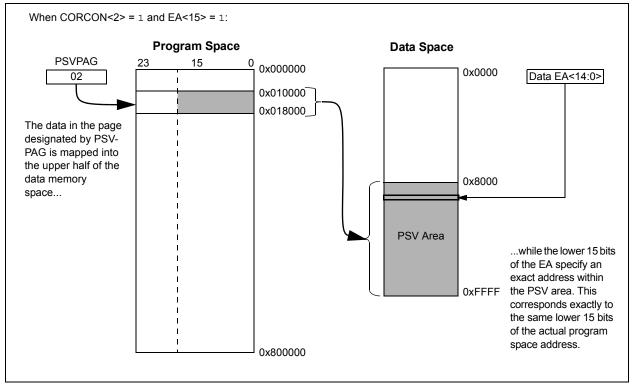

### 4.4.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-8), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

# Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

# FIGURE 4-8: PROGRAM SPACE VISIBILITY OPERATION

# REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit                               |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Enable bit                                                   |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

## REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0                 | U-0             | R/W-0                           | U-0           | U-0              | U-0              | U-0             | R/W-0 |

|---------------------|-----------------|---------------------------------|---------------|------------------|------------------|-----------------|-------|

| _                   | —               | DMA5IE                          | _             | _                | —                | _               | C2IE  |

| bit 15              |                 |                                 |               |                  |                  |                 | bit 8 |

|                     |                 |                                 |               |                  |                  |                 |       |

| R/W-0               | R/W-0           | R/W-0                           | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| C2RXIE              | INT4IE          | INT3IE                          | T9IE          | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |

| bit 7               |                 |                                 |               |                  |                  |                 | bit 0 |

| r                   |                 |                                 |               |                  |                  |                 |       |

| Legend:             |                 |                                 |               |                  |                  |                 |       |

| R = Readable        |                 | W = Writable                    |               | •                | nented bit, read |                 |       |

| -n = Value at F     | POR             | '1' = Bit is set                |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                     |                 | tad. Daad aa f                  | o'            |                  |                  |                 |       |

| bit 15-14<br>bit 13 | -               | ted: Read as '                  |               | amplata Interr   | unt Enchla hit   |                 |       |

| DIL 13              |                 | A Channel 5 D<br>equest enable  |               |                  | upt Enable bit   |                 |       |

|                     | •               | request not ena                 |               |                  |                  |                 |       |

| bit 12-9            | Unimplemen      | ted: Read as '                  | 0'            |                  |                  |                 |       |

| bit 8               | C2IE: ECAN2     | 2 Event Interrup                | ot Enable bit |                  |                  |                 |       |

|                     |                 | equest enable                   |               |                  |                  |                 |       |

|                     | •               | request not ena                 |               |                  |                  |                 |       |

| bit 7               |                 | N2 Receive D                    | -             | errupt Enable I  | Dit              |                 |       |

|                     | •               | equest enable<br>equest not ena |               |                  |                  |                 |       |

| bit 6               |                 | nal Interrupt 4                 |               |                  |                  |                 |       |

|                     | 1 = Interrupt r | equest enable                   | d             |                  |                  |                 |       |

|                     |                 | request not ena                 |               |                  |                  |                 |       |

| bit 5               |                 | nal Interrupt 3                 |               |                  |                  |                 |       |

|                     |                 | equest enable<br>equest not ena |               |                  |                  |                 |       |

| bit 4               | -               | Interrupt Enab                  |               |                  |                  |                 |       |

|                     |                 | equest enable                   |               |                  |                  |                 |       |

|                     | •               | equest not ena                  |               |                  |                  |                 |       |

| bit 3               |                 | Interrupt Enab                  |               |                  |                  |                 |       |

|                     |                 | equest enable                   |               |                  |                  |                 |       |

| bit 2               | -               | equest not ena<br>2 Master Even |               | abla bit         |                  |                 |       |

|                     |                 | equest enable                   | -             |                  |                  |                 |       |

|                     |                 | request not ena                 |               |                  |                  |                 |       |

| bit 1               | SI2C2IE: 12C    | 2 Slave Events                  | Interrupt Ena | ble bit          |                  |                 |       |

|                     |                 | equest enable                   |               |                  |                  |                 |       |

|                     | -               | equest not ena                  |               |                  |                  |                 |       |

| bit 0               |                 | Interrupt Enab                  |               |                  |                  |                 |       |

|                     |                 | equest enable<br>equest not ena |               |                  |                  |                 |       |

|                     |                 | 540501101010                    |               |                  |                  |                 |       |

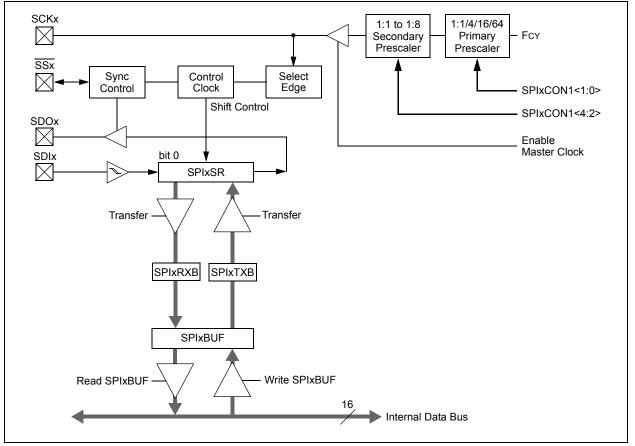

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 18. "Serial Peripheral Interface (SPI)" (DS70243), which is available from the Microchip website (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module. Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

#### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# PIC24HJXXXGPX06/X08/X10

| REGISTER            | 16-2: SPIxC      | ON1: SPIx C                       | ONTROL R               | EGISTER 1          |                    |                     |                      |

|---------------------|------------------|-----------------------------------|------------------------|--------------------|--------------------|---------------------|----------------------|

| U-0                 | U-0              | U-0                               | R/W-0                  | R/W-0              | R/W-0              | R/W-0               | R/W-0                |

|                     |                  |                                   | DISSCK                 | DISSDO             | MODE16             | SMP                 | CKE <sup>(1)</sup>   |

| bit 15              |                  |                                   |                        |                    |                    |                     | bit                  |

| R/W-0               | R/W-0            | R/W-0                             | R/W-0                  | R/W-0              | R/W-0              | R/W-0               | R/W-0                |

| SSEN <sup>(3)</sup> | СКР              | MSTEN                             |                        | SPRE<2:0>(2        | 2)                 | PPRE<               | <1:0> <sup>(2)</sup> |

| bit 7               |                  |                                   |                        |                    |                    | ·                   | bit                  |

| Legend:             |                  |                                   |                        |                    |                    |                     |                      |

| R = Readable        | e bit            | W = Writable                      | bit                    | U = Unimpler       | nented bit, read   | l as '0'            |                      |

| -n = Value at       | POR              | '1' = Bit is set                  | t                      | '0' = Bit is cle   | ared               | x = Bit is unkr     | nown                 |

|                     |                  |                                   |                        |                    |                    |                     |                      |

| bit 15-13           | Unimplemen       | ted: Read as                      | 0'                     |                    |                    |                     |                      |

| bit 12              | DISSCK: Dis      | able SCKx pin                     | bit (SPI Maste         | er modes only)     |                    |                     |                      |

|                     |                  | SPI clock is dis                  |                        | ctions as I/O      |                    |                     |                      |

|                     | 0 = Internal S   | SPI clock is ena                  | abled                  |                    |                    |                     |                      |

| bit 11              |                  | able SDOx pin                     |                        |                    |                    |                     |                      |

|                     |                  | is not used by<br>is controlled b |                        | functions as I/C   | )                  |                     |                      |

| hit 10              | •                |                                   | •                      | a at hit           |                    |                     |                      |

| bit 10              |                  | ord/Byte Comn<br>ication is word  |                        |                    |                    |                     |                      |

|                     |                  | ication is byte-                  |                        |                    |                    |                     |                      |

| bit 9               | SMP: SPIx D      | ata Input Sam                     | ole Phase bit          |                    |                    |                     |                      |

|                     | Master mode      | -                                 |                        |                    |                    |                     |                      |

|                     |                  | a sampled at e                    |                        |                    |                    |                     |                      |

|                     | Slave mode:      | a sampled at m                    |                        | Sulput lime        |                    |                     |                      |

|                     |                  | cleared when                      | SPIx is used           | in Slave mode.     |                    |                     |                      |

| bit 8               | CKE: SPIx C      | lock Edge Sele                    | ect bit <sup>(1)</sup> |                    |                    |                     |                      |

|                     | 1 = Serial out   | put data chang                    | ges on transiti        |                    | clock state to Id  |                     |                      |

|                     |                  |                                   |                        |                    | ock state to activ | /e clock state (s   | see bit 6)           |

| bit 7               |                  | Select Enable                     |                        | de) <sup>(3)</sup> |                    |                     |                      |

|                     |                  | ised for Slave                    |                        | rolled by port fu  | unction            |                     |                      |

| hit 6               | -                | -                                 |                        | iolied by port it  |                    |                     |                      |

| bit 6               |                  | Polarity Select                   |                        | ve state is a lov  | w level            |                     |                      |

|                     |                  |                                   |                        | e state is a high  |                    |                     |                      |

| bit 5               |                  | ster Mode Enal                    |                        | 0                  |                    |                     |                      |

|                     | 1 = Master m     |                                   |                        |                    |                    |                     |                      |

|                     | 0 = Slave mo     | de                                |                        |                    |                    |                     |                      |

| Note 1 · ⊤          | he CKE bit is no | t used in the F                   | ramed SPI m            | odes The user      | should program     | n this hit to 'o' f | or the Fram          |

|                     | PI modes (FRM    |                                   |                        |                    |                    |                     |                      |

| <b>2:</b> D         | o not set both P | rimary and Se                     | condarv preso          | alers to a value   | e of 1:1.          |                     |                      |

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **2:** Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                      | R/W-0                             | R/W-0                                                                                                                     | R/W-0                           | U-0               | R/W-0                  | R/W-0           |

|-----------------------|--------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------------|-----------------|

| UARTEN <sup>(1)</sup> |                          | USIDL                             | IREN <sup>(2)</sup>                                                                                                       | RTSMD                           |                   | UEN                    | <1:0>           |

| bit 15                |                          |                                   |                                                                                                                           |                                 |                   |                        | bit 8           |

|                       |                          |                                   |                                                                                                                           |                                 |                   |                        |                 |

| R/W-0 HC              | R/W-0                    | R/W-0 HC                          | R/W-0                                                                                                                     | R/W-0                           | R/W-0             | R/W-0                  | R/W-0           |

| WAKE                  | LPBACK                   | ABAUD                             | URXINV                                                                                                                    | BRGH                            | PDSE              | _<1:0>                 | STSEL           |

| bit 7                 |                          |                                   |                                                                                                                           |                                 |                   |                        | bit C           |

| Legend:               |                          | HC = Hardwa                       | ro cloared                                                                                                                |                                 |                   |                        |                 |

| R = Readable          | hit                      | W = Writable                      |                                                                                                                           | LI – Unimplo                    | mented bit, read  |                        |                 |

|                       |                          |                                   |                                                                                                                           | $0^{\circ} = \text{Bit is cle}$ |                   |                        |                 |

| -n = Value at F       | 'UR                      | '1' = Bit is set                  |                                                                                                                           |                                 | ared              | x = Bit is unkr        | IOWN            |

| bit 15                | UARTEN: UA               | RTx Enable bi                     | <sub>t</sub> (1)                                                                                                          |                                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           | e controlled by                 | UARTx as defi     | ned by UEN<1:          | :0>             |

|                       |                          |                                   |                                                                                                                           |                                 | y port latches; U |                        |                 |

| bit 14                | Unimplemen               | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |

| bit 13                | USIDL: Stop              | in Idle Mode bi                   | t                                                                                                                         |                                 |                   |                        |                 |

|                       |                          | ue module ope                     |                                                                                                                           |                                 | dle mode          |                        |                 |

| h:: 40                |                          | module opera                      |                                                                                                                           |                                 |                   |                        |                 |

| bit 12                |                          | Encoder and D coder and dec       |                                                                                                                           | e dit'-'                        |                   |                        |                 |

|                       |                          | coder and dec                     |                                                                                                                           |                                 |                   |                        |                 |

| bit 11                | RTSMD: Mod               | le Selection for                  | UxRTS Pin b                                                                                                               | it                              |                   |                        |                 |

|                       |                          | in in Simplex n<br>in in Flow Con |                                                                                                                           |                                 |                   |                        |                 |

| bit 10                | Unimplemen               | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |

| bit 9-8               | <b>UEN&lt;1:0&gt;:</b> ∪ | ARTx Enable I                     | oits                                                                                                                      |                                 |                   |                        |                 |

|                       | 11 = UxTX, U             | xRX and BCL                       | <pins are="" ena<="" td=""><td>bled and used</td><td>I; UxCTS pin co</td><td>ntrolled by port</td><td>latches</td></pins> | bled and used                   | I; UxCTS pin co   | ntrolled by port       | latches         |

|                       |                          | xRX, UxCTS a                      |                                                                                                                           |                                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 | ed; UxCTS pin c   |                        |                 |

|                       | port latcl               |                                   |                                                                                                                           |                                 |                   |                        | lolled by       |

| bit 7                 | WAKE: Wake               | up on Start bi                    | t Detect Durin                                                                                                            | g Sleep Mode                    | Enable bit        |                        |                 |

|                       | 1 = UARTx w              | /ill continue to                  | sample the Ux                                                                                                             | RX pin; interro                 | upt generated o   | n falling edge; l      | oit cleared     |

|                       |                          | are on following                  | g rising edge                                                                                                             |                                 |                   |                        |                 |

|                       | 0 = No wake              | •                                 |                                                                                                                           |                                 |                   |                        |                 |

| bit 6                 |                          | RTx Loopback                      |                                                                                                                           | bit                             |                   |                        |                 |

|                       |                          | oopback mode<br>k mode is disal   |                                                                                                                           |                                 |                   |                        |                 |

| bit 5                 | -                        | -Baud Enable                      |                                                                                                                           |                                 |                   |                        |                 |

|                       | 1 = Enable b             | aud rate meas                     | urement on th                                                                                                             |                                 | er – requires re  | ception of a Sy        | nc field (0x55) |

|                       |                          | ny data; cleared<br>e measuremen  |                                                                                                                           | •                               | on                |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 | amily Referenc    | e <i>Manual"</i> for i | nformation or   |

| en                    | abling the UAR           | T module for re                   | eceive or trans                                                                                                           | smit operation.                 |                   |                        |                 |

|                       |                          |                                   |                                                                                                                           |                                 |                   |                        |                 |

#### 2: This feature is only available for the 16x BRG mode (BRGH = 0).

# PIC24HJXXXGPX06/X08/X10

## REGISTER 19-2: CiCTRL2: ECAN™ MODULE CONTROL REGISTER 2

| U-0             | U-0                | U-0                                | U-0             | U-0              | U-0              | U-0             | U-0   |

|-----------------|--------------------|------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _               | —                  | —                                  | _               | —                | —                | —               | —     |

| bit 15          |                    |                                    |                 |                  |                  |                 | bit 8 |

|                 |                    |                                    |                 |                  |                  |                 |       |

| U-0             | U-0                | U-0                                | R-0             | R-0              | R-0              | R-0             | R-0   |

| —               | —                  | —                                  |                 |                  | DNCNT<4:0>       |                 |       |

| bit 7           |                    |                                    |                 |                  |                  |                 | bit 0 |

|                 |                    |                                    |                 |                  |                  |                 |       |

| Legend:         |                    |                                    |                 |                  |                  |                 |       |

| R = Readable    | bit                | W = Writable                       | bit             | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at F | POR                | '1' = Bit is set                   |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                 |                    |                                    |                 |                  |                  |                 |       |

| bit 15-5        | Unimplemen         | ted: Read as '                     | כ'              |                  |                  |                 |       |

| bit 4-0         | DNCNT<4:0>         | •: DeviceNet™                      | Filter Bit Num  | ber bits         |                  |                 |       |

|                 | 10010-1111         | 1 = Invalid sele                   | ection          |                  |                  |                 |       |

|                 | 10001 <b>= Com</b> | npare up to data                   | a byte 3, bit 6 | with EID<17>     |                  |                 |       |

|                 | •                  |                                    |                 |                  |                  |                 |       |

|                 | •                  |                                    |                 |                  |                  |                 |       |

|                 | •                  |                                    |                 |                  |                  |                 |       |

|                 |                    | npare up to data<br>not compare da |                 | with EID<0>      |                  |                 |       |

# 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 16. "Analog-to-Digital Converter (ADC)" (DS70225), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 devices have up to 32 Analog-to-Digital input channels. These devices also have up to 2 Analog-to-Digital converter modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- · Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Two result alignment options (signed/unsigned)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the Analog-to-Digital Converter can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the device data sheet for further details.

A block diagram of the Analog-to-Digital Converter is shown in Figure 20-1.

# 20.2 Analog-to-Digital Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on the ADC module (ADxCON1<15>)

- Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

2.

b) Select ADC interrupt priority

# 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

#### REGISTER 20-2: ADxCON2: ADCx CONTROL REGISTER 2 (where x = 1 or 2) R/W-0 R/W-0 R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 VCFG<2:0> CSCNA CHPS<1:0> bit 15 bit 8 R/W-0 R-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 BUFS SMPI<3:0> BUFM ALTS bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-13 VCFG<2:0>: Converter Voltage Reference Configuration bits VREF+ **VREF-**AVDD AVss 000 External VREF+ 001 AVss AVDD External VREF-010 External VREF-External VREF+ 011 1xx AVDD **AVss** bit 12-11 Unimplemented: Read as '0' bit 10 CSCNA: Scan Input Selections for CH0+ during Sample A bit 1 = Scan inputs 0 = Do not scan inputs bit 9-8 CHPS<1:0>: Selects Channels Utilized bits When AD12B = 1, CHPS<1:0> is: U-0, Unimplemented, Read as '0' 1x = Converts CH0, CH1, CH2 and CH3 01 = Converts CH0 and CH1 00 = Converts CH0 bit 7 **BUFS:** Buffer Fill Status bit (only valid when BUFM = 1) 1 = ADC is currently filling second half of buffer, user should access data in first half 0 = ADC is currently filling first half of buffer, user should access data in second half bit 6 Unimplemented: Read as '0' bit 5-2 SMPI<3:0>: Selects Increment Rate for DMA Addresses bits or number of sample/conversion operations per interrupt 1111 = Increments the DMA address or generates interrupt after completion of every 16th sample/conversion operation 1110 = Increments the DMA address or generates interrupt after completion of every 15th sample/conversion operation 0001 = Increments the DMA address or generates interrupt after completion of every 2nd sample/conversion operation 0000 = Increments the DMA address or generates interrupt after completion of every sample/conversion operation bit 1 BUFM: Buffer Fill Mode Select bit 1 = Starts filling first half of buffer on first interrupt and second half of buffer on next interrupt 0 = Always starts filling buffer from the beginning bit 0 ALTS: Alternate Input Sample Mode Select bit 1 = Uses channel input selects for Sample A on first sample and Sample B on next sample

# 22.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

The PIC24H instruction set is identical to that of the PIC24F, and is a subset of the dsPIC30F/33F instruction set.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The PIC24H instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

### TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| АС СНА       | RACTERI | 5110.5                                                              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |                    |     |                              |                                |  |  |

|--------------|---------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------------------------------|--------------------------------|--|--|

| Param<br>No. | Symbol  | Characteristic                                                      |                                                                                                                                                  | Min | Typ <sup>(1)</sup> | Max | Units                        | Conditions                     |  |  |

| OS50         | Fplli   | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 0.8                                                                                                                                              |     | 8                  | MHz | ECPLL, HSPLL, XTPLL<br>modes |                                |  |  |

| OS51         | Fsys    | On-Chip VCO System<br>Frequency                                     |                                                                                                                                                  | 100 | _                  | 200 | MHz                          |                                |  |  |

| OS52         | TLOCK   | PLL Start-up Time (Lock                                             | Time)                                                                                                                                            | 0.9 | 1.5                | 3.1 | mS                           |                                |  |  |

| OS53         | DCLK    | CLKO Stability (Jitter)                                             |                                                                                                                                                  | -3  | 0.5                | 3   | %                            | Measured over 100 ms<br>period |  |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### TABLE 24-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHA       | RACTERISTICS                                                                          |     | rd Operating temper |     |       | <b>3.0V to 3.6V (unless ot</b> $C \le TA \le +85^{\circ}C$ for Indu | -    |  |  |  |

|--------------|---------------------------------------------------------------------------------------|-----|---------------------|-----|-------|---------------------------------------------------------------------|------|--|--|--|

| Param<br>No. | Characteristic                                                                        | Min | Тур                 | Max | Units | Condit                                                              | ions |  |  |  |

|              | Internal FRC Accuracy @ 7.3728 MHz <sup>(1,2)</sup>                                   |     |                     |     |       |                                                                     |      |  |  |  |

| F20          | FRC       -2       +2       % $-40^{\circ}C \le TA \le +85^{\circ}C$ VDD = $3.0-3.6V$ |     |                     |     |       |                                                                     |      |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

2: FRC is set to initial frequency of 7.37 MHz (±2%) at 25°C.

#### TABLE 24-19: INTERNAL RC ACCURACY

| АС СН        | ARACTERISTICS                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                       |                |  |

|--------------|----------------------------------|------------------------------------------------------|-----|-----|-------|---------------------------------------|----------------|--|

| Param<br>No. | Characteristic                   | Min                                                  | Тур | Max | Units | Conditions                            |                |  |

|              | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                      |     |     |       |                                       |                |  |

| F21          | LPRC                             | -20                                                  | ±6  | +20 | %     | $-40^\circ C \le T A \le +85^\circ C$ | VDD = 3.0-3.6V |  |

**Note 1:** Change of LPRC frequency as VDD changes.

| AC CHARACTERISTICS |        |                                | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |          |           |           |                                                  |  |

|--------------------|--------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-----------|--------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic Min.            |                                                                                                                                                         | Тур      | Max.      | Units     | Conditions                                       |  |

|                    |        | ADC Accuracy (12-bit Mode      | e) – Meas                                                                                                                                               | uremen   | ts with e | xternal   | VREF+/VREF-                                      |  |

| AD20a              | Nr     | Resolution                     | 12 data bits                                                                                                                                            |          | bits      |           |                                                  |  |

| AD21a              | INL    | Integral Nonlinearity          | -2                                                                                                                                                      | _        | +2        | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD22a              | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                     | —        | <1        | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD23a              | Gerr   | Gain Error                     | 1.25                                                                                                                                                    | 1.5      | 3         | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD24a              | EOFF   | Offset Error                   | 1.25                                                                                                                                                    | 1.52     | 2         | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |

| AD25a              | _      | Monotonicity                   | _                                                                                                                                                       |          | _         | _         | Guaranteed                                       |  |

|                    |        | ADC Accuracy (12-bit Mode      | e) – Meas                                                                                                                                               | uremen   | ts with i | nternal V | VREF+/VREF-                                      |  |

| AD20a              | Nr     | Resolution                     | 12 data bits                                                                                                                                            |          | bits      |           |                                                  |  |

| AD21a              | INL    | Integral Nonlinearity          | -2                                                                                                                                                      | —        | +2        | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD22a              | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                     | —        | <1        | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD23a              | Gerr   | Gain Error                     | 2                                                                                                                                                       | 3        | 7         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD24a              | EOFF   | Offset Error                   | 2                                                                                                                                                       | 3        | 5         | LSb       | VINL = AVSS = 0V, AVDD = 3.6V                    |  |

| AD25a              | —      | Monotonicity                   | —                                                                                                                                                       | —        | —         | —         | Guaranteed                                       |  |

|                    |        | Dynamic                        | Performa                                                                                                                                                | ince (12 | -bit Mod  | e)        |                                                  |  |

| AD30a              | THD    | Total Harmonic Distortion      | -77                                                                                                                                                     | -69      | -61       | dB        | —                                                |  |

| AD31a              | SINAD  | Signal to Noise and Distortion | 59                                                                                                                                                      | 63       | 64        | dB        | _                                                |  |

| AD32a              | SFDR   | Spurious Free Dynamic<br>Range | 63                                                                                                                                                      | 72       | 74        | dB        | _                                                |  |

| AD33a              | Fnyq   | Input Signal Bandwidth         | —                                                                                                                                                       | —        | 250       | kHz       | —                                                |  |

| AD34a              | ENOB   | Effective Number of Bits       | 10.95                                                                                                                                                   | 11.1     | _         | bits      | _                                                |  |

# TABLE 24-36: ADC MODULE SPECIFICATIONS (12-BIT MODE)