Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K × 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp306-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin NameAN0-AN31AVDDAVssCLKICLKOCN0-CN23 | Pin           Type           I           P           I           O | Buffer<br>Type<br>Analog<br>P<br>P<br>ST/CMOS<br>—<br>ST | Description           Analog input channels.           Positive supply for analog modules. This pin must be connected at all times.           Ground reference for analog modules.           External clock source input. Always associated with OSC1 pin function.           Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |

|------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AVDD<br>AVSS<br>CLKI<br>CLKO             | P<br>P<br>I<br>O                                                   | P<br>P<br>ST/CMOS<br>—                                   | Positive supply for analog modules. This pin must be connected at all times.<br>Ground reference for analog modules.<br>External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                  |  |  |  |

| AVss<br>CLKI<br>CLKO                     | P<br>I<br>O                                                        | P<br>ST/CMOS<br>—                                        | Ground reference for analog modules.<br>External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                  |  |  |  |

| CLKI<br>CLKO                             | <br>0<br>                                                          | ST/CMOS<br>—                                             | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                                                          |  |  |  |

| CLKO                                     | 0                                                                  | _                                                        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                                                                                                                                       |  |  |  |

| CN0-CN23                                 |                                                                    | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                          |                                                                    |                                                          | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| C1RX                                     |                                                                    | ST                                                       | ECAN1 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| C1TX                                     | 0                                                                  | —                                                        | ECAN1 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| C2RX                                     | I                                                                  | ST                                                       | ECAN2 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| C2TX                                     | 0                                                                  | —                                                        | ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| PGED1                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 1.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PGEC1                                    | I                                                                  | ST                                                       | Clock input pin for programming/debugging communication channel 1.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PGED2                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 2.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PGEC2                                    | I                                                                  | ST                                                       | Clock input pin for programming/debugging communication channel 2.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PGED3                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 3.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| PGEC3                                    |                                                                    | ST                                                       | Clock input pin for programming/debugging communication channel 3.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

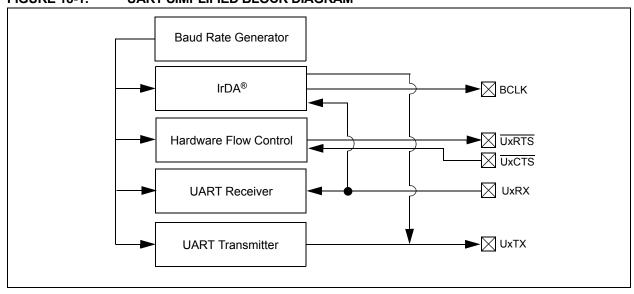

| IC1-IC8                                  | I                                                                  | ST                                                       | Capture inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| INT0                                     |                                                                    | ST                                                       | External interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| INT1                                     | I                                                                  | ST                                                       | External interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| INT2                                     | I                                                                  | ST                                                       | External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| INT3                                     | I                                                                  | ST                                                       | External interrupt 3.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| INT4                                     | I                                                                  | ST                                                       | External interrupt 4.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| MCLR                                     | I/P                                                                | ST                                                       | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| OCFA                                     | I                                                                  | ST                                                       | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| OCFB                                     | I                                                                  | ST                                                       | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

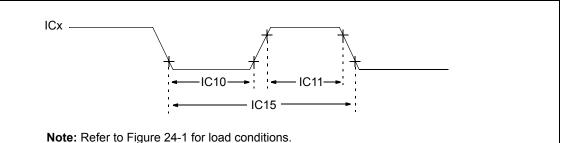

| OC1-OC8                                  | 0                                                                  | —                                                        | Compare outputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| OSC1                                     | I                                                                  | ST/CMOS                                                  | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| OSC2                                     | I/O                                                                | —                                                        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| RA0-RA7                                  | I/O                                                                | ST                                                       | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RA9-RA10                                 | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RA12-RA15                                | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RB0-RB15                                 | I/O                                                                | ST                                                       | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RC1-RC4                                  | I/O                                                                | ST                                                       | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RC12-RC15                                | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RD0-RD15                                 | I/O                                                                | ST                                                       | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RE0-RE7                                  | I/O                                                                | ST                                                       | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RF0-RF8<br>RF12-RF13                     | I/O                                                                | ST                                                       | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RG0-RG3<br>RG6-RG9                       | I/O<br>I/O                                                         | ST<br>ST                                                 | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RG12-RG15<br>Legend: CMOS                | 1/0                                                                | ST                                                       | e input or output Analog = Analog input P = Power                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS</b> |

|------------|--------------------------------|

|------------|--------------------------------|

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog inputP = PowerO = OutputI = Input

| TABLE       | 4-6:        | TIMER REGISTER MAP  |                                                      |        |        |        |        |              |               |                |                |       |        |       |       |       |       |               |

|-------------|-------------|---------------------|------------------------------------------------------|--------|--------|--------|--------|--------------|---------------|----------------|----------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15              | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8         | Bit 7          | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |                     | Timer1 Register                                      |        |        |        |        |              |               |                |                | xxxx  |        |       |       |       |       |               |

| PR1         | 0102        |                     |                                                      |        |        |        |        |              | Period F      | Register 1     |                |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> |       | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |                     |                                                      |        |        |        |        |              | Timer2        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108        |                     |                                                      |        |        |        | Tim    | ner3 Holding | Register (for | 32-bit timer   | operations o   | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |                     |                                                      |        |        |        |        |              | Timer3        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR2         | 010C        |                     |                                                      |        |        |        |        |              | Period F      | Register 2     |                |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |                     |                                                      |        |        |        |        |              | Period F      | Register 3     |                |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T3CON       | 0112        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   | _     | 0000          |

| TMR4        | 0114        |                     |                                                      | •      | •      |        |        | •            | Timer4        | Register       |                |       |        |       |       | •     | •     | xxxx          |

| TMR5HLD     | 0116        |                     | Timer5 Holding Register (for 32-bit operations only) |        |        |        |        |              | xxxx          |                |                |       |        |       |       |       |       |               |

| TMR5        | 0118        | Timer5 Register xxx |                                                      |        |        |        |        | xxxx         |               |                |                |       |        |       |       |       |       |               |

| PR4         | 011A        | Period Register 4   |                                                      |        |        |        | FFFF   |              |               |                |                |       |        |       |       |       |       |               |

| PR5         | 011C        | Period Register 5   |                                                      |        |        |        | FFFF   |              |               |                |                |       |        |       |       |       |       |               |

| T4CON       | 011E        | TON                 |                                                      | TSIDL  | —      | _      | _      | —            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | —     | 0000          |

| T5CON       | 0120        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   | _     | 0000          |

| TMR6        | 0122        |                     |                                                      |        |        |        |        |              | Timer6        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR7HLD     | 0124        |                     |                                                      |        |        |        |        | Timer7 Hold  | ing Register  | (for 32-bit op | perations only | y)    |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |                     |                                                      |        |        |        |        |              | Timer7        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR6         | 0128        |                     |                                                      |        |        |        |        |              | Period F      | Register 6     |                |       |        |       |       |       |       | FFFF          |

| PR7         | 012A        |                     |                                                      |        |        |        |        |              | Period F      | Register 7     |                |       |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T7CON       | 012E        | TON                 |                                                      | TSIDL  | _      | _      | _      | _            | —             | _              | TGATE          | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        |                     |                                                      |        |        |        |        |              | Timer8        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR9HLD     | 0132        |                     |                                                      |        |        |        | -      | Timer9 Hold  | ing Register  | (for 32-bit op | perations only | y)    |        |       |       |       |       | xxxx          |

| TMR9        | 0134        |                     |                                                      |        |        |        |        |              | Timer9        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR8         | 0136        |                     |                                                      |        |        |        |        |              | Period F      | Register 8     |                |       |        |       |       |       |       | FFFF          |

| PR9         | 0138        |                     |                                                      |        |        |        |        |              | Period F      | Register 9     |                |       |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON                 | _                                                    | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T9CON       | 013C        | TON                 | _                                                    | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| L           |             |                     |                                                      |        |        |        |        |              |               |                |                | 1     |        |       |       |       |       |               |

#### . . TIMED DECIGTED MAD

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 6. "Interrupts" (DS70224), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24HJXXXGPX06/X08/X10 CPU. It has the following features:

- Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of 8 nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24HJXXXGPX06/X08/X10 devices implement up to 61 unique interrupts and 5 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24HJXXXGPX06/X08/X10 device clears its registers in response to a Reset which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 7-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0          | U-0                  | U-0                                     | U-0            | R-0              | R-0            | R-0             | R-0   |

|--------------|----------------------|-----------------------------------------|----------------|------------------|----------------|-----------------|-------|

| _            | -                    | —                                       | _              |                  | IL             | R<3:0>          |       |

| bit 15       |                      |                                         |                |                  |                |                 | bit 8 |

|              |                      |                                         |                |                  |                |                 |       |

| U-0          | U-0                  | R-0                                     | R-0            | R-0              | R-0            | R-0             | R-0   |

|              |                      |                                         |                | VECNUM<6:0       | >              |                 |       |

| bit 7        |                      |                                         |                |                  |                |                 | bit 0 |

| Legend:      |                      |                                         |                |                  |                |                 |       |

| R = Readab   | le bit               | W = Writable                            | bit            | U = Unimpler     | nented bit, re | ad as '0'       |       |

| -n = Value a | t POR                | '1' = Bit is set                        |                | '0' = Bit is cle | ared           | x = Bit is unkr | nown  |

| bit 11-8     | 1111 = CPL<br>•<br>• | lew CPU Interrup<br>J Interrupt Priorit | y Level is 15  | el bits          |                |                 |       |

|              | 0000 <b>= CPL</b>    | J Interrupt Priorit                     | y Level is 0   |                  |                |                 |       |

| bit 7        | •                    | nted: Read as '                         |                |                  |                |                 |       |

| bit 6-0      | 1111111 =<br>•<br>•  | :0>: Vector Num<br>Interrupt Vector     | pending is nur | mber 135         | i              |                 |       |

|              |                      | Interrupt Vector<br>Interrupt Vector    | U U            |                  |                |                 |       |

### REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0        | R/W-0            | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|------------------------------------|-------|--------------|------------------|--------------|-----------------|----------|-------|

|                                    |       |              | PAD              | <15:8>       |                 |          |       |

| bit 15                             |       |              |                  |              |                 |          | bit 8 |

|                                    |       |              |                  |              |                 |          |       |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0            | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                    |       |              | PAI              | )<7:0>       |                 |          |       |

| bit 7                              |       |              |                  |              |                 |          | bit 0 |

|                                    |       |              |                  |              |                 |          |       |

| Legend:                            |       |              |                  |              |                 |          |       |

| R = Readable                       | bit   | W = Writable | bit              | U = Unimpler | mented bit, rea | d as '0' |       |

| -n = Value at POR (1' = Bit is set |       |              | '0' = Bit is cle | ared         | x = Bit is unkr | nown     |       |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | R/W-0           | R/W-0               |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|---------------------|

| —               | —     | —                | _     | —                | —                | CNT<            | 9:8> <sup>(2)</sup> |

| bit 15          |       | •                |       |                  |                  |                 | bit 8               |

|                 |       |                  |       |                  |                  |                 |                     |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0               |

|                 |       |                  | CNT<  | :7:0> <b>(2)</b> |                  |                 |                     |

| bit 7           |       |                  |       |                  |                  |                 | bit 0               |

|                 |       |                  |       |                  |                  |                 |                     |

| Legend:         |       |                  |       |                  |                  |                 |                     |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimple      | mented bit, read | d as '0'        |                     |

| -n = Value at F | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | nown                |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: Number of DMA transfers = CNT<9:0> + 1.

**REGISTER 9-4:**

#### U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ \_\_\_\_\_ \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 TUN<5:0>(1) \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-6 Unimplemented: Read as '0' bit 5-0 TUN<5:0>: FRC Oscillator Tuning bits<sup>(1)</sup> 011111 = Center frequency + 11.625% (8.23 MHz) 011110 = Center frequency + 11.25% (8.20 MHz) 000001 = Center frequency + 0.375% (7.40 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.375% (7.345 MHz) 100001 = Center frequency - 11.625% (6.52 MHz) 100000 = Center frequency - 12% (6.49 MHz)

**OSCTUN: FRC OSCILLATOR TUNING REGISTER**

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

| R/W-0         | U-0                                                                                           | R/W-0                                                   | U-0                       | U-0                | U-0            | U-0                | U-0 |  |  |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------|--------------------|----------------|--------------------|-----|--|--|--|--|--|--|

| TON           | _                                                                                             | TSIDL                                                   | _                         | _                  | —              | _                  | _   |  |  |  |  |  |  |

| bit 15        |                                                                                               |                                                         |                           | - <b>I</b>         |                |                    | bit |  |  |  |  |  |  |

|               |                                                                                               |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| U-0           | R/W-0                                                                                         | R/W-0                                                   | R/W-0                     | R/W-0              | U-0            | R/W-0              | U-0 |  |  |  |  |  |  |

| _             | TGATE                                                                                         | TCKP                                                    | S<1:0>                    | T32                | _              | TCS <sup>(1)</sup> | _   |  |  |  |  |  |  |

| bit 7         |                                                                                               |                                                         |                           |                    |                |                    | bit |  |  |  |  |  |  |

| Legend:       |                                                                                               |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                         | W = Writable                                            | bit                       | U = Unimplem       | ented bit, rea | d as '0'           |     |  |  |  |  |  |  |

| -n = Value at | POR                                                                                           | '1' = Bit is se                                         | t                         | '0' = Bit is clea  | ired           | x = Bit is unkn    | own |  |  |  |  |  |  |

|               |                                                                                               |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 15        | TON: Timerx                                                                                   |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | <u>When T32 = 1:</u>                                                                          |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               |                                                                                               | 1 = Starts 32-bit Timerx/y<br>0 = Stops 32-bit Timerx/y |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | •                                                                                             | 0 = Stops 32-bit Timerx/y<br>When T32 = 0:              |                           |                    |                |                    |     |  |  |  |  |  |  |

|               |                                                                                               | 1 = Starts 16-bit Timerx                                |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | 0 = Stops 16-                                                                                 | -bit Timerx                                             |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 14        | Unimplemented: Read as '0'                                                                    |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 13        | TSIDL: Stop in Idle Mode bit                                                                  |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               |                                                                                               | •                                                       |                           | device enters Idle | e mode         |                    |     |  |  |  |  |  |  |

|               |                                                                                               | module opera                                            |                           | ode                |                |                    |     |  |  |  |  |  |  |

| bit 12-7      | -                                                                                             | ited: Read as                                           |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit                                              |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | <u>When TCS = 1:</u><br>This bit is ignored.                                                  |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | When TCS = $0$ :                                                                              |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | <ol> <li>Gated time accumulation enabled</li> <li>Gated time accumulation disabled</li> </ol> |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 5-4       |                                                                                               | : Timerx Input                                          |                           | la Salact hite     |                |                    |     |  |  |  |  |  |  |

| DIL 3-4       | 11 = 1:256                                                                                    | . Innerx input                                          | CIUCKTTESCE               | lie Gelect bits    |                |                    |     |  |  |  |  |  |  |

|               | 11 = 1.256<br>10 = 1.64                                                                       |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | 01 <b>= 1:8</b>                                                                               |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

|               | 00 = 1:1                                                                                      |                                                         |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 3         |                                                                                               | imer Mode Sel                                           |                           |                    |                |                    |     |  |  |  |  |  |  |

|               |                                                                                               | nd Timery form<br>nd Timery act a                       |                           |                    |                |                    |     |  |  |  |  |  |  |

| bit 2         | Unimplemen                                                                                    | ited: Read as                                           | ʻ0 <b>'</b>               |                    |                |                    |     |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                                                   | Clock Source                                            | Select bit <sup>(1)</sup> |                    |                |                    |     |  |  |  |  |  |  |

|               |                                                                                               | clock from pin                                          | TxCK (on the              | rising edge)       |                |                    |     |  |  |  |  |  |  |

|               | 0 = Internal c                                                                                | IOCK (FCY)                                              |                           |                    |                |                    |     |  |  |  |  |  |  |

#### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available for all timers. Refer to the "Pin Diagrams" section for the available pins.

#### **Input Capture Registers** 14.1

| REGISTER 1           | 4-1: ICxCO | N: INPUT CA | APTURE x C | ONTROL RE | GISTER |          |       |

|----------------------|------------|-------------|------------|-----------|--------|----------|-------|

| U-0                  | U-0        | R/W-0       | U-0        | U-0       | U-0    | U-0      | U-0   |

| —                    | —          | ICSIDL      | —          | —         |        | —        | _     |

| bit 15               |            |             |            |           |        |          | bit   |

|                      |            |             |            |           |        |          |       |

| R/W-0                | R/W-0      | R/W-0       | R-0, HC    | R-0, HC   | R/W-0  | R/W-0    | R/W-0 |

| ICTMR <sup>(1)</sup> | ICI<       | 1:0>        | ICOV       | ICBNE     |        | ICM<2:0> |       |

| bit 7                |            |             |            |           |        |          | bit   |

|                      |            |             |            |           |        |          |       |

| Legend:              |            |             |            |           |        |          |       |

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

|                   |                  |                             |                    |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                          |

|           | 1 = Input capture module will halt in CPU Idle mode                                                                                                                                                                            |

|           | 0 = Input capture module will continue to operate in CPU Idle mode                                                                                                                                                             |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                     |

| bit 7     | ICTMR: Input Capture Timer Select bits <sup>(1)</sup>                                                                                                                                                                          |

|           | 1 = TMR2 contents are captured on capture event                                                                                                                                                                                |

|           | 0 = TMR3 contents are captured on capture event                                                                                                                                                                                |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                         |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                   |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                                                                                          |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                          |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                       |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                            |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                         |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                       |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                              |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                       |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable.)</li> <li>110 = Unused (module disabled)</li> </ul> |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                                                                     |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                      |

|           | <ul> <li>011 = Capture mode, every rising edge</li> <li>010 = Capture mode, every falling edge</li> </ul>                                                                                                                      |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                                                                                            |

|           | (ICI<1:0> bits do not control interrupt generation for this mode.)                                                                                                                                                             |

|           | 000 = Input capture module turned off                                                                                                                                                                                          |

|           |                                                                                                                                                                                                                                |

bit 8

bit 0

NOTES:

### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| S: Start bit                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                                                       |

| Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                               |

| <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                |

| <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul> |

| RBF: Receive Buffer Full Status bit                                                                                                                                                                                              |

| <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul>      |

| TBF: Transmit Buffer Full Status bit                                                                                                                                                                                             |

| <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>            |

|                                                                                                                                                                                                                                  |

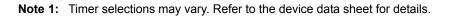

### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 17. "UART" (DS70232), which is available from the Microchip website (www.microchip.com).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJXXXGPX06/X08/X10 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UXCTS and UXRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 1 Mbps to 15 bps at 16x mode at 40 MIPS

- Baud rates ranging from 4 Mbps to 61 bps at 4x mode at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of the key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

- **Note 1:** Both UART1 and UART2 can trigger a DMA data transfer. If U1TX, U1RX, U2TX or U2RX is selected as a DMA IRQ source, a DMA transfer occurs when the U1TXIF, U1RXIF, U2TXIF or U2RXIF bit gets set as a result of a UART1 or UART2 transmission or reception.

- 2: If DMA transfers are required, the UART TX/RX FIFO buffer must be set to a size of 1 byte/word (i.e., UTXISEL<1:0> = 00 and URXISEL<1:0> = 00).

#### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit</li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                                                       |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                               |

- **Note 1:** Refer to **Section 17. "UART"** (DS70232) in the *"PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                     |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |