Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

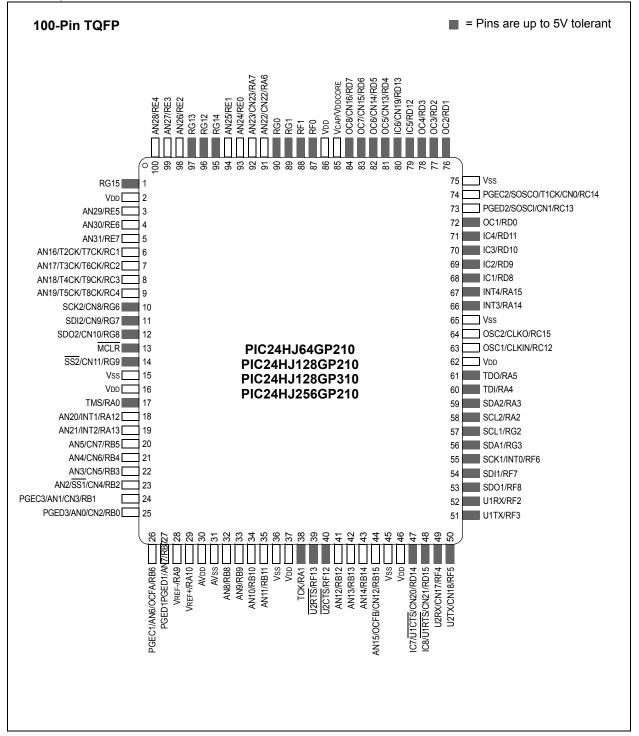

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp310t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams (Continued)**

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor to Vss on unused pins and drive the output to logic low.

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 2. "CPU" (DS70245), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and addressing modes. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free, single-cycle program loop constructs are supported using the REPEAT instruction, which is interruptible at any point.

The PIC24HJXXXGPX06/X08/X10 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The PIC24HJXXXGPX06/X08/X10 instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions, the PIC24HJXXXGPX06/X08/X10 is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1, and the programmer's model for the PIC24HJXXXGPX06/X08/X10 is shown in Figure 3-2.

# 3.1 Data Addressing Overview

The data space can be linearly addressed as 32K words or 64 Kbytes using an Address Generation Unit (AGU). The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The data space also includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general purpose RAM.

# 3.2 Special MCU Features

The PIC24HJXXXGPX06/X08/X10 features a 17-bit by 17-bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication makes mixed-sign multiplication possible.

The PIC24HJXXXGPX06/X08/X10 supports 16/16 and 32/16 integer divide operations. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A multi-bit data shifter is used to perform up to a 16-bit, left or right shift in a single cycle.

| <b>REGISTER 3-2:</b> CORCON: CORE CONTROL REGISTER |

|----------------------------------------------------|

|----------------------------------------------------|

| U-0              | U-0                                         | U-0               | U-0            | U-0                  | U-0    | U-0              | U-0   |  |  |

|------------------|---------------------------------------------|-------------------|----------------|----------------------|--------|------------------|-------|--|--|

| —                | —                                           | —                 | —              | —                    | -      | —                | —     |  |  |

| bit 15           |                                             |                   |                |                      |        |                  | bit 8 |  |  |

|                  |                                             |                   |                |                      |        |                  |       |  |  |

| U-0              | U-0                                         | U-0               | U-0            | R/C-0                | R/W-0  | U-0              | U-0   |  |  |

| —                | —                                           | —                 | —              | IPL3 <sup>(1)</sup>  | PSV    | —                | —     |  |  |

| bit 7            |                                             |                   |                |                      |        |                  | bit 0 |  |  |

|                  |                                             |                   |                |                      |        |                  |       |  |  |

| Legend:          |                                             | C = Clear only    | y bit          |                      |        |                  |       |  |  |

| R = Readable     | bit                                         | W = Writable      | bit            | -n = Value at        | POR    | '1' = Bit is set |       |  |  |

| 0' = Bit is clea | ared                                        | 'x = Bit is unki  | nown           | U = Unimpler         | as '0' |                  |       |  |  |

| bit 15-4         | Unimplemen                                  | ted: Read as '    | 0'             |                      |        |                  |       |  |  |

| bit 3            | •                                           | terrupt Priority  |                | oit 3 <sup>(1)</sup> |        |                  |       |  |  |

|                  |                                             | rupt priority lev |                |                      |        |                  |       |  |  |

|                  |                                             | rupt priority lev | •              |                      |        |                  |       |  |  |

| bit 2            | PSV: Progran                                | n Space Visibili  | ty in Data Spa | ice Enable bit       |        |                  |       |  |  |

|                  | 1 = Program                                 | space visible in  | data space     |                      |        |                  |       |  |  |

|                  | 0 = Program space not visible in data space |                   |                |                      |        |                  |       |  |  |

|                  |                                             |                   |                |                      |        |                  |       |  |  |

bit 1-0 Unimplemented: Read as '0'

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP |

|----------------------------------------------|

|----------------------------------------------|

| IADEE .     | <del>-</del> -J. |        |        |            |            |        |             |            |        |             |              |              |             |              |             |           |               |               |

|-------------|------------------|--------|--------|------------|------------|--------|-------------|------------|--------|-------------|--------------|--------------|-------------|--------------|-------------|-----------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr      | Bit 15 | Bit 14 | Bit 13     | Bit 12     | Bit 11 | Bit 10      | Bit 9      | Bit 8  | Bit 7       | Bit 6        | Bit 5        | Bit 4       | Bit 3        | Bit 2       | Bit 1     | Bit 0         | All<br>Resets |

| INTCON1     | 0080             | NSTDIS | —      | —          | _          | —      | —           | —          | —      | _           | DIV0ERR      | DMACERR      | MATHERR     | ADDRERR      | STKERR      | OSCFAIL   | —             | 0000          |

| INTCON2     | 0082             | ALTIVT | DISI   | _          |            | -      | _           | _          | _      | —           | _            | —            | INT4EP      | INT3EP       | INT2EP      | INT1EP    | INT0EP        | 0000          |

| IFS0        | 0084             | _      | DMA1IF | AD1IF      | U1TXIF     | U1RXIF | SPI1IF      | SPI1EIF    | T3IF   | T2IF        | OC2IF        | IC2IF        | DMA0IF      | T1IF         | OC1IF       | IC1IF     | <b>INT0IF</b> | 0000          |

| IFS1        | 0086             | U2TXIF | U2RXIF | INT2IF     | T5IF       | T4IF   | OC4IF       | OC3IF      | DMA2IF | IC8IF       | IC7IF        | AD2IF        | INT1IF      | CNIF         | _           | MI2C1IF   | SI2C1IF       | 0000          |

| IFS2        | 0088             | T6IF   | DMA4IF | —          | OC8IF      | OC7IF  | OC6IF       | OC5IF      | IC6IF  | IC5IF       | IC4IF        | IC3IF        | DMA3IF      | C1IF         | C1RXIF      | SPI2IF    | SPI2EIF       | 0000          |

| IFS3        | 008A             | _      | _      | DMA5IF     | _          | _      | _           | _          | C2IF   | C2RXIF      | INT4IF       | INT3IF       | T9IF        | T8IF         | MI2C2IF     | SI2C2IF   | T7IF          | 0000          |

| IFS4        | 008C             | _      | _      | —          | _          | _      | _           | _          | _      | C2TXIF      | C1TXIF       | DMA7IF       | DMA6IF      | _            | U2EIF       | U1EIF     | —             | 0000          |

| IEC0        | 0094             | _      | DMA1IE | AD1IE      | U1TXIE     | U1RXIE | SPI1IE      | SPI1EIE    | T3IE   | T2IE        | OC2IE        | IC2IE        | DMA0IE      | T1IE         | OC1IE       | IC1IE     | INT0IE        | 0000          |

| IEC1        | 0096             | U2TXIE | U2RXIE | INT2IE     | T5IE       | T4IE   | OC4IE       | OC3IE      | DMA2IE | IC8IE       | IC7IE        | AD2IE        | INT1IE      | CNIE         | _           | MI2C1IE   | SI2C1IE       | 0000          |

| IEC2        | 0098             | T6IE   | DMA4IE | —          | OC8IE      | OC7IE  | OC6IE       | OC5IE      | IC6IE  | IC5IE       | IC4IE        | IC3IE        | DMA3IE      | C1IE         | C1RXIE      | SPI2IE    | SPI2EIE       | 0000          |

| IEC3        | 009A             | _      | _      | DMA5IE     | _          | _      | _           | _          | C2IE   | C2RXIE      | INT4IE       | INT3IE       | T9IE        | T8IE         | MI2C2IE     | SI2C2IE   | T7IE          | 0000          |

| IEC4        | 009C             | —      | —      | —          | _          | —      | —           | _          | —      | C2TXIE      | C1TXIE       | DMA7IE       | DMA6IE      | —            | U2EIE       | U1EIE     | —             | 0000          |

| IPC0        | 00A4             | —      |        | T1IP<2:0>  |            | —      |             | OC1IP<2:0  | )>     | _           |              | IC1IP<2:0>   |             | -            | INT0IP<2:0> |           | 4444          |               |

| IPC1        | 00A6             | _      |        | T2IP<2:0>  |            | _      |             | OC2IP<2:0  | )>     | _           |              | IC2IP<2:0>   | 0> —        |              | DMA0IP<2:0> |           | 4444          |               |

| IPC2        | 00A8             | _      | ι      | J1RXIP<2:0 | XIP<2:0> — |        | SPI1IP<2:0> |            | )>     | _           |              | SPI1EIP<2:0> |             | _            |             | T3IP<2:0> |               | 4444          |

| IPC3        | 00AA             | _      | _      | _          |            |        | DMA1IP<2:0> |            | _      | AD1IP<2:0>  |              | _            | U1TXIP<2:0> |              | >           | 0444      |               |               |

| IPC4        | 00AC             | _      |        | CNIP<2:0>  | •          | _      | _           | _          | _      | _           | MI2C1IP<2:0> |              | _           | SI2C1IP<2:0> |             | >         | 4044          |               |

| IPC5        | 00AE             | —      |        | IC8IP<2:0> | >          |        | IC7IP<2:0>  |            | >      | —           | AD2IP<2:0>   |              | —           | INT1IP<2:0>  |             | •         | 4444          |               |

| IPC6        | 00B0             | —      |        | T4IP<2:0>  |            |        |             | OC4IP<2:(  | )>     | —           | OC3IP<2:0>   |              | —           | DMA2IP<2:0>  |             | >         | 4444          |               |

| IPC7        | 00B2             | —      | ι      | J2TXIP<2:0 | )>         |        | U2RXIP<2:0> |            | —      | INT2IP<2:0> |              | —            |             | T5IP<2:0>    |             | 4444      |               |               |

| IPC8        | 00B4             | —      |        | C1IP<2:0>  |            |        | C1RXIP<2:0> |            | —      |             | SPI2IP<2:0   | >            | —           | SF           | PI2EIP<2:0  | >         | 4444          |               |

| IPC9        | 00B6             | _      |        | IC5IP<2:0> | >          |        |             | IC4IP<2:0> |        | —           |              | IC3IP<2:0>   |             | —            | DI          | MA3IP<2:0 | >             | 4444          |

| IPC10       | 00B8             | —      |        | OC7IP<2:0  | >          |        |             | OC6IP<2:0  | )>     | —           |              | OC5IP<2:0>   | >           | —            | I           | C6IP<2:0> |               | 4444          |

| IPC11       | 00BA             | _      |        | T6IP<2:0>  |            |        | C           | MA4IP<2:   | 0>     | —           | _            | —            | _           | —            | C           | C8IP<2:0> |               | 4404          |

| IPC12       | 00BC             | _      |        | T8IP<2:0>  |            | _      | N           | 112C2IP<2  | :0>    | _           |              | SI2C2IP<2:0  | )>          | _            |             | T7IP<2:0> |               | 4444          |

| IPC13       | 00BE             | _      | C      | 2RXIP<2:0  | )>         | -      | 1           | NT4IP<2:0  | )>     | —           |              | INT3IP<2:0   | >           | -            |             | T9IP<2:0> |               | 4444          |

| IPC14       | 00C0             | _      | _      | _          | —          | _      | —           | —          | _      | —           | _            | _            | _           | _            | (           | C2IP<2:0> |               | 0004          |

| IPC15       | 00C2             | —      | _      | —          | _          | —      | —           | —          | —      | _           |              | DMA5IP<2:0   | )>          | _            | —           | —         | —             | 0040          |

| IPC16       | 00C4             | _      |        | —          |            | -      |             | U2EIP<2:0  | )>     | —           |              | U1EIP<2:0>   | >           | _            |             | _         | —             | 0440          |

| IPC17       | 00C6             | _      | (      | C2TXIP<2:0 | )>         | _      | (           | C1TXIP<2:  | 0>     | _           |              | DMA7IP<2:0   | )>          | _            | DMA6IP<2:0> |           | >             | 4444          |

| INTTREG     | 00E0             | _      | —      | —          | —          |        | ILR<        | 3:0>       |        | _           |              |              | VE          | CNUM<6:0>    |             |           |               | 0000          |

| Lonordi     |                  |        |        |            |            |        |             |            |        | adaaimal fa |              |              |             |              |             |           |               |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| TABLE 4-20:       ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506/510/610 DEVICES ONLY (CONTINUED) |      |           |                                                                                                               |  |  |  |  |  |          |          |          |       |       |       |       |       |       |               |

|----------------------------------------------------------------------------------------------------------------|------|-----------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|----------|----------|----------|-------|-------|-------|-------|-------|-------|---------------|

| File Name                                                                                                      | Addr | Bit 15    | Bit 15         Bit 14         Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8 |  |  |  |  |  |          | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID                                                                                                     | 046E |           | EID<15:8>                                                                                                     |  |  |  |  |  |          | EID<7:0> |          |       |       |       |       |       |       | xxxx          |

| C1RXF12SID                                                                                                     | 0470 |           | SID<10:3>                                                                                                     |  |  |  |  |  |          | SID<2:0> |          | —     | EXIDE | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXF12EID                                                                                                     | 0472 | EID<15:8> |                                                                                                               |  |  |  |  |  | EID<7:0> |          |          |       |       |       |       |       | xxxx  |               |

| C1RXF13SID                                                                                                     | 0474 |           | SID<10:3>                                                                                                     |  |  |  |  |  |          | SID<2:0> |          | —     | EXIDE | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXF13EID                                                                                                     | 0476 |           | EID<15:8>                                                                                                     |  |  |  |  |  | EID<7:0> |          |          |       |       |       |       | xxxx  |       |               |

| C1RXF14SID                                                                                                     | 0478 |           | SID<10:3>                                                                                                     |  |  |  |  |  |          | SID<2:0> |          | —     | EXIDE | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXF14EID                                                                                                     | 047A |           | EID<15:8>                                                                                                     |  |  |  |  |  | EID<7:0> |          |          |       |       |       |       | xxxx  |       |               |

| C1RXF15SID                                                                                                     | 047C |           | SID<10:3>                                                                                                     |  |  |  |  |  |          |          | SID<2:0> |       | —     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF15EID                                                                                                     | 047E |           | EID<15:8>                                                                                                     |  |  |  |  |  | EID<7:0> |          |          |       |       |       |       | xxxx  |       |               |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices. Legend:

# TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610 DEVICES ONLY (CONTINUED)

| File Name  | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9            | Bit 8              | Bit 7    | Bit 6 | Bit 5 | Bit 4              | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|------------|------|-----------|-----------|--------|--------|--------|--------|------------------|--------------------|----------|-------|-------|--------------------|-------|-------|-------|-------|---------------|

| C2RXF11EID | 056E | EID<15:8> |           |        |        |        |        |                  | EID<7:0>           |          |       |       |                    |       |       |       | xxxx  |               |

| C2RXF12SID | 0570 | SID<10:3> |           |        |        |        |        | SID<2:0> — EXIDE |                    |          |       |       | — EID<17:16>       |       | xxxx  |       |       |               |

| C2RXF12EID | 0572 | EID<15:8> |           |        |        |        |        |                  | EID<7:0>           |          |       |       |                    |       |       |       | xxxx  |               |

| C2RXF13SID | 0574 | SID<10:3> |           |        |        |        |        | SID<2:0> — EXI   |                    |          |       |       | EXIDE — EID<17:16> |       |       | xxxx  |       |               |

| C2RXF13EID | 0576 | EID<15:8> |           |        |        |        |        | EID<7:0>         |                    |          |       |       |                    |       | xxxx  |       |       |               |

| C2RXF14SID | 0578 |           | SID<10:3> |        |        |        |        |                  | SID<2:0> — EXIDE — |          |       |       |                    | _     | EID<1 | 7:16> | xxxx  |               |

| C2RXF14EID | 057A | EID<15:8> |           |        |        |        |        | EID<7:0>         |                    |          |       |       |                    |       | xxxx  |       |       |               |

| C2RXF15SID | 057C |           | SID<10:3> |        |        |        |        |                  |                    | SID<2:0> |       | —     | EXIDE              | —     | EID<1 | 7:16> | xxxx  |               |

| C2RXF15EID | 057E | EID<15:8> |           |        |        |        |        | EID<7:0>         |                    |          |       |       |                    |       | xxxx  |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |

| POR (RCON<0>)     | POR                                                  | —                            |

### TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

| REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 |

|------------------------------------------------------|

|------------------------------------------------------|

| R/W-0           | R/W-0                                                                                                  | U-0                             | R/W-0            | R/W-0           | R/W-0           | R/W-0  | R/W-0   |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------|---------------------------------|------------------|-----------------|-----------------|--------|---------|--|--|

| T6IF            | DMA4IF                                                                                                 |                                 | OC8IF            | OC7IF           | OC6IF           | OC5IF  | IC6IF   |  |  |

| bit 15          | ÷                                                                                                      |                                 |                  |                 |                 |        | bit 8   |  |  |

| R/W-0           | R/W-0                                                                                                  | R/W-0                           | R/W-0            | R/W-0           | R/W-0           | R/W-0  | R/W-0   |  |  |

| IC5IF           | IC4IF                                                                                                  | IC3IF                           | DMA3IF           | C1IF            | C1RXIF          | SPI2IF | SPI2EIF |  |  |

| bit 7           |                                                                                                        |                                 |                  |                 |                 |        |         |  |  |

| Legend:         |                                                                                                        |                                 |                  |                 |                 |        |         |  |  |

| R = Readable    | ble bit W = Writable bit U = Unimplemented bit, read as '0'                                            |                                 |                  |                 |                 |        |         |  |  |

| -n = Value at F | ue at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unk                                         |                                 |                  |                 |                 |        |         |  |  |

| bit 15          | T6IF: Timer6                                                                                           | Interrupt Flag                  | Status bit       |                 |                 |        |         |  |  |

|                 |                                                                                                        | equest has oc                   |                  |                 |                 |        |         |  |  |

|                 | 0 = Interrupt r                                                                                        | equest has no                   | t occurred       |                 |                 |        |         |  |  |

| bit 14          |                                                                                                        |                                 |                  | complete Interr | upt Flag Status | bit    |         |  |  |

|                 | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |                                 |                  |                 |                 |        |         |  |  |

| bit 13          | •                                                                                                      | •                               |                  |                 |                 |        |         |  |  |

| bit 12          | Unimplemented: Read as '0'<br>OC8IF: Output Compare Channel 8 Interrupt Flag Status bit                |                                 |                  |                 |                 |        |         |  |  |

|                 | 1 = Interrupt request has occurred                                                                     |                                 |                  |                 |                 |        |         |  |  |

|                 |                                                                                                        | equest has no                   |                  |                 |                 |        |         |  |  |

| bit 11          | OC7IF: Output Compare Channel 7 Interrupt Flag Status bit                                              |                                 |                  |                 |                 |        |         |  |  |

|                 |                                                                                                        | equest has oc<br>equest has no  |                  |                 |                 |        |         |  |  |

| bit 10          | OC6IF: Output Compare Channel 6 Interrupt Flag Status bit                                              |                                 |                  |                 |                 |        |         |  |  |

|                 |                                                                                                        | equest has oc<br>equest has no  |                  |                 |                 |        |         |  |  |

| bit 9           | •                                                                                                      | •                               |                  | upt Flag Status | s bit           |        |         |  |  |

|                 |                                                                                                        | equest has oc<br>equest has no  |                  |                 |                 |        |         |  |  |

| bit 8           | IC6IF: Input C                                                                                         | apture Chann                    | el 6 Interrupt F | -lag Status bit |                 |        |         |  |  |

|                 |                                                                                                        | equest has oc<br>equest has no  |                  | -               |                 |        |         |  |  |

| bit 7           | •                                                                                                      | apture Chann                    |                  | -lag Status bit |                 |        |         |  |  |

|                 | 1 = Interrupt r                                                                                        | equest has oc                   | curred           | ·               |                 |        |         |  |  |

|                 |                                                                                                        | equest has no                   |                  |                 |                 |        |         |  |  |

| bit 6           | -                                                                                                      | Capture Chann                   | -                | lag Status bit  |                 |        |         |  |  |

|                 | •                                                                                                      | equest has oc<br>equest has no  |                  |                 |                 |        |         |  |  |

| bit 5           | -                                                                                                      | Capture Chann                   |                  | -lag Status bit |                 |        |         |  |  |

|                 | -                                                                                                      | request has oc                  |                  | lag olalao bit  |                 |        |         |  |  |

|                 | 0 = Interrupt r                                                                                        | equest has no                   | t occurred       |                 |                 |        |         |  |  |

| bit 4           | DMA3IF: DMA Channel 3 Data Transfer Complete Interrupt Flag Status bit                                 |                                 |                  |                 |                 |        |         |  |  |

|                 |                                                                                                        | equest has oc                   |                  |                 |                 |        |         |  |  |

|                 | 0 = Interrupt r                                                                                        | equest has no                   | Loccurred        |                 |                 |        |         |  |  |

| hit 0           | •                                                                                                      | •                               |                  | h:+             |                 |        |         |  |  |

| bit 3           | C1IF: ECAN1                                                                                            | Event Interrup<br>equest has oc | ot Flag Status   | bit             |                 |        |         |  |  |

# REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2 (CONTINUED)

| bit 2 | C1RXIF: ECAN1 Receive Data Ready Interrupt Flag Status bit |

|-------|------------------------------------------------------------|

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 1 | SPI2IF: SPI2 Event Interrupt Flag Status bit               |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

| bit 0 | SPI2EIF: SPI2 Error Interrupt Flag Status bit              |

|       | 1 = Interrupt request has occurred                         |

|       | 0 = Interrupt request has not occurred                     |

### REGISTER 7-15: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0           | R/W-1               | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------|---------------------|-----------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _             |                     | T1IP<2:0>                               |                 | —                |                 | OC1IP<2:0>      |       |

| bit 15        |                     |                                         |                 |                  |                 |                 | bit   |

|               |                     |                                         |                 |                  |                 |                 |       |

| U-0           | R/W-1               | R/W-0                                   | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|               |                     | IC1IP<2:0>                              |                 | —                |                 | INT0IP<2:0>     |       |

| bit 7         |                     |                                         |                 |                  |                 |                 | bit   |

| Legend:       |                     |                                         |                 |                  |                 |                 |       |

| R = Readable  | e bit               | W = Writable I                          | bit             | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR                 | '1' = Bit is set                        |                 | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

| bit 15        | Unimpleme           | nted: Read as 'o                        | ז'              |                  |                 |                 |       |

| bit 14-12     | -                   | Timer1 Interrupt                        |                 |                  |                 |                 |       |

|               |                     | upt is priority 7 (I                    |                 | ty interrupt)    |                 |                 |       |

|               | •                   |                                         | 0               | , i ,            |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               | •<br>001 = Interru  | upt is priority 1                       |                 |                  |                 |                 |       |

|               |                     | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 11        | Unimpleme           | nted: Read as 'o                        | )'              |                  |                 |                 |       |

| bit 10-8      | OC1IP<2:0>          | : Output Compa                          | re Channel 1    | Interrupt Prior  | ity bits        |                 |       |

|               | 111 = Interru       | upt is priority 7 (I                    | nighest priorit | ty interrupt)    |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               |                     | upt is priority 1                       |                 |                  |                 |                 |       |

|               | 000 <b>= Interr</b> | upt source is disa                      | abled           |                  |                 |                 |       |

| bit 7         | Unimpleme           | nted: Read as 'o                        | )'              |                  |                 |                 |       |

| bit 6-4       |                     | Input Capture C                         |                 |                  | oits            |                 |       |

|               | 111 = Interru       | upt is priority 7 (I                    | nighest priorit | ty interrupt)    |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               |                     | upt is priority 1<br>upt source is disa | abled           |                  |                 |                 |       |

| bit 3         |                     | nted: Read as '                         |                 |                  |                 |                 |       |

| bit 3-0       | -                   | : External Interr                       |                 | bite             |                 |                 |       |

| DIL 2-0       |                     | upt is priority 7 (h                    |                 |                  |                 |                 |       |

|               | •                   |                                         | gricor priorit  | , monupi)        |                 |                 |       |

|               | •                   |                                         |                 |                  |                 |                 |       |

|               | •<br>001 = Interru  |                                         |                 |                  |                 |                 |       |

|               |                     |                                         |                 |                  |                 |                 |       |

### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0           | R/W-1        | R/W-0                                    | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|---------------|--------------|------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

| _             |              | U1RXIP<2:0>                              |                 | —                |                 | SPI1IP<2:0>     |       |

| bit 15        |              |                                          |                 |                  |                 |                 | bit 8 |

|               |              |                                          |                 |                  |                 |                 |       |

| U-0           | R/W-1        | R/W-0                                    | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|               |              | SPI1EIP<2:0>                             |                 | —                |                 | T3IP<2:0>       |       |

| bit 7         |              |                                          |                 |                  |                 |                 | bit   |

| Legend:       |              |                                          |                 |                  |                 |                 |       |

| R = Readabl   | e bit        | W = Writable                             | bit             | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at | POR          | '1' = Bit is set                         |                 | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15        | Unimpleme    | ented: Read as '                         | 0'              |                  |                 |                 |       |

| bit 14-12     | -            | 0>: UART1 Rece                           |                 | Priority bits    |                 |                 |       |

|               |              | rupt is priority 7 (I                    | -               | -                |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               |              | rupt is priority 1                       |                 |                  |                 |                 |       |

|               | 000 = Interr | rupt source is dis                       | abled           |                  |                 |                 |       |

| bit 11        | Unimpleme    | ented: Read as '                         | 0'              |                  |                 |                 |       |

| bit 10-8      |              | >: SPI1 Event In                         | •               | •                |                 |                 |       |

|               | 111 = Interr | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               |              | rupt is priority 1<br>rupt source is dis | abled           |                  |                 |                 |       |

| bit 7         |              | ented: Read as '                         |                 |                  |                 |                 |       |

| bit 6-4       | SPI1EIP<2:   | :0>: SPI1 Error Ir                       | nterrupt Priori | ty bits          |                 |                 |       |

|               | 111 = Interr | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               |              | rupt is priority 1                       |                 |                  |                 |                 |       |

|               |              | rupt source is dis                       |                 |                  |                 |                 |       |

| bit 3         | -            | ented: Read as '                         |                 |                  |                 |                 |       |

| bit 2-0       |              | Timer3 Interrupt                         | -               |                  |                 |                 |       |

|               | 111 = Interr | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               | •            |                                          |                 |                  |                 |                 |       |

|               |              | rupt is priority 1                       | ablad           |                  |                 |                 |       |

|               | 000 = Interr | rupt source is dis                       | apled           |                  |                 |                 |       |

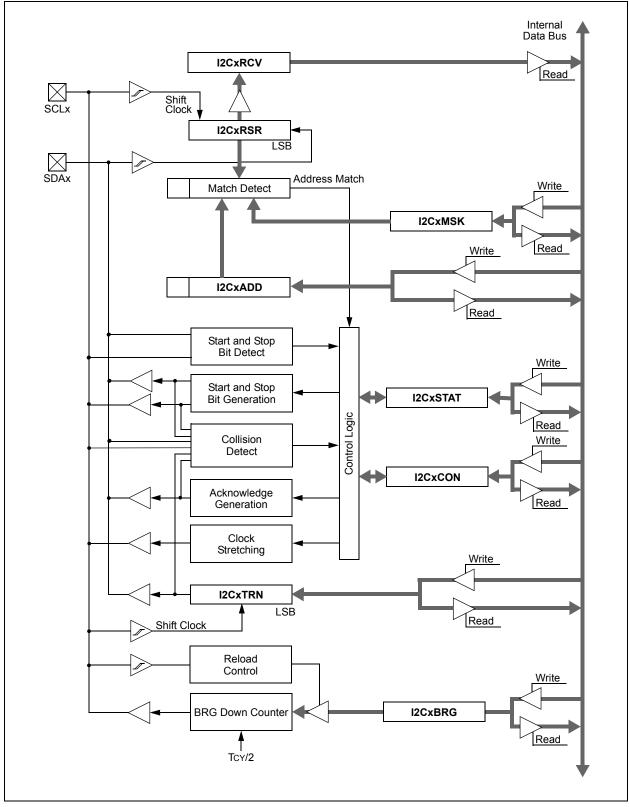

FIGURE 17-1:  $I^2 C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

| Bit Field | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP      | FBS      | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BSS<2:0>  | FBS      | <ul> <li>Boot Segment Program Flash Code Protection Size</li> <li>X11 = No Boot program Flash segment</li> <li>Boot space is 1K IW less VS</li> <li>110 = Standard security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>010 = High security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>Boot space is 4K IW less VS</li> <li>101 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> <li>000 = High security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> </ul> |

| RBS<1:0>  | FBS      | Boot Segment RAM Code Protection<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 Bytes<br>01 = Boot RAM is 256 Bytes<br>00 = Boot RAM is 1024 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SWRP      | FSS      | Secure Segment Program Flash Write Protection<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### TABLE 21-2: PIC24HJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION

### 24.2 AC Characteristics and Timing Parameters

This section defines PIC24HJXXXGPX06/X08/X10 AC characteristics and timing parameters.

### TABLE 24-14: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for IndustrialOperating voltage VDD range as described in Section 24.0 "Electrical |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | Characteristics"                                                                                                                                                                                                      |

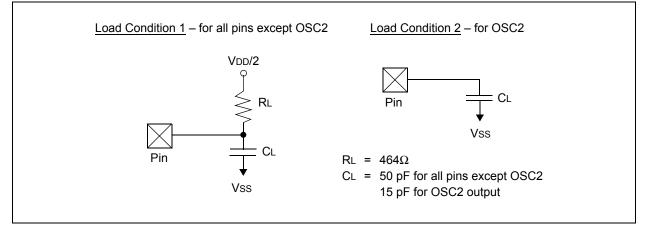

### FIGURE 24-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 24-15: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Тур | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosco  | OSC2/SOSCO pin        | _   | —   | 15  |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1 |

| DO56         | Сю     | All I/O pins and OSC2 | —   | —   | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            | —   |     | 400 | pF    | In l <sup>2</sup> C™ mode                                          |

### TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

|              |        |                                                                     |       |     | -                  |     |       | (unless otherwise stated)<br>for Industrial |

|--------------|--------|---------------------------------------------------------------------|-------|-----|--------------------|-----|-------|---------------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                      |       | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                  |

| OS50         | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |       | 0.8 |                    | 8   | MHz   | ECPLL, HSPLL, XTPLL<br>modes                |

| OS51         | Fsys   | On-Chip VCO System<br>Frequency                                     |       | 100 | _                  | 200 | MHz   |                                             |

| OS52         | TLOCK  | PLL Start-up Time (Lock                                             | Time) | 0.9 | 1.5                | 3.1 | mS    |                                             |

| OS53         | DCLK   | CLKO Stability (Jitter)                                             |       | -3  | 0.5                | 3   | %     | Measured over 100 ms<br>period              |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 24-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICSStandard Operating Conditions: $3.0V$ to $3.6V$ (unless otherwis<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                                     |     |     |     |       | -                                                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|-------|--------------------------------------------------------------|--|--|--|--|

| Param<br>No.                                                                                                                                                      | Characteristic                                      | Min | Тур | Max | Units | Conditions                                                   |  |  |  |  |

|                                                                                                                                                                   | Internal FRC Accuracy @ 7.3728 MHz <sup>(1,2)</sup> |     |     |     |       |                                                              |  |  |  |  |

| F20                                                                                                                                                               | FRC                                                 | -2  |     | +2  | %     | $-40^{\circ}C \le TA \le +85^{\circ}C \qquad VDD = 3.0-3.6V$ |  |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

2: FRC is set to initial frequency of 7.37 MHz (±2%) at 25°C.

### TABLE 24-19: INTERNAL RC ACCURACY

| АС СН        | ARACTERISTICS                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |     |       |                                                              |  |  |  |

|--------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------------------------------------------------|--|--|--|

| Param<br>No. | Characteristic                   | Min                                                                                                                                              | Тур | Max | Units | Conditions                                                   |  |  |  |

|              | LPRC @ 32.768 kHz <sup>(1)</sup> | 68 kHz <sup>(1)</sup>                                                                                                                            |     |     |       |                                                              |  |  |  |

| F21          | LPRC                             | -20                                                                                                                                              | ±6  | +20 | %     | $-40^{\circ}C \le TA \le +85^{\circ}C \qquad VDD = 3.0-3.6V$ |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

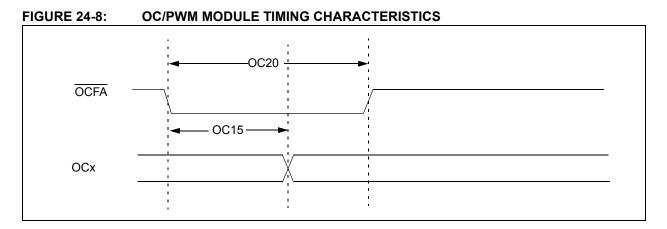

### TABLE 24-27: SIMPLE OC/PWM MODE TIMING REQUIREMENTS

|              |        |                                  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |   |    |    |   |  |

|--------------|--------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|---|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>    | Min Typ Max Units Conditions                                                                                                                    |   |    |    |   |  |

| OC15         | Tfd    | Fault Input to PWM I/O<br>Change | _                                                                                                                                               | _ | 50 | ns | _ |  |

| OC20         | TFLT   | Fault Input Pulse-Width          | 50                                                                                                                                              | _ | _  | ns | — |  |

Note 1: These parameters are characterized but not tested in manufacturing.

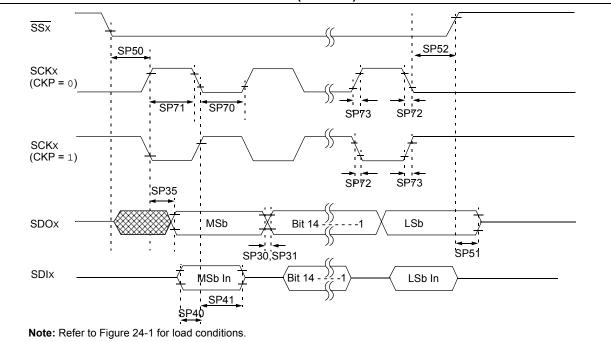

### FIGURE 24-11: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

### TABLE 24-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq \ TA \leq \ +85^{\circ}C \ for \ Industrial \end{array}$ |                    |     |       |                    |

|--------------------|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                                | Min                                                                                                                                                                                                                   | Тур <sup>(2)</sup> | Max | Units | Conditions         |

| SP70               | TscL                  | SCKx Input Low Time                                          | 30                                                                                                                                                                                                                    | —                  | _   | ns    | _                  |

| SP71               | TscH                  | SCKx Input High Time                                         | 30                                                                                                                                                                                                                    | _                  | _   | ns    | —                  |

| SP72               | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                          | —                                                                                                                                                                                                                     | 10                 | 25  | ns    | —                  |

| SP73               | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                          | —                                                                                                                                                                                                                     | 10                 | 25  | ns    | —                  |

| SP30               | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>                    | —                                                                                                                                                                                                                     | —                  | _   | ns    | See parameter D032 |

| SP31               | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>                    | —                                                                                                                                                                                                                     | _                  | _   | ns    | See parameter D031 |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                                                     | —                  | 30  | ns    | —                  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 20                                                                                                                                                                                                                    | —                  |     | ns    | —                  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 20                                                                                                                                                                                                                    | _                  |     | ns    | —                  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                                                   | —                  | _   | ns    | —                  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(3)</sup>        | 10                                                                                                                                                                                                                    | —                  | 50  | ns    | —                  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 Tcy + 40                                                                                                                                                                                                          | _                  |     | ns    | —                  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2**: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** Assumes 50 pF load on all SPIx pins.

### L

| VO Darta                                            | 100      |

|-----------------------------------------------------|----------|

| I/O Ports                                           |          |

| Parallel I/O (PIO)                                  |          |

| Write/Read Timing                                   | 140      |

| l <sup>2</sup> C                                    |          |

| Operating Modes                                     | 161      |

| Registers                                           | 161      |

| I <sup>2</sup> C Module                             |          |

| I2C1 Register Map                                   |          |

| I2C2 Register Map                                   |          |

| In-Circuit Debugger                                 |          |

| In-Circuit Emulation                                |          |

| In-Circuit Serial Programming (ICSP)                |          |

| Input Capture                                       | 215, 220 |

| Registers                                           | 150      |

|                                                     |          |

| Input Change Notification Module                    |          |

| Instruction Addressing Modes                        |          |

| File Register Instructions                          |          |

| Fundamental Modes Supported                         |          |

| MCU Instructions                                    |          |

| Move and Accumulator Instructions                   | 51       |

| Other Instructions                                  | 51       |

| Instruction Set                                     |          |

| Overview                                            | 224      |

| Summary                                             |          |