Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

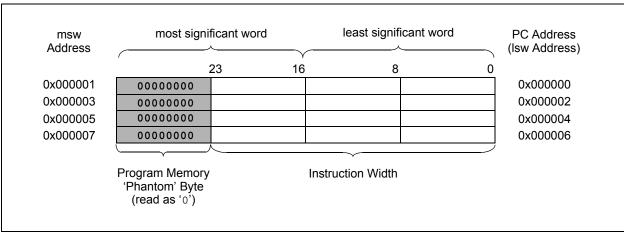

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All PIC24HJXXXGPX06/X08/X10 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

PIC24HJXXXGPX06/X08/X10 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table"**.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

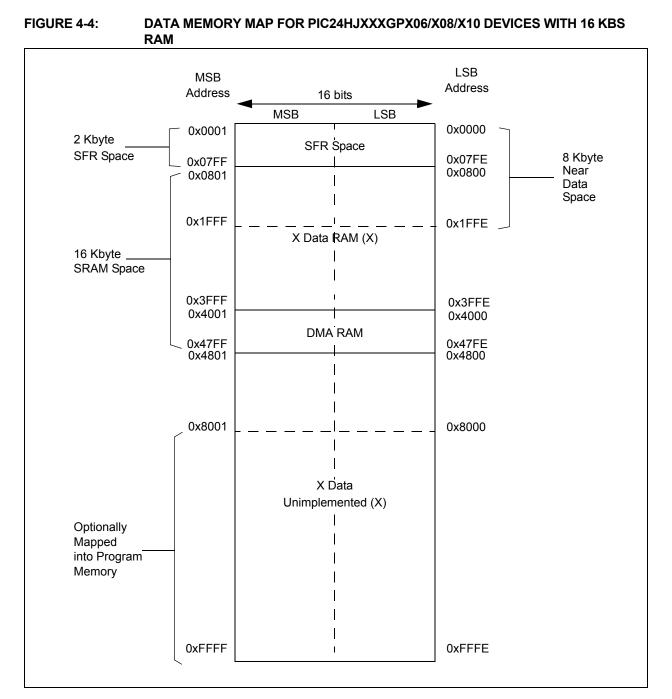

#### 4.2.5 DMA RAM

Every PIC24HJXXXGPX06/X08/X10 device contains 2 Kbytes of dual ported DMA RAM located at the end of data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

**Note:** DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

#### TABLE 4-31: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8    | Bit 7   | Bit 6   | Bit 5  | Bit 4      | Bit 3 | Bit 2     | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|----------|---------|---------|--------|------------|-------|-----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | —         | —      | —      | _      | —         | VREGS    | EXTR    | SWR     | SWDTEN | WDTO       | SLEEP | IDLE      | BOR     | POR   | <sub>XXXX</sub> (1) |

| OSCCON    | 0742 | —      | (      | COSC<2:0> | >      | —      | 1      | NOSC<2:0  | >        | CLKLOCK |         | LOCK   | _          | CF    | -         | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | >      | DOZEN  | FI     | RCDIV<2:0 | )>       | PLLPOS  | ST<1:0> | —      |            | í     | PLLPRE<4: | :0>     |       | 3040                |

| PLLFBD    | 0746 | —      | —      | _         | _      | _      |        | —         |          |         |         | F      | PLLDIV<8:( | )>    |           |         |       | 0030                |

| OSCTUN    | 0748 | _      | —      | _         | _      | _      |        | _         | TUN<5:0> |         |         |        | 0000       |       |           |         |       |                     |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

#### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------------|-------|-------|-------|-------|-------|--------|-------|---------------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | -     | —     | _           | ERASE | _     | _     |       | NVMO  | ><3:0> |       | <sub>0000</sub> (1) |

| NVMKEY    | 0766 | —      | _      | -      |        |        | -      | _     | _     | NVMKEY<7:0> |       |       |       |       |       | 0000   |       |                     |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-33: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | _      | _      | _     |       | —      | —     | —     |        | —      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0       R/W-1       R/W-0       U-0       U-0       U-0       U-0         —       DMA5IP<2:0>       —       —       —       —       —         bit 7       bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                          |                     |                 |                   |                   |                 |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|---------------------|-----------------|-------------------|-------------------|-----------------|-------|

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0       U-0         —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       Is                                                                                                                                                                                                                                                                                                                                            | U-0                               | U-0                      | U-0                 | U-0             | U-0               | U-0               | U-0             | U-0   |

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0       U-0         —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       Is                                                                                                                                                                                                                                                                                                                                            | —                                 | —                        | —                   | —               | —                 |                   | —               | _     |

| DMA5IP<2:0>       -       -       -       -       -         bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .                                                                       | bit 15                            |                          |                     |                 |                   |                   |                 | bit 8 |

| DMA5IP<2:0>       -       -       -       -       -         bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .                                                                       |                                   |                          |                     |                 |                   |                   |                 |       |

| bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       •       •         001 = Interrupt is priority 1       000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                               | R/W-1                    | R/W-0               | R/W-0           | U-0               | U-0               | U-0             | U-0   |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                                 |                          | DMA5IP<2:0>         |                 | —                 | —                 | —               | —     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         . <td>bit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit 0</td> | bit 7                             |                          |                     |                 |                   |                   |                 | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                          |                     |                 |                   |                   |                 |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Legend:                           |                          |                     |                 |                   |                   |                 |       |

| <pre>bit 15-7 Unimplemented: Read as '0' bit 6-4 DMA5IP&lt;2:0&gt;: DMA Channel 5 Data Transfer Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R = Readable bit W = Writable bit |                          |                     |                 | U = Unimplen      | nented bit, read  | as '0'          |       |

| bit 6-4 DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -n = Value at F                   | POR                      | '1' = Bit is set    |                 | '0' = Bit is clea | ared              | x = Bit is unkr | iown  |

| bit 6-4 DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |                          |                     |                 |                   |                   |                 |       |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 15-7                          | Unimplemen               | ted: Read as '0     | )'              |                   |                   |                 |       |

| •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 6-4                           | DMA5IP<2:0               | >: DMA Channe       | el 5 Data Trai  | nsfer Complete    | Interrupt Priorit | y bits          |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                          |                     |                 |                   |                   |                 |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | 111 = Interru            | ot is priority 7 (h | nighest priorit | y interrupt)      |                   |                 |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | 111 = Interruj<br>•      | ot is priority 7 (h | nighest priorit | y interrupt)      |                   |                 |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | 111 = Interruj<br>•<br>• | ot is priority 7 (h | ighest priorit  | y interrupt)      |                   |                 |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   | •                        |                     | iighest priorit | y interrupt)      |                   |                 |       |

| bit 2.0 Unimplemented: Read as 'o'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | •<br>•<br>001 = Interru  | ot is priority 1    |                 | y interrupt)      |                   |                 |       |

| bit 3-0 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   | •<br>•<br>001 = Interru  | ot is priority 1    |                 | y interrupt)      |                   |                 |       |

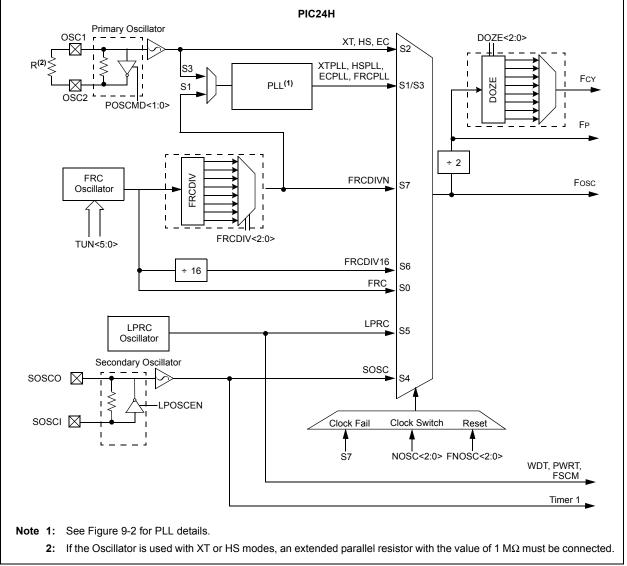

#### 9.0 **OSCILLATOR** CONFIGURATION

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 7. "Oscillator" (DS70227), which is available from the Microchip website (www.microchip.com)

The PIC24HJXXXGPX06/X08/X10 oscillator system provides:

· Various external and internal oscillator options as clock sources

FIGURE 9-1:

- · An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- · The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- · Programmable clock postscaler for system power savings

- · A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- · Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 9-1.

PIC24HJXXXGPX06/X08/X10 OSCILLATOR SYSTEM DIAGRAM

### 9.1 CPU Clocking System

There are seven system clock options provided by the PIC24HJXXXGPX06/X08/X10:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- 1. XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 2. HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 3. EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 24-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 21.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJXXXGPX06/X08/ X10 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

$FCY = \frac{FOSC}{2}$

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

NOTES:

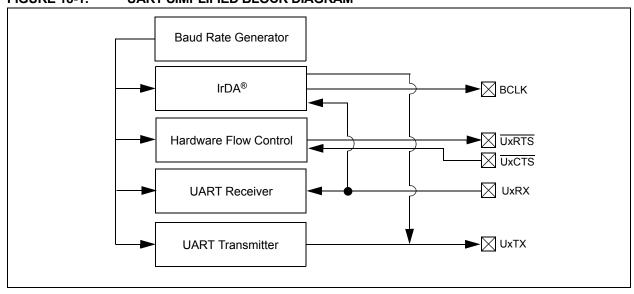

## 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 17. "UART" (DS70232), which is available from the Microchip website (www.microchip.com).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24HJXXXGPX06/X08/X10 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UXCTS and UXRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit Prescaler

- Baud rates ranging from 1 Mbps to 15 bps at 16x mode at 40 MIPS

- Baud rates ranging from 4 Mbps to 61 bps at 4x mode at 40 MIPS

- 4-deep First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UART Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA<sup>®</sup> Support

A simplified block diagram of the UART is shown in Figure 18-1. The UART module consists of the key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 18-1: UART SIMPLIFIED BLOCK DIAGRAM

- **Note 1:** Both UART1 and UART2 can trigger a DMA data transfer. If U1TX, U1RX, U2TX or U2RX is selected as a DMA IRQ source, a DMA transfer occurs when the U1TXIF, U1RXIF, U2TXIF or U2RXIF bit gets set as a result of a UART1 or UART2 transmission or reception.

- 2: If DMA transfers are required, the UART TX/RX FIFO buffer must be set to a size of 1 byte/word (i.e., UTXISEL<1:0> = 00 and URXISEL<1:0> = 00).

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                     |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                                 |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

**Note 1:** Refer to **Section 17. "UART"** (DS70232) in the *"PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

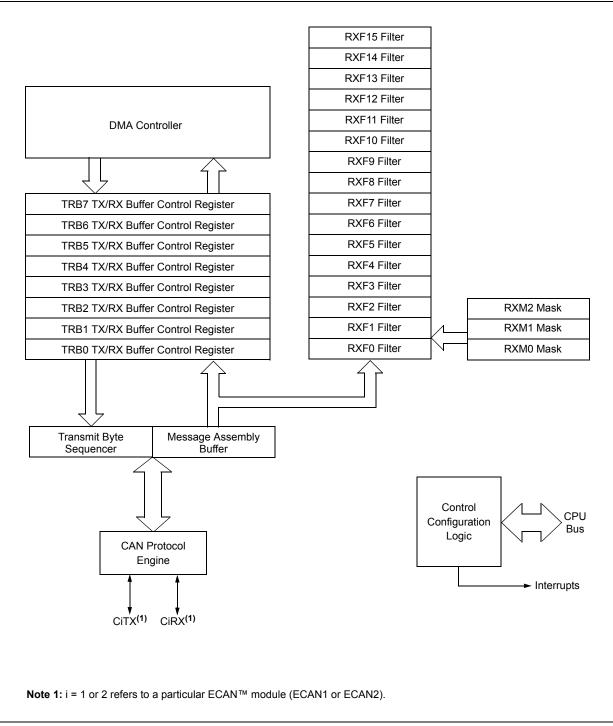

### FIGURE 19-1: ECAN™ MODULE BLOCK DIAGRAM

#### REGISTER 19-22: CiRXFUL1: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                            |                    |

|-------------------|--------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 19-23: CIRXFUL2: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  | •       |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1 (where x = 1 or 2) (CONTINUED)

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                  |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                          |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software may write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software may write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul> |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>1 = ADC conversion cycle is completed.</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when analog-to-digital conversion is complete. Software may write '0' to clear DONE status (software not allowed to write '1'). Clearing this bit will NOT affect any operation</li> </ul>                                                                   |

in progress. Automatically cleared by hardware at start of a new conversion.

#### REGISTER 20-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0                                     | U-0 | U-0              | U-0 | U-0                                | U-0        | U-0            | U-0   |  |

|-----------------------------------------|-----|------------------|-----|------------------------------------|------------|----------------|-------|--|

| —                                       | —   | —                | —   | —                                  | —          | —              | —     |  |

| bit 15                                  |     |                  |     |                                    |            |                | bit 8 |  |

|                                         |     |                  |     |                                    |            |                |       |  |

| U-0                                     | U-0 | U-0              | U-0 | U-0                                | R/W-0      | R/W-0          | R/W-0 |  |

| —                                       | —   | —                | —   | —                                  | DMABL<2:0> |                |       |  |

| bit 7                                   | •   |                  |     |                                    |            |                | bit 0 |  |

|                                         |     |                  |     |                                    |            |                |       |  |

| Legend:                                 |     |                  |     |                                    |            |                |       |  |

| R = Readable bit W = Writable bit U = U |     |                  |     | U = Unimplemented bit, read as '0' |            |                |       |  |

| -n = Value at P                         | POR | '1' = Bit is set |     | '0' = Bit is cle                   | eared      | x = Bit is unk | nown  |  |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

| Bit Field   | Register | Description                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IESO        | FOSCSEL  | Internal External Start-up Option bit<br>1 = Start-up device with FRC, then automatically switch to the user-selected<br>oscillator source when ready<br>0 = Start-up device with user-selected oscillator source                                                                                                                                        |

| FNOSC<2:0>  | FOSCSEL  | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Reserved<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |

| FCKSM<1:0>  | FOSC     | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                        |

| OSCIOFNC    | FOSC     | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                             |

| POSCMD<1:0> | FOSC     | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                           |

| FWDTEN      | FWDT     | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                    |

| WINDIS      | FWDT     | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                           |

| WDTPRE      | FWDT     | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                                    |

| WDTPOST     | FWDT     | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>0001 = 1:2<br>0000 = 1:1                                                                                                                                                                                                                                                         |

#### TABLE 21-2: PIC24HJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

|                    | E 22-2:              |        |                 |                                                   |               |                |                          |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 35                 | INC                  | INC    | f               | f = f + 1                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG          | WREG = f + 1                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd           | Wd = Ws + 1                                       | 1             | 1              | C,DC,N,OV,Z              |

| 36                 | INC2                 | INC2   | f               | f = f + 2                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG          | WREG = f + 2                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd           | Wd = Ws + 2                                       | 1             | 1              | C,DC,N,OV,Z              |

| 37                 | IOR                  | IOR    | f               | f = f .IOR. WREG                                  | 1             | 1              | N,Z                      |

|                    |                      | IOR    | f,WREG          | WREG = f .IOR. WREG                               | 1             | 1              | N,Z                      |

|                    |                      | IOR    | #lit10,Wn       | Wd = lit10 .IOR. Wd                               | 1             | 1              | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd        | Wd = Wb .IOR. Ws                                  | 1             | 1              | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd     | Wd = Wb .IOR. lit5                                | 1             | 1              | N,Z                      |

| 38                 | LNK                  | LNK    | #lit14          | Link Frame Pointer                                | 1             | 1              | None                     |

| 39                 | LSR                  | LSR    | f               | f = Logical Right Shift f                         | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG          | WREG = Logical Right Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd           | Wd = Logical Right Shift Ws                       | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd      | Wnd = Logical Right Shift Wb by Wns               | 1             | 1              | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd    | Wnd = Logical Right Shift Wb by lit5              | 1             | 1              | N,Z                      |

| 40                 | MOV                  | MOV    | f,Wn            | Move f to Wn                                      | 1             | 1              | None                     |

|                    |                      | MOV    | f               | Move f to f                                       | 1             | 1              | N,Z                      |

|                    |                      | MOV    | f,WREG          | Move f to WREG                                    | 1             | 1              | N,Z                      |

|                    |                      | MOV    | #lit16,Wn       | Move 16-bit literal to Wn                         | 1             | 1              | None                     |

|                    |                      | MOV.b  | #lit8,Wn        | Move 8-bit literal to Wn                          | 1             | 1              | None                     |

|                    |                      | MOV    | Wn,f            | Move Wn to f                                      | 1             | 1              | None                     |

|                    |                      | MOV    | Wso,Wdo         | Move Ws to Wd                                     | 1             | 1              | None                     |

|                    |                      | MOV    | WREG, f         | Move WREG to f                                    | 1             | 1              | N,Z                      |

|                    |                      | MOV.D  | Wns,Wd          | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |

|                    |                      | MOV.D  | Ws,Wnd          | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2              | None                     |

| 41                 | MUL                  | MUL.SS | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |

|                    |                      | MUL.SU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.SU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1             | 1              | None                     |

|                    |                      | MUL.UU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL    | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 42                 | NEG                  | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 43                 | NOP                  | NOP    |                 | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1             | 1              | None                     |

| 44                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 45                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1             | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 46                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic | Assembly Syntax Description |             | Description                  | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-----------------------------|-------------|------------------------------|---------------|----------------|--------------------------|

| 66                 | TBLRDL               | TBLRDL                      | Ws,Wd       | Read Prog<15:0> to Wd        | 1             | 2              | None                     |

| 67                 | TBLWTH               | TBLWTH                      | Ws,Wd       | Write Ws<7:0> to Prog<23:16> | 1             | 2              | None                     |

| 68                 | TBLWTL               | TBLWTL                      | Ws,Wd       | Write Ws to Prog<15:0>       | 1             | 2              | None                     |

| 69                 | ULNK                 | ULNK                        |             | Unlink Frame Pointer         | 1             | 1              | None                     |

| 70                 | XOR                  | XOR                         | f           | f = f .XOR. WREG             | 1             | 1              | N,Z                      |

|                    |                      | XOR                         | f,WREG      | WREG = f .XOR. WREG          | 1             | 1              | N,Z                      |

|                    |                      | XOR                         | #lit10,Wn   | Wd = lit10 .XOR. Wd          | 1             | 1              | N,Z                      |

|                    |                      | XOR                         | Wb,Ws,Wd    | Wd = Wb .XOR. Ws             | 1             | 1              | N,Z                      |

|                    |                      | XOR                         | Wb,#lit5,Wd | Wd = Wb .XOR. lit5           | 1             | 1              | N,Z                      |

| 71                 | ZE                   | ZE                          | Ws,Wnd      | Wnd = Zero-extend Ws         | 1             | 1              | C,Z,N                    |

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### TABLE 24-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHARACTERISTICS |                               |                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |     |       |                           |  |

|--------------------|-------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|---------------------------|--|

| Param<br>No.       | Symbol Characteristic Min Ivi |                     |                                                                                                                                                 | Тур | Max | Units | Conditions                |  |

|                    | Vol                           | Output Low Voltage  |                                                                                                                                                 |     |     |       |                           |  |

| DO10               |                               | I/O ports           | _                                                                                                                                               | —   | 0.4 | V     | IOL = 2 mA, VDD = 3.3V    |  |

| DO16               |                               | OSC2/CLKO           | —                                                                                                                                               | —   | 0.4 | V     | IOL = 2 mA, VDD = 3.3V    |  |

|                    | Voн                           | Output High Voltage |                                                                                                                                                 |     |     |       |                           |  |

| DO20               |                               | I/O ports           | 2.40                                                                                                                                            | —   | —   | V     | Iон = -2.3 mA, Vdd = 3.3V |  |

| DO26               |                               | OSC2/CLKO           | 2.41                                                                                                                                            | _   | —   | V     | Iон = -1.3 mA, Vdd = 3.3V |  |

#### TABLE 24-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                                                                 | Standard Opera<br>(unless otherw<br>Operating temp | ise state          | ed) |                    |       | Industrial |

|--------------------|--------|-------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------|-----|--------------------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                                                                                  |                                                    | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low<br>BOR event is tied to VDD core voltage<br>decrease |                                                    | 2.40               | _   | 2.55               | V     | _          |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

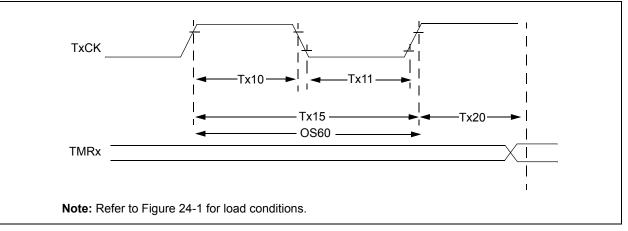

#### FIGURE 24-5: TIMER1, 2, 3, 4, 5, 6, 7, 8 AND 9 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CHARACTERISTICS (I |                       |                                                                |                                                                |       | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |         |       |                                          |  |  |