Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp506t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin NameAN0-AN31AVDDAVssCLKICLKOCN0-CN23 | Pin           Type           I           P           I           O | Buffer<br>Type<br>Analog<br>P<br>P<br>ST/CMOS<br>—<br>ST | Description           Analog input channels.           Positive supply for analog modules. This pin must be connected at all times.           Ground reference for analog modules.           External clock source input. Always associated with OSC1 pin function.           Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |  |  |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| AVDD<br>AVSS<br>CLKI<br>CLKO             | P<br>P<br>I<br>O                                                   | P<br>P<br>ST/CMOS<br>—                                   | Positive supply for analog modules. This pin must be connected at all times.<br>Ground reference for analog modules.<br>External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                  |  |  |  |  |  |  |  |  |

| AVss<br>CLKI<br>CLKO                     | P<br>I<br>O                                                        | P<br>ST/CMOS<br>—                                        | Ground reference for analog modules.<br>External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| CLKI<br>CLKO                             | <br>0<br>                                                          | ST/CMOS<br>—                                             | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| CLKO                                     | 0                                                                  | _                                                        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| CN0-CN23                                 |                                                                    | ST                                                       | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator<br>mode. Optionally functions as CLKO in RC and EC modes. Always associate<br>with OSC2 pin function.                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                                          |                                                                    |                                                          | Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| C1RX                                     |                                                                    | ST                                                       | ECAN1 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| C1TX                                     | 0                                                                  | —                                                        | ECAN1 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| C2RX                                     | I                                                                  | ST                                                       | ECAN2 bus receive pin.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| C2TX                                     | 0                                                                  | —                                                        | ECAN2 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| PGED1                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 1.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| PGEC1                                    | I                                                                  | ST                                                       | Clock input pin for programming/debugging communication channel 1.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| PGED2                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 2.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| PGEC2                                    | I                                                                  | ST                                                       | Clock input pin for programming/debugging communication channel 2.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| PGED3                                    | I/O                                                                | ST                                                       | Data I/O pin for programming/debugging communication channel 3.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| PGEC3                                    |                                                                    | ST                                                       | Clock input pin for programming/debugging communication channel 3.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| IC1-IC8                                  | I                                                                  | ST                                                       | Capture inputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| INT0                                     |                                                                    | ST                                                       | External interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| INT1                                     | I                                                                  | ST                                                       | External interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| INT2                                     | I                                                                  | ST                                                       | External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| INT3                                     | I                                                                  | ST                                                       | External interrupt 3.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| INT4                                     | I                                                                  | ST                                                       | External interrupt 4.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| MCLR                                     | I/P                                                                | ST                                                       | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| OCFA                                     | I                                                                  | ST                                                       | Compare Fault A input (for Compare Channels 1, 2, 3 and 4).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| OCFB                                     | I                                                                  | ST                                                       | Compare Fault B input (for Compare Channels 5, 6, 7 and 8).                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| OC1-OC8                                  | 0                                                                  | —                                                        | Compare outputs 1 through 8.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| OSC1                                     | I                                                                  | ST/CMOS                                                  | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| OSC2                                     | I/O                                                                | —                                                        | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| RA0-RA7                                  | I/O                                                                | ST                                                       | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RA9-RA10                                 | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| RA12-RA15                                | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| RB0-RB15                                 | I/O                                                                | ST                                                       | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RC1-RC4                                  | I/O                                                                | ST                                                       | PORTC is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RC12-RC15                                | I/O                                                                | ST                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| RD0-RD15                                 | I/O                                                                | ST                                                       | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RE0-RE7                                  | I/O                                                                | ST                                                       | PORTE is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RF0-RF8<br>RF12-RF13                     | I/O                                                                | ST                                                       | PORTF is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RG0-RG3<br>RG6-RG9                       | I/O<br>I/O                                                         | ST<br>ST                                                 | PORTG is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| RG12-RG15<br>Legend: CMOS                | 1/0                                                                | ST                                                       | e input or output Analog = Analog input P = Power                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| TABLE 1-1: | <b>PINOUT I/O DESCRIPTIONS</b> |

|------------|--------------------------------|

|------------|--------------------------------|

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog inputP = PowerO = OutputI = Input

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6     | Bit 5     | Bit 4         | Bit 3      | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

|----------|-------------|--------|-------------------------|--------|--------|--------|--------|---------|---------------|--------------|-----------|-----------|---------------|------------|--------------|---------|--------|---------------|

| WREG0    | 0000        |        |                         | •      |        |        | •      | •       | Working Re    | egister 0    |           |           |               |            |              |         | •      | 0000          |

| WREG1    | 0002        |        |                         |        |        |        |        |         | Working Re    | egister 1    |           |           |               |            |              |         |        | 0000          |

| WREG2    | 0004        |        |                         |        |        |        |        |         | Working Re    | egister 2    |           |           |               |            |              |         |        | 0000          |

| WREG3    | 0006        |        |                         |        |        |        |        |         | Working Re    | egister 3    |           |           |               |            |              |         |        | 0000          |

| WREG4    | 0008        |        | Working Register 4      |        |        |        |        |         |               |              |           |           |               | 0000       |              |         |        |               |

| WREG5    | 000A        |        | Working Register 5      |        |        |        |        |         |               |              |           |           |               | 0000       |              |         |        |               |

| WREG6    | 000C        |        | Working Register 6 0    |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG7    | 000E        |        | Working Register 7 00   |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG8    | 0010        |        | Working Register 8 0    |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG9    | 0012        |        | Working Register 9 0    |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG10   | 0014        |        | Working Register 10 00  |        |        |        |        |         |               |              |           |           |               | 0000       |              |         |        |               |

| WREG11   | 0016        |        | Working Register 11 000 |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG12   | 0018        |        | Working Register 12 c   |        |        |        |        |         |               |              |           |           | 0000          |            |              |         |        |               |

| WREG13   | 001A        |        |                         |        |        |        |        |         | Working Re    | gister 13    |           |           |               |            |              |         |        | 0000          |

| WREG14   | 001C        |        |                         |        |        |        |        |         | Working Re    | gister 14    |           |           |               |            |              |         |        | 0000          |

| WREG15   | 001E        |        |                         |        |        |        |        |         | Working Re    | •            |           |           |               |            |              |         |        | 0800          |

| SPLIM    | 0020        |        |                         |        |        |        |        | Sta     | ck Pointer Li | mit Register | -         |           |               |            |              |         |        | xxxx          |

| PCL      | 002E        |        |                         | •      |        |        | •      | Program | Counter Lo    | w Word Reg   | gister    |           |               |            |              |         |        | 0000          |

| PCH      | 0030        | _      | _                       | —      | _      | _      | —      | _       | _             |              |           |           | m Counter     |            | -            |         |        | 0000          |

| TBLPAG   | 0032        | _      | _                       | —      | _      | _      | —      | _       | _             |              |           |           | Page Addre    |            | •            |         |        | 0000          |

| PSVPAG   | 0034        | —      | —                       | —      | —      | —      | —      | —       | —             |              |           | am Memory | Visibility Pa | age Addres | s Pointer Re | egister |        | 0000          |

| RCOUNT   | 0036        |        |                         |        |        |        |        | Repe    | at Loop Cou   | unter Regist |           |           | 1             |            | 1            | 1       | 1      | XXXX          |

| SR       | 0042        | _      | _                       | _      | _      | _      | _      |         | DC            |              | IPL<2:0>  |           | RA            | N          | OV           | Z       | С      | 0000          |

| CORCON   | 0044        | _      | _                       | -      | —      | —      | -      | —       | —             | —            | —         | —         | —             | IPL3       | PSV          | —       | —      | 0000          |

| DISICNT  | 0052        | _      | _                       |        |        |        |        |         | Disable       | e Interrupts | Counter R | egister   |               |            |              | 1       |        | xxxx          |

| BSRAM    | 0750        |        | —                       | —      | —      | —      | -      | —       | —             | —            | —         | —         | —             | —          | IW_BSR       | IR_BSR  | RL_BSR | 0000          |

| SSRAM    | 0752        |        | -                       | -      | —      | -      | —      | -       | —             | —            | —         | —         | —             | —          | IW_SSR       | IR_SSR  | RL_SSR | 0000          |

### TABLE 4-1: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

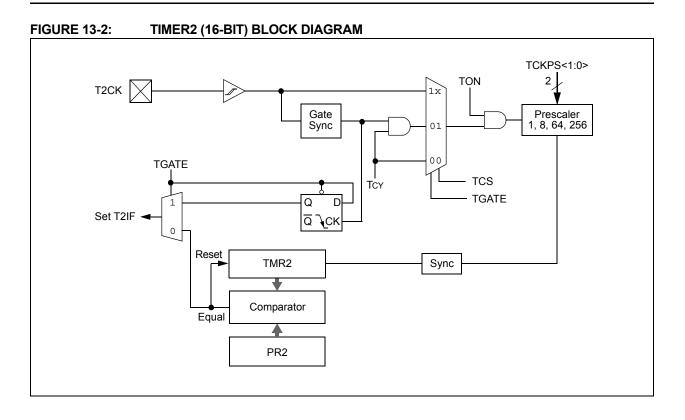

| TABLE       | 4-6:        | : TIMER REGISTER MAP |                                                      |        |        |        |        |              |               |                |                |       |        |       |       |       |       |               |

|-------------|-------------|----------------------|------------------------------------------------------|--------|--------|--------|--------|--------------|---------------|----------------|----------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15               | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8         | Bit 7          | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |                      |                                                      |        |        |        |        |              | Timer1        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR1         | 0102        |                      |                                                      |        |        |        |        |              | Period F      | Register 1     |                |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> |       | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |                      |                                                      |        |        |        |        |              | Timer2        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108        |                      |                                                      |        |        |        | Tim    | ner3 Holding | Register (for | 32-bit timer   | operations o   | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |                      |                                                      |        |        |        |        |              | Timer3        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR2         | 010C        |                      |                                                      |        |        |        |        |              | Period F      | Register 2     |                |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |                      | Period Register 3                                    |        |        |        |        |              |               |                |                |       | FFFF   |       |       |       |       |               |

| T2CON       | 0110        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T3CON       | 0112        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   | _     | 0000          |

| TMR4        | 0114        |                      |                                                      | •      | •      |        |        | •            | Timer4        | Register       |                |       |        |       |       | •     | •     | xxxx          |

| TMR5HLD     | 0116        |                      | Timer5 Holding Register (for 32-bit operations only) |        |        |        |        |              |               |                |                |       |        | xxxx  |       |       |       |               |

| TMR5        | 0118        |                      | Timer5 Register x                                    |        |        |        |        |              |               |                |                |       | xxxx   |       |       |       |       |               |

| PR4         | 011A        |                      | Period Register 4                                    |        |        |        |        |              |               |                |                |       | FFFF   |       |       |       |       |               |

| PR5         | 011C        | Period Register 5    |                                                      |        |        |        |        |              |               |                | FFFF           |       |        |       |       |       |       |               |

| T4CON       | 011E        | TON                  |                                                      | TSIDL  | —      | _      | _      | —            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | —     | 0000          |

| T5CON       | 0120        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | —     | TCS   | _     | 0000          |

| TMR6        | 0122        |                      |                                                      |        |        |        |        |              | Timer6        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR7HLD     | 0124        |                      |                                                      |        |        |        |        | Timer7 Hold  | ing Register  | (for 32-bit op | perations only | y)    |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |                      |                                                      |        |        |        |        |              | Timer7        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR6         | 0128        |                      |                                                      |        |        |        |        |              | Period F      | Register 6     |                |       |        |       |       |       |       | FFFF          |

| PR7         | 012A        |                      |                                                      |        |        |        |        |              | Period F      | Register 7     |                |       |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T7CON       | 012E        | TON                  |                                                      | TSIDL  | _      | _      | _      | _            | —             | _              | TGATE          | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        |                      |                                                      |        |        |        |        |              | Timer8        | Register       |                |       |        |       |       |       |       | xxxx          |

| TMR9HLD     | 0132        |                      |                                                      |        |        |        | -      | Timer9 Hold  | ing Register  | (for 32-bit op | perations only | y)    |        |       |       |       |       | xxxx          |

| TMR9        | 0134        |                      |                                                      |        |        |        |        |              | Timer9        | Register       |                |       |        |       |       |       |       | xxxx          |

| PR8         | 0136        |                      |                                                      |        |        |        |        |              | Period F      | Register 8     |                |       |        |       |       |       |       | FFFF          |

| PR9         | 0138        |                      |                                                      |        |        |        |        |              | Period F      | Register 9     |                |       |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON                  | _                                                    | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | T32   |       | TCS   | _     | 0000          |

| T9CON       | 013C        | TON                  | _                                                    | TSIDL  | _      | _      | _      | _            | _             | _              | TGATE          | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| L           |             |                      |                                                      |        |        |        |        |              |               |                |                | 1     |        |       |       |       |       |               |

#### . . TIMED DECIGTED MAD

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### 6.0 RESET

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 8. "Reset" (DS70229), which is available from the Microchip website (www.microchip.com).

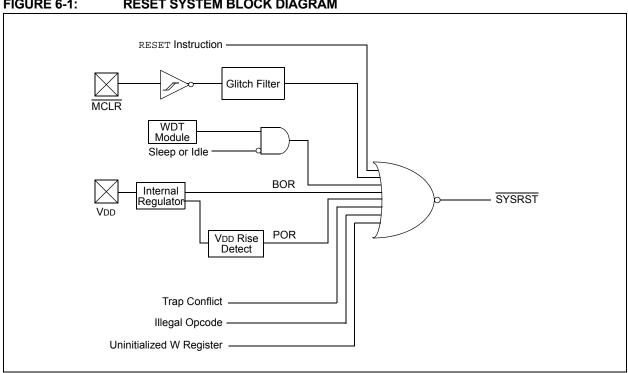

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- · WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W **Register Reset**

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

Refer to the specific peripheral or CPU Note: section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the POR bit (RCON<0>), that are set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

### REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | XWCOL3: Channel 3 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected        |

|-------|------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | XWCOL2: Channel 2 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected        |

| bit 1 | <b>XWCOL1:</b> Channel 1 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected |

| bit 0 | XWCOL0: Channel 0 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected        |

### REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit<br>1 = Output Compare 4 module is disabled<br>0 = Output Compare 4 module is enabled |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                                                      |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul>                               |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                                                      |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul>                               |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                                                      |

|       | 1 = Output Compare 1 module is disabled                                                                                                |

|       | 0 = Output Compare 1 module is enabled                                                                                                 |

|       |                                                                                                                                        |

### REGISTER 19-22: CiRXFUL1: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                            |                    |

|-------------------|--------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 19-23: CIRXFUL2: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  | •       |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

### REGISTER 19-26: CiTRmnCON: ECAN™ MODULE TX/RX BUFFER m CONTROL REGISTER

| R/W-0        | R-0                                                              | R-0                                                                    | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0         |  |  |  |  |

|--------------|------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------|------------------|--------------------|-----------------|---------------|--|--|--|--|

| TXENn        | TXABTn                                                           | TXLARBn                                                                | TXERRn                        | TXREQn           | RTRENn             | TXnPF           | RI<1:0>       |  |  |  |  |

| bit 15       |                                                                  | I                                                                      |                               |                  |                    |                 | bit           |  |  |  |  |

|              |                                                                  |                                                                        |                               |                  |                    |                 |               |  |  |  |  |

| R/W-0        | R-0                                                              | R-0                                                                    | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0         |  |  |  |  |

| TXENm        | TXABTm <sup>(1)</sup>                                            | TXLARBm <sup>(1)</sup>                                                 | TXERRm <sup>(1)</sup>         | TXREQm           | RTRENm             | TXmPF           |               |  |  |  |  |

| bit 7        |                                                                  |                                                                        |                               |                  |                    |                 | bit           |  |  |  |  |

| Legend:      |                                                                  |                                                                        |                               |                  |                    |                 |               |  |  |  |  |

| R = Readab   | le bit                                                           | W = Writable                                                           | bit                           | U = Unimpler     | mented bit, read   | as '0'          |               |  |  |  |  |

| -n = Value a | t POR                                                            | '1' = Bit is set                                                       |                               | '0' = Bit is cle | ared               | x = Bit is unkr | nown          |  |  |  |  |

|              |                                                                  |                                                                        |                               |                  |                    |                 |               |  |  |  |  |

| bit 15-8     | See Definitio                                                    | n for Bits 7-0,                                                        | Controls Buff                 | fer n            |                    |                 |               |  |  |  |  |

| bit 7        |                                                                  | RX Buffer Sele                                                         |                               |                  |                    |                 |               |  |  |  |  |

|              |                                                                  | Bn is a transmi<br>Bn is a receive                                     |                               |                  |                    |                 |               |  |  |  |  |

| bit 6        |                                                                  | essage Aborted                                                         |                               |                  |                    |                 |               |  |  |  |  |

|              | 1 = Message                                                      | •                                                                      | - Dit                         |                  |                    |                 |               |  |  |  |  |

|              |                                                                  | completed trar                                                         | smission succ                 | essfully         |                    |                 |               |  |  |  |  |

| bit 5        | TXLARBm:                                                         | Message Lost                                                           | Arbitration bit <sup>(1</sup> | )                |                    |                 |               |  |  |  |  |

|              |                                                                  | lost arbitration<br>did not lose arl                                   |                               |                  |                    |                 |               |  |  |  |  |

| bit 4        | •                                                                | ror Detected D                                                         |                               | •                |                    |                 |               |  |  |  |  |

|              |                                                                  | or occurred whi                                                        | •                             | •                |                    |                 |               |  |  |  |  |

| bit 3        |                                                                  | or did not occui<br>essage Send F                                      |                               | saye was bei     | ng sent            |                 |               |  |  |  |  |

| DIL D        |                                                                  | •                                                                      | •                             | essage The h     | it will automatica | ally clear when | the message   |  |  |  |  |

|              |                                                                  |                                                                        |                               |                  | equest a messag    |                 | i ilio moodag |  |  |  |  |

| bit 2        | RTRENm: Au                                                       | ito-Remote Tra                                                         | nsmit Enable b                | oit              |                    |                 |               |  |  |  |  |

|              |                                                                  | emote transmit                                                         | ,                             |                  |                    |                 |               |  |  |  |  |

|              | 0 = When a remote transmit is received, TXREQ will be unaffected |                                                                        |                               |                  |                    |                 |               |  |  |  |  |

| bit 1-0      |                                                                  | >: Message Tr                                                          |                               | iority bits      |                    |                 |               |  |  |  |  |

|              |                                                                  | message priori                                                         |                               |                  |                    |                 |               |  |  |  |  |

|              |                                                                  | 10 = High intermediate message priority                                |                               |                  |                    |                 |               |  |  |  |  |

|              |                                                                  | 01 = Low intermediate message priority<br>00 = Lowest message priority |                               |                  |                    |                 |               |  |  |  |  |

Note 1: This bit is cleared when TXREQ is set.

### TABLE 24-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT                             | ERISTICS               |     | (unless oth | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |         |  |  |  |

|----------------------------------------|------------------------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|--|--|--|

| Parameter<br>No.                       | Typical <sup>(1)</sup> | Мах | Units       | Conditions                                                                                                                                              |      |         |  |  |  |

| Operating Current (IDD) <sup>(2)</sup> |                        |     |             |                                                                                                                                                         |      |         |  |  |  |

| DC20d                                  | 27                     | 30  | mA          | -40°C                                                                                                                                                   |      |         |  |  |  |

| DC20a                                  | 27                     | 30  | mA          | +25°C                                                                                                                                                   | 3.3V | 10 MIPS |  |  |  |

| DC20b                                  | 27                     | 30  | mA          | +85°C                                                                                                                                                   | _    |         |  |  |  |

| DC21d                                  | 36                     | 40  | mA          | -40°C                                                                                                                                                   |      |         |  |  |  |

| DC21a                                  | 37                     | 40  | mA          | +25°C                                                                                                                                                   | 3.3V | 16 MIPS |  |  |  |

| DC21b                                  | 38                     | 45  | mA          | +85°C                                                                                                                                                   | _    |         |  |  |  |

| DC22d                                  | 43                     | 50  | mA          | -40°C                                                                                                                                                   |      |         |  |  |  |

| DC22a                                  | 46                     | 50  | mA          | +25°C                                                                                                                                                   | 3.3V | 20 MIPS |  |  |  |

| DC22b                                  | 46                     | 55  | mA          | +85°C                                                                                                                                                   | _    |         |  |  |  |

| DC23d                                  | 65                     | 70  | mA          | -40°C                                                                                                                                                   |      | 1       |  |  |  |

| DC23a                                  | 65                     | 70  | mA          | +25°C                                                                                                                                                   | 3.3V | 30 MIPS |  |  |  |

| DC23b                                  | 65                     | 70  | mA          | +85°C                                                                                                                                                   |      |         |  |  |  |

| DC24d                                  | 84                     | 90  | mA          | -40°C                                                                                                                                                   |      |         |  |  |  |

| DC24a                                  | 84                     | 90  | mA          | +25°C                                                                                                                                                   | 3.3V | 40 MIPS |  |  |  |

| DC24b                                  | 84                     | 90  | mA          | +85°C                                                                                                                                                   |      |         |  |  |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail to rail. All I/O pins are configured as inputs and pulled to Vss. MCLR = VDD, WDT and FSCM are disabled. CPU, SRAM, program memory and data memory are operational. No peripheral modules are operating; however, every peripheral is being clocked (PMD bits are all zeroed).

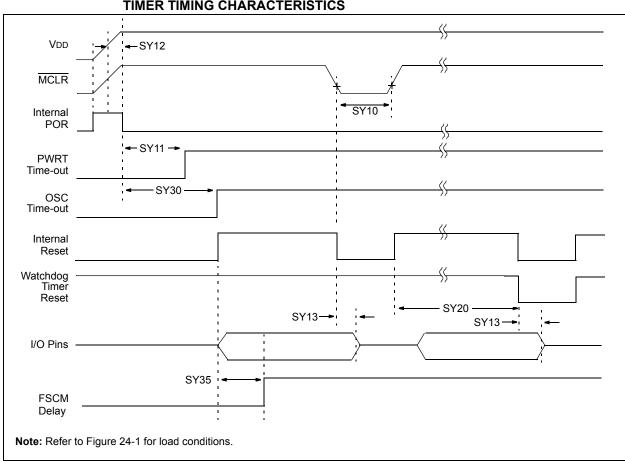

### FIGURE 24-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

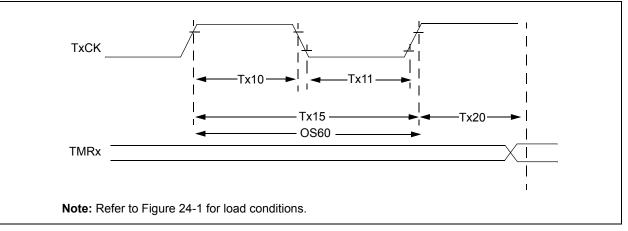

#### FIGURE 24-5: TIMER1, 2, 3, 4, 5, 6, 7, 8 AND 9 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CHARACTERISTICSStandard Operating Conditions: 3.0V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le$ |           |                                                                |                                                                |       |                                         |     |         |       |                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------|----------------------------------------------------------------|-------|-----------------------------------------|-----|---------|-------|------------------------------------------|

| Param<br>No.                                                                                                                          | Symbol    | Characte                                                       | eristic                                                        |       | Min                                     | Тур | Мах     | Units | Conditions                               |

| TA10                                                                                                                                  | ТтхН      | TxCK High Time                                                 | Synchron<br>no presc                                           |       | 0.5 Tcy + 20                            |     | _       | ns    | Must also meet parameter TA15            |

|                                                                                                                                       |           |                                                                | Synchron<br>with pres                                          |       | 10                                      |     | —       | ns    |                                          |

|                                                                                                                                       |           |                                                                | Asynchro                                                       | onous | 10                                      |     |         | ns    |                                          |

| TA11                                                                                                                                  | ΤτxL      | TxCK Low Time                                                  | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |       | 0.5 TCY + 20                            | _   | —       | ns    | Must also meet parameter TA15            |

|                                                                                                                                       |           |                                                                |                                                                |       |                                         |     | 10      |       | —                                        |

|                                                                                                                                       |           |                                                                | Asynchro                                                       | onous | 10                                      | _   |         | ns    |                                          |

| TA15                                                                                                                                  | ΤτχΡ      | TxCK Input Period                                              | Synchron<br>no presc                                           | •     | Тсү + 40                                |     | _       | ns    | —                                        |

|                                                                                                                                       |           |                                                                | Synchronous, with prescaler                                    |       | Greater of:<br>20 ns or<br>(Tcy + 40)/N | —   | —       | _     | N = prescale<br>value<br>(1, 8, 64, 256) |

|                                                                                                                                       |           |                                                                | Asynchro                                                       | onous | 20                                      |     |         | ns    | _                                        |

| OS60                                                                                                                                  | Ft1       | SOSCI/T1CK Oscil<br>frequency Range (o<br>by setting bit TCS ( | oscillator enabled                                             |       | DC                                      |     | 50      | kHz   | —                                        |

| TA20                                                                                                                                  | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre                      |                                                                | lock  | 0.5 TCY                                 |     | 1.5 TCY | _     | —                                        |

### TABLE 24-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

| AC CHARACTERISTICS |                |                                          |                                                                | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                         |     |         |       |                               |

|--------------------|----------------|------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|

| Param<br>No.       | Symbol         | Charact                                  | eristic                                                        |                                                                                                                                                         | Min                                     | Тур | Max     | Units | Conditions                    |

| TB10               | TtxH           | TxCK High Time                           | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                         | 0.5 TCY + 20                            |     | _       | ns    | Must also meet parameter TB15 |

|                    |                |                                          |                                                                |                                                                                                                                                         | 10                                      | _   | —       | ns    |                               |

| TB11               | TtxL           | TxCK Low Time                            | Synchronous, no prescaler                                      |                                                                                                                                                         | 0.5 TCY + 20                            | _   | —       | ns    | Must also meet parameter TB15 |

|                    |                |                                          | Synchronous, with prescaler                                    |                                                                                                                                                         | 10                                      | _   | —       | ns    |                               |

| TB15               | TtxP           | TxCK Input<br>Period                     | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                         | Tcy + 40                                | _   | —       | ns    | N = prescale<br>value         |

|                    |                |                                          |                                                                |                                                                                                                                                         | Greater of:<br>20 ns or<br>(Tcy + 40)/N |     |         |       | (1, 8, 64, 256)               |

| TB20               | TCKEXT-<br>MRL | Delay from Externa<br>Edge to Timer Incr |                                                                | Clock                                                                                                                                                   | 0.5 TCY                                 |     | 1.5 TCY | —     | —                             |

#### TABLE 24-23: TIMER2, 4, 6 AND 8 EXTERNAL CLOCK TIMING REQUIREMENTS