Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp510-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

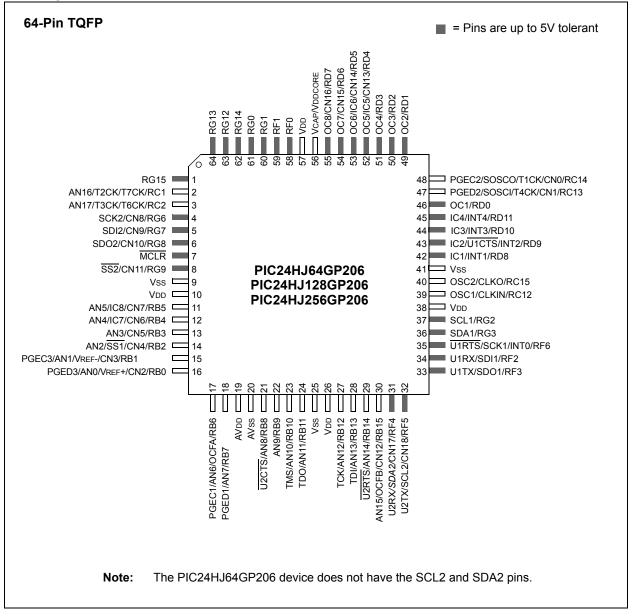

## **Pin Diagrams**

### TABLE 4-12: UART2 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7        | Bit 6   | Bit 5 | Bit 4       | Bit 3   | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------------|----------|--------|----------|--------|--------|--------|-------|----------|--------------|---------|-------|-------------|---------|-------|--------|-------|---------------|

| U2MODE      | 0230        | UARTEN   |        | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0     | WAKE         | LPBACK  | ABAUD | URXINV      | BRGH    | PDSE  | _<1:0> | STSEL | 0000          |

| U2STA       | 0232        | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | TRMT     | URXISE       | EL<1:0> | ADDEN | RIDLE       | PERR    | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234        | _        | _      | _        | _      | _      |        | _     |          |              |         | UART  | Transmit Re | egister |       |        |       | xxxx          |

| U2RXREG     | 0236        | _        | _      | —        | _      | _      | _      | —     |          |              |         | UART  | Receive Re  | gister  |       |        |       | 0000          |

| U2BRG       | 0238        |          |        |          |        |        |        | Baud  | Rate Gen | erator Presc | aler    |       |             |         |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-13: SPI1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7       | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|--------|---------|--------|--------|--------|------------|-------------|-------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT    | 0240        | SPIEN  | -      | SPISIDL | _      | —      | —      |            |             |             | SPIROV   | —     | _     | —         | —     | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242        | _      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN        | CKP      | MSTEN |       | SPRE<2:0> | •     | PPRE   | <1:0>  | 0000          |

| SPI1CON2    | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _           | _           | _        | _     | _     | _         | _     | FRMDLY | _      | 0000          |

| SPI1BUF     | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Red | eive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### TABLE 4-14: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|-----------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | _      | SPISIDL | _      | _      | _      | -         |             | —            | SPIROV   | _     | _     | —         | _     | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | -      | _      | _       | DISSCK | DISSDO | MODE16 | SMP       | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD | FRMPOL  | _      | —      | —      | _         | -           | _            | _        | _     | —     | —         | _     | FRMDLY | —      | 0000          |

| SPI2BUF  | 0268        |        |        |         |        |        |        | SPI2 Tran | smit and Re | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-24: PORTA REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | _      | TRISA10 | TRISA9 | —     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA     | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 06C0 | ODCA15  | ODCA14  | _       | _       | _      | _       | -      | -     |        | _      | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-25: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-26: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | —      | _     | _     |       | _     | _     | TRISC4 | TRISC3 | TRISC2 | TRISC1 |       | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | _      | _     | _     | _     | _     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | _      |       |       |       | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  | -     | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-27: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 5. *"Flash Programming"* (DS70228), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP programming capability allows a PIC24HJXXXGPX06/X08/X10 device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or single instructions and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

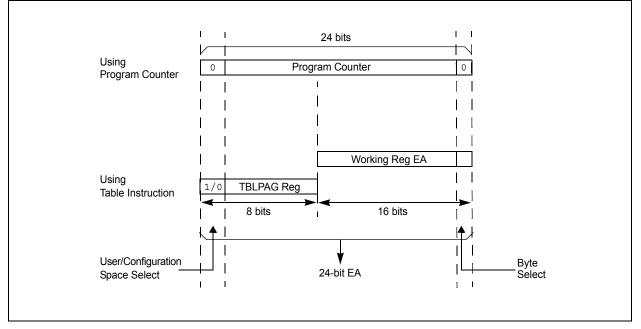

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Compare 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1:INTERRUPT VECTORS

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0  | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| NSTDIS | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | U-0   |

|-------|---------|---------|---------|---------|--------|---------|-------|

| —     | DIV0ERR | DMACERR | MATHERR | ADDRERR | STKERR | OSCFAIL | —     |

| bit 7 |         |         |         |         |        |         | bit 0 |

| Legend:      |         |                                                             |                       |                    |

|--------------|---------|-------------------------------------------------------------|-----------------------|--------------------|

| R = Readab   | ole bit | W = Writable bit                                            | U = Unimplemented bit | , read as '0'      |

| -n = Value a | at POR  | '1' = Bit is set                                            | '0' = Bit is cleared  | x = Bit is unknown |

|              |         |                                                             |                       |                    |

| bit 15       |         | : Interrupt Nesting Disable bi                              | t                     |                    |

|              |         | rupt nesting is disabled<br>rupt nesting is enabled         |                       |                    |

| bit 14-7     |         | emented: Read as '0'                                        |                       |                    |

| bit 6        | -       | <b>R:</b> Arithmetic Error Status bit                       |                       |                    |

|              |         | n error trap was caused by a                                |                       |                    |

|              |         | error trap was not caused by a                              | 5                     |                    |

| bit 5        | DMACE   | RR: DMA Controller Error Sta                                | atus bit              |                    |

|              | 1 = DMA | controller error trap has occ                               | urred                 |                    |

|              | 0 = DMA | controller error trap has not                               | occurred              |                    |

| bit 4        | MATHER  | RR: Arithmetic Error Status b                               | it                    |                    |

|              |         | error trap has occurred                                     |                       |                    |

|              |         | error trap has not occurred                                 |                       |                    |

| bit 3        |         | RR: Address Error Trap Statu                                | is bit                |                    |

|              |         | ress error trap has occurred                                | ad                    |                    |

| bit 2        |         | ess error trap has not occurr                               |                       |                    |

|              |         | R: Stack Error Trap Status bit<br>k error trap has occurred |                       |                    |

|              |         | k error trap has not occurred                               |                       |                    |

| bit 1        |         | L: Oscillator Failure Trap Sta                              | tus bit               |                    |

|              |         | llator failure trap has occurre                             |                       |                    |

|              |         | llator failure trap has not occ                             |                       |                    |

| bit 0        | Unimple | mented: Read as '0'                                         |                       |                    |

## REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 **CNIF:** Input Change Notification Interrupt Flag Status bit 1 = Interrupt request has occurred 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| REGISTER (-10. IECO. INTERROFTENABLE CONTROL REGISTER U | REGISTER 7-10: | IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 |

|---------------------------------------------------------|----------------|-------------------------------------------|

|---------------------------------------------------------|----------------|-------------------------------------------|

| U-0           | R/W-0                                                                                                      | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|------------------|------------------|-----------------|--------|--|--|

| _             | DMA1IE                                                                                                     | AD1IE                            | U1TXIE          | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |  |  |

| bit 15        |                                                                                                            |                                  |                 |                  |                  |                 | bit 8  |  |  |

|               |                                                                                                            |                                  |                 |                  |                  |                 |        |  |  |

| R/W-0         | R/W-0                                                                                                      | R/W-0                            | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |  |  |

| T2IE          | OC2IE                                                                                                      | IC2IE                            | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INT0IE |  |  |

| bit 7         |                                                                                                            |                                  |                 |                  |                  |                 | bit C  |  |  |

| Legend:       |                                                                                                            |                                  |                 |                  |                  |                 |        |  |  |

| R = Readable  | e bit                                                                                                      | W = Writable                     | bit             | U = Unimpler     | mented bit, read | 1 as '0'        |        |  |  |

| -n = Value at | POR                                                                                                        | '1' = Bit is set                 | İ               | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |  |  |

|               |                                                                                                            |                                  |                 |                  |                  |                 |        |  |  |

| bit 15        | Unimplemen                                                                                                 | ted: Read as '                   | 0'              |                  |                  |                 |        |  |  |

| bit 14        |                                                                                                            |                                  |                 | Complete Interr  | rupt Enable bit  |                 |        |  |  |

|               | •                                                                                                          | equest enable<br>equest not ena  |                 |                  |                  |                 |        |  |  |

| bit 13        |                                                                                                            |                                  |                 | rupt Enable bit  |                  |                 |        |  |  |

|               |                                                                                                            | equest enable                    | -               |                  |                  |                 |        |  |  |

|               |                                                                                                            | equest not en                    |                 |                  |                  |                 |        |  |  |

| bit 12        | U1TXIE: UAF                                                                                                | RT1 Transmitte                   | r Interrupt Ena | able bit         |                  |                 |        |  |  |

|               |                                                                                                            | equest enable                    |                 |                  |                  |                 |        |  |  |

| bit 11        | <ul> <li>0 = Interrupt request not enabled</li> <li>U1RXIE: UART1 Receiver Interrupt Enable bit</li> </ul> |                                  |                 |                  |                  |                 |        |  |  |

|               |                                                                                                            | request enable                   | •               |                  |                  |                 |        |  |  |

|               | •                                                                                                          | equest not en                    |                 |                  |                  |                 |        |  |  |

| bit 10        | SPI1IE: SPI1                                                                                               | Event Interrup                   | t Enable bit    |                  |                  |                 |        |  |  |

|               |                                                                                                            | equest enable                    |                 |                  |                  |                 |        |  |  |

| L:1 0         |                                                                                                            | equest not en                    |                 |                  |                  |                 |        |  |  |

| bit 9         |                                                                                                            | 1 Error Interru<br>equest enable | •               |                  |                  |                 |        |  |  |

|               |                                                                                                            | equest enable                    |                 |                  |                  |                 |        |  |  |

| bit 8         | T3IE: Timer3                                                                                               | Interrupt Enab                   | le bit          |                  |                  |                 |        |  |  |

|               |                                                                                                            | equest enable                    |                 |                  |                  |                 |        |  |  |

|               | -                                                                                                          | equest not en                    |                 |                  |                  |                 |        |  |  |

| bit 7         |                                                                                                            | Interrupt Enab                   |                 |                  |                  |                 |        |  |  |

|               | •                                                                                                          | equest enable<br>equest not ena  |                 |                  |                  |                 |        |  |  |

| bit 6         | •                                                                                                          | •                                |                 | upt Enable bit   |                  |                 |        |  |  |

|               | -                                                                                                          | equest enable                    |                 |                  |                  |                 |        |  |  |

|               | 0 = Interrupt r                                                                                            | equest not en                    | abled           |                  |                  |                 |        |  |  |

| bit 5         |                                                                                                            | Capture Chann                    | -               | Enable bit       |                  |                 |        |  |  |

|               |                                                                                                            | equest enable<br>equest not ena  |                 |                  |                  |                 |        |  |  |

| bit 4         | -                                                                                                          | -                                |                 | Complete Interr  | rupt Enable bit  |                 |        |  |  |

|               |                                                                                                            | equest enable                    |                 |                  |                  |                 |        |  |  |

|               |                                                                                                            | equest not en                    |                 |                  |                  |                 |        |  |  |

|               |                                                                                                            |                                  |                 |                  |                  |                 |        |  |  |

| bit 3         | T1IE: Timer1                                                                                               | Interrupt Enab                   | le bit          |                  |                  |                 |        |  |  |

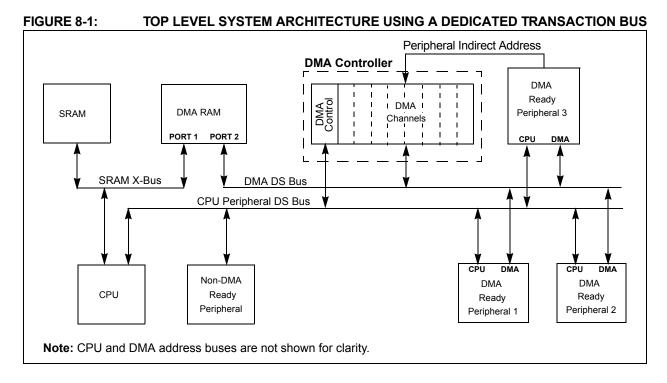

## 8.0 DIRECT MEMORY ACCESS (DMA)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 22. "Direct Memory Access (DMA)" (DS70223), which is available from the Microchip website (www.microchip.com).

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal intervention. The CPU DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and, therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The PIC24HJXXXGPX06/X08/X10 peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

| <b>TABLE 8-1</b> : | PERIPHERALS WITH DMA |

|--------------------|----------------------|

|                    | SUPPORT              |

| Peripheral         | IRQ Number |

|--------------------|------------|

| INT0               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- Word or byte sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- · Automatic or manual initiation of block transfers

- Each channel can select from 19 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

<sup>© 2009</sup> Microchip Technology Inc.

## 8.1 DMAC Registers

Each DMAC Channel x (x = 0, 1, 2, 3, 4, 5, 6 or 7) contains the following registers:

- A 16-bit DMA Channel Control register (DMAxCON)

- A 16-bit DMA Channel IRQ Select register (DMAxREQ)

- A 16-bit DMA RAM Primary Start Address Offset register (DMAxSTA)

- A 16-bit DMA RAM Secondary Start Address Offset register (DMAxSTB)

- A 16-bit DMA Peripheral Address register (DMAxPAD)

- A 10-bit DMA Transfer Count register (DMAxCNT)

An additional pair of status registers, DMACS0 and DMACS1 are common to all DMAC channels.

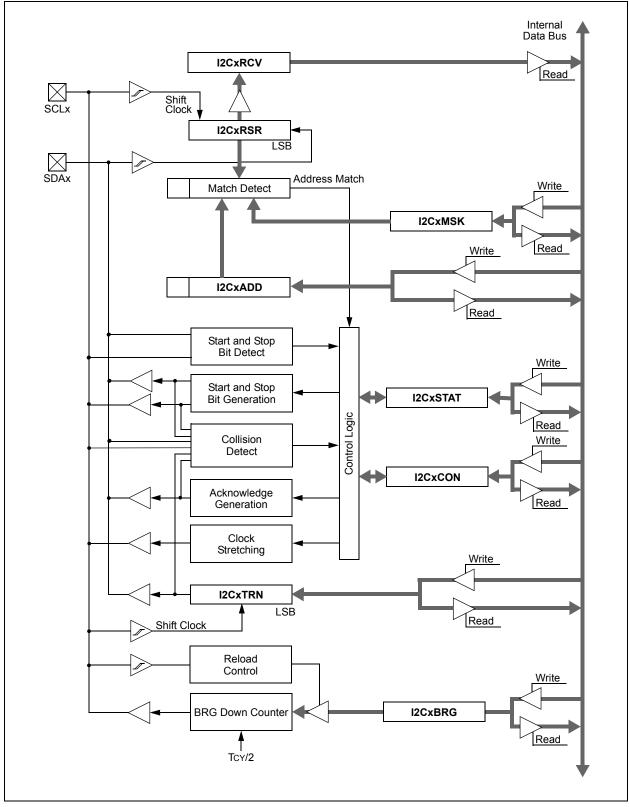

FIGURE 17-1:  $I^2 C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

## **REGISTER 19-4:** CIFCTRL: ECAN<sup>™</sup> MODULE FIFO CONTROL REGISTER

| R/W-0         | R/W-0                                                                                                                                  | R/W-0                                                                                                       | U-0              | U-0              | U-0             | U-0             | U-0   |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|-------|

|               | DMABS<2:0>                                                                                                                             | •                                                                                                           | _                |                  | _               | _               |       |

| bit 15        |                                                                                                                                        |                                                                                                             |                  |                  |                 |                 | bit 8 |

| U-0           | U-0                                                                                                                                    | U-0                                                                                                         | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| 0-0           | 0-0                                                                                                                                    | 0-0                                                                                                         | R/W-U            | R/W-0            | FSA<4:0>        | R/W-U           | R/W-U |

| <br>bit 7     |                                                                                                                                        |                                                                                                             |                  |                  | F3A54.02        |                 | bit 0 |

|               |                                                                                                                                        |                                                                                                             |                  |                  |                 |                 | DILU  |

| Legend:       |                                                                                                                                        |                                                                                                             |                  |                  |                 |                 |       |

| R = Readabl   | le bit                                                                                                                                 | W = Writable                                                                                                | bit              | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at | t POR                                                                                                                                  | '1' = Bit is set                                                                                            |                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|               | 100 = 16 bur<br>011 = 12 bur<br>010 = 8 buff<br>001 = 6 buff<br>000 = 4 buff                                                           | ffers in DMA RA<br>ffers in DMA RA<br>ffers in DMA RA<br>ers in DMA RAN<br>ers in DMA RAN<br>ers in DMA RAN | M<br>M<br>1<br>1 |                  |                 |                 |       |

| bit 12-5      | -                                                                                                                                      | nted: Read as '                                                                                             |                  |                  |                 |                 |       |

| bit 4-0       | FSA<4:0>: F<br>11111 = RB<br>11110 = RB<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | 30 buffer<br>B1 buffer                                                                                      | with Buffer b    | its              |                 |                 |       |

## REGISTER 19-7: CIINTE: ECAN™ MODULE INTERRUPT ENABLE REGISTER

| U-0            | U-0            | U-0              | U-0             | U-0              | U-0              | U-0             | U-0   |  |  |

|----------------|----------------|------------------|-----------------|------------------|------------------|-----------------|-------|--|--|

| _              |                | —                | _               | —                | —                |                 | _     |  |  |

| bit 15         |                |                  |                 |                  |                  |                 | bit 8 |  |  |

|                |                |                  |                 |                  |                  |                 |       |  |  |

| R/W-0          | R/W-0          | R/W-0            | U-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| IVRIE          | WAKIE          | ERRIE            |                 | FIFOIE           | RBOVIE           | RBIE            | TBIE  |  |  |

| bit 7          |                |                  |                 |                  |                  |                 | bit 0 |  |  |

|                |                |                  |                 |                  |                  |                 |       |  |  |

| Legend:        |                |                  |                 |                  |                  |                 |       |  |  |

| R = Readab     | le bit         | W = Writable     | bit             | U = Unimpler     | mented bit, read | 1 as '0'        |       |  |  |

| -n = Value a   | t POR          | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

|                |                |                  |                 |                  |                  |                 |       |  |  |

| bit 15-8       | Unimplemen     | ted: Read as '   | 0'              |                  |                  |                 |       |  |  |

| bit 7          | IVRIE: Invalio | I Message Rec    | eived Interrup  | t Enable bit     |                  |                 |       |  |  |

| bit 6          | WAKIE: Bus     | Wake-up Activi   | ty Interrupt FI | ag bit           |                  |                 |       |  |  |

| 1. 1. <b>F</b> |                |                  |                 |                  |                  |                 |       |  |  |

- bit 5 ERRIE: Error Interrupt Enable bit bit 4 Unimplemented: Read as '0'

- bit 3 **FIFOIE:** FIFO Almost Full Interrupt Enable bit

- bit 2 **RBOVIE:** RX Buffer Overflow Interrupt Enable bit

- bit 1 **RBIE:** RX Buffer Interrupt Enable bit

- bit 0 TBIE: TX Buffer Interrupt Enable bit

| DC CHARACT                                                          | ERISTICS               |     | (unless oth | perating Condition<br>erwise stated)<br>emperature -40°C | s: 3.0V to 3.6V<br>≤ Ta ≤ +85°C for In | dustrial |  |  |  |  |

|---------------------------------------------------------------------|------------------------|-----|-------------|----------------------------------------------------------|----------------------------------------|----------|--|--|--|--|

| Parameter<br>No.                                                    | Typical <sup>(1)</sup> | Мах | Units       | Conditions                                               |                                        |          |  |  |  |  |

| Idle Current (IIDLE): Core OFF Clock ON Base Current <sup>(2)</sup> |                        |     |             |                                                          |                                        |          |  |  |  |  |

| DC40d                                                               | 3                      | 25  | mA          | -40°C                                                    |                                        |          |  |  |  |  |

| DC40a                                                               | 3                      | 25  | mA          | +25°C                                                    | 3.3V                                   | 10 MIPS  |  |  |  |  |

| DC40b                                                               | 3                      | 25  | mA          | +85°C                                                    | 0.5 V                                  |          |  |  |  |  |

| DC41d                                                               | 4                      | 25  | mA          | -40°C                                                    |                                        | 16 MIPS  |  |  |  |  |

| DC41a                                                               | 5                      | 25  | mA          | +25°C                                                    | 3.3V                                   |          |  |  |  |  |

| DC41b                                                               | 6                      | 25  | mA          | +85°C                                                    |                                        |          |  |  |  |  |

| DC42d                                                               | 8                      | 25  | mA          | -40°C                                                    |                                        | 20 MIPS  |  |  |  |  |

| DC42a                                                               | 9                      | 25  | mA          | +25°C                                                    | 3.3V                                   |          |  |  |  |  |

| DC42b                                                               | 10                     | 25  | mA          | +85°C                                                    |                                        |          |  |  |  |  |

| DC43a                                                               | 15                     | 25  | mA          | +25°C                                                    |                                        | 30 MIPS  |  |  |  |  |

| DC43d                                                               | 15                     | 25  | mA          | -40°C                                                    | 3.3V                                   |          |  |  |  |  |

| DC43b                                                               | 15                     | 25  | mA          | +85°C                                                    |                                        |          |  |  |  |  |

| DC44d                                                               | 16                     | 25  | mA          | -40°C                                                    |                                        |          |  |  |  |  |

| DC44a                                                               | 16                     | 25  | mA          | +25°C                                                    | 3.3V                                   | 40 MIPS  |  |  |  |  |

| DC44b                                                               | 16                     | 25  | mA          | +85°C                                                    |                                        |          |  |  |  |  |

#### TABLE 24-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: Base IIDLE current is measured with core off, clock on and all modules turned off. Peripheral Module Disable SFR registers are zeroed. All I/O pins are configured as inputs and pulled to Vss.

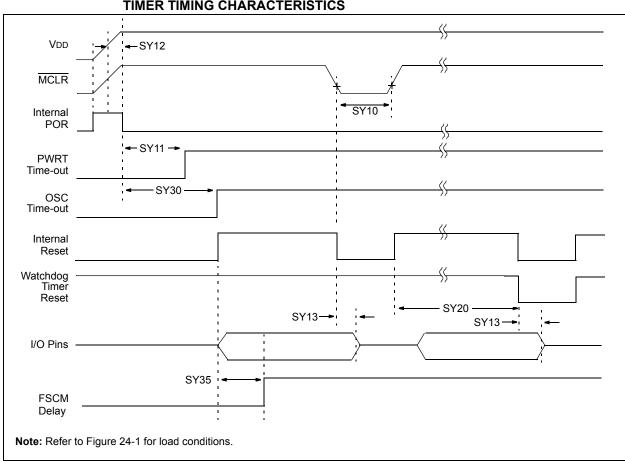

## FIGURE 24-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

### TABLE 24-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHA       | RACTER | ISTICS                                                         | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial |                                 |     |       |                                                                                        |  |

|--------------|--------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-------|----------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                  | Min                                                                                                                                               | Тур <sup>(2)</sup>              | Мах | Units | Conditions                                                                             |  |

| SY10         | TMCL   | MCLR Pulse-Width (low)                                         | 2                                                                                                                                                 | _                               | _   | μs    | -40°C to +85°C                                                                         |  |

| SY11         | Tpwrt  | Power-up Timer Period                                          | _                                                                                                                                                 | 2<br>4<br>16<br>32<br>64<br>128 | _   | ms    | -40°C to +85°C<br>User programmable                                                    |  |

| SY12         | TPOR   | Power-on Reset Delay                                           | 3                                                                                                                                                 | 10                              | 30  | μs    | -40°C to +85°C                                                                         |  |

| SY13         | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68                                                                                                                                              | 0.72                            | 1.2 | μs    | _                                                                                      |  |

| SY20         | Twdt1  | Watchdog Timer Time-out<br>Period                              | —                                                                                                                                                 | —                               | _   | _     | See Section 21.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 24-19) |  |

| SY30         | Tost   | Oscillator Start-up Timer<br>Period                            | —                                                                                                                                                 | 1024 Tosc                       | _   | —     | Tosc = OSC1 period                                                                     |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               |                                                                                                                                                   | 500                             | 900 | μs    | -40°C to +85°C                                                                         |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

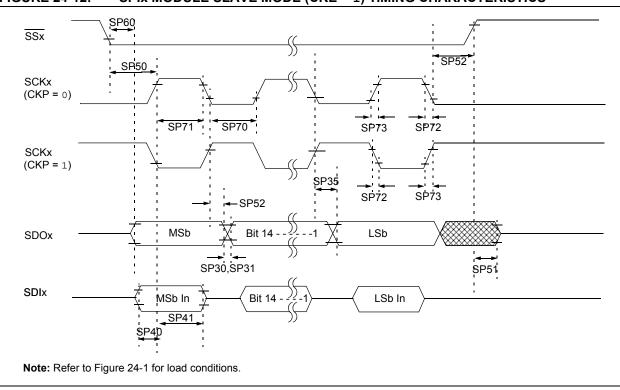

#### FIGURE 24-12: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

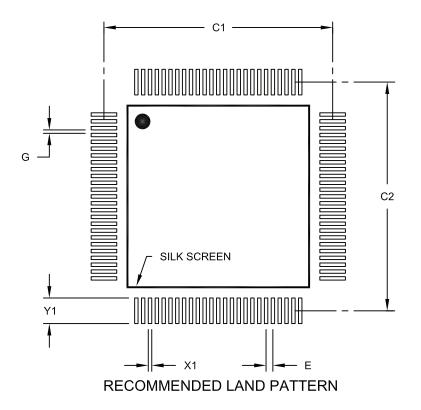

## 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIM | ETERS    |       |      |  |

|---------------------------|--------|----------|-------|------|--|

| Dimension                 | MIN    | NOM      | MAX   |      |  |

| Contact Pitch             | E      | 0.40 BSC |       |      |  |

| Contact Pad Spacing       | C1     |          | 13.40 |      |  |

| Contact Pad Spacing       | C2     |          | 13.40 |      |  |

| Contact Pad Width (X100)  | X1     |          |       | 0.20 |  |

| Contact Pad Length (X100) | Y1     |          |       | 1.50 |  |

| Distance Between Pads     | G      | 0.20     |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100A

NOTES: