Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

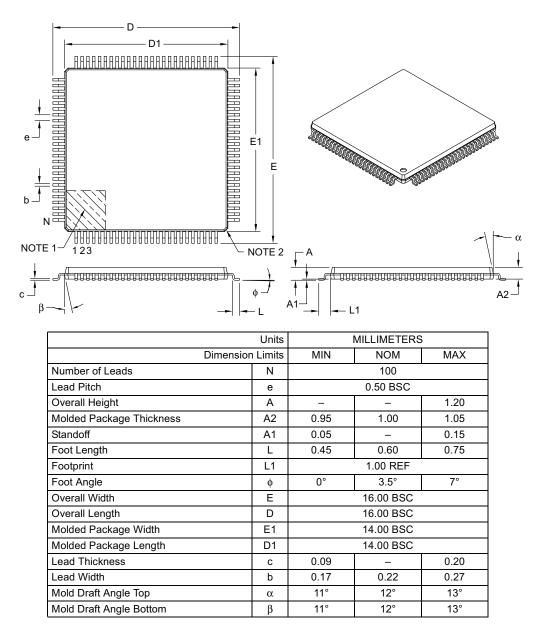

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp510t-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 2, ICD 3, or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor to Vss on unused pins and drive the output to logic low.

| File Name  | Addr          | Bit 15    | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10                        | Bit 9    | Bit 8       | Bit 7                        | Bit 6    | Bit 5  | Bit 4  | Bit 3              | Bit 2 | Bit 1               | Bit 0  | All<br>Resets |

|------------|---------------|-----------|-----------------------|--------|--------|--------|-------------------------------|----------|-------------|------------------------------|----------|--------|--------|--------------------|-------|---------------------|--------|---------------|

|            | 0400-<br>041E |           |                       | •      |        |        |                               |          | See definit | ion when V                   | VIN = x  | •      | ·      | ·                  |       |                     | •      |               |

| C1BUFPNT1  | 0420          |           | F3BF                  | P<3:0> |        |        | F2BF                          | P<3:0>   |             |                              | F1BP     | <3:0>  |        |                    | F0BP  | <3:0>               |        | 0000          |

| C1BUFPNT2  | 0422          |           | F7BF                  | P<3:0> |        |        | F6BF                          | P<3:0>   |             |                              | F5BP     | <3:0>  |        | F4BP<3:0>          |       |                     |        | 0000          |

| C1BUFPNT3  | 0424          |           | F11BP<3:0> F10BP<3:0> |        |        |        |                               |          |             | F9BP<3:0> F8                 |          |        |        |                    | F8BP  | <3:0>               |        | 0000          |

| C1BUFPNT4  | 0426          |           | F15B                  | P<3:0> |        |        | F14B                          | P<3:0>   |             |                              | F13BF    | P<3:0> |        |                    | F12BF | <b>?&lt;3:0&gt;</b> |        | 0000          |

| C1RXM0SID  | 0430          |           | SID<10:3>             |        |        |        |                               |          |             | SID<2:0> — MIDE — EID<       |          |        |        |                    |       | EID<                | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |           |                       |        | EID<   | :15:8> |                               |          |             | EID<7:0>                     |          |        |        |                    |       |                     |        | xxxx          |

| C1RXM1SID  | 0434          |           | SID<10:3>             |        |        |        |                               |          |             | SID<2:0> — MIDE — EID<17:16> |          |        |        |                    |       |                     |        | xxxx          |

| C1RXM1EID  | 0436          |           | EID<15:8>             |        |        |        |                               |          |             | EID<7:0>                     |          |        |        |                    |       |                     |        | xxxx          |

| C1RXM2SID  | 0438          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | —      | MIDE               |       | EID<                | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |           |                       |        | EID<   | :15:8> |                               |          |             | EID<7:0>                     |          |        |        |                    |       |                     |        | xxxx          |

| C1RXF0SID  | 0440          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | —      | EXIDE              |       | EID<                | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |           |                       |        | EID<   | :15:8> |                               |          |             | EID<7:0>                     |          |        |        |                    |       |                     | xxxx   |               |

| C1RXF1SID  | 0444          |           | SID<10:3>             |        |        |        |                               |          |             | SID<2:0>                     |          |        | EXIDE  |                    | EID<  | 17:16>              | xxxx   |               |

| C1RXF1EID  | 0446          |           | EID<15:8>             |        |        |        |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF2SID  | 0448          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | —      | EXIDE              |       | EID<                | 17:16> | xxxx          |

| C1RXF2EID  | 044A          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF3SID  | 044C          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | —      | EXIDE — EID<17:16> |       |                     |        | xxxx          |

| C1RXF3EID  | 044E          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | <7:0>              |       |                     |        | xxxx          |

| C1RXF4SID  | 0450          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | _      | - EXIDE -          |       |                     | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF5SID  | 0454          |           |                       |        | SID<   | :10:3> |                               |          |             | SID<2:0> — EXIDE — E         |          |        |        |                    |       |                     | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF6SID  | 0458          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | _      | EXIDE              |       | EID<                | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF7SID  | 045C          |           |                       |        | SID<   | 10:3>  |                               |          |             |                              | SID<2:0> |        | —      | EXIDE              |       | EID<                | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |           |                       |        | EID<   | :15:8> |                               |          |             |                              |          |        | EID<   | 7:0>               |       |                     |        | xxxx          |

| C1RXF8SID  | 0460          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | —      | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |           | EID<15:8>             |        |        |        |                               |          | EID<7:0>    |                              |          |        |        |                    |       | xxxx                |        |               |

| C1RXF9SID  | 0464          | SID<10:3> |                       |        |        |        | SID<2:0> — EXIDE — EID<17:16> |          |             |                              |          |        | 17:16> | xxxx               |       |                     |        |               |

| C1RXF9EID  | 0466          | EID<15:8> |                       |        |        |        |                               | EID<7:0> |             |                              |          |        |        |                    | xxxx  |                     |        |               |

| C1RXF10SID | 0468          |           | SID<10:3>             |        |        |        |                               |          |             | SID<2:0>                     |          |        | EXIDE  |                    | EID<  | 17:16>              | xxxx   |               |

| C1RXF10EID | 046A          |           | EID<15:8>             |        |        |        |                               |          |             |                              |          | EID<   | 7:0>   |                    |       |                     | xxxx   |               |

| C1RXF11SID | 046C          |           |                       |        | SID<   | :10:3> |                               |          |             |                              | SID<2:0> |        | _      | EXIDE              | _     | EID<                | 17:16> | xxxx          |

### TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506/510/610 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-28: PORTE REGISTER MAP<sup>(1)</sup>

|           |      |        |        |        |        |        |        |       | -     |        | -      | -      | -      |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | -      | —      | _      | _      | -      | —     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | XXXX          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-29: PORTF REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|---------------------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF               | 02DE | _      | _      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF               | 02E0 | -      | _      | RF13    | RF12    | -      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF                | 02E2 | -      | _      | LATF13  | LATF12  | -      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF <sup>(2)</sup> | 06DE | _      | _      | ODCF13  | ODCF12  | _      | —      | —     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-30: PORTG REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG               | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG               | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | XXXX          |

| LATG                | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | XXXX          |

| ODCG <sup>(2)</sup> | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | —     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

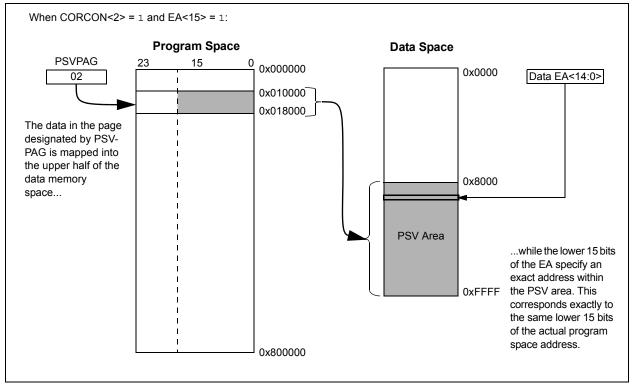

#### 4.4.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-8), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

## Note: PSV access is temporarily disabled during table reads/writes.

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

## FIGURE 4-8: PROGRAM SPACE VISIBILITY OPERATION

#### REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------|----------------------|----------------------|-----|-----|-----|-----|-------|

| WR                    | WREN                 | WRERR                | —   | —   | —   | —   | —     |

| bit 15                |                      |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0 <sup>(1)</sup> | U-0 | U-0 | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

|-------|----------------------|-----|-----|----------------------|----------------------|----------------------|----------------------|

| _     | ERASE                | —   | —   |                      | NVMOF                | o<3:0>(2)            |                      |

| bit 7 |                      |     |     |                      |                      |                      | bit 0                |

| Legend:           | SO = Settable only bit |                       |                    |

|-------------------|------------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared  | x = Bit is unknown |

| <u> </u>          |                        |                       |                    |

| WR: Write Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is cleared by hardware once operation is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0 = Program or erase operation is complete and inactive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WREN: Write Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul><li>1 = Enable Flash program/erase operations</li><li>0 = Inhibit Flash program/erase operations</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| WRERR: Write Sequence Error Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>1 = An improper program or erase sequence attempt or termination has occurred (bit is set<br/>automatically on any set attempt of the WR bit)</li> <li>The means are accurately accuratel</li></ul> |

| 0 = The program or erase operation completed normally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ERASE: Erase/Program Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>1 = Perform the erase operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> <li>0 = Perform the program operation specified by NVMOP&lt;3:0&gt; on the next WR command</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NVMOP<3:0>: NVM Operation Select bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <pre>1111 = Memory bulk erase operation (ERASE = 1) or no operation (ERASE = 0) 1110 = Reserved</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1101 = Erase General Segment and FGS Configuration Register<br>(ERASE = 1) or no operation (ERASE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1100 = Erase Secure Segment and FSS Configuration Register<br>(ERASE = 1) or no operation (ERASE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1011-0100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0011 = Memory word program operation (ERASE = 0) or no operation (ERASE = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0010 = Memory page erase operation (ERASE = 1) or no operation (ERASE = 0)<br>0001 = Memory row program operation (ERASE = 0) or no operation (ERASE = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0000 = Program or erase a single Configuration register byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**Note 1:** These bits can only be reset on POR.

2: All other combinations of NVMOP<3:0> are unimplemented.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

|   | -            |                                  | -     |                                       |

|---|--------------|----------------------------------|-------|---------------------------------------|

| ; | Set up NVMCO | N for row programming operations | 3     |                                       |

|   | MOV          | #0x4001, W0                      | ;     |                                       |

|   | MOV          | W0, NVMCON                       | ;     | Initialize NVMCON                     |

| ; | Set up a poi | nter to the first program memory | / loc | ation to be written                   |

| ; | program memo | ry selected, and writes enabled  |       |                                       |

|   | MOV          | #0x0000, W0                      | ;     |                                       |

|   | MOV          | W0, TBLPAG                       | ;     | Initialize PM Page Boundary SFR       |

|   | MOV          | #0x6000, W0                      | ;     | An example program memory address     |

| ; | Perform the  | TBLWT instructions to write the  | latc  | hes                                   |

| ; | 0th_program_ | word                             |       |                                       |

|   | MOV          | #LOW_WORD_0, W2                  | ;     |                                       |

|   | MOV          | #HIGH_BYTE_0, W3                 | ;     |                                       |

|   | TBLWTL       | W2, [W0]                         | ;     | Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; | 1st_program_ | word                             |       |                                       |

|   | MOV          | #LOW_WORD_1, W2                  | ;     |                                       |

|   | MOV          | #HIGH_BYTE_1, W3                 | ;     |                                       |

|   | TBLWTL       | W2, [W0]                         | ;     | Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                       | ;     | Write PM high byte into program latch |

| ; | 2nd_program  | _word                            |       |                                       |

|   | MOV          | #LOW_WORD_2, W2                  | ;     |                                       |

|   | MOV          | #HIGH_BYTE_2, W3                 | ;     |                                       |

|   | TBLWTL       | W2, [W0]                         |       | Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                       | ;     | Write PM high byte into program latch |

|   | •            |                                  |       |                                       |

|   | •            |                                  |       |                                       |

|   | •            |                                  |       |                                       |

| ; | 63rd_program | —                                |       |                                       |

|   | MOV          | #LOW_WORD_31, W2                 | ;     |                                       |

|   | MOV          | #HIGH_BYTE_31, W3                | ;     |                                       |

|   |              | W2, [W0]                         |       | Write PM low word into program latch  |

|   | TBLWTH       | W3, [W0++]                       | ;     | Write PM high byte into program latch |

|   |              |                                  |       |                                       |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI                      |                                          | Block all interrupts with priority <7<br>for next 5 instructions                                       |

|---------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|

| MOV<br>MOV<br>MOV         | #0x55, W0<br>W0, NVMKEY ;<br>#0xAA, W1 ; | Write the 55 key                                                                                       |

| MOV<br>BSET<br>NOP<br>NOP | W1, NVMKEY ;<br>NVMCON, #WR ;<br>;       | Write the AA key<br>Start the erase sequence<br>Insert two NOPs after the<br>erase command is asserted |

| R/W-0        | R/W-0                                                                                                                    | U-0                                                                                                                                 | U-0             | U-0                   | U-0               | U-0              | R/W-0        |  |  |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|-------------------|------------------|--------------|--|--|--|--|--|--|--|--|

| TRAPR        | IOPUWR                                                                                                                   |                                                                                                                                     | _               |                       | _                 |                  | VREGS        |  |  |  |  |  |  |  |  |

| bit 15       |                                                                                                                          |                                                                                                                                     |                 |                       |                   |                  | bit          |  |  |  |  |  |  |  |  |

| R/W-0        | R/W-0                                                                                                                    | R/W-0                                                                                                                               | R/W-0           | R/W-0                 | R/W-0             | R/W-1            | R/W-1        |  |  |  |  |  |  |  |  |

| EXTR         | SWR                                                                                                                      | SWDTEN <sup>(2)</sup>                                                                                                               | WDTO            | SLEEP                 | IDLE              | BOR              | POR          |  |  |  |  |  |  |  |  |

| bit 7        |                                                                                                                          |                                                                                                                                     |                 |                       |                   |                  | bit          |  |  |  |  |  |  |  |  |

| Legend:      |                                                                                                                          |                                                                                                                                     |                 |                       |                   |                  |              |  |  |  |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                   | W = Writable I                                                                                                                      | oit             | U = Unimpler          | nented bit, read  | as '0'           |              |  |  |  |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                    | '1' = Bit is set                                                                                                                    |                 | '0' = Bit is cle      | ared              | x = Bit is unk   | nown         |  |  |  |  |  |  |  |  |

| bit 15       | TRAPR: Tran                                                                                                              | Reset Flag bit                                                                                                                      |                 |                       |                   |                  |              |  |  |  |  |  |  |  |  |

| bit 10       |                                                                                                                          | onflict Reset ha                                                                                                                    | s occurred      |                       |                   |                  |              |  |  |  |  |  |  |  |  |

|              | •                                                                                                                        | <ul> <li>a Trap Conflict Reset has not occurred</li> <li>IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit</li> </ul> |                 |                       |                   |                  |              |  |  |  |  |  |  |  |  |

| bit 14       | IOPUWR: Ille                                                                                                             | gal Opcode or                                                                                                                       | Uninitialized \ | N Access Rese         | et Flag bit       |                  |              |  |  |  |  |  |  |  |  |

|              |                                                                                                                          |                                                                                                                                     |                 | al address mo         | ode or uninitiali | zed W registe    | er used as a |  |  |  |  |  |  |  |  |

|              |                                                                                                                          | Pointer caused<br>opcode or unir                                                                                                    |                 | eset has not o        | courred           |                  |              |  |  |  |  |  |  |  |  |