Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b, 18x12b                                                             |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp206-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

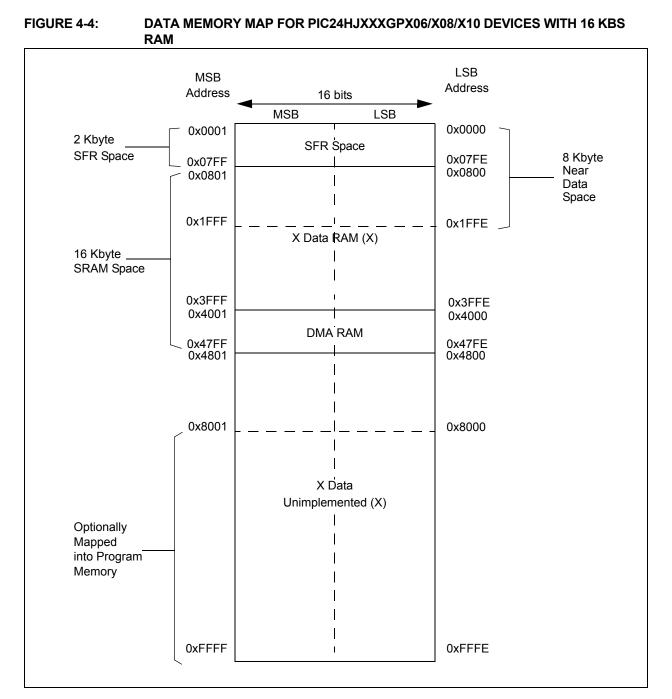

## 4.2.5 DMA RAM

Every PIC24HJXXXGPX06/X08/X10 device contains 2 Kbytes of dual ported DMA RAM located at the end of data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

**Note:** DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

### TABLE 4-9: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                                                                                                                                  | Bit 11 | Bit 10 | Bit 9  | Bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|----------|----------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | —       | _      | _       | _                                                                                                                                                                       | _      | -      | _      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |         | Receive  | Register |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | _      | _       | Receive Register         0000                 0007                0007                0007                0007               Baud Rate Generator Register         00000 |        |        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |         |          |          |       |       |       |               |

| I2C1BRG  | 0204        | _       | _      | _       | _                                                                                                                                                                       | _      | _      | _      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Image: Constraint of the second state of the second sta |       |         |          |          |       | 0000  |       |               |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL                                                                                                                                                                  | IPMIEN | A10M   | DISSLW | Image: Constraint of the second se |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |         |          |          | 1000  |       |       |               |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _                                                                                                                                                                       | _      | BCL    | GCSTAT | ADD10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IWCOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I2COV | D_A     | Р        | S        | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | —       |        | -       |                                                                                                                                                                         |        |        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | Address | Register |          |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | -       | _                                                                                                                                                                       | —      |        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Address Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |         |          |          |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-10: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                                                                  | Bit 7                        | Bit 6 | Bit 5 | Bit 4   | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|------------------------------------------------------------------------|------------------------------|-------|-------|---------|----------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | —       | _      | —       | _      | -      | —      | _      |                                                                        |                              |       |       | Receive | Register |       |       |       | 0000          |

| I2C2TRN  | 0212        | _       | _      | _       | _      | _      | _      | _      | —     —     Transmit Register       —     Baud Rate Generator Register |                              |       |       |         |          |       | OOFF  |       |               |

| I2C2BRG  | 0214        | _       | _      | _       | _      | _      | _      | _      |                                                                        | Baud Rate Generator Register |       |       |         |          |       |       |       | 0000          |

| I2C2CON  | 0216        | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                                                                   |                              |       |       |         |          |       |       | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10                                                                  | IWCOL                        | I2COV | D_A   | Р       | S        | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        | _       |        |         | —      |        |        |        |                                                                        | Address Register             |       |       |         |          |       |       |       | 0000          |

| I2C2MSK  | 021C        | _       |        |         | —      |        |        |        |                                                                        | Address Mask Register        |       |       |         |          |       |       |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

# TABLE 4-11: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                        | Bit 14                            | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8                                                | Bit 7 | Bit 6 | Bit 5 | Bit 4        | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|-------------------------------|-----------------------------------|----------|--------|--------|--------|-------|------------------------------------------------------|-------|-------|-------|--------------|--------|-------|-------|-------|---------------|

| U1MODE   | 0220        | UARTEN                        | —                                 | USIDL    | IREN   | RTSMD  |        |       |                                                      |       |       |       |              |        |       | 0000  |       |               |

| U1STA    | 0222        | UTXISEL1                      | UTXINV                            | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF | F TRMT URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXDA |       |       |       |              |        |       |       |       | 0110          |

| U1TXREG  | 0224        | _                             | _                                 | _        | _      | _      | _      | _     |                                                      |       |       | UART  | Transmit Reg | gister |       |       |       | xxxx          |

| U1RXREG  | 0226        | _                             | — — — — — — UART Receive Register |          |        |        |        |       |                                                      |       |       | 0000  |              |        |       |       |       |               |

| U1BRG    | 0228        | Baud Rate Generator Prescaler |                                   |          |        |        |        |       |                                                      |       |       |       | 0000         |        |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

# TABLE 4-28: PORTE REGISTER MAP<sup>(1)</sup>

|           |      |        |        |        |        |        |        |       | -     |        | -      | -      | -      |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | -      | —      | _      | _      | -      | —     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | XXXX          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-29: PORTF REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|---------------------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF               | 02DE | _      | _      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF               | 02E0 | -      | _      | RF13    | RF12    | -      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF                | 02E2 | -      | _      | LATF13  | LATF12  | -      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF <sup>(2)</sup> | 06DE | _      | _      | ODCF13  | ODCF12  | _      | —      | —     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-30: PORTG REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG               | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG               | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | XXXX          |

| LATG                | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | XXXX          |

| ODCG <sup>(2)</sup> | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | —     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

|  | REGISTER 7-6: | <b>IFS1: INTERRUPT FLAG STATUS REGISTER 1</b> |

|--|---------------|-----------------------------------------------|

|--|---------------|-----------------------------------------------|

| U2TXIF<br>bit 15<br>R/W-0<br>IC8IF<br>bit 7 | U2RXIF         | INT2IF                             | T5IF             | T4IF             | OC4IF            | OC3IF           |         |

|---------------------------------------------|----------------|------------------------------------|------------------|------------------|------------------|-----------------|---------|

| R/W-0<br>IC8IF                              |                | •                                  |                  | 141              | 00416            | OCSIF           | DMA21IF |

| IC8IF                                       |                |                                    | ·                |                  |                  |                 | bit 8   |

|                                             | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | U-0              | R/W-0           | R/W-0   |

| bit 7                                       | IC7IF          | AD2IF                              | INT1IF           | CNIF             | _                | MI2C1IF         | SI2C1IF |

|                                             |                |                                    | 1                | 1                |                  |                 | bit (   |

| Legend:                                     |                |                                    |                  |                  |                  |                 |         |

| R = Readable                                | bit            | W = Writable                       | bit              | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at F                             | POR            | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

| bit 15                                      | U2TXIF: UAF    | RT2 Transmitte                     | r Interrupt Flag | g Status bit     |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 14                                      | U2RXIF: UAF    | RT2 Receiver li                    | nterrupt Flag S  | Status bit       |                  |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

| L:1 1 0                                     | •              | request has no                     |                  |                  |                  |                 |         |

| bit 13                                      |                | rnal Interrupt 2<br>request has oc | -                | t                |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 12                                      | T5IF: Timer5   | Interrupt Flag                     | Status bit       |                  |                  |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | •              | request has no                     |                  |                  |                  |                 |         |

| bit 11                                      |                | Interrupt Flag<br>request has oc   |                  |                  |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 10                                      | OC4IF: Outp    | ut Compare Ch                      | annel 4 Interru  | upt Flag Status  | s bit            |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 9                                       | -              | ut Compare Ch                      |                  | upt Flag Status  | s bit            |                 |         |

|                                             | 1 = Interrupt  | request has oc<br>request has no   | curred           |                  |                  |                 |         |

| bit 8                                       | DMA21IF: DI    | MA Channel 2 I                     | Data Transfer    | Complete Inte    | rrupt Flag Statu | ıs bit          |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | •              | request has no                     |                  |                  |                  |                 |         |

| bit 7                                       |                | Capture Chann<br>request has oc    | •                | -lag Status bit  |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 6                                       | IC7IF: Input ( | Capture Chann                      | el 7 Interrupt F | lag Status bit   |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 5                                       | AD2IF: ADC2    | 2 Conversion C                     | omplete Interr   | upt Flag Statu   | s bit            |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | -              | request has no                     |                  |                  |                  |                 |         |

| bit 4                                       |                | rnal Interrupt 1                   | -                | t                |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

## REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <b>CNIE:</b> Input Change Notification Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                        |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul>                                         |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                                                                   |

- 1 = Interrupt request enabled

- 0 = Interrupt request on abled

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _            |                   | T2IP<2:0>                               |                |                   |                  | OC2IP<2:0>      |       |

| bit 15       |                   |                                         |                |                   |                  |                 | bit 8 |

|              |                   |                                         |                |                   |                  |                 |       |

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|              |                   | IC2IP<2:0>                              |                |                   |                  | DMA0IP<2:0>     |       |

| bit 7        |                   |                                         |                |                   |                  |                 | bit C |

| Legend:      |                   |                                         |                |                   |                  |                 |       |

| R = Readab   | le bit            | W = Writable I                          | oit            | U = Unimple       | mented bit, re   | ad as '0'       |       |

| -n = Value a | t POR             | '1' = Bit is set                        |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

| bit 15       | Unimpleme         | ented: Read as 'o                       | )'             |                   |                  |                 |       |

| bit 14-12    | -                 | Timer2 Interrupt                        |                |                   |                  |                 |       |

|              | 111 = Interr      | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      |                |                   |                  |                 |       |

| bit 11       | -                 | ented: Read as 'o                       |                |                   |                  |                 |       |

| bit 10-8     |                   | >: Output Compa                         |                | -                 | rity bits        |                 |       |

|              | 111 = Interr      | upt is priority 7 (I                    | lignest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1<br>upt source is disa | ahlad          |                   |                  |                 |       |

| bit 7        |                   | ented: Read as '                        |                |                   |                  |                 |       |

| bit 6-4      | -                 | Input Capture C                         |                | errupt Priority h | oits             |                 |       |

|              |                   | upt is priority 7 (I                    |                |                   | 110              |                 |       |

|              | •                 |                                         | 0              | , i,              |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •<br>001 = Interr | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      | abled          |                   |                  |                 |       |

| bit 3        | Unimpleme         | ented: Read as 'o                       | )'             |                   |                  |                 |       |

| bit 2-0      | DMA0IP<2:         | 0>: DMA Channe                          | el 0 Data Tra  | nsfer Complete    | e Interrupt Pric | ority bits      |       |

|              | 111 = Interr      | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      |                |                   |                  |                 |       |

# REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

## REGISTER 7-33: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| U-0          | U-0                  | U-0                                     | U-0            | R-0              | R-0            | R-0             | R-0   |

|--------------|----------------------|-----------------------------------------|----------------|------------------|----------------|-----------------|-------|

| _            | -                    | —                                       | _              |                  | IL             | R<3:0>          |       |

| bit 15       |                      |                                         |                |                  |                |                 | bit 8 |

|              |                      |                                         |                |                  |                |                 |       |

| U-0          | U-0                  | R-0                                     | R-0            | R-0              | R-0            | R-0             | R-0   |

|              |                      |                                         |                | VECNUM<6:0       | >              |                 |       |

| bit 7        |                      |                                         |                |                  |                |                 | bit 0 |

| Legend:      |                      |                                         |                |                  |                |                 |       |

| R = Readab   | le bit               | W = Writable                            | bit            | U = Unimpler     | nented bit, re | ad as '0'       |       |

| -n = Value a | t POR                | '1' = Bit is set                        |                | '0' = Bit is cle | ared           | x = Bit is unkr | nown  |

| bit 11-8     | 1111 = CPL<br>•<br>• | lew CPU Interrup<br>J Interrupt Priorit | y Level is 15  | el bits          |                |                 |       |

|              | 0000 <b>= CPL</b>    | J Interrupt Priorit                     | y Level is 0   |                  |                |                 |       |

| bit 7        | •                    | nted: Read as '                         |                |                  |                |                 |       |

| bit 6-0      | 1111111 =<br>•<br>•  | :0>: Vector Num<br>Interrupt Vector     | pending is nur | mber 135         | i              |                 |       |

|              |                      | Interrupt Vector<br>Interrupt Vector    | U U            |                  |                |                 |       |

## REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0           | U-0                  | U-0                                                                                              | U-0            | R-1               | R-1              | R-1             | R-1   |  |  |  |  |  |

|---------------|----------------------|--------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|--|

| _             | _                    |                                                                                                  | —              |                   | LSTC             | H<3:0>          |       |  |  |  |  |  |

| bit 15        |                      |                                                                                                  |                |                   |                  |                 | bit 8 |  |  |  |  |  |

|               |                      | <b>D</b> 0                                                                                       | <b>D</b> 0     | <b>D</b> 0        |                  |                 |       |  |  |  |  |  |

| R-0           | R-0                  | R-0                                                                                              | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |  |

| PPST7         | PPST6                | PPST5                                                                                            | PPST4          | PPST3             | PPST2            | PPST1           | PPST0 |  |  |  |  |  |

| bit 7         |                      |                                                                                                  |                |                   |                  |                 | bit 0 |  |  |  |  |  |

| Legend:       |                      |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |  |

| R = Readabl   | e bit                | W = Writable                                                                                     | bit            | U = Unimplem      | nented bit, read | d as '0'        |       |  |  |  |  |  |

| -n = Value at | POR                  | '1' = Bit is set                                                                                 |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |  |  |  |  |

|               |                      |                                                                                                  |                |                   |                  |                 |       |  |  |  |  |  |

| bit 15-12     | Unimplemen           | ted: Read as 'o                                                                                  | )'             |                   |                  |                 |       |  |  |  |  |  |

| bit 11-8      | LSTCH<3:0>           | : Last DMA Ch                                                                                    | annel Active b | oits              |                  |                 |       |  |  |  |  |  |

|               |                      |                                                                                                  | s occurred sin | ce system Res     | et               |                 |       |  |  |  |  |  |

|               | 1110-1000 =          | Reserved                                                                                         |                | annol 7           |                  |                 |       |  |  |  |  |  |

|               |                      | data transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |  |

|               | 0101 = Last c        | data transfer wa                                                                                 | as by DMA Ch   | annel 5           |                  |                 |       |  |  |  |  |  |

|               | 0100 <b>= Last c</b> | 0101 = Last data transfer was by DMA Channel 5<br>0100 = Last data transfer was by DMA Channel 4 |                |                   |                  |                 |       |  |  |  |  |  |

|               |                      | 0011 = Last data transfer was by DMA Channel 3<br>0010 = Last data transfer was by DMA Channel 2 |                |                   |                  |                 |       |  |  |  |  |  |

|               |                      | lata transfer wa<br>lata transfer wa                                                             |                |                   |                  |                 |       |  |  |  |  |  |

|               |                      | data transfer wa                                                                                 |                |                   |                  |                 |       |  |  |  |  |  |

| bit 7         | PPST7: Chan          | nel 7 Ping-Pon                                                                                   | ig Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |  |

|               |                      | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |  |

| bit 6         |                      | nnel 6 Ping-Pon                                                                                  | -              | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec<br>A register selec                                                             |                |                   |                  |                 |       |  |  |  |  |  |

| bit 5         | PPST5: Chan          | nnel 5 Ping-Pon                                                                                  | ig Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec<br>A register selec                                                             |                |                   |                  |                 |       |  |  |  |  |  |

| bit 4         |                      | nel 4 Ping-Pon                                                                                   |                | s Elag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec                                                                                 | -              | o :               |                  |                 |       |  |  |  |  |  |

|               |                      | A register selec                                                                                 |                |                   |                  |                 |       |  |  |  |  |  |

| bit 3         | PPST3: Chan          | nnel 3 Ping-Pon                                                                                  | ig Mode Statu  | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec<br>A register selec                                                             |                |                   |                  |                 |       |  |  |  |  |  |

| bit 2         |                      | nel 2 Ping-Pon                                                                                   |                | s Flag bit        |                  |                 |       |  |  |  |  |  |

|               | 1 = DMA2STE          | B register selec                                                                                 | ted            | Ū                 |                  |                 |       |  |  |  |  |  |

| bit 1         |                      | nel 1 Ping-Pon                                                                                   |                | s Elag bit        |                  |                 |       |  |  |  |  |  |

|               |                      | B register selec                                                                                 | •              |                   |                  |                 |       |  |  |  |  |  |

|               | 0 = DMA1STA          | •                                                                                                |                |                   |                  |                 |       |  |  |  |  |  |

|               |                      | Tregister Selec                                                                                  | leu            |                   |                  |                 |       |  |  |  |  |  |

| bit 0         | PPST0: Chan          | nel 0 Ping-Pon                                                                                   |                | s Flag bit        |                  |                 |       |  |  |  |  |  |

#### 11.2 **Open-Drain Configuration**

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "Pin Diagrams" for the available pins and their functionality.

#### 11.3 **Configuring Analog Port Pins**

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the Analog-to-Digital port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

MOV W0, TRISBB NOP PORTB, #13 btss

11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification