Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 256КВ (85.5К х 24)                                                             |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b, 32x12b                                                             |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp210-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, which is available from the Microchip website (www.microchip.com).

#### 2.1 Basic Connection Requirements

Getting started with the PIC24HJXXXGPX06/X08/X10 family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors") • VCAP/VDDCORE

- (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss    | pins | mu  | st be |

|-------|-------|---------|-------|---------|------|-----|-------|

|       | conn  | ected   | indep | endent  | of   | the | ADC   |

|       | volta | ge refe | rence | source. |      |     |       |

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide" DS51331

- "Using MPLAB<sup>®</sup> ICD 2" (poster) DS51265

- "MPLAB<sup>®</sup> ICD 2 Design Advisory" DS51566

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide"* DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

#### 2.6 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

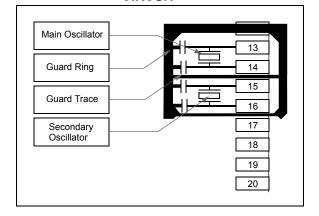

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### FIGURE 2-3: S

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| <b>REGISTER 3-2:</b> CORCON: CORE CONTROL REGISTER |

|----------------------------------------------------|

|----------------------------------------------------|

| U-0              | U-0                                                                   | U-0              | U-0        | U-0                        | U-0              | U-0    | U-0   |

|------------------|-----------------------------------------------------------------------|------------------|------------|----------------------------|------------------|--------|-------|

| —                | —                                                                     | —                | —          | —                          | -                | —      | —     |

| bit 15           |                                                                       |                  |            |                            |                  |        | bit 8 |

|                  |                                                                       |                  |            |                            |                  |        |       |

| U-0              | U-0                                                                   | U-0              | U-0        | R/C-0                      | R/W-0            | U-0    | U-0   |

| —                | —                                                                     | —                | —          | IPL3 <sup>(1)</sup>        | PSV              | —      | —     |

| bit 7            |                                                                       |                  |            |                            |                  |        | bit 0 |

|                  |                                                                       |                  |            |                            |                  |        |       |

| Legend:          |                                                                       | C = Clear only   | y bit      |                            |                  |        |       |

| R = Readable     | bit                                                                   | W = Writable     | bit        | -n = Value at POR '1' = Bi |                  |        |       |

| 0' = Bit is clea | ared                                                                  | 'x = Bit is unki | nown       | U = Unimpler               | nented bit, read | as '0' |       |

| bit 15-4         | Unimplemen                                                            | ted: Read as '   | 0'         |                            |                  |        |       |

| bit 3            | <b>IPL3:</b> CPU Interrupt Priority Level Status bit 3 <sup>(1)</sup> |                  |            |                            |                  |        |       |

|                  | 1 = CPU interrupt priority level is greater than 7                    |                  |            |                            |                  |        |       |

|                  | 0 = CPU interrupt priority level is 7 or less                         |                  |            |                            |                  |        |       |

| bit 2            | <b>PSV:</b> Program Space Visibility in Data Space Enable bit         |                  |            |                            |                  |        |       |

|                  | 1 = Program                                                           | space visible in | data space |                            |                  |        |       |

|                  | •                                                                     | space not visibl |            | ce                         |                  |        |       |

|                  |                                                                       |                  |            |                            |                  |        |       |

bit 1-0 Unimplemented: Read as '0'

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

| TABLE 4-20:       ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506/510/610 DEVICES ONLY (CONTINUED) |      |           |           |        |          |          |          |       |       |       |       |       |       |       |       |       |       |               |

|----------------------------------------------------------------------------------------------------------------|------|-----------|-----------|--------|----------|----------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| File Name                                                                                                      | Addr | Bit 15    | Bit 14    | Bit 13 | Bit 12   | Bit 11   | Bit 10   | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID                                                                                                     | 046E |           | EID<15:8> |        |          |          |          |       |       | EID<  | 7:0>  |       |       |       | xxxx  |       |       |               |

| C1RXF12SID                                                                                                     | 0470 | SID<10:3> |           |        |          |          | SID<2:0> |       | _     | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |       |       |               |

| C1RXF12EID                                                                                                     | 0472 | EID<15:8> |           |        |          |          |          |       | EID<  | 7:0>  |       |       |       | xxxx  |       |       |       |               |

| C1RXF13SID                                                                                                     | 0474 | SID<10:3> |           |        |          | SID<2:0> |          | _     | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |       |       |       |               |

| C1RXF13EID                                                                                                     | 0476 | EID<15:8> |           |        |          |          |          |       | EID<  | 7:0>  |       |       |       | xxxx  |       |       |       |               |

| C1RXF14SID                                                                                                     | 0478 |           | SID<10:3> |        |          |          | SID<2:0> |       | _     | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |       |       |               |

| C1RXF14EID                                                                                                     | 047A | EID<15:8> |           |        | EID<7:0> |          |          |       | xxxx  |       |       |       |       |       |       |       |       |               |

| C1RXF15SID                                                                                                     | 047C |           | SID<10:3> |        |          |          | SID<2:0> |       | —     | EXIDE | —     | EID<1 | 7:16> | xxxx  |       |       |       |               |

| C1RXF15EID                                                                                                     | 047E |           |           |        | EID<     | 15:8>    |          |       |       |       |       |       | EID<  | 7:0>  |       |       |       | xxxx          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices. Legend:

| R/W-0        | R/W-0                | U-0                                 | U-0             | U-0                   | U-0               | U-0              | R/W-0        |

|--------------|----------------------|-------------------------------------|-----------------|-----------------------|-------------------|------------------|--------------|

| TRAPR        | IOPUWR               |                                     | _               |                       | _                 |                  | VREGS        |

| bit 15       |                      |                                     |                 |                       |                   |                  | bit          |

| R/W-0        | R/W-0                | R/W-0                               | R/W-0           | R/W-0                 | R/W-0             | R/W-1            | R/W-1        |

| EXTR         | SWR                  | SWDTEN <sup>(2)</sup>               | WDTO            | SLEEP                 | IDLE              | BOR              | POR          |

| bit 7        |                      |                                     |                 |                       |                   |                  | bit          |

| Legend:      |                      |                                     |                 |                       |                   |                  |              |

| R = Readab   | le bit               | W = Writable I                      | oit             | U = Unimpler          | nented bit, read  | as '0'           |              |

| -n = Value a | t POR                | '1' = Bit is set                    |                 | '0' = Bit is cle      | ared              | x = Bit is unk   | nown         |

| bit 15       | TRAPR: Tran          | Reset Flag bit                      |                 |                       |                   |                  |              |

| bit 10       |                      | onflict Reset ha                    | s occurred      |                       |                   |                  |              |

|              | •                    | onflict Reset ha                    |                 | d                     |                   |                  |              |

| bit 14       | IOPUWR: Ille         | gal Opcode or                       | Uninitialized \ | N Access Rese         | et Flag bit       |                  |              |

|              |                      |                                     |                 | al address mo         | ode or uninitiali | zed W registe    | er used as a |

|              |                      | Pointer caused<br>opcode or unir    |                 | eset has not o        | courred           |                  |              |

| bit 13-9     |                      | ted: Read as '                      |                 |                       | conco             |                  |              |

| bit 8        | -                    | age Regulator S                     |                 | a Sleen hit           |                   |                  |              |

|              |                      | egulator is activ                   | •               | • .                   |                   |                  |              |

|              | •                    | egulator goes i                     | •               | •                     | еер               |                  |              |

| bit 7        |                      | nal Reset (MCL                      |                 |                       |                   |                  |              |

|              |                      | Clear (pin) Res<br>Clear (pin) Res  |                 |                       |                   |                  |              |

| bit 6        |                      |                                     |                 |                       |                   |                  |              |

|              |                      | re Reset (Instruinstruction has     |                 |                       |                   |                  |              |

|              |                      | instruction has                     |                 |                       |                   |                  |              |

| bit 5        | SWDTEN: So           | oftware Enable/                     | Disable of WI   | DT bit <sup>(2)</sup> |                   |                  |              |

|              | 1 = WDT is e         |                                     |                 |                       |                   |                  |              |

|              | 0 = WDT is di        |                                     |                 |                       |                   |                  |              |

| bit 4        |                      | hdog Timer Tim<br>-out has occur    | -               | t                     |                   |                  |              |

|              |                      | e-out has occur                     |                 |                       |                   |                  |              |

| bit 3        |                      | e-up from Sleep                     |                 |                       |                   |                  |              |

|              |                      | as been in Slee                     | -               |                       |                   |                  |              |

|              | 0 = Device ha        | as not been in S                    | leep mode       |                       |                   |                  |              |

| bit 2        |                      | up from Idle Fla                    | g bit           |                       |                   |                  |              |

|              |                      | as in Idle mode<br>as not in Idle m | odo             |                       |                   |                  |              |

| bit 1        |                      | out Reset Flag                      |                 |                       |                   |                  |              |

|              |                      | out Reset has c                     |                 |                       |                   |                  |              |

|              |                      | out Reset has r                     |                 |                       |                   |                  |              |

| bit 0        | POR: Power-          | on Reset Flag I                     | oit             |                       |                   |                  |              |

|              |                      | on Reset has o                      |                 |                       |                   |                  |              |

|              | 0 = A Power-0        | on Reset has n                      | ot occurred     |                       |                   |                  |              |

|              | All of the Reset sta |                                     | e set or cleare | ed in software.       | Setting one of th | nese bits in sof | tware does n |

| 0            | cause a device R     | eset.                               |                 |                       |                   |                  |              |

### 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| REGISTER /-IU. IEGU. INTERROFTENADEL CONTROL REGISTER U | REGISTER 7-10: | IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 |

|---------------------------------------------------------|----------------|-------------------------------------------|

|---------------------------------------------------------|----------------|-------------------------------------------|

| U-0           | R/W-0        | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------|-----------------------------------|-----------------|------------------|------------------|-----------------|--------|

| _             | DMA1IE       | AD1IE                             | U1TXIE          | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |

| bit 15        |              |                                   |                 |                  |                  |                 | bit 8  |

|               |              |                                   |                 |                  |                  |                 |        |

| R/W-0         | R/W-0        | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE        | IC2IE                             | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INT0IE |

| bit 7         |              |                                   |                 |                  |                  |                 | bit C  |

| Legend:       |              |                                   |                 |                  |                  |                 |        |

| R = Readable  | e bit        | W = Writable                      | bit             | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at | POR          | '1' = Bit is set                  | t               | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |

|               |              |                                   |                 |                  |                  |                 |        |

| bit 15        | Unimplemen   | ted: Read as '                    | 0'              |                  |                  |                 |        |

| bit 14        |              |                                   |                 | Complete Interr  | rupt Enable bit  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 13        |              | •                                 |                 | rupt Enable bit  |                  |                 |        |

|               |              | request enable                    | -               |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

| bit 12        | U1TXIE: UAF  | RT1 Transmitte                    | r Interrupt Ena | able bit         |                  |                 |        |

|               |              | request enable                    |                 |                  |                  |                 |        |

| bit 11        | -            | request not ena                   |                 | la hit           |                  |                 |        |

|               |              | RT1 Receiver I<br>request enable  | •               |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

| bit 10        | SPI1IE: SPI1 | Event Interrup                    | t Enable bit    |                  |                  |                 |        |

|               |              | request enable                    |                 |                  |                  |                 |        |

| L:1 0         |              | request not en                    |                 |                  |                  |                 |        |

| bit 9         |              | 1 Error Interru<br>request enable |                 |                  |                  |                 |        |

|               |              | request not enable                |                 |                  |                  |                 |        |

| bit 8         | T3IE: Timer3 | Interrupt Enab                    | le bit          |                  |                  |                 |        |

|               |              | equest enable                     |                 |                  |                  |                 |        |

|               | -            | request not en                    |                 |                  |                  |                 |        |

| bit 7         |              | Interrupt Enab                    |                 |                  |                  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 6         | •            | •                                 |                 | upt Enable bit   |                  |                 |        |

|               | -            | request enable                    |                 |                  |                  |                 |        |

|               | •            | request not en                    |                 |                  |                  |                 |        |

| bit 5         |              | Capture Chann                     | -               | Enable bit       |                  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 4         | -            | -                                 |                 | Complete Interr  | rupt Enable bit  |                 |        |

| •             |              | request enable                    |                 |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

|               |              |                                   |                 |                  |                  |                 |        |

| bit 3         | T1IE: Timer1 | Interrupt Enab                    | ole bit         |                  |                  |                 |        |

NOTES:

#### **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0      | U-0   |

|--------|-----|--------|---------|--------|-------|----------|-------|

| _      | _   | OCSIDL | —       | _      | —     | —        | _     |

| bit 15 |     |        |         |        |       |          | bit 8 |

|        |     |        |         |        |       |          |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

| —      | -   | —      | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7  |     |        |         |        |       |          | bit 0 |

|--|

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                   |

|           | 1 = Output Compare x halts in CPU Idle mode                                                            |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                                             |

| bit 12-5  | Unimplemented: Read as '0'                                                                             |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                  |

|           | 1 = PWM Fault condition has occurred (cleared in hardware only)                                        |

|           | 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111)                    |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                |

|           | 1 = Timer3 is the clock source for Compare x                                                           |

|           | 0 = Timer2 is the clock source for Compare x                                                           |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                              |

|           | 111 = PWM mode on OCx, Fault pin enabled                                                               |

|           | 110 = PWM mode on OCx, Fault pin disabled                                                              |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin                             |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin                                  |

|           | 011 = Compare event toggles OCx pin<br>010 = Initialize OCx pin high, compare event forces OCx pin low |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin low                                         |

|           | 000 = Output compare channel is disabled                                                               |

|           |                                                                                                        |

#### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ADDEN:</b> Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                         |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul>                                                     |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                                                                                 |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

**Note 1:** Refer to **Section 17. "UART"** (DS70232) in the *"PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

### 19.0 ENHANCED CAN (ECAN™) MODULE

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70226), which is available from the Microchip website (www.microchip.com).

#### 19.1 Overview

The Enhanced Controller Area Network (ECAN<sup>™</sup>) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The PIC24HJXXXGPX06/X08/X10 devices contain up to two ECAN modules.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and extended data frames

- · 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to 8 transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer may contain up to 8 bytes of data)

- Up to 16 full (standard/extended identifier) acceptance filters

- 3 full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to input capture module (IC2 for both CAN1 and CAN2) for time-stamping and

network synchronization

· Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### 19.2 Frame Types

The CAN module transmits various types of frames which include data messages, remote transmission requests and as other frames that are automatically generated for control purposes. The following frame types are supported:

· Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit standard identifier (SID) but not an 18-bit extended identifier (EID).

Extended Data Frame:

An extended data frame is similar to a standard data frame but includes an extended identifier as well.

· Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

· Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

· Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

'1' = Bit is set

#### REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                                   | (n = 0, | 1,, 31) |         |              |                  |         |         |

|-----------------------------------|---------|---------|---------|--------------|------------------|---------|---------|

| U-0                               | U-0     | U-0     | R/W-x   | R/W-x        | R/W-x            | R/W-x   | R/W-x   |

| —                                 | _       | —       | FILHIT4 | FILHIT3      | FILHIT2          | FILHIT1 | FILHIT0 |

| bit 15                            |         |         |         |              |                  |         | bit 8   |

|                                   |         |         |         |              |                  |         |         |

| U-0                               | U-0     | U-0     | U-0     | U-0          | U-0              | U-0     | U-0     |

| —                                 | —       | —       | —       | —            | _                | —       | —       |

| bit 7                             |         |         |         |              |                  |         | bit 0   |

|                                   |         |         |         |              |                  |         |         |

| Legend:                           |         |         |         |              |                  |         |         |

| R = Readable bit W = Writable bit |         |         |         | U = Unimpler | mented bit, read | as '0'  |         |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

### 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 16. "Analog-to-Digital Converter (ADC)" (DS70225), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 devices have up to 32 Analog-to-Digital input channels. These devices also have up to 2 Analog-to-Digital converter modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

#### 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- · Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Two result alignment options (signed/unsigned)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the Analog-to-Digital Converter can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the device data sheet for further details.

A block diagram of the Analog-to-Digital Converter is shown in Figure 20-1.

### 20.2 Analog-to-Digital Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on the ADC module (ADxCON1<15>)

- Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

2.

b) Select ADC interrupt priority

#### 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

### 21.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Code-Guard<sup>™</sup> Security" (DS70239), Section 24. "Programming and Diagnostics" (DS70246), and Section 25. "Device Configuration" (DS70231) in the "PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

PIC24HJXXXGPX06/X08/X10 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- In-Circuit Emulation

#### 21.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The device Configuration register map is shown in Table 21-1.

The individual Configuration bit descriptions for the FBS, FSS, FGS, FOSCSEL, FOSC, FWDT and FPOR Configuration registers are shown in Table 21-2.

Note that address 0xF80000 is beyond the user program memory space. In fact, it belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The upper byte of all device Configuration registers should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

To prevent inadvertent configuration changes during code execution, all programmable Configuration bits are write-once. After a bit is initially programmed during a power cycle, it cannot be written to again. Changing a device configuration requires that power to the device be cycled.

| Address  | Name    | Bit 7  | Bit 6                   | Bit 5  | Bit 4          | Bit 3  | Bit 2    | Bit 1    | Bit 0   |  |  |

|----------|---------|--------|-------------------------|--------|----------------|--------|----------|----------|---------|--|--|

| 0xF80000 | FBS     | RBS    | <1:0>                   | —      | _              |        | BSS<2:0> |          | BWRP    |  |  |

| 0xF80002 | FSS     | RSS    | <1:0>                   | _      | _              |        | SSS<2:0> |          | SWRP    |  |  |

| 0xF80004 | FGS     | _      | —                       | _      | _              | —      | GSS<1    | :0>      | GWRP    |  |  |

| 0xF80006 | FOSCSEL | IESO   | Reserved <sup>(2)</sup> | _      | _              | —      | FNC      | )SC<2:0> |         |  |  |

| 0xF80008 | FOSC    | FCKSI  | VI<1:0>                 | _      | _              | —      | OSCIOFNC | POSCN    | 1D<1:0> |  |  |

| 0xF8000A | FWDT    | FWDTEN | WINDIS                  | _      | WDTPRE         |        | WDTPOST- | <3:0>    |         |  |  |

| 0xF8000C | FPOR    | _      | _                       | _      | _              | —      | FPW      | /RT<2:0> |         |  |  |

| 0xF8000E | FICD    | Rese   | ved <sup>(1)</sup>      | JTAGEN | _              | —      | —        | ICS<     | :1:0>   |  |  |

| 0xF80010 | FUID0   |        |                         |        | User Unit ID E | Byte 0 |          |          |         |  |  |

| 0xF80012 | FUID1   |        |                         |        | User Unit ID E | Byte 1 |          |          |         |  |  |

| 0xF80014 | FUID2   |        | User Unit ID Byte 2     |        |                |        |          |          |         |  |  |

| 0xF80016 | FUID3   |        |                         |        | User Unit ID E | Byte 3 |          |          |         |  |  |

#### TABLE 21-1: DEVICE CONFIGURATION REGISTER MAP

Note 1: When read, these bits will appear as '1'. When you write to these bits, set these bits to '1'.

2: When read, this bit returns the current programmed value.

#### 24.1 DC Characteristics

| Characteristic | VDD Range  | Temp Range     | Max MIPS                |

|----------------|------------|----------------|-------------------------|

| onaracteristic | (in Volts) | (in °C)        | PIC24HJXXXGPX06/X08/X10 |

|                | 3.0-3.6V   | -40°C to +85°C | 40                      |

#### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

#### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----|------|------|

| Industrial Temperature Devices                                                                                                                                                         |        |               |     |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | _   | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | _   | +85  | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O   |     |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax  | (TJ – TA)/θJA |     |      | W    |

#### TABLE 24-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                                        | Symbol | Тур | Мах | Unit | Notes |

|-------------------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θja    | 40  |     | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θја    | 40  | _   | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θја    | 40  | _   | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

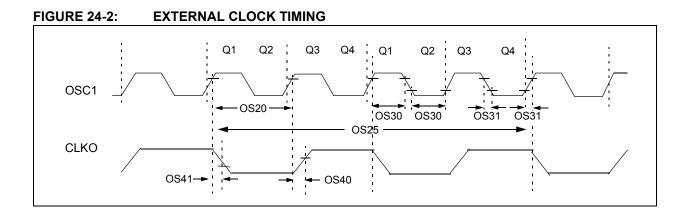

| TABLE 24-16: | EXTERNAL | CLOCK TIM | ING | REQUI  | REME   | NTS    |         |        |

|--------------|----------|-----------|-----|--------|--------|--------|---------|--------|

|              |          |           |     | Standa | rd Ope | rating | Conditi | ons: 3 |

|              |          |           |     |        |        |        |         |        |

| AC CHA       | RACTE         | RISTICS                                                                            | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |                |                   |                          |  |

|--------------|---------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|

| Param<br>No. | Sym<br>bol    | Characteristic                                                                     | Min                                                                                                                                             | Typ <sup>(1)</sup> | Мах            | Units             | Conditions               |  |

| OS10         | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                              | —                  | 40             | MHz               | EC                       |  |

|              |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                                                                                                                       |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |

| OS20         | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                                                                                                            |                    | DC             | ns                | —                        |  |

| OS25         | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                                                                                                              |                    | DC             | ns                | —                        |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                    | —                  | 0.625 x Tosc   | ns                | EC                       |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                                                                                                               | —                  | 20             | ns                | EC                       |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | —                                                                                                                                               | 5.2                | —              | ns                | —                        |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      | —                                                                                                                                               | 5.2                | —              | ns                | —                        |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                                                                                                              | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: Instruction cycle period (Tcr) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: Data for this parameter is Preliminary. This parameter is characterized, but not tested in manufacturing.

#### TABLE 24-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial |     |       |                                                                                        |  |  |  |

|--------------------|--------|----------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                  | Min  | Тур <sup>(2)</sup>                                                                                                                                | Мах | Units | Conditions                                                                             |  |  |  |

| SY10               | TMCL   | MCLR Pulse-Width (low)                                         | 2    | —                                                                                                                                                 | _   | μs    | -40°C to +85°C                                                                         |  |  |  |

| SY11               | Tpwrt  | Power-up Timer Period                                          | _    | 2<br>4<br>16<br>32<br>64<br>128                                                                                                                   | _   | ms    | -40°C to +85°C<br>User programmable                                                    |  |  |  |

| SY12               | TPOR   | Power-on Reset Delay                                           | 3    | 10                                                                                                                                                | 30  | μs    | -40°C to +85°C                                                                         |  |  |  |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68 | 0.72                                                                                                                                              | 1.2 | μs    | _                                                                                      |  |  |  |

| SY20               | Twdt1  | Watchdog Timer Time-out<br>Period                              | —    | —                                                                                                                                                 | _   | _     | See Section 21.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 24-19) |  |  |  |

| SY30               | Tost   | Oscillator Start-up Timer<br>Period                            | —    | 1024 Tosc                                                                                                                                         | _   | —     | Tosc = OSC1 period                                                                     |  |  |  |

| SY35               | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               | _    | 500                                                                                                                                               | 900 | μs    | -40°C to +85°C                                                                         |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

### 25.0 PACKAGING INFORMATION

#### 25.1 Package Marking Information

64-Lead TQFP (10x10x1 mm)

100-Lead TQFP (12x12x1 mm)

100-Lead TQFP (14x14x1mm)

100-Lead TQFP (14x14x1mm)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                    |

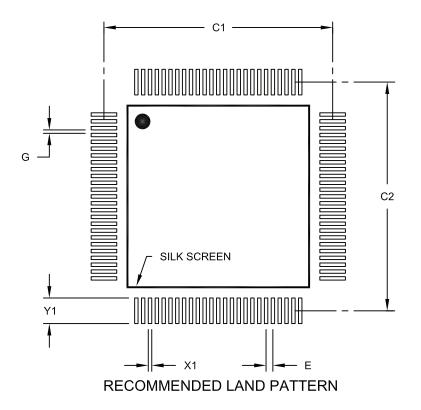

#### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |       |      |

|---------------------------|-------------|------|-------|------|

| Dimension                 | Limits      | MIN  | NOM   | MAX  |

| Contact Pitch             | E 0.40 BSC  |      |       |      |

| Contact Pad Spacing       | C1          |      | 13.40 |      |

| Contact Pad Spacing       | C2          |      | 13.40 |      |

| Contact Pad Width (X100)  | X1          |      |       | 0.20 |

| Contact Pad Length (X100) | Y1          |      |       | 1.50 |

| Distance Between Pads     | G           | 0.20 |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100A

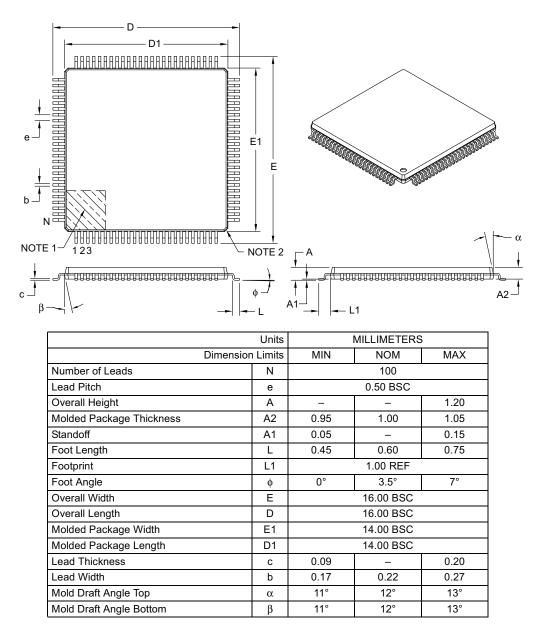

#### 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

#### Revision H (March 2009)

This revision includes minor typographical and formatting changes throughout the data sheet text.

Global changes include:

- Changed all instances of OSCI to OSC1 and OSC0 to OSC2

- Changed all instances of VDDCORE and VDDCORE/ VCAP to VCAP/VDDCORE

The other changes are referenced by their respective section in the following table.

#### TABLE A-2: MAJOR SECTION UPDATES

| Section Name                                                                 | Update Description                                                                                                                                                 |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit<br>Microcontrollers"                               | Updated all pin diagrams to denote the pin voltage tolerance (see " <b>Pin Diagrams</b> ").                                                                        |

|                                                                              | Added Note 2 to the 28-Pin QFN-S and 44-Pin QFN pin diagrams, which references pin connections to Vss.                                                             |

| Section 1.0 "Device Overview"                                                | Updated AVDD in the PINOUT I/O Descriptions (see Table 1-1).                                                                                                       |

| Section 2.0 "Guidelines for Getting<br>Started with 16-Bit Microcontrollers" | Added new section to the data sheet that provides guidelines on getting started with 16-bit Microcontrollers.                                                      |

| Section 4.0 "Memory Organization"                                            | Add Accumulator A and B SFRs (ACCAL, ACCAH, ACCAU, ACCBL, ACCBH and ACCBU) and updated the Reset value for CORCON in the CPU Core Register Map (see Table 4-1).    |

|                                                                              | Updated Reset values for IPC3, IPC4, IPC11 and IPC13-IPC15 in the Interrupt Controller Register Map (see Table 4-5).                                               |

|                                                                              | Updated the Reset value for CLKDIV in the System Control Register Map (see Table 4-31).                                                                            |

| Section 5.0 "Flash Program Memory"                                           | Updated <b>Section 5.3 "Programming Operations"</b> with programming time formula.                                                                                 |

| Section 9.0 "Oscillator Configuration"                                       | Added Note 2 to the Oscillator System Diagram (see Figure 9-1).                                                                                                    |

|                                                                              | Updated default bit values for DOZE<2:0> and FRCDIV<2:0> in the Clock Divisor (CLKDIV) Register (see Register 9-2).                                                |

|                                                                              | Added a paragraph regarding FRC accuracy at the end of <b>Section 9.1.1</b> " <b>System Clock sources</b> ".                                                       |

|                                                                              | Added Note 1 to the FRC Oscillator Tuning (OSCTUN) Register (see Register 9-4).                                                                                    |

| Section 10.0 "Power-Saving                                                   | Added the following registers:                                                                                                                                     |

| Features"                                                                    | • PMD1: Peripheral Module Disable Control Register 1 (Register 10-1)                                                                                               |

|                                                                              | <ul> <li>PMD2: Peripheral Module Disable Control Register 2 (Register 10-2)</li> <li>PMD3: Peripheral Module Disable Control Register 3 (Register 10-3)</li> </ul> |

| Section 11.0 "I/O Ports"                                                     | Added reference to pin diagrams for I/O pin availability and functionality (see <b>Section 11.2 "Open-Drain Configuration"</b> ).                                  |

| Section 16.0 "Serial Peripheral<br>Interface (SPI)"                          | Added Note 2 to the SPIxCON1 register (see Register 16-2).                                                                                                         |

| Section 18.0 "Universal<br>Asynchronous Receiver Transmitter<br>(UART)"      | Updated the UTXINV bit settings in the UxSTA register (see Register 18-2).                                                                                         |