Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 18x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp206-i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| File Name  | Addr          | Bit 15 | Bit 14              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7      | Bit 6    | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1               | Bit 0  | All<br>Resets |

|------------|---------------|--------|---------------------|--------|--------|--------|--------|--------|-------------|------------|----------|--------|-------|-------|--------|---------------------|--------|---------------|

|            | 0400-<br>041E |        |                     | •      |        |        |        |        | See definit | ion when V | VIN = x  | •      | ·     | ·     |        |                     | •      |               |

| C1BUFPNT1  | 0420          |        | F3BF                | P<3:0> |        |        | F2BF   | P<3:0> |             |            | F1BP     | <3:0>  |       |       | F0BP   | <3:0>               |        | 0000          |

| C1BUFPNT2  | 0422          |        | F7BP<3:0> F6BP<3:0> |        |        |        |        |        | F5BP        | <3:0>      |          |        | F4BP  | <3:0> |        | 0000                |        |               |

| C1BUFPNT3  | 0424          |        | F11B                | P<3:0> |        |        | F10B   | P<3:0> |             |            | F9BP     | <3:0>  |       |       | F8BP   | <3:0>               |        | 0000          |

| C1BUFPNT4  | 0426          |        | F15B                | P<3:0> |        |        | F14B   | P<3:0> |             |            | F13BF    | P<3:0> |       |       | F12BF  | <b>?&lt;3:0&gt;</b> |        | 0000          |

| C1RXM0SID  | 0430          |        |                     |        | SID<   | 10:3>  |        |        |             |            | SID<2:0> |        | —     | MIDE  |        | EID<                | 17:16> | xxxx          |

| C1RXM0EID  | 0432          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXM1SID  | 0434          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | MIDE  |        | EID<                | 17:16> | xxxx          |

| C1RXM1EID  | 0436          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXM2SID  | 0438          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | MIDE  |        | EID<                | 17:16> | xxxx          |

| C1RXM2EID  | 043A          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF0SID  | 0440          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF0EID  | 0442          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF1SID  | 0444          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        |       | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF1EID  | 0446          |        | EID<15:8>           |        |        |        |        |        |             | EID<       | 7:0>     |        |       |       | xxxx   |                     |        |               |

| C1RXF2SID  | 0448          |        | SID<10:3>           |        |        |        |        |        | SID<2:0>    |            | —        | EXIDE  |       | EID<  | 17:16> | xxxx                |        |               |

| C1RXF2EID  | 044A          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF3SID  | 044C          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF3EID  | 044E          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF4SID  | 0450          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF4EID  | 0452          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF5SID  | 0454          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF5EID  | 0456          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF6SID  | 0458          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF6EID  | 045A          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF7SID  | 045C          |        |                     |        | SID<   | 10:3>  |        |        |             |            | SID<2:0> |        | —     | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF7EID  | 045E          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF8SID  | 0460          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | _      | EID<                | 17:16> | xxxx          |

| C1RXF8EID  | 0462          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF9SID  | 0464          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | —     | EXIDE | _      | EID<                | 17:16> | xxxx          |

| C1RXF9EID  | 0466          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF10SID | 0468          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        |       | EXIDE |        | EID<                | 17:16> | xxxx          |

| C1RXF10EID | 046A          |        |                     |        | EID<   | :15:8> |        |        |             |            |          |        | EID<  | 7:0>  |        |                     |        | xxxx          |

| C1RXF11SID | 046C          |        |                     |        | SID<   | :10:3> |        |        |             |            | SID<2:0> |        | _     | EXIDE | _      | EID<                | 17:16> | xxxx          |

## TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506/510/610 DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |

| POR (RCON<0>)     | POR                                                  | —                            |

#### TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

## 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

## 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

### REGISTER 7-30: IPC15: INTERRUPT PRIORITY CONTROL REGISTER 15

| U-0       R/W-1       R/W-0       U-0       U-0       U-0       U-0         —       DMA5IP<2:0>       —       —       —       —       —         bit 7       bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                          |                     |                 |                      |                   |                    |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|---------------------|-----------------|----------------------|-------------------|--------------------|-------|

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0       U-0         —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       Is                                                                                                                                                                                                                                                                                                                                            | U-0             | U-0                      | U-0                 | U-0             | U-0                  | U-0               | U-0                | U-0   |

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0       U-0         —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       Is                                                                                                                                                                                                                                                                                                                                            | —               | —                        | —                   | —               | —                    |                   | —                  | _     |

| DMA5IP<2:0>       -       -       -       -       -         bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .                                                                       | bit 15          |                          |                     |                 |                      |                   |                    | bit 8 |

| DMA5IP<2:0>       -       -       -       -       -         bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .                                                                       |                 |                          |                     |                 |                      |                   |                    |       |

| bit 7       bit         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       •       •         001 = Interrupt is priority 1       000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0             | R/W-1                    | R/W-0               | R/W-0           | U-0                  | U-0               | U-0                | U-0   |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —               |                          | DMA5IP<2:0>         |                 | —                    | —                 | —                  | —     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'       bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         . <td>bit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit 0</td> | bit 7           |                          |                     |                 |                      |                   |                    | bit 0 |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                          |                     |                 |                      |                   |                    |       |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-4       DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Legend:         |                          |                     |                 |                      |                   |                    |       |

| <pre>bit 15-7 Unimplemented: Read as '0' bit 6-4 DMA5IP&lt;2:0&gt;: DMA Channel 5 Data Transfer Complete Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R = Readable    | bit                      | W = Writable b      | bit             | U = Unimplen         | nented bit, read  | as '0'             |       |

| bit 6-4 DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -n = Value at F | POR                      | '1' = Bit is set    |                 | '0' = Bit is cleared |                   | x = Bit is unknown |       |

| bit 6-4 DMA5IP<2:0>: DMA Channel 5 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                          |                     |                 |                      |                   |                    |       |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 15-7        | Unimplemen               | ted: Read as '0     | )'              |                      |                   |                    |       |

| •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 6-4         | DMA5IP<2:0               | >: DMA Channe       | el 5 Data Trai  | nsfer Complete       | Interrupt Priorit | y bits             |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                          |                     |                 |                      |                   |                    |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | 111 = Interru            | ot is priority 7 (h | nighest priorit | y interrupt)         |                   |                    |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | 111 = Interruj<br>•      | ot is priority 7 (h | nighest priorit | y interrupt)         |                   |                    |       |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | 111 = Interruj<br>•<br>• | ot is priority 7 (h | ighest priorit  | y interrupt)         |                   |                    |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | •                        |                     | iighest priorit | y interrupt)         |                   |                    |       |

| bit 2.0 Unimplemented: Read as 'o'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | •<br>•<br>001 = Interru  | ot is priority 1    |                 | y interrupt)         |                   |                    |       |

| bit 3-0 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | •<br>•<br>001 = Interru  | ot is priority 1    |                 | y interrupt)         |                   |                    |       |

| R/W-0        | R/W-0                          | R/W-0                                                                                                                                                                                               | R/W-0           | R/W-0                            | U-0             | U-0              | U-0           |  |  |  |  |

|--------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|-----------------|------------------|---------------|--|--|--|--|

| CHEN         | SIZE                           | DIR                                                                                                                                                                                                 | HALF            | NULLW                            | —               | _                | —             |  |  |  |  |

| bit 15       | ·                              |                                                                                                                                                                                                     |                 |                                  |                 |                  | bit           |  |  |  |  |

|              |                                |                                                                                                                                                                                                     |                 |                                  |                 |                  |               |  |  |  |  |

| U-0          | U-0                            | R/W-0                                                                                                                                                                                               | R/W-0           | U-0                              | U-0             | R/W-0            | R/W-0         |  |  |  |  |

| <br>bit 7    | _                              | AMOD                                                                                                                                                                                                | E<1:0>          | —                                | —               | MODE             | -<1:0><br>bit |  |  |  |  |

|              |                                |                                                                                                                                                                                                     |                 |                                  |                 |                  | DIL           |  |  |  |  |

| Legend:      |                                |                                                                                                                                                                                                     |                 |                                  |                 |                  |               |  |  |  |  |

| R = Readab   | ole bit                        | W = Writable                                                                                                                                                                                        | bit             | U = Unimplen                     | nented bit, rea | ad as '0'        |               |  |  |  |  |

| -n = Value a | at POR                         | '1' = Bit is set                                                                                                                                                                                    |                 | '0' = Bit is cle                 | ared            | x = Bit is unkn  | own           |  |  |  |  |

|              |                                |                                                                                                                                                                                                     |                 |                                  |                 |                  |               |  |  |  |  |

| bit 15       |                                | nel Enable bit                                                                                                                                                                                      |                 |                                  |                 |                  |               |  |  |  |  |

|              | 1 = Channel e<br>0 = Channel e |                                                                                                                                                                                                     |                 |                                  |                 |                  |               |  |  |  |  |

| bit 14       |                                | ransfer Size bit                                                                                                                                                                                    | ł               |                                  |                 |                  |               |  |  |  |  |

|              | 1 = Byte                       |                                                                                                                                                                                                     | •               |                                  |                 |                  |               |  |  |  |  |

|              | 0 = Word                       |                                                                                                                                                                                                     |                 |                                  |                 |                  |               |  |  |  |  |

| bit 13       | DIR: Transfer                  | <b>DIR:</b> Transfer Direction bit (source/destination bus select)                                                                                                                                  |                 |                                  |                 |                  |               |  |  |  |  |

|              |                                |                                                                                                                                                                                                     |                 | to peripheral ad<br>o DMA RAM ad |                 |                  |               |  |  |  |  |

| bit 12       | HALF: Early                    | IALF: Early Block Transfer Complete Interrupt Select bit                                                                                                                                            |                 |                                  |                 |                  |               |  |  |  |  |

|              |                                | <ul> <li>1 = Initiate block transfer complete interrupt when half of the data has been moved</li> <li>0 = Initiate block transfer complete interrupt when all of the data has been moved</li> </ul> |                 |                                  |                 |                  |               |  |  |  |  |

| bit 11       | NULLW: Null                    | Data Peripher                                                                                                                                                                                       | al Write Mode   | e Select bit                     |                 |                  |               |  |  |  |  |

|              | 1 = Null data<br>0 = Normal o  |                                                                                                                                                                                                     | eral in additio | n to DMA RAM                     | write (DIR bit  | must also be cle | ar)           |  |  |  |  |

| bit 10-6     | Unimplemen                     | ted: Read as '                                                                                                                                                                                      | 0'              |                                  |                 |                  |               |  |  |  |  |

| bit 5-4      | AMODE<1:0                      | >: DMA Chann                                                                                                                                                                                        | el Operating I  | Mode Select bit                  | S               |                  |               |  |  |  |  |

|              | 01 = Register                  | ral Indirect Ado<br>Indirect witho                                                                                                                                                                  | ut Post-Incren  | nent mode                        |                 |                  |               |  |  |  |  |

|              | -                              | r Indirect with F                                                                                                                                                                                   |                 | nt mode                          |                 |                  |               |  |  |  |  |

| bit 3-2      |                                | ted: Read as '                                                                                                                                                                                      |                 |                                  |                 |                  |               |  |  |  |  |

| bit 1-0      |                                |                                                                                                                                                                                                     |                 | ode Select bits                  | anefor from/to  | each DNAA DAM    | buffer)       |  |  |  |  |

|              |                                | ous, Ping-Pong i<br>ous, Ping-Pong                                                                                                                                                                  |                 |                                  |                 | each DMA RAM     | buller)       |  |  |  |  |

|              | 01 = One-Sh                    | ot, Ping-Pong                                                                                                                                                                                       | nodes disable   | ed                               |                 |                  |               |  |  |  |  |

|              | 00 = Continue                  | oue Ding Dong                                                                                                                                                                                       | n modae dieat   |                                  |                 |                  |               |  |  |  |  |

### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0             | R-0         | R-0                                  | R-0            | U-0              | R/W-y           | R/W-y                    | R/W-y      |

|-----------------|-------------|--------------------------------------|----------------|------------------|-----------------|--------------------------|------------|

| —               |             | COSC<2:0>                            |                | —                |                 | NOSC<2:0> <sup>(2)</sup> |            |

| bit 15          |             |                                      |                |                  |                 |                          | bit 8      |

| R/W-0           | U-0         | R-0                                  | U-0            | R/C-0            | U-0             | R/W-0                    | R/W-0      |

| CLKLOCK         | _           | LOCK                                 | _              | CF               | _               | LPOSCEN                  | OSWEN      |

| bit 7           |             |                                      |                | 0.               |                 |                          | bit 0      |

|                 |             |                                      |                |                  |                 |                          |            |

| Legend:         | ••          | •                                    | •              | ation bits on P  |                 | C = Clear                | r only bit |

| R = Readable I  |             | W = Writable                         | bit            | -                | nented bit, rea |                          |            |

| -n = Value at P | OR          | '1' = Bit is set                     |                | '0' = Bit is cle | ared            | x = Bit is unkn          | own        |

| bit 15          | Unimplemen  | ted: Read as '                       | ) <b>'</b>     |                  |                 |                          |            |

| bit 14-12       | -           | Current Oscilla                      |                | bits (read-only  | )               |                          |            |

| 51(11)2         |             | C oscillator (FF                     |                |                  | /               |                          |            |

|                 |             | C oscillator (FF                     |                |                  |                 |                          |            |

|                 |             | y oscillator (XT                     |                |                  |                 |                          |            |

|                 |             | y oscillator (XT                     |                | PLL              |                 |                          |            |

|                 |             | dary oscillator (<br>ower RC oscilla |                |                  |                 |                          |            |

|                 |             | C oscillator (FF                     |                | e-by-16          |                 |                          |            |

|                 |             | C oscillator (FF                     |                |                  |                 |                          |            |

| bit 11          | Unimplemen  | ted: Read as '                       | כ'             |                  |                 |                          |            |

| bit 10-8        | NOSC<2:0>:  | New Oscillator                       | Selection bits | <sub>3</sub> (2) |                 |                          |            |

|                 |             | C oscillator (FF                     |                |                  |                 |                          |            |

|                 |             | C oscillator (FF                     |                |                  |                 |                          |            |

|                 |             | y oscillator (XT<br>y oscillator (XT |                | PU               |                 |                          |            |

|                 |             | dary oscillator (                    |                |                  |                 |                          |            |

|                 | 101 = Low-P | ower RC oscilla                      | tor (LPRC)     |                  |                 |                          |            |

|                 |             | C oscillator (FF                     |                |                  |                 |                          |            |

| hit 7           |             | C oscillator (FF<br>Clock Lock Ena   | -              | e-by-n           |                 |                          |            |

| bit 7           |             | M0 = 1), then c                      |                | configurations   | are locked      |                          |            |

|                 |             | MO = 1), then C $MO = 0$ ), then c   |                |                  |                 | ied                      |            |

|                 |             | d PLL selection                      |                |                  |                 |                          |            |

| bit 6           | Unimplemen  | ted: Read as '                       | כ'             |                  |                 |                          |            |

| bit 5           | LOCK: PLL L | ock Status bit (                     | read-only)     |                  |                 |                          |            |

|                 |             | that PLL is in I                     |                |                  |                 |                          |            |

|                 |             | that PLL is out                      |                | up timer is in p | progress or PL  | L is disabled            |            |

| bit 4           | -           | ted: Read as '                       |                |                  |                 |                          |            |

| bit 3           |             | il Detect bit (rea                   |                | plication)       |                 |                          |            |

|                 |             | as detected clo<br>as not detected   |                |                  |                 |                          |            |

|                 |             |                                      |                |                  |                 |                          |            |

| bit 2           | Unimplemen  | ted: Read as '                       | )              |                  |                 |                          |            |

**Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator**" (DS70227) in the *"PIC24H Family Reference Manual"* (available from the Microchip website) for details.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 10. "I/O Ports" (DS70230), which is available from the Microchip website (www.microchip.com).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

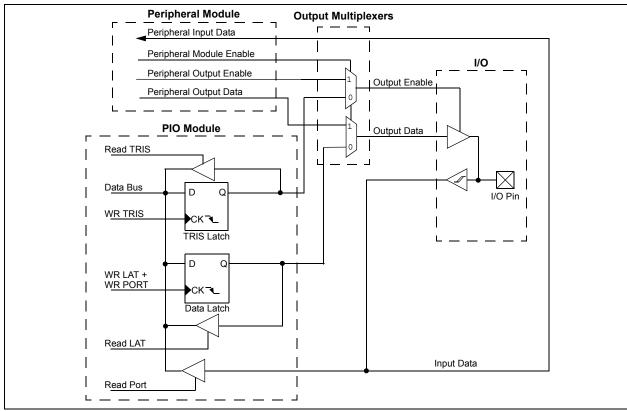

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

**Note:** The voltage on a digital input pin can be between -0.3V to 5.6V.

## FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

| R/W-0          | R/W-0                                                               | R/W-0                                                                                                              | U-0                                         | U-0                          | U-0             | U-0                | U-0   |  |

|----------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|-----------------|--------------------|-------|--|

| FRMEN          | SPIFSD                                                              | FRMPOL                                                                                                             | _                                           | —                            | —               | —                  | —     |  |

| bit 15         |                                                                     |                                                                                                                    |                                             |                              |                 |                    | bit 8 |  |

|                |                                                                     |                                                                                                                    |                                             |                              |                 |                    |       |  |

| U-0            | U-0                                                                 | U-0                                                                                                                | U-0                                         | U-0                          | U-0             | R/W-0              | U-0   |  |

| —              | —                                                                   |                                                                                                                    | _                                           | —                            | —               | FRMDLY             | —     |  |

| bit 7          |                                                                     |                                                                                                                    |                                             |                              |                 |                    | bit 0 |  |

|                |                                                                     |                                                                                                                    |                                             |                              |                 |                    |       |  |

| Legend:        |                                                                     |                                                                                                                    |                                             |                              |                 |                    |       |  |

| R = Readabl    | e bit                                                               | W = Writable I                                                                                                     | oit                                         | U = Unimplen                 | nented bit, rea | ad as '0'          |       |  |

| -n = Value at  | POR                                                                 | '1' = Bit is set                                                                                                   |                                             | '0' = Bit is clea            | ared            | x = Bit is unknown |       |  |

| bit 14         | 0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy | Plx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output                                            | abled<br>Direction Co<br>slave)<br>(master) | in used as fram<br>ntrol bit | e sync pulse    | input/output)      |       |  |

| bit 13         | 1 = Frame sy                                                        | FRMPOL: Frame Sync Pulse Polarity bit<br>1 = Frame sync pulse is active-high<br>0 = Frame sync pulse is active-low |                                             |                              |                 |                    |       |  |

| bit 12-2       | Unimplemen                                                          | ted: Read as 'o                                                                                                    | )'                                          |                              |                 |                    |       |  |

| bit 1<br>bit 0 | 1 = Frame sy<br>0 = Frame sy<br><b>Unimplemen</b>                   | ime Sync Pulse<br>nc pulse coincio<br>nc pulse preceo<br><b>ted:</b> Read as 'o                                    | des with first<br>des first bit cl          | bit clock<br>ock             |                 |                    |       |  |

|                | i his dit must                                                      | not be set to '1                                                                                                   | by the user                                 | application.                 |                 |                    |       |  |

#### REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0 HSC | R-0 HSC | U-0 | U-0 | U-0 | R/C-0 HS | R-0 HSC | R-0 HSC |

|---------|---------|-----|-----|-----|----------|---------|---------|

| ACKSTAT | TRSTAT  | —   | _   | —   | BCL      | GCSTAT  | ADD10   |

| bit 15  |         |     |     |     |          |         | bit 8   |

| R/C-0 HS | R/C-0 HS | R-0 HSC | R/C-0 HSC | R/C-0 HSC | R-0 HSC | R-0 HSC | R-0 HSC |

|----------|----------|---------|-----------|-----------|---------|---------|---------|

| IWCOL    | I2COV    | D_A     | Р         | S         | R_W     | RBF     | TBF     |

| bit 7    |          |         |           |           |         |         | bit 0   |

| Legend:           | U = Unimplemented b | oit, read as '0'     | C = Clear only bit         |

|-------------------|---------------------|----------------------|----------------------------|

| R = Readable bit  | W = Writable bit    | HS = Set in hardware | HSC = Hardware set/cleared |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown         |

| <b>ACKSTAT:</b> Acknowledge Status bit (when operation) (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = NACK received from slave</li> <li>0 = ACK received from slave</li> </ul>                                                                                                                                        |

| Hardware set or clear at end of slave Acknowledge.                                                                                                                                                                           |

| <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                                      |

| <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul> |

| Unimplemented: Read as '0'                                                                                                                                                                                                   |

| BCL: Master Bus Collision Detect bit                                                                                                                                                                                         |

| <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> </ul>                                                                                                                |

| Hardware set at detection of bus collision.                                                                                                                                                                                  |

| GCSTAT: General Call Status bit                                                                                                                                                                                              |

| <ul> <li>1 = General call address was received</li> <li>0 = General call address was not received</li> </ul>                                                                                                                 |

| Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                                                                                    |

| ADD10: 10-Bit Address Status bit                                                                                                                                                                                             |

| 1 = 10-bit address was matched<br>0 = 10-bit address was not matched                                                                                                                                                         |

| Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                                                                               |

| IWCOL: Write Collision Detect bit                                                                                                                                                                                            |

| 1 = An attempt to write the I2CxTRN register failed because the $I^2C$ module is busy<br>0 = No collision                                                                                                                    |

| Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).                                                                                                                                             |

| I2COV: Receive Overflow Flag bit                                                                                                                                                                                             |

| <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                                                                           |

| Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                                                |

| <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                      |

| 1 = Indicates that the last byte received was data                                                                                                                                                                           |

| <ul> <li>Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul>                                                       |

| P: Stop bit                                                                                                                                                                                                                  |

| 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                         |

| 0 = Stop bit was not detected last                                                                                                                                                                                           |

| Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                           |

|                                                                                                                                                                                                                              |

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                | R/W-0                             | R/W-0           | R/W-0                           | U-0                              | R/W-0                  | R/W-0           |  |

|-----------------------|--------------------------------------------------------------------|-----------------------------------|-----------------|---------------------------------|----------------------------------|------------------------|-----------------|--|

| UARTEN <sup>(1)</sup> | <sup>(1)</sup> — USIDL IREN <sup>(2)</sup> RTSMD —                 |                                   |                 |                                 | UEN                              | <1:0>                  |                 |  |

| bit 15                |                                                                    |                                   |                 |                                 |                                  |                        | bit 8           |  |