Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 85                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | - ·                                                                           |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 32x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp210-i-pf |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   |     | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

#### Note 1: For complete register details, see Register 3-1, SR: CPU STATUS Register.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

## REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0                                                | U-0                               | U-0             | U-0            | U-0                                | U-0   | U-0 | U-0   |

|----------------------------------------------------|-----------------------------------|-----------------|----------------|------------------------------------|-------|-----|-------|

| —                                                  | —                                 | —               | —              | —                                  | —     | —   | —     |

| bit 15                                             |                                   |                 |                |                                    |       |     | bit 8 |

|                                                    |                                   |                 |                |                                    |       |     |       |

| U-0                                                | U-0                               | U-0             | U-0            | R/C-0                              | R/W-0 | U-0 | U-0   |

| _                                                  | —                                 |                 | —              | IPL3 <sup>(2)</sup>                | PSV   | —   | —     |

| bit 7                                              |                                   |                 |                |                                    |       |     | bit 0 |

|                                                    |                                   |                 |                |                                    |       |     |       |

| Legend:                                            |                                   | C = Clear only  | / bit          |                                    |       |     |       |

| R = Readable I                                     | R = Readable bit W = Writable bit |                 | bit            | -n = Value at POR '1' = Bit is set |       |     |       |

| 0' = Bit is cleared 'x = Bit is unknown            |                                   |                 | nown           | U = Unimplemented bit, read as '0' |       |     |       |

|                                                    |                                   |                 |                | (0)                                |       |     |       |

| bit 3                                              | IPL3: CPU Int                     | errupt Priority | Level Status b | bit $3^{(2)}$                      |       |     |       |

| 1 = CPU interrupt priority level is greater than 7 |                                   |                 |                |                                    |       |     |       |

0 = CPU interrupt priority level is 7 or less

#### Note 1: For complete register details, see Register 3-2, CORCON: CORE Control Register.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IF:</b> Output Compare Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IF:</b> Input Capture Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred  |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                     |

| U-0             | U-0                                                                | U-0              | U-0             | U-0              | U-0              | U-0             | U-0 |

|-----------------|--------------------------------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|-----|

| _               | _                                                                  | _                | _               |                  | _                |                 | _   |

| bit 15          |                                                                    |                  |                 |                  |                  |                 | bit |

| DAMA            | DAVA                                                               | D/// 0           | DAMA            |                  | DAMA             | DAMA            |     |

| R/W-0<br>C2TXIE | R/W-0<br>C1TXIE                                                    | R/W-0<br>DMA7IE  | R/W-0<br>DMA6IE | U-0              | R/W-0<br>U2EIE   | R/W-0<br>U1EIE  | U-0 |

| bit 7           | CITALE                                                             | DIMATIE          | DIVIAOIE        | —                | UZEIE            | UTEIE           | bit |

|                 |                                                                    |                  |                 |                  |                  |                 |     |

| Legend:         |                                                                    |                  |                 |                  |                  |                 |     |

| R = Readabl     |                                                                    | W = Writable     |                 | •                | mented bit, read |                 |     |

| -n = Value at   | POR                                                                | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkn | own |

| bit 15-8        | Unimplomon                                                         | ted: Read as '   | o'              |                  |                  |                 |     |

| bit 7           | -                                                                  |                  |                 | Interrupt Enabl  | e hit            |                 |     |

|                 |                                                                    | equest enable    | •               |                  |                  |                 |     |

|                 |                                                                    | equest not ena   |                 |                  |                  |                 |     |

| bit 6           | •                                                                  | •                |                 | Interrupt Enabl  | e bit            |                 |     |

|                 |                                                                    | equest enable    | •               | ·                |                  |                 |     |

|                 | 0 = Interrupt r                                                    | equest not ena   | abled           |                  |                  |                 |     |

| bit 5           | DMA7IE: DM                                                         | A Channel 7 D    | ata Transfer (  | Complete Enab    | le Status bit    |                 |     |

|                 |                                                                    | equest enable    |                 |                  |                  |                 |     |

|                 | •                                                                  | equest not ena   |                 |                  |                  |                 |     |

| bit 4           |                                                                    |                  |                 | Complete Enab    | le Status bit    |                 |     |

|                 | 1 = Interrupt request enabled                                      |                  |                 |                  |                  |                 |     |

|                 | •                                                                  | equest not ena   |                 |                  |                  |                 |     |

| bit 3           | -                                                                  | ted: Read as '   |                 |                  |                  |                 |     |

| bit 2           | U2EIE: UART2 Error Interrupt Enable bit                            |                  |                 |                  |                  |                 |     |

|                 | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled |                  |                 |                  |                  |                 |     |

| bit 1           | U1EIE: UART1 Error Interrupt Enable bit                            |                  |                 |                  |                  |                 |     |

|                 |                                                                    | equest enable    |                 |                  |                  |                 |     |

|                 | 0 = Interrupt r                                                    | equest not ena   | abled           |                  |                  |                 |     |

| bit 0           | Unimplemented: Read as '0'                                         |                  |                 |                  |                  |                 |     |

## REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

## REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0           | U-0                                                                                     | U-0                                  | U-0            | R-1               | R-1              | R-1             | R-1        |

|---------------|-----------------------------------------------------------------------------------------|--------------------------------------|----------------|-------------------|------------------|-----------------|------------|

| _             | _                                                                                       |                                      | —              |                   | LSTC             | H<3:0>          |            |

| bit 15        |                                                                                         |                                      |                |                   |                  |                 | bit 8      |

|               |                                                                                         | <b>D</b> 0                           | <b>D</b> 0     | <b>D</b> 0        |                  |                 | <b>D</b> 0 |

| R-0           | R-0                                                                                     | R-0                                  | R-0            | R-0               | R-0              | R-0             | R-0        |

| PPST7         | PPST6                                                                                   | PPST5                                | PPST4          | PPST3             | PPST2            | PPST1           | PPST0      |

| bit 7         |                                                                                         |                                      |                |                   |                  |                 | bit 0      |

| Legend:       |                                                                                         |                                      |                |                   |                  |                 |            |

| R = Readabl   | e bit                                                                                   | W = Writable                         | bit            | U = Unimplem      | nented bit, read | d as '0'        |            |

| -n = Value at | POR                                                                                     | '1' = Bit is set                     |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown       |

|               |                                                                                         |                                      |                |                   |                  |                 |            |

| bit 15-12     | Unimplemen                                                                              | ted: Read as 'o                      | )'             |                   |                  |                 |            |

| bit 11-8      | LSTCH<3:0>                                                                              | : Last DMA Ch                        | annel Active b | oits              |                  |                 |            |

|               |                                                                                         |                                      | s occurred sin | ce system Res     | et               |                 |            |

|               | 1110-1000 =                                                                             | Reserved                             |                | annol 7           |                  |                 |            |

|               |                                                                                         | data transfer wa                     |                |                   |                  |                 |            |

|               | 0101 = Last c                                                                           | data transfer wa                     | as by DMA Ch   | annel 5           |                  |                 |            |

|               | 0100 <b>= Last c</b>                                                                    | data transfer wa                     | as by DMA Ch   | annel 4           |                  |                 |            |

|               |                                                                                         | data transfer wa                     |                |                   |                  |                 |            |

|               |                                                                                         | data transfer wa<br>data transfer wa |                |                   |                  |                 |            |

|               |                                                                                         | data transfer wa                     |                |                   |                  |                 |            |

| bit 7         | PPST7: Chan                                                                             | nel 7 Ping-Pon                       | ig Mode Statu  | s Flag bit        |                  |                 |            |

|               |                                                                                         | B register selec                     |                |                   |                  |                 |            |

|               |                                                                                         | A register selec                     |                |                   |                  |                 |            |

| bit 6         |                                                                                         | nnel 6 Ping-Pon                      | -              | s Flag bit        |                  |                 |            |

|               |                                                                                         | B register selec<br>A register selec |                |                   |                  |                 |            |

| bit 5         | PPST5: Chan                                                                             | nnel 5 Ping-Pon                      | ig Mode Statu  | s Flag bit        |                  |                 |            |

|               |                                                                                         | B register selec<br>A register selec |                |                   |                  |                 |            |

| bit 4         |                                                                                         | -                                    |                | s Elag bit        |                  |                 |            |

|               | <b>PPST4:</b> Channel 4 Ping-Pong Mode Status Flag bit<br>1 = DMA4STB register selected |                                      |                |                   |                  |                 |            |

|               |                                                                                         | A register selec                     |                |                   |                  |                 |            |

| bit 3         | PPST3: Channel 3 Ping-Pong Mode Status Flag bit                                         |                                      |                |                   |                  |                 |            |

|               |                                                                                         | B register selec<br>A register selec |                |                   |                  |                 |            |

| bit 2         | <b>PPST2:</b> Channel 2 Ping-Pong Mode Status Flag bit                                  |                                      |                |                   |                  |                 |            |

|               | 1 = DMA2STE                                                                             | B register selec                     | ted            | Ū                 |                  |                 |            |

| bit 1         |                                                                                         | nel 1 Ping-Pon                       |                | s Elag bit        |                  |                 |            |

|               |                                                                                         | B register selec                     | •              |                   |                  |                 |            |

|               | 0 = DMA1STA                                                                             | •                                    |                |                   |                  |                 |            |

|               |                                                                                         | Tregister Selec                      | leu            |                   |                  |                 |            |

| bit 0         | PPST0: Chan                                                                             | nel 0 Ping-Pon                       |                | s Flag bit        |                  |                 |            |

## REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0          | U-0        | U-0              | U-0            | U-0                  | U-0              | U-0                | R/W-0     |

|--------------|------------|------------------|----------------|----------------------|------------------|--------------------|-----------|

|              | —          | _                | _              | —                    | _                | _                  | PLLDIV<8> |

| bit 15       |            |                  |                |                      |                  |                    | bit 8     |

| R/W-0        | R/W-0      | R/W-1            | R/W-1          | R/W-0                | R/W-0            | R/W-0              | R/W-0     |

|              |            | 10111            |                | IV<7:0>              | 1011 0           | 10110              |           |

| bit 7        |            |                  |                |                      |                  |                    | bit 0     |

| Legend:      |            |                  |                |                      |                  |                    |           |

| R = Readat   | ole hit    | W = Writable     | hit            | U = Unimpler         | nented bit, read | 1 as '0'           |           |

| -n = Value a |            | '1' = Bit is set |                | '0' = Bit is cleared |                  | x = Bit is unknown |           |

|              |            |                  |                |                      |                  |                    |           |

| bit 15-9     | Unimpleme  | ented: Read as ' | 0'             |                      |                  |                    |           |

| bit 8-0      | PLLDIV<8:0 | >: PLL Feedbad   | k Divisor bits | (also denoted        | as 'M', PLL mu   | ıltiplier)         |           |

|              | 000000000  |                  |                |                      |                  |                    |           |

|              | 00000001   |                  |                |                      |                  |                    |           |

|              | 00000010   | = 4              |                |                      |                  |                    |           |

|              | •          |                  |                |                      |                  |                    |           |

|              | •          |                  |                |                      |                  |                    |           |

|              | •          |                  |                |                      |                  |                    |           |

|              | 000110000  | = 50 (default)   |                |                      |                  |                    |           |

|              | •          |                  |                |                      |                  |                    |           |

|              | •          |                  |                |                      |                  |                    |           |

|              | •          | 540              |                |                      |                  |                    |           |

|              | 111111111  | = 513            |                |                      |                  |                    |           |

© 2009 Microchip Technology Inc.

NOTES:

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| R/W-0                 | U-0                                                                                                                                                                                | R/W-0                             | R/W-0                                                                                                                     | R/W-0                           | U-0               | R/W-0                  | R/W-0           |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|------------------------|-----------------|--|--|

| UARTEN <sup>(1)</sup> | <sup>1)</sup> — USIDL IREN <sup>(2)</sup> RTSMD — UEN<1                                                                                                                            |                                   |                                                                                                                           |                                 |                   |                        | <1:0>           |  |  |

| bit 15                |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 |                   |                        | bit 8           |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 |                   |                        |                 |  |  |

| R/W-0 HC              | R/W-0                                                                                                                                                                              | R/W-0 HC                          | R/W-0                                                                                                                     | R/W-0                           | R/W-0             | R/W-0                  | R/W-0           |  |  |

| WAKE                  | LPBACK                                                                                                                                                                             | ABAUD                             | URXINV                                                                                                                    | BRGH                            | PDSE              | _<1:0>                 | STSEL           |  |  |

| bit 7                 |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 |                   |                        | bit C           |  |  |

| Legend:               |                                                                                                                                                                                    | HC = Hardwa                       | ro cloared                                                                                                                |                                 |                   |                        |                 |  |  |

| R = Readable          | hit                                                                                                                                                                                | W = Writable                      |                                                                                                                           | LI – Unimplo                    | mented bit, read  |                        |                 |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           | $0^{\circ} = \text{Bit is cle}$ |                   |                        |                 |  |  |

| -n = Value at F       | 'UR                                                                                                                                                                                | '1' = Bit is set                  |                                                                                                                           |                                 | ared              | x = Bit is unkr        | IOWN            |  |  |

| bit 15                | UARTEN: UA                                                                                                                                                                         | RTx Enable bi                     | <sub>t</sub> (1)                                                                                                          |                                 |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           | e controlled by                 | UARTx as defi     | ned by UEN<1:          | :0>             |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 | y port latches; U |                        |                 |  |  |

| bit 14                | Unimplemen                                                                                                                                                                         | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |  |  |

| bit 13                | USIDL: Stop                                                                                                                                                                        | in Idle Mode bi                   | t                                                                                                                         |                                 |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    | ue module ope                     |                                                                                                                           |                                 | dle mode          |                        |                 |  |  |

| h:: 40                |                                                                                                                                                                                    | module opera                      |                                                                                                                           |                                 |                   |                        |                 |  |  |

| bit 12                |                                                                                                                                                                                    | Encoder and D coder and dec       |                                                                                                                           | e dit'-'                        |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    | coder and dec                     |                                                                                                                           |                                 |                   |                        |                 |  |  |

| bit 11                | RTSMD: Mod                                                                                                                                                                         | le Selection for                  | UxRTS Pin b                                                                                                               | it                              |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    | in in Simplex n<br>in in Flow Con |                                                                                                                           |                                 |                   |                        |                 |  |  |

| bit 10                | Unimplemen                                                                                                                                                                         | ted: Read as '                    | 0'                                                                                                                        |                                 |                   |                        |                 |  |  |

| bit 9-8               | <b>UEN&lt;1:0&gt;:</b> ∪                                                                                                                                                           | ARTx Enable I                     | oits                                                                                                                      |                                 |                   |                        |                 |  |  |

|                       | 11 = UxTX, U                                                                                                                                                                       | xRX and BCL                       | <pins are="" ena<="" td=""><td>bled and used</td><td>I; UxCTS pin co</td><td>ntrolled by port</td><td>latches</td></pins> | bled and used                   | I; UxCTS pin co   | ntrolled by port       | latches         |  |  |

|                       |                                                                                                                                                                                    | xRX, UxCTS a                      |                                                                                                                           |                                 |                   |                        |                 |  |  |

|                       | 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches<br>00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by |                                   |                                                                                                                           |                                 |                   |                        |                 |  |  |

|                       | port latcl                                                                                                                                                                         |                                   |                                                                                                                           |                                 |                   |                        | lolled by       |  |  |

| bit 7                 | WAKE: Wake                                                                                                                                                                         | up on Start bi                    | t Detect Durin                                                                                                            | g Sleep Mode                    | Enable bit        |                        |                 |  |  |

|                       | 1 = UARTx w                                                                                                                                                                        | /ill continue to                  | sample the Ux                                                                                                             | RX pin; interro                 | upt generated o   | n falling edge; l      | oit cleared     |  |  |

|                       | in hardware on following rising edge                                                                                                                                               |                                   |                                                                                                                           |                                 |                   |                        |                 |  |  |

|                       | 0 = No wake                                                                                                                                                                        | •                                 |                                                                                                                           |                                 |                   |                        |                 |  |  |

| bit 6                 |                                                                                                                                                                                    | RTx Loopback                      |                                                                                                                           | bit                             |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    | oopback mode<br>k mode is disal   |                                                                                                                           |                                 |                   |                        |                 |  |  |

| bit 5                 | -                                                                                                                                                                                  | -Baud Enable                      |                                                                                                                           |                                 |                   |                        |                 |  |  |

|                       | 1 = Enable b                                                                                                                                                                       | aud rate meas                     | urement on th                                                                                                             |                                 | er – requires re  | ception of a Sy        | nc field (0x55) |  |  |

|                       |                                                                                                                                                                                    | ny data; cleared<br>e measuremen  |                                                                                                                           | •                               | on                |                        |                 |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 | amily Referenc    | e <i>Manual"</i> for i | nformation or   |  |  |

| en                    | abling the UAR                                                                                                                                                                     | T module for re                   | eceive or trans                                                                                                           | smit operation.                 |                   |                        |                 |  |  |

|                       |                                                                                                                                                                                    |                                   |                                                                                                                           |                                 |                   |                        |                 |  |  |

#### 2: This feature is only available for the 16x BRG mode (BRGH = 0).

**UxSTA: UARTx STATUS AND CONTROL REGISTER**

REGISTER 18-2:

#### R/W-0 R/W-0 R/W-0 U-0 **R/W-0 HC** R/W-0 R-0 R-1 UTXEN<sup>(1)</sup> UTXBF UTXISEL1 UTXINV UTXISEL0 UTXBRK TRMT \_\_\_\_ bit 15 bit 8 R/W-0 R/W-0 R/W-0 R-1 R-0 R-0 R/C-0 R-0 RIDLE PERR FERR URXDA URXISEL<1:0> ADDEN OERR bit 7 bit 0 Legend: HC = Hardware cleared C = Clear only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15,13 UTXISEL<1:0>: Transmission Interrupt Mode Selection bits 11 = Reserved; do not use 10 = Interrupt when a character is transferred to the Transmit Shift Register, and as a result, the transmit buffer becomes empty 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer) UTXINV: Transmit Polarity Inversion bit bit 14 If IREN = 0: 1 = UxTX Idle state is '0' 0 = UxTX Idle state is '1' If IREN = 1: 1 = IrDA<sup>®</sup> encoded UxTX Idle state is '1' 0 = IrDA<sup>®</sup> encoded UxTX Idle state is '0' bit 12 Unimplemented: Read as '0' bit 11 UTXBRK: Transmit Break bit 1 = Send Sync Break on next transmission – Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion 0 = Sync Break transmission disabled or completed bit 10 UTXEN: Transmit Enable bit<sup>(1)</sup> 1 = Transmit enabled, UxTX pin controlled by UARTx 0 = Transmit disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled by port. bit 9 UTXBF: Transmit Buffer Full Status bit (read-only) 1 = Transmit buffer is full 0 = Transmit buffer is not full, at least one more character can be written bit 8 TRMT: Transmit Shift Register Empty bit (read-only) 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit Shift Register is not empty, a transmission is in progress or queued bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bits 11 = Interrupt is set on UxRSR transfer making the receive buffer full (i.e., has 4 data characters) 10 = Interrupt is set on UxRSR transfer making the receive buffer 3/4 full (i.e., has 3 data characters) 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer. Receive buffer has one or more characters.

Note 1: Refer to Section 17. "UART" (DS70232) in the "PIC24H Family Reference Manual" for information on enabling the UART module for transmit operation.

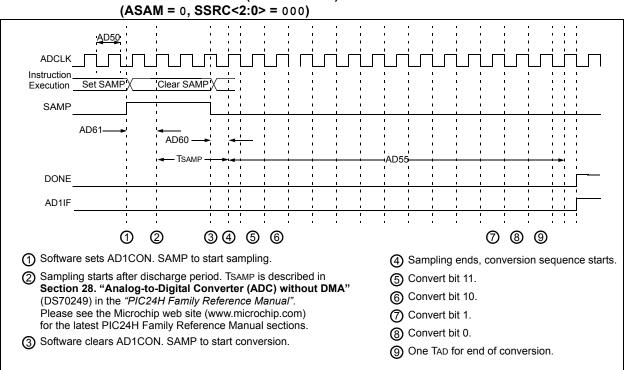

## 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC24H Family Reference Manual", Section 16. "Analog-to-Digital Converter (ADC)" (DS70225), which is available from the Microchip website (www.microchip.com).

The PIC24HJXXXGPX06/X08/X10 devices have up to 32 Analog-to-Digital input channels. These devices also have up to 2 Analog-to-Digital converter modules (ADCx, where 'x' = 1 or 2), each with its own set of Special Function Registers.

The AD12B bit (ADxCON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- · Up to 32 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Two result alignment options (signed/unsigned)

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only 1 sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the Analog-to-Digital Converter can have up to 32 analog input pins, designated AN0 through AN31. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the device data sheet for further details.

A block diagram of the Analog-to-Digital Converter is shown in Figure 20-1.

## 20.2 Analog-to-Digital Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (ADxCON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (ADxCON3<7:0>)

- d) Determine how many S/H channels will be used (ADxCON2<9:8> and ADxPCFGH<15:0> or ADxPCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (ADxCON1<7:5> and ADxCON3<12:8>)

- f) Select how conversion results are presented in the buffer (ADxCON1<9:8>)

- g) Turn on the ADC module (ADxCON1<15>)

- Configure ADC interrupt (if required):

- a) Clear the ADxIF bit

2.

b) Select ADC interrupt priority

## 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. Both ADC1 and ADC2 can trigger a DMA data transfer. If ADC1 or ADC2 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF or AD2IF bit gets set as a result of an ADC1 or ADC2 sample conversion sequence.

The SMPI<3:0> bits (ADxCON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (ADxCON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

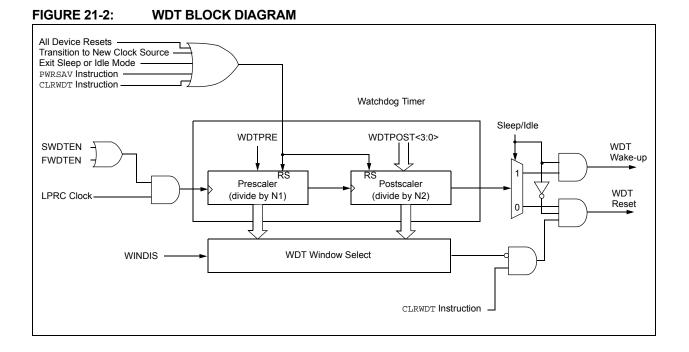

## 21.4 Watchdog Timer (WDT)

For PIC24HJXXXGPX06/X08/X10 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

#### © 2009 Microchip Technology Inc.

## 21.5 JTAG Interface

PIC24HJXXXGPX06/X08/X10 devices implement a JTAG interface, which supports boundary scan device testing, as well as in-circuit programming. Detailed information on the interface will be provided in future revisions of the document.

| Note: | For further information, refer to the |

|-------|---------------------------------------|

|       | PIC24H Family Reference Manual",      |

|       | Section 24. "Programming and          |

|       | Diagnostics" (DS70246), which is      |

|       | available from the Microchip website  |

|       | (www.microchip.com).                  |

## 21.6 Code Protection and CodeGuard™ Security

The PIC24H product families offer advanced implementation of CodeGuard<sup>™</sup> Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. This feature helps protect individual Intellectual Property in collaborative system designs.

When coupled with software encryption libraries, CodeGuard Security can be used to securely update Flash even when multiple IP are resident on the single chip. The code protection features vary depending on the actual PIC24H implemented. The following sections provide an overview these features.

The code protection features are controlled by the Configuration registers: FBS, FSS and FGS.

| Note: | For further information, refer to the  |

|-------|----------------------------------------|

|       | "PIC24H Family Reference Manual", Sec- |

|       | tion 23. "CodeGuard™ Security"         |

|       | (DS70239), which is available from the |

|       | Microchip website (www.microchip.com). |

## 21.7 In-Circuit Serial Programming Programming Capability

PIC24HJXXXGPX06/X08/X10 family digital signal controllers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming sequence. This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware, to be programmed. Please refer to the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) document for details about ICSP programming capability.

Any one out of three pairs of programming clock/data pins may be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 21.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any one out of three pairs of debugging clock/data pins may be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP programming capability connections to MCLR, VDD, Vss and the PGEDx/PGECx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

## 22.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

The PIC24H instruction set is identical to that of the PIC24F, and is a subset of the dsPIC30F/33F instruction set.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The PIC24H instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- · A program memory address

- The mode of the table read and table write instructions

| Field | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| Wnd   | One of 16 destination working registers ∈ {W0W15}                               |

| Wns   | One of 16 source working registers $\in$ {W0W15}                                |

| WREG  | W0 (working register used in file register instructions)                        |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                    |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] } |

### TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| IABL               | E 22-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                 |                                         |               |                |                          |  |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |  |

| 47                 | RCALL                | RCALL                                | Expr            | Relative Call                           | 1             | 2              | None                     |  |  |  |  |  |

|                    |                      | RCALL                                | Wn              | Computed Call                           | 1             | 2              | None                     |  |  |  |  |  |

| 48                 | REPEAT               | REPEAT                               | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | REPEAT                               | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |  |  |  |  |  |

| 49                 | RESET                | RESET                                |                 | Software device Reset                   | 1             | 1              | None                     |  |  |  |  |  |

| 50                 | RETFIE               | RETFIE                               |                 | Return from interrupt                   | 1             | 3 (2)          | None                     |  |  |  |  |  |

| 51                 | RETLW                | RETLW                                | #lit10,Wn       | Return with literal in Wn               | 1             | 3 (2)          | None                     |  |  |  |  |  |

| 52                 | RETURN               | RETURN                               |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |  |  |  |  |  |

| 53                 | RLC                  | RLC                                  | f               | f = Rotate Left through Carry f         | 1             | 1              | C,N,Z                    |  |  |  |  |  |

|                    |                      | RLC                                  | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C,N,Z                    |  |  |  |  |  |

|                    |                      | RLC                                  | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C,N,Z                    |  |  |  |  |  |

| 54                 | RLNC                 | RLNC                                 | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | RLNC                                 | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | RLNC                                 | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N,Z                      |  |  |  |  |  |

| 55                 | RRC                  | RRC                                  | f               | f = Rotate Right through Carry f        | 1             | 1              | C,N,Z                    |  |  |  |  |  |

|                    |                      | RRC                                  | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C,N,Z                    |  |  |  |  |  |

|                    |                      | RRC                                  | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C,N,Z                    |  |  |  |  |  |

| 56                 | RRNC                 | RRNC                                 | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | RRNC                                 | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | RRNC                                 | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N,Z                      |  |  |  |  |  |

| 57                 | SE                   | SE                                   | Ws,Wnd          | Wnd = sign-extended Ws                  | 1             | 1              | C,N,Z                    |  |  |  |  |  |

| 58                 | SETM                 | SETM                                 | f               | f = 0xFFFF                              | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | SETM                                 | WREG            | WREG = 0xFFFF                           | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | SETM                                 | Ws              | Ws = 0xFFFF                             | 1             | 1              | None                     |  |  |  |  |  |

| 59                 | SL                   | SL                                   | f               | f = Left Shift f                        | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |

|                    |                      | SL                                   | f,WREG          | WREG = Left Shift f                     | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |

|                    |                      | SL                                   | Ws,Wd           | Wd = Left Shift Ws                      | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |

|                    |                      | SL                                   | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N,Z                      |  |  |  |  |  |

|                    |                      | SL                                   | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N,Z                      |  |  |  |  |  |

| 60                 | SUB                  | SUB                                  | f               | f = f – WREG                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUB                                  | f,WREG          | WREG = f – WREG                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUB                                  | #lit10,Wn       | Wn = Wn - lit10                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUB                                  | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUB                                  | Wb,#lit5,Wd     | Wd = Wb – lit5                          | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 61                 | SUBB                 | SUBB                                 | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBB                                 | f,WREG          | WREG = f – WREG – $(\overline{C})$      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBB                                 | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBB                                 | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      |                                      |                 | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              |                          |  |  |  |  |  |

| 62                 | QUIDD                | SUBB                                 | Wb,#lit5,Wd     | f = WREG - f                            | 1             | 1              |                          |  |  |  |  |  |

| 02                 | SUBR                 | SUBR                                 | f MDEG          | WREG = WREG – f                         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBR                                 | f,WREG          | WKEG - WKEG - 1<br>Wd = Ws - Wb         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBR                                 | Wb,Ws,Wd        |                                         | 1             |                | C,DC,N,OV,Z              |  |  |  |  |  |

| 62                 | 0111111              | SUBR                                 | Wb,#lit5,Wd     | Wd = lit5 - Wb                          |               | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 63                 | SUBBR                | SUBBR                                | f               | f = WREG - f - (C)                      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBBR                                | f,WREG          | WREG = WREG - $f - (\overline{C})$      | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBBR                                | Wb,Ws,Wd        | $Wd = Ws - Wb - (\overline{C})$         | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

|                    |                      | SUBBR                                | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |

| 64                 | SWAP                 | SWAP.b                               | Wn              | Wn = nibble swap Wn                     | 1             | 1              | None                     |  |  |  |  |  |

|                    |                      | SWAP                                 | Wn              | Wn = byte swap Wn                       | 1             | 1              | None                     |  |  |  |  |  |

| 65                 | TBLRDH               | TBLRDH                               | Ws,Wd           | Read Prog<23:16> to Wd<7:0>             | 1             | 2              | None                     |  |  |  |  |  |

## TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

## 24.1 DC Characteristics

| Characteristic | VDD Range  | Temp Range     | Max MIPS                |

|----------------|------------|----------------|-------------------------|

| onaracteristic | (in Volts) | (in °C)        | PIC24HJXXXGPX06/X08/X10 |

|                | 3.0-3.6V   | -40°C to +85°C | 40                      |

### TABLE 24-1: OPERATING MIPS VS. VOLTAGE

### TABLE 24-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol              | Min | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------------|------|------|

| Industrial Temperature Devices                                                                                                                                                         |                     |     |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ                  | -40 | _           | +125 | °C   |