Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp210t-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-28: PORTE REGISTER MAP<sup>(1)</sup>

|           |      |        |        |        |        |        |        |       | -     |        | -      | -      | -      |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | -      | —      | _      | _      | -      | —     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | XXXX          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-29: PORTF REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|---------------------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF               | 02DE | _      | _      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF               | 02E0 | -      | _      | RF13    | RF12    | -      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF                | 02E2 | -      | _      | LATF13  | LATF12  | -      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF <sup>(2)</sup> | 06DE | _      | _      | ODCF13  | ODCF12  | _      | —      | —     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-30: PORTG REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG               | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG               | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | XXXX          |

| LATG                | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | XXXX          |

| ODCG <sup>(2)</sup> | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | —     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Compare 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1:INTERRUPT VECTORS

|  | REGISTER 7-6: | <b>IFS1: INTERRUPT FLAG STATUS REGISTER 1</b> |

|--|---------------|-----------------------------------------------|

|--|---------------|-----------------------------------------------|

| U2TXIF<br>bit 15<br>R/W-0<br>IC8IF<br>bit 7 | U2RXIF                                                                             | INT2IF                             | T5IF             | T4IF             | OC4IF            | OC3IF           |         |  |  |  |  |

|---------------------------------------------|------------------------------------------------------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| R/W-0<br>IC8IF                              |                                                                                    | •                                  |                  | 141              | 00416            | OCSIF           | DMA21IF |  |  |  |  |

| IC8IF                                       |                                                                                    |                                    | ·                |                  |                  |                 | bit 8   |  |  |  |  |

|                                             | R/W-0                                                                              | R/W-0                              | R/W-0            | R/W-0            | U-0              | R/W-0           | R/W-0   |  |  |  |  |

| bit 7                                       | IC7IF                                                                              | AD2IF                              | INT1IF           | CNIF             | _                | MI2C1IF         | SI2C1IF |  |  |  |  |

|                                             |                                                                                    |                                    | 1                | 1                |                  |                 | bit (   |  |  |  |  |

| Legend:                                     |                                                                                    |                                    |                  |                  |                  |                 |         |  |  |  |  |

| R = Readable                                | bit                                                                                | W = Writable                       | bit              | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |

| -n = Value at F                             | POR                                                                                | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unki | nown    |  |  |  |  |

| bit 15                                      | U2TXIF: UAF                                                                        | RT2 Transmitte                     | r Interrupt Flag | g Status bit     |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc<br>request has no   |                  |                  |                  |                 |         |  |  |  |  |

| bit 14                                      | U2RXIF: UAF                                                                        | RT2 Receiver li                    | nterrupt Flag S  | Status bit       |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc                     |                  |                  |                  |                 |         |  |  |  |  |

| L:1 1 0                                     | •                                                                                  | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 13                                      |                                                                                    | rnal Interrupt 2<br>request has oc | -                | t                |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 12                                      | T5IF: Timer5                                                                       | Interrupt Flag                     | Status bit       |                  |                  |                 |         |  |  |  |  |

|                                             | 1 = Interrupt request has occurred                                                 |                                    |                  |                  |                  |                 |         |  |  |  |  |

|                                             | •                                                                                  | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 11                                      |                                                                                    | Interrupt Flag<br>request has oc   |                  |                  |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 10                                      | OC4IF: Outp                                                                        | ut Compare Ch                      | annel 4 Interru  | upt Flag Status  | s bit            |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc<br>request has no   |                  |                  |                  |                 |         |  |  |  |  |

| bit 9                                       |                                                                                    | ut Compare Ch                      |                  | upt Flag Status  | s bit            |                 |         |  |  |  |  |

|                                             | 1 = Interrupt                                                                      | request has oc<br>request has no   | curred           |                  |                  |                 |         |  |  |  |  |

| bit 8                                       | DMA21IF: DI                                                                        | MA Channel 2 I                     | Data Transfer    | Complete Inte    | rrupt Flag Statu | ıs bit          |         |  |  |  |  |

|                                             |                                                                                    | request has oc                     |                  |                  |                  |                 |         |  |  |  |  |

|                                             | •                                                                                  | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 7                                       |                                                                                    | Capture Chann<br>request has oc    | •                | -lag Status bit  |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 6                                       | IC7IF: Input (                                                                     | Capture Chann                      | el 7 Interrupt F | lag Status bit   |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc<br>request has no   |                  |                  |                  |                 |         |  |  |  |  |

| bit 5                                       | AD2IF: ADC2                                                                        | 2 Conversion C                     | omplete Interr   | upt Flag Statu   | s bit            |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc                     |                  |                  |                  |                 |         |  |  |  |  |

|                                             | -                                                                                  | request has no                     |                  |                  |                  |                 |         |  |  |  |  |

| bit 4                                       | INT1IF: External Interrupt 1 Flag Status bit<br>1 = Interrupt request has occurred |                                    |                  |                  |                  |                 |         |  |  |  |  |

|                                             |                                                                                    | request has oc<br>request has no   |                  |                  |                  |                 |         |  |  |  |  |

### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0           | R/W-0                                                                                            | R/W-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0            |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------|-----------------------------------|----------------|------------------|------------------|-----------------|------------------|--|--|--|

| U2TXIE          | U2RXIE                                                                                           | INT2IE                            | T5IE           | T4IE             | OC4IE            | OC3IE           | DMA2IE           |  |  |  |

| bit 15          |                                                                                                  |                                   |                |                  |                  |                 | bit 8            |  |  |  |

|                 | DAMA                                                                                             | <b>DMU</b> O                      | <b>D</b> 444 0 | <b>DMUO</b>      |                  | DAVA            | DAMO             |  |  |  |

| R/W-0           | R/W-0                                                                                            | R/W-0                             | R/W-0          | R/W-0            | U-0              | R/W-0           | R/W-0            |  |  |  |

| IC8IE<br>bit 7  | IC7IE                                                                                            | AD2IE                             | INT1IE         | CNIE             |                  | MI2C1IE         | SI2C1IE<br>bit 0 |  |  |  |

|                 |                                                                                                  |                                   |                |                  |                  |                 | bit 0            |  |  |  |

| Legend:         |                                                                                                  |                                   |                |                  |                  |                 |                  |  |  |  |

| R = Readable    | bit                                                                                              | W = Writable                      | bit            | U = Unimpler     | mented bit, read | d as '0'        |                  |  |  |  |

| -n = Value at F | POR                                                                                              | '1' = Bit is set                  |                | '0' = Bit is cle | ared             | x = Bit is unkr | iown             |  |  |  |

|                 |                                                                                                  |                                   |                |                  |                  |                 |                  |  |  |  |

| bit 15          |                                                                                                  | RT2 Transmitte                    | -              | able bit         |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request enable<br>request not ena |                |                  |                  |                 |                  |  |  |  |

| bit 14          |                                                                                                  | RT2 Receiver li                   |                | le hit           |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request enable                    | •              |                  |                  |                 |                  |  |  |  |

|                 | 0 = Interrupt r                                                                                  | request not ena                   | abled          |                  |                  |                 |                  |  |  |  |

| bit 13          |                                                                                                  | rnal Interrupt 2                  |                |                  |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request enable                    |                |                  |                  |                 |                  |  |  |  |

| bit 12          | <ul> <li>0 = Interrupt request not enabled</li> <li>T5IE: Timer5 Interrupt Enable bit</li> </ul> |                                   |                |                  |                  |                 |                  |  |  |  |

|                 | 1 = Interrupt request enabled                                                                    |                                   |                |                  |                  |                 |                  |  |  |  |

|                 | 0 = Interrupt request not enabled                                                                |                                   |                |                  |                  |                 |                  |  |  |  |

| bit 11          |                                                                                                  | Interrupt Enab                    |                |                  |                  |                 |                  |  |  |  |

|                 | •                                                                                                | request enable<br>request not ena |                |                  |                  |                 |                  |  |  |  |

| bit 10          | -                                                                                                | ut Compare Ch                     |                | upt Enable bit   |                  |                 |                  |  |  |  |

|                 | •                                                                                                | request enable                    |                |                  |                  |                 |                  |  |  |  |

|                 | 0 = Interrupt r                                                                                  | request not ena                   | abled          |                  |                  |                 |                  |  |  |  |

| bit 9           |                                                                                                  | ut Compare Ch                     |                | upt Enable bit   |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request enable<br>request not ena |                |                  |                  |                 |                  |  |  |  |

| bit 8           |                                                                                                  | A Channel 2 D                     |                | Complete Interr  | unt Enable hit   |                 |                  |  |  |  |

| bit 0           |                                                                                                  | request enable                    |                |                  |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request not ena                   |                |                  |                  |                 |                  |  |  |  |

| bit 7           | IC8IE: Input C                                                                                   | Capture Chann                     | el 8 Interrupt | Enable bit       |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request enable<br>request not ena |                |                  |                  |                 |                  |  |  |  |

| bit 6           |                                                                                                  | Capture Chann                     |                | Enable bit       |                  |                 |                  |  |  |  |

|                 | -                                                                                                | request enable                    | -              |                  |                  |                 |                  |  |  |  |

|                 |                                                                                                  | request not ena                   |                |                  |                  |                 |                  |  |  |  |

| bit 5           | AD2IE: ADC2                                                                                      | 2 Conversion C                    | omplete Inter  | rupt Enable bit  |                  |                 |                  |  |  |  |

|                 | •                                                                                                | request enable                    |                |                  |                  |                 |                  |  |  |  |

| hit 4           | -                                                                                                | request not ena                   |                |                  |                  |                 |                  |  |  |  |

| bit 4           | 1 = Interrupt r                                                                                  | rnal Interrupt 1                  |                |                  |                  |                 |                  |  |  |  |

|                 |                                                                                                  | naniaet anabia                    | n              |                  |                  |                 |                  |  |  |  |

### REGISTER 7-13: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0                 | U-0                                                                                                              | R/W-0                                                                                                     | U-0           | U-0              | U-0              | U-0             | R/W-0 |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|-------|--|--|--|

| _                   | —                                                                                                                | DMA5IE                                                                                                    | _             | _                | —                | _               | C2IE  |  |  |  |

| bit 15              |                                                                                                                  |                                                                                                           |               |                  |                  |                 | bit 8 |  |  |  |

|                     |                                                                                                                  |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| R/W-0               | R/W-0                                                                                                            | R/W-0                                                                                                     | R/W-0         | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| C2RXIE              | INT4IE                                                                                                           | INT3IE                                                                                                    | T9IE          | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |  |  |  |

| bit 7               |                                                                                                                  |                                                                                                           |               |                  |                  |                 | bit 0 |  |  |  |

| r                   |                                                                                                                  |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| Legend:             |                                                                                                                  |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| R = Readable        |                                                                                                                  | W = Writable                                                                                              |               | •                | nented bit, read |                 |       |  |  |  |

| -n = Value at F     | POR                                                                                                              | '1' = Bit is set                                                                                          |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |

|                     |                                                                                                                  | tad. Daad as f                                                                                            | o'            |                  |                  |                 |       |  |  |  |

| bit 15-14<br>bit 13 | -                                                                                                                | ted: Read as '                                                                                            |               | amplata Interr   | unt Enchla hit   |                 |       |  |  |  |

| DIL 13              |                                                                                                                  | <b>DMA5IE:</b> DMA Channel 5 Data Transfer Complete Interrupt Enable bit<br>1 = Interrupt request enabled |               |                  |                  |                 |       |  |  |  |

|                     | 0 = Interrupt request not enabled                                                                                |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 12-9            | Unimplemented: Read as '0'                                                                                       |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 8               | C2IE: ECAN2 Event Interrupt Enable bit                                                                           |                                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     | 1 = Interrupt request enabled                                                                                    |                                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     | <ul> <li>Interrupt request not enabled</li> <li>C2RXIE: ECAN2 Receive Data Ready Interrupt Enable bit</li> </ul> |                                                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 7               |                                                                                                                  |                                                                                                           | -             | errupt Enable I  | Dit              |                 |       |  |  |  |

|                     | •                                                                                                                | equest enable<br>equest not ena                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 6               |                                                                                                                  | nal Interrupt 4                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     | 1 = Interrupt r                                                                                                  | equest enable                                                                                             | d             |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | request not ena                                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 5               |                                                                                                                  | nal Interrupt 3                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | equest enable<br>equest not ena                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 4               | -                                                                                                                | Interrupt Enab                                                                                            |               |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | equest enable                                                                                             |               |                  |                  |                 |       |  |  |  |

|                     | •                                                                                                                | equest not ena                                                                                            |               |                  |                  |                 |       |  |  |  |

| bit 3               |                                                                                                                  | Interrupt Enab                                                                                            |               |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | equest enable                                                                                             |               |                  |                  |                 |       |  |  |  |

| bit 2               | 0 = Interrupt request not enabled                                                                                |                                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     | MI2C2IE: I2C2 Master Events Interrupt Enable bit<br>1 = Interrupt request enabled                                |                                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | request not ena                                                                                           |               |                  |                  |                 |       |  |  |  |

| bit 1               | SI2C2IE: 12C                                                                                                     | 2 Slave Events                                                                                            | Interrupt Ena | ble bit          |                  |                 |       |  |  |  |

|                     |                                                                                                                  | equest enable                                                                                             |               |                  |                  |                 |       |  |  |  |

|                     | -                                                                                                                | equest not ena                                                                                            |               |                  |                  |                 |       |  |  |  |

| bit 0               |                                                                                                                  | Interrupt Enab                                                                                            |               |                  |                  |                 |       |  |  |  |

|                     | <ol> <li>I = Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>                         |                                                                                                           |               |                  |                  |                 |       |  |  |  |

|                     |                                                                                                                  | 540501101010                                                                                              |               |                  |                  |                 |       |  |  |  |

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0             | R-0                        | R-0                                  | R-0            | U-0              | R/W-y           | R/W-y                    | R/W-y      |  |  |

|-----------------|----------------------------|--------------------------------------|----------------|------------------|-----------------|--------------------------|------------|--|--|

| —               |                            | COSC<2:0>                            |                | —                |                 | NOSC<2:0> <sup>(2)</sup> |            |  |  |

| bit 15          |                            |                                      |                |                  |                 |                          | bit 8      |  |  |

| R/W-0           | U-0                        | R-0                                  | U-0            | R/C-0            | U-0             | R/W-0                    | R/W-0      |  |  |

| CLKLOCK         | _                          | LOCK                                 | _              | CF               | _               | LPOSCEN                  | OSWEN      |  |  |

| bit 7           |                            |                                      |                | 0.               |                 |                          | bit 0      |  |  |

|                 |                            |                                      |                |                  |                 |                          |            |  |  |

| Legend:         | ••                         | -                                    | -              | ation bits on P  |                 | C = Clear                | r only bit |  |  |

| R = Readable I  |                            | W = Writable                         | bit            | -                | nented bit, rea |                          |            |  |  |

| -n = Value at P | OR                         | '1' = Bit is set                     |                | '0' = Bit is cle | ared            | x = Bit is unkn          | own        |  |  |

| bit 15          | Unimplemen                 | ted: Read as '                       | ) <b>'</b>     |                  |                 |                          |            |  |  |

| bit 14-12       | -                          | Current Oscilla                      |                | bits (read-only  | )               |                          |            |  |  |

| 51(11)2         |                            | C oscillator (FF                     |                |                  | /               |                          |            |  |  |

|                 | 001 <b>= Fast R</b>        | C oscillator (FF                     | RC) with PLL   |                  |                 |                          |            |  |  |

|                 |                            | y oscillator (XT                     |                |                  |                 |                          |            |  |  |

|                 |                            | y oscillator (XT                     |                | PLL              |                 |                          |            |  |  |

|                 |                            | dary oscillator (<br>ower RC oscilla |                |                  |                 |                          |            |  |  |

|                 |                            | C oscillator (FF                     |                | e-by-16          |                 |                          |            |  |  |

|                 |                            | C oscillator (FF                     |                |                  |                 |                          |            |  |  |

| bit 11          | Unimplemented: Read as '0' |                                      |                |                  |                 |                          |            |  |  |

| bit 10-8        | NOSC<2:0>:                 | New Oscillator                       | Selection bits | <sub>3</sub> (2) |                 |                          |            |  |  |

|                 |                            | C oscillator (FF                     |                |                  |                 |                          |            |  |  |

|                 |                            | C oscillator (FF                     |                |                  |                 |                          |            |  |  |

|                 |                            | y oscillator (XT<br>y oscillator (XT |                | PU               |                 |                          |            |  |  |

|                 |                            | dary oscillator (                    |                |                  |                 |                          |            |  |  |

|                 | 101 = Low-P                | ower RC oscilla                      | tor (LPRC)     |                  |                 |                          |            |  |  |

|                 |                            | C oscillator (FF                     |                |                  |                 |                          |            |  |  |

| hit 7           |                            | C oscillator (FF<br>Clock Lock Ena   | -              | e-by-n           |                 |                          |            |  |  |

| bit 7           |                            | M0 = 1), then c                      |                | configurations   | are locked      |                          |            |  |  |

|                 |                            | MO = 1), then C $MO = 0$ ), then c   |                |                  |                 | ied                      |            |  |  |

|                 |                            | d PLL selection                      |                |                  |                 |                          |            |  |  |

| bit 6           | Unimplemen                 | ted: Read as '                       | כ'             |                  |                 |                          |            |  |  |

| bit 5           | LOCK: PLL L                | ock Status bit (                     | read-only)     |                  |                 |                          |            |  |  |

|                 |                            | that PLL is in I                     |                |                  |                 |                          |            |  |  |

|                 |                            | that PLL is out                      |                | up timer is in p | progress or PL  | L is disabled            |            |  |  |

| bit 4           | -                          | ted: Read as '                       |                |                  |                 |                          |            |  |  |

| bit 3           |                            | il Detect bit (rea                   |                | plication)       |                 |                          |            |  |  |

|                 |                            | as detected clo<br>as not detected   |                |                  |                 |                          |            |  |  |

|                 |                            |                                      |                |                  |                 |                          |            |  |  |

| bit 2           | Unimplemen                 | ted: Read as '                       | )              |                  |                 |                          |            |  |  |

**Note 1:** Writes to this register require an unlock sequence. Refer to **Section 7. "Oscillator**" (DS70227) in the *"PIC24H Family Reference Manual"* (available from the Microchip website) for details.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

# 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, PIC24HJXXXGPX06/X08/X10 devices have a safe-guard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 21.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70227) in the "PIC24H Family Reference Manual" for details.

# 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

If an oscillator failure occurs, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

| REGISTER '    | 10-1: PMD                                                                                 | 1: PERIPHER                          | RAL MODULE  | E DISABLE CO      | ONTROL RE     | GISTER 1        |       |  |  |

|---------------|-------------------------------------------------------------------------------------------|--------------------------------------|-------------|-------------------|---------------|-----------------|-------|--|--|

| R/W-0         | R/W-0                                                                                     | R/W-0                                | R/W-0       | R/W-0             | U-0           | U-0             | U-0   |  |  |

| T5MD          | T4MD                                                                                      | T3MD                                 | T2MD        | T1MD              |               | _               |       |  |  |

| bit 15        |                                                                                           |                                      |             |                   |               | ·               | bit 8 |  |  |

| R/W-0         | R/W-0                                                                                     | R/W-0                                | R/W-0       | R/W-0             | R/W-0         | R/W-0           | R/W-0 |  |  |

| I2C1MD        | U2MD                                                                                      | U1MD                                 | SPI2MD      | SPI1MD            | C2MD          | C1MD            | AD1MD |  |  |

| bit 7         | OZIND                                                                                     | OTWD                                 | OF 121WID   | SI TIMD           | OZIND         | OIND            | bit ( |  |  |

|               |                                                                                           |                                      |             |                   |               |                 |       |  |  |

| Legend:       | - I-:4                                                                                    |                                      | <b>L</b> :4 |                   | anted hit was | d aa (0)        |       |  |  |

| R = Readable  |                                                                                           | W = Writable                         |             | U = Unimplem      |               |                 |       |  |  |

| -n = Value at | PUR                                                                                       | '1' = Bit is set                     | [           | '0' = Bit is clea | ared          | x = Bit is unki | nown  |  |  |

| bit 15        | T5MD: Time                                                                                | r5 Module Disa                       | ble bit     |                   |               |                 |       |  |  |

|               |                                                                                           | nodule is disabl                     |             |                   |               |                 |       |  |  |

| bit 14        | <ul> <li>0 = Timer5 module is enabled</li> <li>T4MD: Timer4 Module Disable bit</li> </ul> |                                      |             |                   |               |                 |       |  |  |

| DIL 14        | 14MD: Timer4 Module Disable bit<br>1 = Timer4 module is disabled                          |                                      |             |                   |               |                 |       |  |  |

|               | 0 = Timer4 module is enabled                                                              |                                      |             |                   |               |                 |       |  |  |

| bit 13        | T3MD: Timer3 Module Disable bit                                                           |                                      |             |                   |               |                 |       |  |  |

|               | 1 = Timer3 module is disabled                                                             |                                      |             |                   |               |                 |       |  |  |

| 1:1.40        | <ul> <li>0 = Timer3 module is enabled</li> <li>T2MD: Timer2 Module Disable bit</li> </ul> |                                      |             |                   |               |                 |       |  |  |

| bit 12        | -                                                                                         |                                      |             |                   |               |                 |       |  |  |

|               | 1 = Timer2 module is disabled<br>0 = Timer2 module is enabled                             |                                      |             |                   |               |                 |       |  |  |

| bit 11        | T1MD: Time                                                                                | 1 Module Disa                        | ble bit     |                   |               |                 |       |  |  |

|               | -                                                                                         | nodule is disabl<br>nodule is enable |             |                   |               |                 |       |  |  |

| bit 10-8      |                                                                                           | nted: Read as '                      |             |                   |               |                 |       |  |  |

| bit 7         | -                                                                                         | 1 Module Disal                       |             |                   |               |                 |       |  |  |

|               |                                                                                           | dule is disabled                     |             |                   |               |                 |       |  |  |

|               | 0 = I <sup>2</sup> C1 mod                                                                 | dule is enabled                      |             |                   |               |                 |       |  |  |

| bit 6         |                                                                                           | T2 Module Disa                       |             |                   |               |                 |       |  |  |

|               |                                                                                           | nodule is disabl<br>nodule is enabl  |             |                   |               |                 |       |  |  |

| bit 5         | U1MD: UAR                                                                                 | T1 Module Disa                       | able bit    |                   |               |                 |       |  |  |

|               | -                                                                                         | nodule is disabl                     |             |                   |               |                 |       |  |  |

| hit 1         | 0 = UART1 module is enabled                                                               |                                      |             |                   |               |                 |       |  |  |

| bit 4         | SPI2MD: SPI2 Module Disable bit<br>1 = SPI2 module is disabled                            |                                      |             |                   |               |                 |       |  |  |

|               |                                                                                           | dule is enabled                      |             |                   |               |                 |       |  |  |

| bit 3         | SPI1MD: SP                                                                                | I1 Module Disa                       | ble bit     |                   |               |                 |       |  |  |

|               |                                                                                           | dule is disabled<br>dule is enabled  |             |                   |               |                 |       |  |  |

| bit 2         | C2MD: ECA                                                                                 | N2 Module Disa                       | able bit    |                   |               |                 |       |  |  |

|               | 1 = ECAN2 r                                                                               | nodule is disab                      | led         |                   |               |                 |       |  |  |

# REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 C1MD: ECAN1 Module Disable bit

- 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

#### 11.2 **Open-Drain Configuration**

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired digital only pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "Pin Diagrams" for the available pins and their functionality.

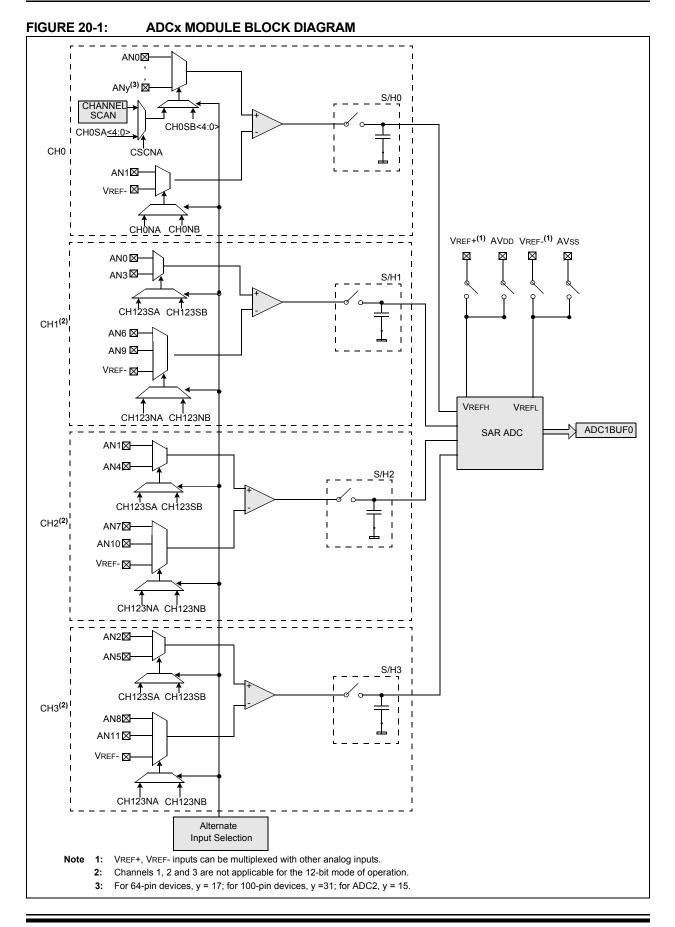

#### 11.3 **Configuring Analog Port Pins**

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the Analog-to-Digital port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

MOV W0, TRISBB NOP PORTB, #13 btss

11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJXXXGPX06/X08/X10 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

MOV 0xFF00, W0 ; Configure PORTB<15:8> as inputs ; and PORTB<7:0> as outputs ; Delay 1 cycle ; Next Instruction

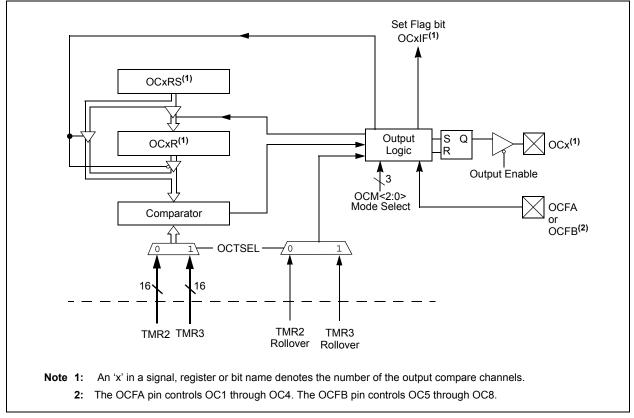

# 15.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC24H Family Reference Manual"*, Section 13. "Output Compare" (DS70247), which is available on the Microchip web site (www.microchip.com).

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

### FIGURE 15-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM