Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 53                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 18x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 64-TQFP                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp506-e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

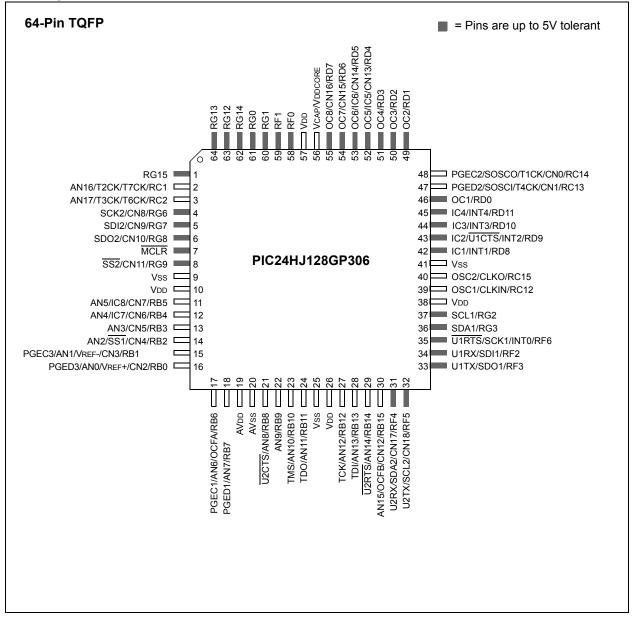

### **Pin Diagrams (Continued)**

#### SR: CPU STATUS REGISTER **REGISTER 3-1:** U-0 U-0 U-0 U-0 U-0 U-0 U-0 R/W-0 DC bit 15 bit 8 R/W-0<sup>(1)</sup> R/W-0<sup>(2)</sup> R/W-0<sup>(2)</sup> R-0 R/W-0 R/W-0 R/W-0 R/W-0 IPL<2:0>(2) RA Ν OV Ζ С bit 7 bit 0 Leaend: C = Clear only bit U = Unimplemented bit, read as '0' R = Readable bit S = Set only bit W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-9 Unimplemented: Read as '0' bit 8 DC: MCU ALU Half Carry/Borrow bit 1 = A carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred 0 = No carry-out from the 4th low-order bit (for byte sized data) or 8th low-order bit (for word sized data) of the result occurred IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup> bit 7-5 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled 110 = CPU Interrupt Priority Level is 6 (14) 101 = CPU Interrupt Priority Level is 5 (13) 100 = CPU Interrupt Priority Level is 4 (12) 011 = CPU Interrupt Priority Level is 3 (11) 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9) 000 = CPU Interrupt Priority Level is 0 (8) bit 4 **RA:** REPEAT Loop Active bit 1 = REPEAT loop in progress 0 = REPEAT loop not in progress bit 3 N: MCU ALU Negative bit 1 = Result was negative 0 = Result was non-negative (zero or positive) bit 2 OV: MCU ALU Overflow bit This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude which causes the sign bit to change state. 1 = Overflow occurred for signed arithmetic (in this arithmetic operation) 0 = No overflow occurred Z: MCU ALU Zero bit bit 1 1 = An operation which affects the Z bit has set it at some time in the past 0 = The most recent operation which affects the Z bit has cleared it (i.e., a non-zero result) bit 0 C: MCU ALU Carry/Borrow bit 1 = A carry-out from the Most Significant bit (MSb) of the result occurred 0 = No carry-out from the Most Significant bit of the result occurred Note 1: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

2: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

## 5.2 RTSP Operation

The PIC24HJXXXGPX06/X08/X10 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 24-12 displays typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 24-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 24-12).

### EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +85°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the Minimum Row Write Time is:

$$T_{RW} = \frac{11064 \text{ Cycles}}{7.37 \text{ MHz} \times (1 + 0.02) \times (1 - 0.00375)} = 1.48 \text{ms}$$

and, the Maximum Row Write Time is:

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 1.54 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

## 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |

| POR (RCON<0>)     | POR                                                  | —                            |

### TABLE 6-1: RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

#### TABLE 6-2: OSCILLATOR SELECTION vs. TYPE OF RESET (CLOCK SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

### REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS

| R-0               | R-0 | R-0              | R-0                                        | R-0                                | R-0               | R-0 | R-0   |

|-------------------|-----|------------------|--------------------------------------------|------------------------------------|-------------------|-----|-------|

|                   |     |                  | DSAI                                       | DR<15:8>                           |                   |     |       |

| bit 15            |     |                  |                                            |                                    |                   |     | bit 8 |

|                   |     |                  |                                            |                                    |                   |     |       |

| R-0               | R-0 | R-0              | R-0                                        | R-0                                | R-0               | R-0 | R-0   |

|                   |     |                  | DSA                                        | .DR<7:0>                           |                   |     |       |

| bit 7             |     |                  |                                            |                                    |                   |     | bit 0 |

|                   |     |                  |                                            |                                    |                   |     |       |

| Legend:           |     |                  |                                            |                                    |                   |     |       |

| R = Readable bit  |     | W = Writable bit | :                                          | U = Unimplemented bit, read as '0' |                   |     |       |

| -n = Value at POF | २   | '1' = Bit is set | t is set '0' = Bit is cleared x = Bit is u |                                    | x = Bit is unknow | /n  |       |

|                   |     |                  |                                            |                                    |                   |     |       |

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

## 9.2 Clock Switching Operation

Applications are free to switch between any of the four clock sources (Primary, LP, FRC and LPRC) under software control at any time. To limit the possible side effects that could result from this flexibility, PIC24HJXXXGPX06/X08/X10 devices have a safe-guard lock built into the switch process.

Note: Primary Oscillator mode has three different submodes (XT, HS and EC) which are determined by the POSCMD<1:0> Configuration bits. While an application can switch to and from Primary Oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 9.2.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the Configuration register must be programmed to '0'. (Refer to **Section 21.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and Fail-Safe Clock Monitor function are disabled. This is the default setting.

The NOSC control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSC bits (OSCCON<14:12>) reflect the clock source selected by the FNOSC Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled. It is held at '0' at all times.

### 9.2.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSC bits (OSCCON<14:12>) to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- Write the appropriate value to the NOSC control bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

The clock switching hardware compares the COSC status bits with the new value of the NOSC control bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and the CF (OSCCON<3>) status bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware waits until the Oscillator Start-up Timer (OST) expires. If the new source is using the PLL, the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSC bit values are transferred to the COSC status bits.

- 6. The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM are enabled) or LP (if LPOSCEN remains set).

- Note 1: The processor continues to execute code throughout the clock switching sequence. Timing sensitive code should not be executed during this time.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- 3: Refer to Section 7. "Oscillator" (DS70227) in the "PIC24H Family Reference Manual" for details.

## 9.3 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

If an oscillator failure occurs, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. Then the application program can either attempt to restart the oscillator or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

If the PLL multiplier is used to scale the system clock, the internal FRC is also multiplied by the same factor on clock failure. Essentially, the device switches to FRC with PLL on a clock failure.

NOTES:

NOTES:

### **REGISTER 19-6:** CIINTF: ECAN<sup>™</sup> MODULE INTERRUPT FLAG REGISTER

| U-0    | U-0 | R-0  | R-0  | R-0  | R-0   | R-0   | R-0   |

|--------|-----|------|------|------|-------|-------|-------|

| —      | —   | ТХВО | TXBP | RXBP | TXWAR | RXWAR | EWARN |

| bit 15 |     |      |      |      |       |       | bit 8 |

| R/C-0       | R/C-0 | R/C-0 | U-0 | R/C-0  | R/C-0  | R/C-0 | R/C-0 |

|-------------|-------|-------|-----|--------|--------|-------|-------|

| IVRIF       | WAKIF | ERRIF | —   | FIFOIF | RBOVIF | RBIF  | TBIF  |

| bit 7 bit 0 |       |       |     |        |        |       |       |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                  |

|-----------|-----------------------------------------------------------------------------|

| bit 13    | TXBO: Transmitter in Error State Bus Off bit                                |

| bit 12    | TXBP: Transmitter in Error State Bus Passive bit                            |

| bit 11    | RXBP: Receiver in Error State Bus Passive bit                               |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                               |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                  |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                   |

| bit 7     | IVRIF: Invalid Message Received Interrupt Flag bit                          |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                              |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CiINTF<13:8> register) |

| bit 4     | Unimplemented: Read as '0'                                                  |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                 |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                               |

| bit 1     | RBIF: RX Buffer Interrupt Flag bit                                          |

| bit 0     | TBIF: TX Buffer Interrupt Flag bit                                          |

|           |                                                                             |

### REGISTER 19-7: CIINTE: ECAN™ MODULE INTERRUPT ENABLE REGISTER

| U-0          | U-0            | U-0                                            | U-0            | U-0                                     | U-0    | U-0   | U-0   |  |  |

|--------------|----------------|------------------------------------------------|----------------|-----------------------------------------|--------|-------|-------|--|--|

| _            | —              | —                                              | _              | _                                       | —      | —     | _     |  |  |

| bit 15       |                |                                                |                |                                         |        |       | bit 8 |  |  |

|              |                |                                                |                |                                         |        |       |       |  |  |

| R/W-0        | R/W-0          | R/W-0                                          | U-0            | R/W-0                                   | R/W-0  | R/W-0 | R/W-0 |  |  |

| IVRIE        | WAKIE          | ERRIE                                          |                | FIFOIE                                  | RBOVIE | RBIE  | TBIE  |  |  |

| bit 7        |                |                                                |                |                                         |        |       | bit C |  |  |

|              |                |                                                |                |                                         |        |       |       |  |  |

| Legend:      |                |                                                |                |                                         |        |       |       |  |  |

| R = Readab   | le bit         | W = Writable                                   | bit            | U = Unimplemented bit, read as '0'      |        |       |       |  |  |

| -n = Value a | t POR          | '1' = Bit is set                               |                | '0' = Bit is cleared x = Bit is unknown |        |       | nown  |  |  |

|              |                |                                                |                |                                         |        |       |       |  |  |

| bit 15-8     | Unimplemen     | ted: Read as '                                 | 0'             |                                         |        |       |       |  |  |

| bit 7        | IVRIE: Invalio | I Message Rec                                  | eived Interrup | t Enable bit                            |        |       |       |  |  |

| bit 6        | WAKIE: Bus     | WAKIE: Bus Wake-up Activity Interrupt Flag bit |                |                                         |        |       |       |  |  |

| L:4 F        |                |                                                |                |                                         |        |       |       |  |  |

- bit 5 ERRIE: Error Interrupt Enable bit bit 4 Unimplemented: Read as '0'

- bit 3 **FIFOIE:** FIFO Almost Full Interrupt Enable bit

- bit 2 **RBOVIE:** RX Buffer Overflow Interrupt Enable bit

- bit 1 **RBIE:** RX Buffer Interrupt Enable bit

- bit 0 TBIE: TX Buffer Interrupt Enable bit

### **REGISTER 19-11:** CIFEN1: ECAN™ MODULE ACCEPTANCE FILTER ENABLE REGISTER

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:                                                              |                  |                      |                    |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-0

FLTENn: Enable Filter n to Accept Messages bits

1 = Enable Filter n

0 = Disable Filter n

### REGISTER 19-12: CIBUFPNT1: ECAN™ MODULE FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                 | R/W-0              | R/W-0          | R/W-0                                 | R/W-0           | R/W-0    | R/W-0 |

|---------------|-----------------------|--------------------|----------------|---------------------------------------|-----------------|----------|-------|

| F3BP<3:0>     |                       |                    |                | F2BF                                  | P<3:0>          |          |       |

| bit 15        |                       |                    |                | ·                                     |                 |          | bit 8 |

| R/W-0         | R/W-0                 | R/W-0              | R/W-0          | R/W-0                                 | R/W-0           | R/W-0    | R/W-0 |

|               | F1BP                  | <3:0>              |                |                                       | F0BF            | P<3:0>   |       |

| bit 7         |                       |                    |                |                                       |                 |          | bit 0 |

| Legend:       |                       |                    |                |                                       |                 |          |       |

| R = Readable  | e bit                 | W = Writable       | bit            | U = Unimplen                          | nented bit, rea | d as '0' |       |

| -n = Value at | POR                   | '1' = Bit is set   |                | '0' = Bit is cleared x = Bit is unkno |                 |          | nown  |

|               |                       |                    |                |                                       |                 |          |       |

| bit 15-12     | F3BP<3:0>:            | RX Buffer Writt    | en when Filte  | r 3 Hits bits                         |                 |          |       |

| bit 11-8      | F2BP<3:0>:            | RX Buffer Writt    | en when Filte  | r 2 Hits bits                         |                 |          |       |

| bit 7-4       | F1BP<3:0>:            | RX Buffer Writt    | en when Filte  | r 1 Hits bits                         |                 |          |       |

| bit 3-0       | F0BP<3:0>:            | RX Buffer Writ     | ten when Filte | er 0 Hits bits                        |                 |          |       |

|               | 1111 = Filter         | r hits received ir | n RX FIFO bu   | ffer                                  |                 |          |       |

|               | 1110 <b>= Filte</b> i | r hits received ir | n RX Buffer 14 | 4                                     |                 |          |       |

|               | •                     |                    |                |                                       |                 |          |       |

|               | •                     |                    |                |                                       |                 |          |       |

|               | •                     |                    |                |                                       |                 |          |       |

|               | 0001 <b>= Filte</b> r | r hits received ir | DV Buffor 1    |                                       |                 |          |       |

|               |                       | This received in   |                |                                       |                 |          |       |

## REGISTER 19-26: CiTRmnCON: ECAN™ MODULE TX/RX BUFFER m CONTROL REGISTER

| R/W-0        | R-0                                       | R-0                                  | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0       |

|--------------|-------------------------------------------|--------------------------------------|-------------------------------|------------------|--------------------|-----------------|-------------|

| TXENn        | TXABTN TXLARBN TXERRN TXREQN RTRENN TXnPF |                                      |                               |                  |                    |                 | RI<1:0>     |

| bit 15       |                                           | I                                    |                               |                  |                    |                 | bit         |

|              |                                           |                                      |                               |                  |                    |                 |             |

| R/W-0        | R-0                                       | R-0                                  | R-0                           | R/W-0            | R/W-0              | R/W-0           | R/W-0       |

| TXENm        | TXABTm <sup>(1)</sup>                     | TXLARBm <sup>(1)</sup>               | TXERRm <sup>(1)</sup>         | TXREQm           | RTRENm             | TXmPF           |             |

| bit 7        |                                           |                                      |                               |                  |                    |                 | bit         |

| Legend:      |                                           |                                      |                               |                  |                    |                 |             |

| R = Readab   | le bit                                    | W = Writable                         | bit                           | U = Unimpler     | mented bit, read   | as '0'          |             |

| -n = Value a | t POR                                     | '1' = Bit is set                     |                               | '0' = Bit is cle | ared               | x = Bit is unkr | nown        |

|              |                                           |                                      |                               |                  |                    |                 |             |

| bit 15-8     | See Definitio                             | n for Bits 7-0,                      | Controls Buff                 | fer n            |                    |                 |             |

| bit 7        |                                           | RX Buffer Sele                       |                               |                  |                    |                 |             |

|              |                                           | Bn is a transmi<br>Bn is a receive   |                               |                  |                    |                 |             |

| bit 6        |                                           | essage Aborted                       |                               |                  |                    |                 |             |

|              | 1 = Message                               | •                                    | - Dit                         |                  |                    |                 |             |

|              |                                           | completed trar                       | smission succ                 | essfully         |                    |                 |             |

| bit 5        | TXLARBm:                                  | Message Lost                         | Arbitration bit <sup>(1</sup> | )                |                    |                 |             |

|              |                                           | lost arbitration<br>did not lose arl |                               |                  |                    |                 |             |

| bit 4        | •                                         | ror Detected D                       |                               | •                |                    |                 |             |

|              |                                           | or occurred whi                      | •                             | •                |                    |                 |             |

| bit 3        |                                           | or did not occui<br>essage Send F    |                               | saye was bei     | ng sent            |                 |             |

| DIL D        |                                           | •                                    | •                             | essage The h     | it will automatica | ally clear when | the message |

|              |                                           |                                      |                               |                  | equest a messag    |                 | and moodag  |

| bit 2        | RTRENm: Au                                | ito-Remote Tra                       | nsmit Enable b                | oit              |                    |                 |             |

|              |                                           | emote transmit                       | ,                             |                  |                    |                 |             |

|              |                                           | emote transmit                       | ,                             |                  | unaffected         |                 |             |

| bit 1-0      |                                           | >: Message Tr                        |                               | iority bits      |                    |                 |             |

|              |                                           | message priori<br>ermediate mes      |                               |                  |                    |                 |             |

|              | 01 = Low inte                             |                                      |                               |                  |                    |                 |             |

|              |                                           |                                      |                               |                  |                    |                 |             |

Note 1: This bit is cleared when TXREQ is set.

#### REGISTER 19-29: CiTRBnDLC: ECAN™ MODULE BUFFER n DATA LENGTH CONTROL (n = 0, 1, ..., 31)

| R/W-x |       |       |       |       |       |       |        |

|-------|-------|-------|-------|-------|-------|-------|--------|

|       | R/W-x  |

| RB1   | RTR   | EID0  | EID1  | EID2  | EID3  | EID4  | EID5   |

| bit 8 |       |       |       |       |       |       | bit 15 |

|       |       |       |       |       |       |       | bit 15 |

| U-0   | U-0 | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RB0   | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-10 | EID<5:0>: Extended Identifier bits                                                        |

|-----------|-------------------------------------------------------------------------------------------|

| bit 9     | RTR: Remote Transmission Request bit                                                      |

|           | <ul><li>1 = Message will request remote transmission</li><li>0 = Normal message</li></ul> |

| bit 8     | RB1: Reserved Bit 1                                                                       |

|           | User must set this bit to '0' per CAN protocol.                                           |

| bit 7-5   | Unimplemented: Read as '0'                                                                |

| bit 4     | RB0: Reserved Bit 0                                                                       |

|           | User must set this bit to '0' per CAN protocol.                                           |

| bit 3-0   | DLC<3:0>: Data Length Code bits                                                           |

# REGISTER 19-30: CiTRBnDm: ECAN<sup>TM</sup> MODULE BUFFER n DATA FIELD BYTE m $(n = 0, 1, ..., 31; m = 0, 1, ..., 7)^{(1)}$

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRBnDm7 | TRBnDm6 | TRBnDm5 | TRBnDm4 | TRBnDm3 | TRBnDm2 | TRBnDm1 | TRBnDm0 |

| bit 7   | •       |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-0 TRnDm<7:0>: Data Field Buffer 'n' Byte 'm' bits

Note 1: The Most Significant Byte contains byte (m + 1) of the buffer.

## 21.0 SPECIAL FEATURES

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06/X08/X10 families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Code-Guard<sup>™</sup> Security" (DS70239), Section 24. "Programming and Diagnostics" (DS70246), and Section 25. "Device Configuration" (DS70231) in the "PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

PIC24HJXXXGPX06/X08/X10 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible Configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard™ Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- In-Circuit Emulation

### 21.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The device Configuration register map is shown in Table 21-1.

The individual Configuration bit descriptions for the FBS, FSS, FGS, FOSCSEL, FOSC, FWDT and FPOR Configuration registers are shown in Table 21-2.

Note that address 0xF80000 is beyond the user program memory space. In fact, it belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

The upper byte of all device Configuration registers should always be '1111 1111'. This makes them appear to be NOP instructions in the remote event that their locations are ever executed by accident. Since Configuration bits are not implemented in the corresponding locations, writing '1's to these locations has no effect on device operation.

To prevent inadvertent configuration changes during code execution, all programmable Configuration bits are write-once. After a bit is initially programmed during a power cycle, it cannot be written to again. Changing a device configuration requires that power to the device be cycled.

| Address  | Name    | Bit 7  | Bit 6                   | Bit 5  | Bit 4          | Bit 3  | Bit 2    | Bit 1    | Bit 0   |

|----------|---------|--------|-------------------------|--------|----------------|--------|----------|----------|---------|

| 0xF80000 | FBS     | RBS    | <1:0>                   | —      | _              |        | BSS<2:0> |          | BWRP    |

| 0xF80002 | FSS     | RSS    | <1:0>                   | _      | _              |        | SSS<2:0> |          | SWRP    |

| 0xF80004 | FGS     | _      | —                       | _      | _              | —      | GSS<1    | :0>      | GWRP    |

| 0xF80006 | FOSCSEL | IESO   | Reserved <sup>(2)</sup> | _      | _              | —      | FNC      | )SC<2:0> |         |

| 0xF80008 | FOSC    | FCKSI  | VI<1:0>                 | _      | _              | —      | OSCIOFNC | POSCN    | 1D<1:0> |

| 0xF8000A | FWDT    | FWDTEN | WINDIS                  | _      | WDTPRE         |        | WDTPOST- | <3:0>    |         |

| 0xF8000C | FPOR    | _      | _                       | _      | _              | —      | FPW      | /RT<2:0> |         |

| 0xF8000E | FICD    | Rese   | ved <sup>(1)</sup>      | JTAGEN | _              | —      | —        | ICS<     | :1:0>   |

| 0xF80010 | FUID0   |        |                         |        | User Unit ID E | Byte 0 |          |          |         |

| 0xF80012 | FUID1   |        | User Unit ID Byte 1     |        |                |        |          |          |         |

| 0xF80014 | FUID2   |        | User Unit ID Byte 2     |        |                |        |          |          |         |

| 0xF80016 | FUID3   |        |                         |        | User Unit ID E | Byte 3 |          |          |         |

### TABLE 21-1: DEVICE CONFIGURATION REGISTER MAP

Note 1: When read, these bits will appear as '1'. When you write to these bits, set these bits to '1'.

2: When read, this bit returns the current programmed value.

| Bit Field | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BWRP      | FBS      | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BSS<2:0>  | FBS      | <ul> <li>Boot Segment Program Flash Code Protection Size</li> <li>X11 = No Boot program Flash segment</li> <li>Boot space is 1K IW less VS</li> <li>110 = Standard security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>010 = High security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>Boot space is 4K IW less VS</li> <li>101 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> <li>000 = High security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> </ul> |

| RBS<1:0>  | FBS      | Boot Segment RAM Code Protection<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 Bytes<br>01 = Boot RAM is 256 Bytes<br>00 = Boot RAM is 1024 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SWRP      | FSS      | Secure Segment Program Flash Write Protection<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### TABLE 21-2: PIC24HJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION

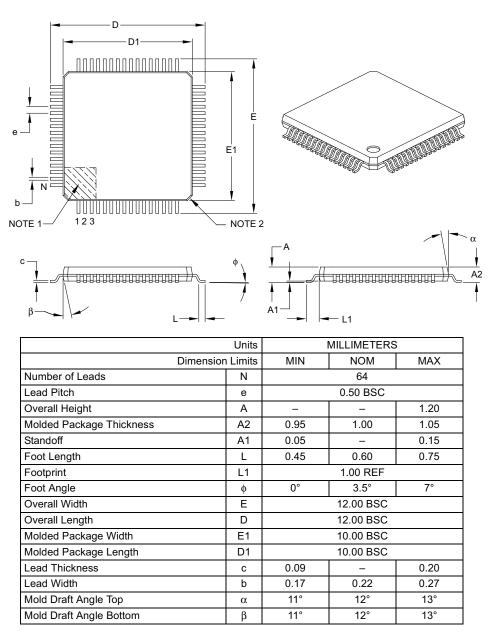

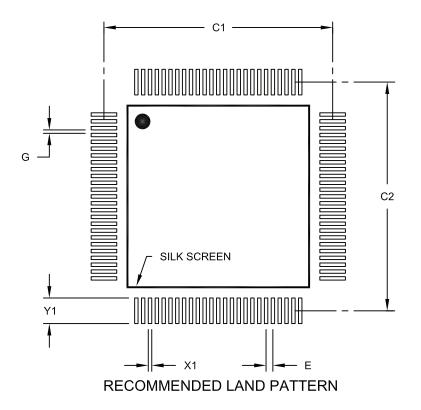

### 25.2 Package Details

### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

### 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIM | ETERS |          |      |

|---------------------------|--------|-------|----------|------|

| Dimension                 | Limits | MIN   | NOM      | MAX  |

| Contact Pitch             | E      |       | 0.40 BSC |      |

| Contact Pad Spacing       | C1     |       | 13.40    |      |

| Contact Pad Spacing       | C2     |       | 13.40    |      |

| Contact Pad Width (X100)  | X1     |       |          | 0.20 |

| Contact Pad Length (X100) | Y1     |       |          | 1.50 |

| Distance Between Pads     | G      | 0.20  |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100A

## INDEX

| Α                                       |    |

|-----------------------------------------|----|

| AC Characteristics                      |    |

| Internal RC Accuracy                    |    |

| Load Conditions                         |    |

| ADC Module                              |    |

| ADC1 Register Map                       |    |

| ADC2 Register Map                       |    |

| Alternate Interrupt Vector Table (AIVT) | 67 |

| Analog-to-Digital Converter             |    |

| DMA                                     |    |

| Initialization                          |    |

| Key Features                            |    |

| Arithmetic Logic Unit (ALU)             | 24 |

| Assembler                               |    |

| MPASM Assembler                         |    |

| Automatic Clock Stretch                 |    |

### В

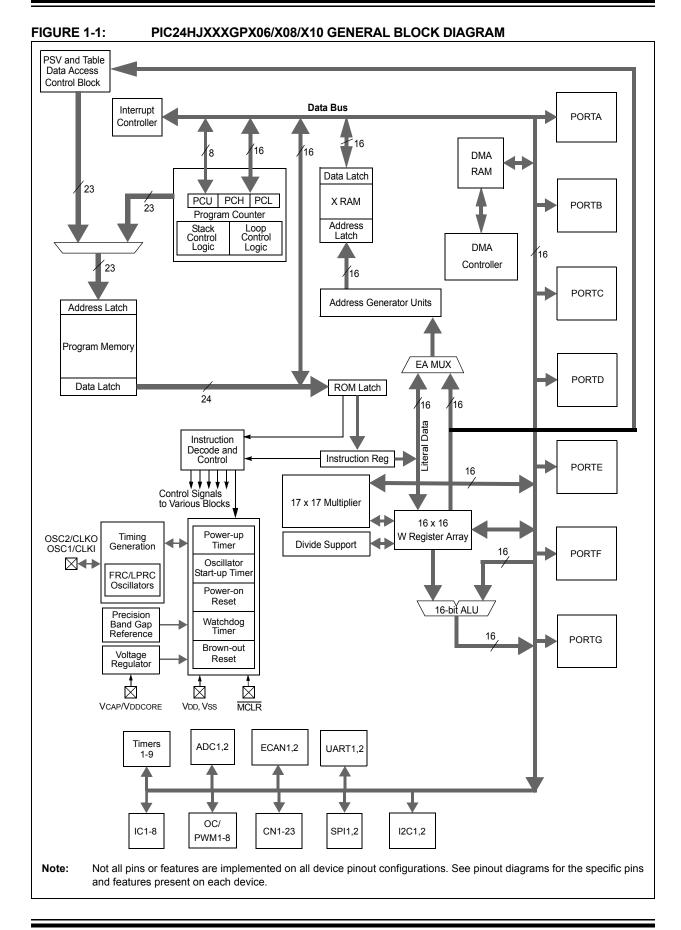

| Block Diagrams                            |     |

|-------------------------------------------|-----|

| 16-bit Timer1 Module                      | 141 |

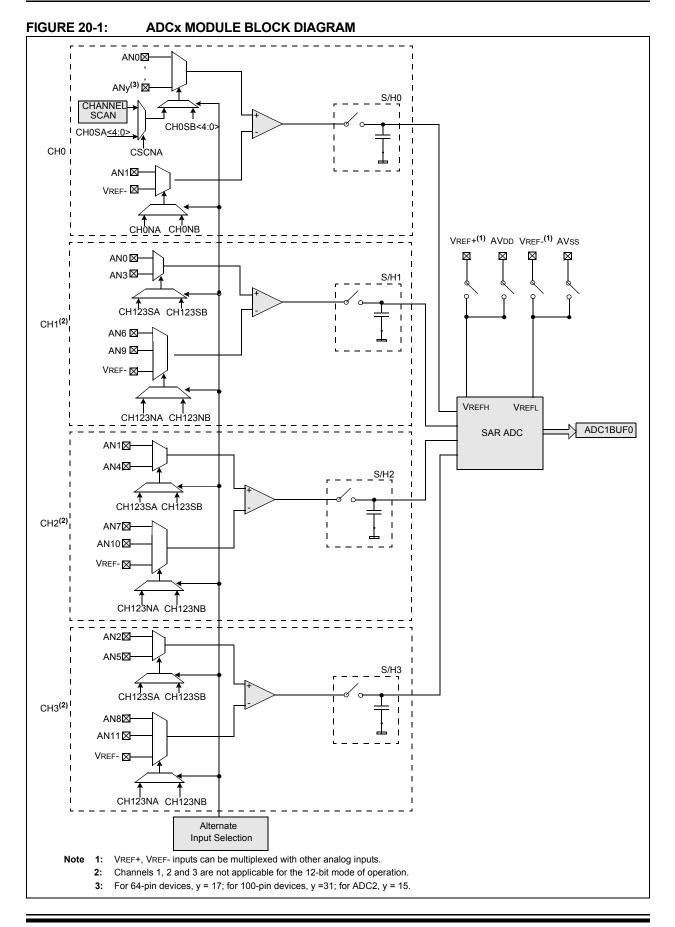

| ADC1 Module                               | 202 |

| Connections for On-Chip Voltage Regulator | 218 |

| ECAN Module                               | 176 |

| Input Capture                             | 149 |

| Output Compare                            | 151 |

| PIC24H                                    | 12  |

| PIC24H CPU Core                           | 20  |

| PIC24H Oscillator System Diagram          | 121 |

| PIC24H PLL                                | 123 |

| Reset System                              | 63  |

| Shared Port Structure                     | 139 |

| SPI                                       | 155 |

| Timer2 (16-bit)                           | 145 |

| Timer2/3 (32-bit)                         | 144 |

| UART                                      | 169 |

| Watchdog Timer (WDT)                      | 219 |

## С

| C Compilers                          |

|--------------------------------------|

| MPLAB C18                            |

| MPLAB C30 230                        |

| Clock Switching                      |

| Enabling129                          |

| Sequence129                          |

| Code Examples                        |

| Erasing a Program Memory Page60      |

| Initiating a Programming Sequence61  |

| Loading Write Buffers61              |

| Port Write/Read140                   |

| PWRSAV Instruction Syntax131         |

| Code Protection                      |

| Configuration Bits                   |

| Description (Table)214               |

| Configuration Register Map 213       |

| Configuring Analog Port Pins 140     |

| CPU                                  |

| Control Register 21                  |

| CPU Clocking System 122              |

| PLL Configuration 122                |

| Selection 122                        |

| Sources                              |

| Customer Change Notification Service |

| Customer Support                     |

## D

| Data Address Space                     | 27  |

|----------------------------------------|-----|

| Alignment                              |     |

| Memory Map for PIC24HJXXXGPX06/X08/X1  |     |

| with 16 KB RAM                         |     |

| Memory Map for PIC24HJXXXGPX06/X08/X1  |     |

| with 8 KB RAM                          |     |

| Near Data Space                        | 27  |

| Software Stack                         |     |

| Width                                  |     |

| DC Characteristics                     | 234 |

| I/O Pin Input Specifications           | 239 |

| I/O Pin Output Specifications          |     |

| Idle Current (IDOZE)                   |     |

| Idle Current (IIDLE)                   | 237 |

| Operating Current (IDD)                | 236 |

| Power-Down Current (IPD)               |     |

| Program Memory                         |     |

| Temperature and Voltage Specifications | 235 |

| Development Support                    |     |

| DMA Module                             |     |

| DMA Register Map                       | 39  |

| DMAC Registers                         | 112 |

| DMAXCNT                                | 112 |

| DMAxCON                                | 112 |

| DMAxPAD                                | 112 |

| DMAxREQ                                | 112 |

| DMAxSTA                                | 112 |

| DMAxSTB                                | 112 |

|                                        |     |

## Ε

| ECAN Module                                        |     |

|----------------------------------------------------|-----|

| CiFMSKSEL2 register 1                              | 193 |

| ECAN1 Register Map (C1CTRL1.WIN = 0 or 1)          | 41  |

| ECAN1 Register Map (C1CTRL1.WIN = 0)               | 41  |

| ECAN1 Register Map (C1CTRL1.WIN = 1)               | 42  |

| ECAN2 Register Map (C2CTRL1.WIN = 0 or 1)          | 44  |

| ECAN2 Register Map (C2CTRL1.WIN = 0)               | 44  |

| ECAN2 Register Map (C2CTRL1.WIN = 1)               | 45  |

| Frame Types 1                                      | 175 |

| Modes of Operation 1                               | 177 |

| Overview1                                          | 175 |

| ECAN Registers                                     |     |

| Filter 15-8 Mask Selection Register (CiFMSKSEL2) 1 | 93  |

| Electrical Characteristics                         | 233 |

| AC                                                 | 242 |

| Enhanced CAN Module 1                              | 175 |

| Equations                                          |     |

| Device Operating Frequency 1                       | 22  |

| FOSC Calculation 1                                 | 22  |

| XT with PLL Mode Example 1                         | 23  |

| Errata                                             | 10  |

| F                                                  |     |

| •                                                  |     |

| Flash Program Memory                               |     |

| Control Registers                                  |     |

| Onerationa                                         | EO  |

| Operations                              | 58  |

|-----------------------------------------|-----|

| Programming Algorithm                   | 60  |

| RTSP Operation                          | 58  |

| Table Instructions                      | 57  |

| Flexible Configuration                  | 213 |

| FSCM                                    |     |

| Delay for Crystal and PLL Clock Sources | 66  |

| Device Resets                           | 66  |

|                                         |     |