Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K × 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp506t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

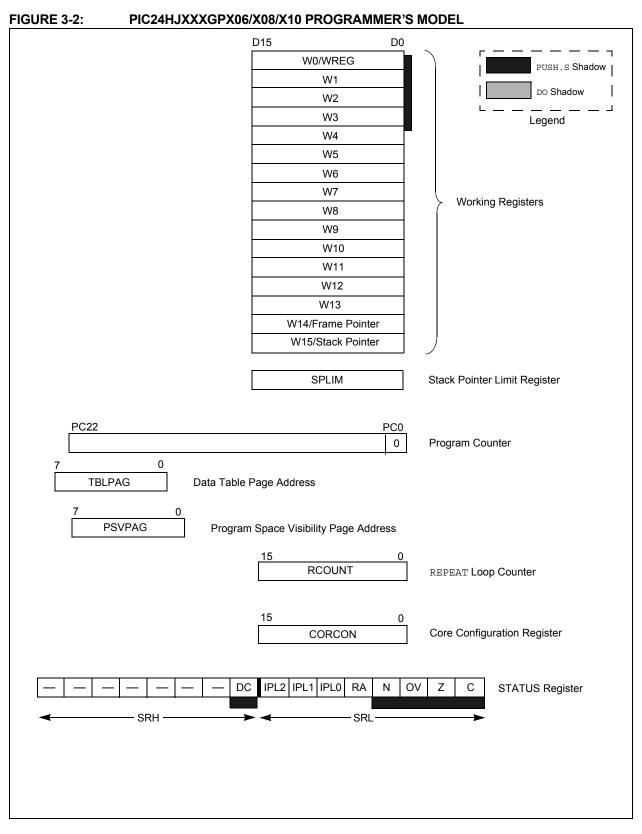

#### 3.3 CPU Control Registers

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6     | Bit 5     | Bit 4         | Bit 3      | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|---------------|--------------|-----------|-----------|---------------|------------|--------------|---------|--------|---------------|

| WREG0    | 0000        |        |        | •      |        |        | •      | •       | Working Re    | egister 0    |           |           |               |            |              |         | •      | 0000          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re    | egister 1    |           |           |               |            |              |         |        | 0000          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re    | egister 2    |           |           |               |            |              |         |        | 0000          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re    | egister 3    |           |           |               |            |              |         |        | 0000          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re    | egister 4    |           |           |               |            |              |         |        | 0000          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re    | egister 5    |           |           |               |            |              |         |        | 0000          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re    | egister 6    |           |           |               |            |              |         |        | 0000          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re    | egister 7    |           |           |               |            |              |         |        | 0000          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re    | egister 8    |           |           |               |            |              |         |        | 0000          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re    | egister 9    |           |           |               |            |              |         |        | 0000          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re    | gister 10    |           |           |               |            |              |         |        | 0000          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re    | gister 11    |           |           |               |            |              |         |        | 0000          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re    | gister 12    |           |           |               |            |              |         |        | 0000          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re    | gister 13    |           |           |               |            |              |         |        | 0000          |

| WREG14   | 001C        |        |        |        |        |        |        |         | Working Re    | gister 14    |           |           |               |            |              |         |        | 0000          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re    | •            |           |           |               |            |              |         |        | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Sta     | ck Pointer Li | mit Register | -         |           |               |            |              |         |        | xxxx          |

| PCL      | 002E        |        |        | •      |        |        | •      | Program | Counter Lo    | w Word Reg   | gister    |           |               |            |              |         |        | 0000          |

| PCH      | 0030        | _      | _      | —      | _      | _      | —      | _       | _             |              |           |           | m Counter     |            | -            |         |        | 0000          |

| TBLPAG   | 0032        | _      | _      | —      | _      | _      | —      | _       | _             |              |           |           | Page Addre    |            | •            |         |        | 0000          |

| PSVPAG   | 0034        | —      | —      | —      | —      | —      | —      | —       | —             |              |           | am Memory | Visibility Pa | age Addres | s Pointer Re | egister |        | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | at Loop Cou   | unter Regist |           |           | 1             |            | 1            | 1       | 1      | XXXX          |

| SR       | 0042        | _      | _      | _      | _      | _      | _      |         | DC            |              | IPL<2:0>  |           | RA            | N          | OV           | Z       | С      | 0000          |

| CORCON   | 0044        | _      | _      | -      | —      | —      | -      | —       | —             | —            | —         | —         | —             | IPL3       | PSV          | —       | —      | 0000          |

| DISICNT  | 0052        | _      | _      |        |        |        |        |         | Disable       | e Interrupts | Counter R | egister   |               |            |              | 1       |        | xxxx          |

| BSRAM    | 0750        |        | —      | —      | —      | —      | -      | —       | —             | —            | —         | —         | —             | —          | IW_BSR       | IR_BSR  | RL_BSR | 0000          |

| SSRAM    | 0752        |        | -      | -      | —      | -      | —      | -       | —             | —            | —         | —         | —             | —          | IW_SSR       | IR_SSR  | RL_SSR | 0000          |

#### TABLE 4-1: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### TABLE 4-28: PORTE REGISTER MAP<sup>(1)</sup>

|           |      |        |        |        |        |        |        |       | -     |        | -      | -      | -      |        |        |        |        |               |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISE     | 02D8 | —      | -      | —      | _      | _      | -      | —     | —     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | XXXX          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-29: PORTF REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|---------------------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF               | 02DE | _      | _      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF               | 02E0 | -      | _      | RF13    | RF12    | -      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF                | 02E2 | -      | _      | LATF13  | LATF12  | -      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF <sup>(2)</sup> | 06DE | _      | _      | ODCF13  | ODCF12  | _      | —      | —     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-30: PORTG REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG               | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG               | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | XXXX          |

| LATG                | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | XXXX          |

| ODCG <sup>(2)</sup> | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | —     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| R/W-0        | R/W-0                | U-0                                 | U-0             | U-0                   | U-0               | U-0              | R/W-0        |

|--------------|----------------------|-------------------------------------|-----------------|-----------------------|-------------------|------------------|--------------|

| TRAPR        | IOPUWR               |                                     | _               |                       | _                 |                  | VREGS        |

| bit 15       |                      |                                     |                 |                       |                   |                  | bit          |

| R/W-0        | R/W-0                | R/W-0                               | R/W-0           | R/W-0                 | R/W-0             | R/W-1            | R/W-1        |

| EXTR         | SWR                  | SWDTEN <sup>(2)</sup>               | WDTO            | SLEEP                 | IDLE              | BOR              | POR          |

| bit 7        |                      |                                     |                 |                       |                   |                  | bit          |

| Legend:      |                      |                                     |                 |                       |                   |                  |              |

| R = Readab   | le bit               | W = Writable I                      | oit             | U = Unimpler          | nented bit, read  | as '0'           |              |

| -n = Value a | t POR                | '1' = Bit is set                    |                 | '0' = Bit is cle      | ared              | x = Bit is unk   | nown         |

| bit 15       | TRAPR: Tran          | Reset Flag bit                      |                 |                       |                   |                  |              |

| bit 10       |                      | onflict Reset ha                    | s occurred      |                       |                   |                  |              |

|              | •                    | onflict Reset ha                    |                 | d                     |                   |                  |              |

| bit 14       | IOPUWR: Ille         | gal Opcode or                       | Uninitialized \ | N Access Rese         | et Flag bit       |                  |              |

|              |                      |                                     |                 | al address mo         | ode or uninitiali | zed W registe    | er used as a |

|              |                      | Pointer caused<br>opcode or unir    |                 | eset has not o        | courred           |                  |              |

| bit 13-9     |                      | ted: Read as '                      |                 |                       | conco             |                  |              |

| bit 8        | -                    | age Regulator S                     |                 | a Sleen hit           |                   |                  |              |

|              |                      | egulator is activ                   | •               | • .                   |                   |                  |              |

|              | •                    | egulator goes i                     | •               | •                     | еер               |                  |              |

| bit 7        |                      | nal Reset (MCL                      |                 |                       |                   |                  |              |

|              |                      | Clear (pin) Res<br>Clear (pin) Res  |                 |                       |                   |                  |              |

| bit 6        |                      |                                     |                 |                       |                   |                  |              |

|              |                      | re Reset (Instruinstruction has     |                 |                       |                   |                  |              |

|              |                      | instruction has                     |                 |                       |                   |                  |              |

| bit 5        | SWDTEN: So           | oftware Enable/                     | Disable of WI   | DT bit <sup>(2)</sup> |                   |                  |              |

|              | 1 = WDT is e         |                                     |                 |                       |                   |                  |              |

|              | 0 = WDT is di        |                                     |                 |                       |                   |                  |              |

| bit 4        |                      | hdog Timer Tim<br>-out has occur    | -               | t                     |                   |                  |              |

|              |                      | e-out has occur                     |                 |                       |                   |                  |              |

| bit 3        |                      | e-up from Sleep                     |                 |                       |                   |                  |              |

|              |                      | as been in Slee                     | -               |                       |                   |                  |              |

|              | 0 = Device ha        | as not been in S                    | leep mode       |                       |                   |                  |              |

| bit 2        |                      | up from Idle Fla                    | g bit           |                       |                   |                  |              |

|              |                      | as in Idle mode<br>as not in Idle m | odo             |                       |                   |                  |              |

| bit 1        |                      | out Reset Flag                      |                 |                       |                   |                  |              |

|              |                      | out Reset has c                     |                 |                       |                   |                  |              |

|              |                      | out Reset has r                     |                 |                       |                   |                  |              |

| bit 0        | POR: Power-          | on Reset Flag I                     | oit             |                       |                   |                  |              |

|              |                      | on Reset has o                      |                 |                       |                   |                  |              |

|              | 0 = A Power-0        | on Reset has n                      | ot occurred     |                       |                   |                  |              |

|              | All of the Reset sta |                                     | e set or cleare | ed in software.       | Setting one of th | nese bits in sof | tware does n |

| 0            | cause a device R     | eset.                               |                 |                       |                   |                  |              |

### 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   |     | DC    |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------------|----------------------|----------------------|-----|-------|-------|-------|-------|

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA  | Ν     | OV    | Z     | С     |

| bit 7                |                      |                      |     |       |       |       | bit 0 |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5 IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10) 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

#### Note 1: For complete register details, see Register 3-1, SR: CPU STATUS Register.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

#### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0               | U-0           | U-0               | U-0              | U-0                 | U-0              | U-0              | U-0   |

|-------------------|---------------|-------------------|------------------|---------------------|------------------|------------------|-------|

| —                 | —             | —                 | —                | —                   | —                | —                | —     |

| bit 15            |               |                   |                  |                     |                  |                  | bit 8 |

|                   |               |                   |                  |                     |                  |                  |       |

| U-0               | U-0           | U-0               | U-0              | R/C-0               | R/W-0            | U-0              | U-0   |

| _                 | —             |                   | —                | IPL3 <sup>(2)</sup> | PSV              | —                | —     |

| bit 7             |               |                   |                  |                     |                  |                  | bit 0 |

|                   |               |                   |                  |                     |                  |                  |       |

| Legend:           |               | C = Clear only    | / bit            |                     |                  |                  |       |

| R = Readable I    | bit           | W = Writable      | bit              | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clear | ed            | ʻx = Bit is unki  | nown             | U = Unimpler        | mented bit, read | as '0'           |       |

|                   |               |                   |                  | (0)                 |                  |                  |       |

| bit 3             | IPL3: CPU Int | errupt Priority   | Level Status b   | bit $3^{(2)}$       |                  |                  |       |

|                   | 1 = CPU inter | rupt priority lev | el is greater tl | han 7               |                  |                  |       |

0 = CPU interrupt priority level is 7 or less

#### Note 1: For complete register details, see Register 3-2, CORCON: CORE Control Register.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

| bit 3 | <b>CNIE:</b> Input Change Notification Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Unimplemented: Read as '0'                                                                                                        |

| bit 1 | MI2C1IE: I2C1 Master Events Interrupt Enable bit                                                                                  |

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul>                                         |

| bit 0 | SI2C1IE: I2C1 Slave Events Interrupt Enable bit                                                                                   |

- 1 = Interrupt request enabled

- 0 = Interrupt request on abled

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _            |                   | T2IP<2:0>                               |                |                   |                  | OC2IP<2:0>      |       |

| bit 15       |                   |                                         |                |                   |                  |                 | bit 8 |

|              |                   |                                         |                |                   |                  |                 |       |

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|              |                   | IC2IP<2:0>                              |                |                   |                  | DMA0IP<2:0>     |       |

| bit 7        |                   |                                         |                |                   |                  |                 | bit C |

| Legend:      |                   |                                         |                |                   |                  |                 |       |

| R = Readab   | le bit            | W = Writable I                          | oit            | U = Unimple       | mented bit, re   | ad as '0'       |       |

| -n = Value a | t POR             | '1' = Bit is set                        |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

| bit 15       | Unimpleme         | ented: Read as 'o                       | )'             |                   |                  |                 |       |

| bit 14-12    | -                 | Timer2 Interrupt                        |                |                   |                  |                 |       |

|              | 111 = Interr      | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      |                |                   |                  |                 |       |

| bit 11       | -                 | ented: Read as 'o                       |                |                   |                  |                 |       |

| bit 10-8     |                   | >: Output Compa                         |                | -                 | rity bits        |                 |       |

|              | 111 = Interr      | upt is priority 7 (I                    | lignest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1<br>upt source is disa | ahlad          |                   |                  |                 |       |

| bit 7        |                   | ented: Read as '                        |                |                   |                  |                 |       |

| bit 6-4      | -                 | Input Capture C                         |                | errupt Priority h | oits             |                 |       |

|              |                   | upt is priority 7 (I                    |                |                   | 110              |                 |       |

|              | •                 |                                         | 0              | , i,              |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •<br>001 = Interr | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      | abled          |                   |                  |                 |       |

| bit 3        | Unimpleme         | ented: Read as 'o                       | )'             |                   |                  |                 |       |

| bit 2-0      | DMA0IP<2:         | 0>: DMA Channe                          | el 0 Data Tra  | nsfer Complete    | e Interrupt Pric | ority bits      |       |

|              | 111 = Interr      | upt is priority 7 (I                    | nighest priori | ty interrupt)     |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      |                |                   |                  |                 |       |

#### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0          | R/W-1                                                               | R/W-0                                    | R/W-0         | U-0                                | R/W-1 | R/W-0           | R/W-0 |  |  |  |  |

|--------------|---------------------------------------------------------------------|------------------------------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|--|--|

| _            |                                                                     | IC8IP<2:0>                               |               | —                                  |       | IC7IP<2:0>      |       |  |  |  |  |

| bit 15       |                                                                     |                                          |               |                                    |       |                 | bit   |  |  |  |  |

| U-0          | R/W-1                                                               | R/W-0                                    | R/W-0         | U-0                                | R/W-1 | R/W-0           | R/W-0 |  |  |  |  |

| _            |                                                                     | AD2IP<2:0>                               | -             | _                                  |       | INT1IP<2:0>     | -     |  |  |  |  |

| bit 7        |                                                                     |                                          |               |                                    |       |                 | bit   |  |  |  |  |

| Legend:      |                                                                     |                                          |               |                                    |       |                 |       |  |  |  |  |

| R = Readab   | le bit                                                              | W = Writable I                           | bit           | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |  |

| -n = Value a | POR                                                                 | '1' = Bit is set                         |               | '0' = Bit is cle                   | ared  | x = Bit is unkn | own   |  |  |  |  |

| bit 15       | Unimpleme                                                           | nted: Read as 'o                         | )'            |                                    |       |                 |       |  |  |  |  |

| bit 14-12    | IC8IP<2:0>:                                                         | Input Capture C                          | hannel 8 Inte | errupt Priority b                  | its   |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)          |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                          |               |                                    |       |                 |       |  |  |  |  |

| bit 11       |                                                                     | nted: Read as 'o                         |               |                                    |       |                 |       |  |  |  |  |

| bit 10-8     | IC7IP<2:0>: Input Capture Channel 7 Interrupt Priority bits         |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)          |                                          |               |                                    |       |                 |       |  |  |  |  |

|              |                                                                     |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                          |               |                                    |       |                 |       |  |  |  |  |

| bit 7        |                                                                     | nted: Read as 'o                         |               |                                    |       |                 |       |  |  |  |  |

| bit 6-4      | AD2IP<2:0>: ADC2 Conversion Complete Interrupt Priority bits        |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt)          |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1                                       |                                          |               |                                    |       |                 |       |  |  |  |  |

|              |                                                                     | upt source is dis                        |               |                                    |       |                 |       |  |  |  |  |

| bit 3        | -                                                                   | nted: Read as 'o                         |               | 1.10                               |       |                 |       |  |  |  |  |

| bit 2-0      |                                                                     | External Interr<br>upt is priority 7 (I) |               |                                    |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          | lighest phon  | ty interrupt)                      |       |                 |       |  |  |  |  |

|              | •                                                                   |                                          |               |                                    |       |                 |       |  |  |  |  |

|              | •<br>001 = Interr                                                   | unt is priority 1                        |               |                                    |       |                 |       |  |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                          |               |                                    |       |                 |       |  |  |  |  |

#### REGISTER 7-20: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0           | R/W-1                                                                                                                                   | R/W-0                                                        | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------|------------------|------------------|-----------------|-------|--|--|--|

| _             |                                                                                                                                         | T4IP<2:0>                                                    |                  |                  |                  | OC4IP<2:0>      |       |  |  |  |

| bit 15        |                                                                                                                                         |                                                              |                  |                  |                  |                 | bit   |  |  |  |

|               |                                                                                                                                         |                                                              |                  |                  |                  |                 |       |  |  |  |

| U-0           | R/W-1                                                                                                                                   | R/W-0                                                        | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|               |                                                                                                                                         | OC3IP<2:0>                                                   |                  |                  |                  | DMA2IP<2:0>     |       |  |  |  |

| bit 7         |                                                                                                                                         |                                                              |                  |                  |                  |                 | bit   |  |  |  |

| Legend:       |                                                                                                                                         |                                                              |                  |                  |                  |                 |       |  |  |  |

| R = Readabl   | e bit                                                                                                                                   | W = Writable I                                               | oit              | U = Unimple      | mented bit, re   | ad as '0'       |       |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                                             |                  | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |  |  |  |

| bit 15        | Unimpleme                                                                                                                               | ented: Read as 'o                                            | )'               |                  |                  |                 |       |  |  |  |

| bit 14-12     | T4IP<2:0>:                                                                                                                              | Timer4 Interrupt                                             | Priority bits    |                  |                  |                 |       |  |  |  |

|               | 111 = Interr                                                                                                                            | 111 = Interrupt is priority 7 (highest priority interrupt)   |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | 001 = Interr                                                                                                                            | 001 = Interrupt is priority 1                                |                  |                  |                  |                 |       |  |  |  |

|               | 000 <b>= Interr</b>                                                                                                                     | upt source is disa                                           | abled            |                  |                  |                 |       |  |  |  |

| bit 11        | Unimpleme                                                                                                                               | ented: Read as 'o                                            | )'               |                  |                  |                 |       |  |  |  |

| bit 10-8      |                                                                                                                                         | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits |                  |                  |                  |                 |       |  |  |  |

|               | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                   |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                     |                                                              |                  |                  |                  |                 |       |  |  |  |

| hit 7         |                                                                                                                                         |                                                              |                  |                  |                  |                 |       |  |  |  |

| bit 7         | -                                                                                                                                       | ented: Read as 'o                                            |                  | Internut Driev   | ity hite         |                 |       |  |  |  |

| bit 6-4       | <b>OC3IP&lt;2:0&gt;:</b> Output Compare Channel 3 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              | lighest phone    | y interrupt)     |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                     |                                                              |                  |                  |                  |                 |       |  |  |  |

| bit 3         | Unimpleme                                                                                                                               | ented: Read as 'o                                            | )'               |                  |                  |                 |       |  |  |  |

| bit 2-0       | DMA2IP<2:                                                                                                                               | 0>: DMA Channe                                               | el 2 Data Tran   | sfer Complete    | e Interrupt Pric | ority bits      |       |  |  |  |

|               | 111 = Interr                                                                                                                            | upt is priority 7 (h                                         | nighest priority | y interrupt)     |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | •                                                                                                                                       |                                                              |                  |                  |                  |                 |       |  |  |  |

|               | 001 = Interr                                                                                                                            | upt is priority 1                                            |                  |                  |                  |                 |       |  |  |  |

|               |                                                                                                                                         |                                                              |                  |                  |                  |                 |       |  |  |  |

#### 13.0 TIMER2/3, TIMER4/5, TIMER6/7 AND TIMER8/9

| Note: | This data sheet summarizes the features<br>of the PIC24HJXXXGPX06/X08/X10 fam- |

|-------|--------------------------------------------------------------------------------|

|       | ily of devices. However, it is not intended                                    |

|       | to be a comprehensive reference source.                                        |

|       | To complement the information in this data                                     |

|       | sheet, refer to the "PIC24H Family Refer-                                      |

|       | ence Manual", Section 11. "Timers"                                             |

|       | (DS70244), which is available from the                                         |

|       | Microchip website (www.microchip.com).                                         |

The Timer2/3, Timer4/5, Timer6/7 and Timer8/9 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3, Timer4/5, Timer6/7 and Timer8/9 operate in three modes:

- Two Independent 16-bit Timers (e.g., Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit Timer

- Single 32-bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- · Timer Operation during Idle and Sleep modes

- Interrupt on a 32-bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

- ADC2 Event Trigger (Timer4/5 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON, T5CON, T6CON, T7CON, T8CON and T9CON registers. T2CON, T4CON, T6CON and T8CON are shown in generic form in Register 13-1. T3CON, T5CON, T7CON and T9CON are shown in Register 13-2. For 32-bit timer/counter operation, Timer2, Timer4, Timer6 or Timer8 is the least significant word; Timer3, Timer5, Timer7 or Timer9 is the most significant word of the 32-bit timers.

To configure Timer2/3, Timer4/5, Timer6/7 or Timer8/9 for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2, Timer4, Timer6 or Timer8 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3, PR5, PR7 or PR9 contains the most significant word of the value, while PR2, PR4, PR6 or PR8 contains the least significant word.

- If interrupts are required, set the interrupt enable bit, T3IE, T5IE, T7IE or T9IE. Use the priority bits, T3IP<2:0>, T5IP<2:0>, T7IP<2:0> or T9IP<2:0>, to set the interrupt priority. While Timer2, Timer4, Timer6 or Timer8 control the timer, the interrupt appears as a Timer3, Timer5, Timer7 or Timer9 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair, TMR3:TMR2, TMR5:TMR4, TMR7:TMR6 or TMR9:TMR8. TMR3, TMR5, TMR7 or TMR9 always contains the most significant word of the count, while TMR2, TMR4, TMR6 or TMR8 contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

NOTES:

#### **19.3 Modes of Operation**

The CAN module can operate in one of several operation modes selected by the user. These modes include:

- Initialization Mode

- Disable Mode

- Normal Operation Mode

- Listen Only Mode

- Listen All Messages Mode

- Loopback Mode

Modes are requested by setting the REQOP<2:0> bits (CiCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CiCTRL1<7:5>). The module will not change the mode and the OPMODE bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 19.3.1 INITIALIZATION MODE

In the Initialization mode, the module will not transmit or receive. The error counters are cleared and the interrupt flags remain unchanged. The programmer will have access to Configuration registers that are access restricted in other modes. The module will protect the user from accidentally violating the CAN protocol through programming errors. All registers which control the configuration of the module can not be modified while the module is on-line. The CAN module will not be allowed to enter the Configuration mode while a transmission is taking place. The Configuration mode serves as a lock to protect the following registers.

- All Module Control Registers

- Baud Rate and Interrupt Configuration Registers

- Bus Timing Registers

- Identifier Acceptance Filter Registers

- Identifier Acceptance Mask Registers

#### 19.3.2 DISABLE MODE

In Disable mode, the module will not transmit or receive. The module has the ability to set the WAKIF bit due to bus activity, however, any pending interrupts will remain and the error counters will retain their value.

If the REQOP<2:0> bits (CiCTRL1<10:8>) = 001, the module will enter the Module Disable mode. If the module is active, the module will wait for 11 recessive bits on the CAN bus, detect that condition as an Idle bus, then accept the module disable command. When the OPMODE<2:0> bits (CiCTRL1<7:5>) = 001, that indicates whether the module successfully went into Module Disable mode. The I/O pins will revert to normal I/O function when the module is in the Module Disable mode.

The module can be programmed to apply a low-pass filter function to the CiRX input line while the module or the CPU is in Sleep mode. The WAKFIL bit (CiCFG2<14>) enables or disables the filter.

Note: Typically, if the CAN module is allowed to transmit in a particular mode of operation and a transmission is requested immediately after the CAN module has been placed in that mode of operation, the module waits for 11 consecutive recessive bits on the bus before starting transmission. If the user switches to Disable mode within this 11-bit period, then this transmission is aborted and the corresponding TXABT bit is set and TXREQ bit is cleared.

#### 19.3.3 NORMAL OPERATION MODE

Normal Operation mode is selected when REQOP<2:0> = 000. In this mode, the module is activated and the I/O pins will assume the CAN bus functions. The module will transmit and receive CAN bus messages via the CiTX and CiRX pins.

#### 19.3.4 LISTEN ONLY MODE

If the Listen Only mode is activated, the module on the CAN bus is passive. The transmitter buffers revert to the port I/O function. The receive pins remain inputs. For the receiver, no error flags or Acknowledge signals are sent. The error counters are deactivated in this state. The Listen Only mode can be used for detecting the baud rate on the CAN bus. To use this, it is necessary that there are at least two further nodes that communicate with each other.

#### 19.3.5 LISTEN ALL MESSAGES MODE

The module can be set to ignore all errors and receive any message. The Listen All Messages mode is activated by setting REQOP<2:0> = '111'. In this mode, the data which is in the message assembly buffer, until the time an error occurred, is copied in the receive buffer and can be read via the CPU interface.

#### 19.3.6 LOOPBACK MODE

If the Loopback mode is activated, the module will connect the internal transmit signal to the internal receive signal at the module boundary. The transmit and receive pins revert to their port I/O function.

'1' = Bit is set

#### REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                        | (n = 0, | 1,, 31)      |         |              |                  |         |         |

|------------------------|---------|--------------|---------|--------------|------------------|---------|---------|

| U-0                    | U-0     | U-0          | R/W-x   | R/W-x        | R/W-x            | R/W-x   | R/W-x   |

| —                      | _       | —            | FILHIT4 | FILHIT3      | FILHIT2          | FILHIT1 | FILHIT0 |

| bit 15                 |         |              |         |              |                  |         | bit 8   |

|                        |         |              |         |              |                  |         |         |

| U-0                    | U-0     | U-0          | U-0     | U-0          | U-0              | U-0     | U-0     |

| —                      | —       | —            | —       | —            | —                | —       | —       |

| bit 7                  |         |              |         |              |                  |         | bit 0   |

|                        |         |              |         |              |                  |         |         |

| Legend:                |         |              |         |              |                  |         |         |

| R = Readable bit W = W |         | W = Writable | bit     | U = Unimpler | mented bit, read | as '0'  |         |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

#### **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1 (where x = 1 or 2) (CONTINUED)

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                         |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                  |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                          |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software may write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software may write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul> |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                            |

|       | <ul> <li>1 = ADC conversion cycle is completed.</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when analog-to-digital conversion is complete. Software may write '0' to clear DONE status (software not allowed to write '1'). Clearing this bit will NOT affect any operation</li> </ul>                                                                   |

in progress. Automatically cleared by hardware at start of a new conversion.

| R/W-0           | U-0                                                                                                  | U-0                                                                                   | R/W-0         | R/W-0                | R/W-0               | R/W-0           | R/W-0 |  |  |

|-----------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|----------------------|---------------------|-----------------|-------|--|--|

| ADRC            |                                                                                                      | _                                                                                     |               |                      | SAMC<4:0>(1         | 1)              |       |  |  |

| bit 15          |                                                                                                      |                                                                                       |               |                      |                     |                 | bit 8 |  |  |

|                 |                                                                                                      |                                                                                       |               |                      |                     |                 |       |  |  |

| R/W-0           | R/W-0                                                                                                | R/W-0                                                                                 | R/W-0         | R/W-0                | R/W-0               | R/W-0           | R/W-0 |  |  |

| 1.1.7           |                                                                                                      |                                                                                       | ADCS          | <7:0> <sup>(2)</sup> |                     |                 |       |  |  |

| bit 7           |                                                                                                      |                                                                                       |               |                      |                     |                 | bit   |  |  |

| Legend:         |                                                                                                      |                                                                                       |               |                      |                     |                 |       |  |  |

| R = Readable    | bit                                                                                                  | W = Writable b                                                                        | it            | U = Unimple          | mented bit, rea     | ad as '0'       |       |  |  |

| -n = Value at P | OR                                                                                                   | '1' = Bit is set                                                                      |               | '0' = Bit is cle     | eared               | x = Bit is unki | nown  |  |  |

|                 |                                                                                                      |                                                                                       |               |                      |                     |                 |       |  |  |

| bit 15          | ADRC: ADC                                                                                            | Conversion Cloc                                                                       | k Source bit  | t                    |                     |                 |       |  |  |

|                 | 1 = ADC internal RC clock                                                                            |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | 0 = Clock derived from system clock                                                                  |                                                                                       |               |                      |                     |                 |       |  |  |

| bit 14-13       | Unimpleme                                                                                            | nted: Read as '0'                                                                     |               |                      |                     |                 |       |  |  |

| bit 12-8        | -                                                                                                    | : Auto Sample Ti                                                                      |               |                      |                     |                 |       |  |  |

|                 | 11111 = 31                                                                                           |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    | in to                                                                                 |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | 00001 = 1 TAD                                                                                        |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | $00000 = 0 T_{0}$                                                                                    | AD                                                                                    |               |                      |                     |                 |       |  |  |

| bit 7-0         | ADCS<7:0>:                                                                                           | : Analog-to-Digita                                                                    | I Conversio   | n Clock Select I     | bits <sup>(2)</sup> |                 |       |  |  |

|                 | 11111111 =                                                                                           | Reserved                                                                              |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | 01000000 =                                                                                           | Reserved                                                                              |               |                      |                     |                 |       |  |  |

|                 |                                                                                                      | TCY · (ADCS<7                                                                         | :0> + 1) = 64 | • Tcy = Tad          |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |

|                 | •                                                                                                    |                                                                                       |               |                      |                     |                 |       |  |  |