Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 85                                                                            |

| Program Memory Size        | 64KB (22K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Data Converters            | A/D 32x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-TQFP                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp510-i-pf |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

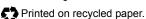

#### 4.2.5 DMA RAM

Every PIC24HJXXXGPX06/X08/X10 device contains 2 Kbytes of dual ported DMA RAM located at the end of data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

**Note:** DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

#### TABLE 4-17: DMA REGISTER MAP

|           | 4-17: |           | REGIS             |        |        | i      |        | İ     |       |          | 1     | 1     |        | 1         | i     |       |       | 1             |

|-----------|-------|-----------|-------------------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|---------------|

| File Name | Addr  | Bit 15    | Bit 14            | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| DMA0CON   | 0380  | CHEN      | SIZE              | DIR    | HALF   | NULLW  |        | —     |       |          | _     | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000          |

| DMA0REQ   | 0382  | FORCE     | FORCE IRQSEL<6:0> |        |        |        |        |       |       |          |       | 0000  |        |           |       |       |       |               |

| DMA0STA   | 0384  |           |                   |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0STB   | 0386  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0PAD   | 0388  |           |                   |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA0CNT   | 038A  |           | _                 | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000          |

| DMA1CON   | 038C  | CHEN      | SIZE              | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA1REQ   | 038E  | FORCE     | _                 | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA1STA   | 0390  |           |                   |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1STB   | 0392  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1PAD   | 0394  |           |                   |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA1CNT   | 0396  | _         | —                 | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000          |

| DMA2CON   | 0398  | CHEN      | SIZE              | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA2REQ   | 039A  | FORCE     | _                 | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA2STA   | 039C  | STA<15:0> |                   |        |        |        |        |       |       | 0000     |       |       |        |           |       |       |       |               |

| DMA2STB   | 039E  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2PAD   | 03A0  |           |                   |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA2CNT   | 03A2  | _         | —                 | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000          |

| DMA3CON   | 03A4  | CHEN      | SIZE              | DIR    | HALF   | NULLW  | _      | _     | _     | _        | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000          |

| DMA3REQ   | 03A6  | FORCE     | —                 | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA3STA   | 03A8  |           |                   |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3STB   | 03AA  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3PAD   | 03AC  |           |                   |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA3CNT   | 03AE  | _         | _                 | —      | —      | _      | —      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000          |

| DMA4CON   | 03B0  | CHEN      | SIZE              | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA4REQ   | 03B2  | FORCE     | _                 | _      | _      | _      | _      | _     | _     | -        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA4STA   | 03B4  |           |                   |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4STB   | 03B6  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4PAD   | 03B8  |           |                   |        |        |        |        |       | P     | AD<15:0> |       |       |        |           |       |       |       | 0000          |

| DMA4CNT   | 03BA  | —         | —                 | _      | —      | _      | —      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000          |

| DMA5CON   | 03BC  | CHEN      | SIZE              | DIR    | HALF   | NULLW  | _      | —     | —     | —        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000          |

| DMA5REQ   | 03BE  | FORCE     | _                 | —      | —      | —      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000          |

| DMA5STA   | 03C0  |           |                   |        |        |        |        |       | S     | TA<15:0> | •     |       |        |           |       |       |       | 0000          |

| DMA5STB   | 03C2  |           |                   |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Compare 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1:INTERRUPT VECTORS

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IF:</b> Output Compare Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IF:</b> Input Capture Channel 1 Interrupt Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred  |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit<br>1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                     |

|  | REGISTER 7-6: | <b>IFS1: INTERRUPT FLAG STATUS REGISTER 1</b> |

|--|---------------|-----------------------------------------------|

|--|---------------|-----------------------------------------------|

| U2TXIF<br>bit 15<br>R/W-0<br>IC8IF<br>bit 7 | U2RXIF         | INT2IF                             | T5IF             | T4IF             | OC4IF            | OC3IF           |         |

|---------------------------------------------|----------------|------------------------------------|------------------|------------------|------------------|-----------------|---------|

| R/W-0<br>IC8IF                              |                | •                                  |                  | 141              | 00416            | OCSIF           | DMA21IF |

| IC8IF                                       |                |                                    | ·                |                  |                  |                 | bit 8   |

|                                             | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | U-0              | R/W-0           | R/W-0   |

| bit 7                                       | IC7IF          | AD2IF                              | INT1IF           | CNIF             | _                | MI2C1IF         | SI2C1IF |

|                                             |                |                                    | 1                | 1                |                  |                 | bit (   |

| Legend:                                     |                |                                    |                  |                  |                  |                 |         |

| R = Readable                                | bit            | W = Writable                       | bit              | U = Unimpler     | mented bit, read | d as '0'        |         |

| -n = Value at F                             | POR            | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

| bit 15                                      | U2TXIF: UAF    | RT2 Transmitte                     | r Interrupt Flag | g Status bit     |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 14                                      | U2RXIF: UAF    | RT2 Receiver li                    | nterrupt Flag S  | Status bit       |                  |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

| L:1 1 0                                     | •              | request has no                     |                  |                  |                  |                 |         |

| bit 13                                      |                | rnal Interrupt 2<br>request has oc | -                | t                |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 12                                      | T5IF: Timer5   | Interrupt Flag                     | Status bit       |                  |                  |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | •              | request has no                     |                  |                  |                  |                 |         |

| bit 11                                      |                | Interrupt Flag<br>request has oc   |                  |                  |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 10                                      | OC4IF: Outp    | ut Compare Ch                      | annel 4 Interru  | upt Flag Status  | s bit            |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 9                                       | -              | ut Compare Ch                      |                  | upt Flag Status  | s bit            |                 |         |

|                                             | 1 = Interrupt  | request has oc<br>request has no   | curred           |                  |                  |                 |         |

| bit 8                                       | DMA21IF: DI    | MA Channel 2 I                     | Data Transfer    | Complete Inte    | rrupt Flag Statu | ıs bit          |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | •              | request has no                     |                  |                  |                  |                 |         |

| bit 7                                       |                | Capture Chann<br>request has oc    | •                | -lag Status bit  |                  |                 |         |

|                                             |                | request has no                     |                  |                  |                  |                 |         |

| bit 6                                       | IC7IF: Input ( | Capture Chann                      | el 7 Interrupt F | lag Status bit   |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| bit 5                                       | AD2IF: ADC2    | 2 Conversion C                     | omplete Interr   | upt Flag Statu   | s bit            |                 |         |

|                                             |                | request has oc                     |                  |                  |                  |                 |         |

|                                             | -              | request has no                     |                  |                  |                  |                 |         |

| bit 4                                       |                | rnal Interrupt 1                   | -                | t                |                  |                 |         |

|                                             |                | request has oc<br>request has no   |                  |                  |                  |                 |         |

| REGISTER /-IU. IEGU. INTERROFTENADEL CONTROL REGISTER U | REGISTER 7-10: | IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 |

|---------------------------------------------------------|----------------|-------------------------------------------|

|---------------------------------------------------------|----------------|-------------------------------------------|

| U-0           | R/W-0        | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|---------------|--------------|-----------------------------------|-----------------|------------------|------------------|-----------------|--------|

| _             | DMA1IE       | AD1IE                             | U1TXIE          | U1RXIE           | SPI1IE           | SPI1EIE         | T3IE   |

| bit 15        |              |                                   |                 |                  |                  |                 | bit 8  |

|               |              |                                   |                 |                  |                  |                 |        |

| R/W-0         | R/W-0        | R/W-0                             | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IE          | OC2IE        | IC2IE                             | DMA0IE          | T1IE             | OC1IE            | IC1IE           | INT0IE |

| bit 7         |              |                                   |                 |                  |                  |                 | bit C  |

| Legend:       |              |                                   |                 |                  |                  |                 |        |

| R = Readable  | e bit        | W = Writable                      | bit             | U = Unimpler     | mented bit, read | l as '0'        |        |

| -n = Value at | POR          | '1' = Bit is set                  | t               | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |

|               |              |                                   |                 |                  |                  |                 |        |

| bit 15        | Unimplemen   | ted: Read as '                    | 0'              |                  |                  |                 |        |

| bit 14        |              |                                   |                 | Complete Interr  | rupt Enable bit  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 13        |              | •                                 |                 | rupt Enable bit  |                  |                 |        |

|               |              | request enable                    | -               |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

| bit 12        | U1TXIE: UAF  | RT1 Transmitte                    | r Interrupt Ena | able bit         |                  |                 |        |

|               |              | request enable                    |                 |                  |                  |                 |        |

| bit 11        | -            | request not ena                   |                 | la hit           |                  |                 |        |

|               |              | RT1 Receiver I<br>request enable  | •               |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

| bit 10        | SPI1IE: SPI1 | Event Interrup                    | t Enable bit    |                  |                  |                 |        |

|               |              | request enable                    |                 |                  |                  |                 |        |

| L:1 0         |              | request not en                    |                 |                  |                  |                 |        |

| bit 9         |              | 1 Error Interru<br>request enable |                 |                  |                  |                 |        |

|               |              | request not enable                |                 |                  |                  |                 |        |

| bit 8         | T3IE: Timer3 | Interrupt Enab                    | le bit          |                  |                  |                 |        |

|               |              | equest enable                     |                 |                  |                  |                 |        |

|               | -            | request not en                    |                 |                  |                  |                 |        |

| bit 7         |              | Interrupt Enab                    |                 |                  |                  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 6         | •            | •                                 |                 | upt Enable bit   |                  |                 |        |

|               | -            | request enable                    |                 |                  |                  |                 |        |

|               | •            | request not en                    |                 |                  |                  |                 |        |

| bit 5         |              | Capture Chann                     | -               | Enable bit       |                  |                 |        |

|               |              | request enable<br>request not ena |                 |                  |                  |                 |        |

| bit 4         | -            | -                                 |                 | Complete Interr  | rupt Enable bit  |                 |        |

| •             |              | request enable                    |                 |                  |                  |                 |        |

|               |              | request not en                    |                 |                  |                  |                 |        |

|               |              |                                   |                 |                  |                  |                 |        |

| bit 3         | T1IE: Timer1 | Interrupt Enab                    | ole bit         |                  |                  |                 |        |

#### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit                               |

|-------|-------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enabled</li></ul> |

| bit 1 | IC1IE: Input Capture Channel 1 Interrupt Enable bit                                       |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

| bit 0 | INTOIE: External Interrupt 0 Enable bit                                                   |

|       | 1 = Interrupt request enabled                                                             |

|       | 0 = Interrupt request not enabled                                                         |

#### REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|---------------|-------------------|------------------------------------------|----------------|-------------------|-----------------|-----------------|-------|

| _             |                   | OC7IP<2:0>                               |                | —                 |                 | OC6IP<2:0>      |       |

| bit 15        |                   |                                          |                |                   |                 |                 | bit 8 |

|               | <b>—</b>          | <b></b>                                  |                |                   |                 |                 |       |

| U-0           | R/W-1             | R/W-0                                    | R/W-0          | U-0               | R/W-1           | R/W-0           | R/W-0 |

|               |                   | OC5IP<2:0>                               |                | —                 |                 | IC6IP<2:0>      | L :4  |

| bit 7         |                   |                                          |                |                   |                 |                 | bit   |

| Legend:       |                   |                                          |                |                   |                 |                 |       |

| R = Readable  | e bit             | W = Writable                             | bit            | U = Unimple       | mented bit, rea | ad as '0'       |       |

| -n = Value at | POR               | '1' = Bit is set                         |                | '0' = Bit is cle  | eared           | x = Bit is unkn | iown  |

| bit 15        | Unimpleme         | ented: Read as '                         | o'             |                   |                 |                 |       |

| bit 14-12     | -                 | >: Output Compa                          |                | Interrupt Prior   | ritv bits       |                 |       |

|               |                   | rupt is priority 7 (                     |                | -                 | ,               |                 |       |

|               | •                 |                                          | •              |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | 001 = Interr      | rupt is priority 1                       |                |                   |                 |                 |       |

|               |                   | rupt source is dis                       | abled          |                   |                 |                 |       |

| bit 11        | Unimpleme         | ented: Read as '                         | 0'             |                   |                 |                 |       |

| bit 10-8      | OC6IP<2:0         | >: Output Compa                          | are Channel 6  | Interrupt Prior   | rity bits       |                 |       |

|               | 111 = Interr      | rupt is priority 7 (                     | highest priori | ty interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | rupt is priority 1                       | . 1. 1 1       |                   |                 |                 |       |

| bit 7         |                   | rupt source is dis<br>ented: Read as '   |                |                   |                 |                 |       |

| bit 6-4       | -                 | >: Output Compa                          |                | Intorrupt Prior   | rity bite       |                 |       |

| DIL 0-4       |                   | rupt is priority 7 (                     |                |                   | ity bits        |                 |       |

|               | •                 |                                          | nightest phon  | ly interrupt)     |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               |                   | rupt is priority 1<br>rupt source is dis | abled          |                   |                 |                 |       |

| bit 3         |                   | ented: Read as '                         |                |                   |                 |                 |       |

| bit 2-0       | -                 | : Input Capture C                        |                | errupt Priority b | oits            |                 |       |

|               |                   | rupt is priority 7 (                     |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •                 |                                          |                |                   |                 |                 |       |

|               | •<br>001 = Interr | rupt is priority 1                       |                |                   |                 |                 |       |

|               |                   |                                          |                |                   |                 |                 |       |

#### 9.1 CPU Clocking System

There are seven system clock options provided by the PIC24HJXXXGPX06/X08/X10:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- · FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- 1. XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 2. HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 3. EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration"**.

The FRC frequency depends on the FRC accuracy (see Table 24-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 21.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJXXXGPX06/X08/ X10 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$FCY = \frac{FOSC}{2}$

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

#### EQUATION 9-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

**REGISTER 9-4:**

#### U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ \_\_\_\_\_ \_\_\_\_ bit 15 bit 8 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 TUN<5:0>(1) \_\_\_\_ bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15-6 Unimplemented: Read as '0' bit 5-0 TUN<5:0>: FRC Oscillator Tuning bits<sup>(1)</sup> 011111 = Center frequency + 11.625% (8.23 MHz) 011110 = Center frequency + 11.25% (8.20 MHz) 000001 = Center frequency + 0.375% (7.40 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.375% (7.345 MHz) 100001 = Center frequency - 11.625% (6.52 MHz) 100000 = Center frequency - 12% (6.49 MHz)

**OSCTUN: FRC OSCILLATOR TUNING REGISTER**

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

#### REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

| R-0 HSC | R-0 HSC | U-0 | U-0 | U-0 | R/C-0 HS | R-0 HSC | R-0 HSC |

|---------|---------|-----|-----|-----|----------|---------|---------|

| ACKSTAT | TRSTAT  | —   | _   | —   | BCL      | GCSTAT  | ADD10   |

| bit 15  |         |     |     |     |          |         | bit 8   |

| R/C-0 HS | R/C-0 HS | R-0 HSC | R/C-0 HSC | R/C-0 HSC | R-0 HSC | R-0 HSC | R-0 HSC |

|----------|----------|---------|-----------|-----------|---------|---------|---------|

| IWCOL    | I2COV    | D_A     | Р         | S         | R_W     | RBF     | TBF     |

| bit 7    |          |         |           |           |         |         | bit 0   |

| Legend:           | U = Unimplemented b | oit, read as '0'     | C = Clear only bit         |  |

|-------------------|---------------------|----------------------|----------------------------|--|

| R = Readable bit  | W = Writable bit    | HS = Set in hardware | HSC = Hardware set/cleared |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared | x = Bit is unknown         |  |

| <b>ACKSTAT:</b> Acknowledge Status bit (when operation) (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = NACK received from slave</li> <li>0 = ACK received from slave</li> </ul>                                                                                                                                        |

| Hardware set or clear at end of slave Acknowledge.                                                                                                                                                                           |

| <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                                                      |

| <ul> <li>1 = Master transmit is in progress (8 bits + ACK)</li> <li>0 = Master transmit is not in progress</li> <li>Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.</li> </ul> |

| Unimplemented: Read as '0'                                                                                                                                                                                                   |

| BCL: Master Bus Collision Detect bit                                                                                                                                                                                         |

| <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No collision</li> </ul>                                                                                                                |

| Hardware set at detection of bus collision.                                                                                                                                                                                  |

| GCSTAT: General Call Status bit                                                                                                                                                                                              |

| 1 = General call address was received<br>0 = General call address was not received<br>Hardware get when address matches general call address. Hardware clear at Step detection                                               |

| Hardware set when address matches general call address. Hardware clear at Stop detection.                                                                                                                                    |

| ADD10: 10-Bit Address Status bit                                                                                                                                                                                             |

| 1 = 10-bit address was matched<br>0 = 10-bit address was not matched                                                                                                                                                         |

| Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.                                                                                                                               |

| IWCOL: Write Collision Detect bit                                                                                                                                                                                            |

| <ul> <li>1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul>                                                                                  |

| Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).                                                                                                                                             |

| I2COV: Receive Overflow Flag bit                                                                                                                                                                                             |

| <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                                                                           |

| Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                                                |

| <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                                                                                      |

| 1 = Indicates that the last byte received was data                                                                                                                                                                           |

| <ul> <li>Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> </ul>                                                       |

| P: Stop bit                                                                                                                                                                                                                  |

| 1 = Indicates that a Stop bit has been detected last                                                                                                                                                                         |

| 0 = Stop bit was not detected last                                                                                                                                                                                           |

| Hardware set or clear when Start, Repeated Start or Stop detected.                                                                                                                                                           |

|                                                                                                                                                                                                                              |

'1' = Bit is set

#### REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                                   | (n = 0, | 1,, 31) |              |                  |         |         |         |

|-----------------------------------|---------|---------|--------------|------------------|---------|---------|---------|

| U-0                               | U-0     | U-0     | R/W-x        | R/W-x            | R/W-x   | R/W-x   | R/W-x   |

| —                                 | _       | —       | FILHIT4      | FILHIT3          | FILHIT2 | FILHIT1 | FILHIT0 |

| bit 15                            |         |         |              |                  |         |         | bit 8   |

|                                   |         |         |              |                  |         |         |         |

| U-0                               | U-0     | U-0     | U-0          | U-0              | U-0     | U-0     | U-0     |

| —                                 | —       | —       | —            | —                | —       | —       | —       |

| bit 7                             |         |         |              |                  |         |         | bit 0   |

|                                   |         |         |              |                  |         |         |         |

| Legend:                           |         |         |              |                  |         |         |         |

| R = Readable bit W = Writable bit |         | bit     | U = Unimpler | mented bit, read | as '0'  |         |         |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

| Bit Field | Register | Description                                                                                                                                                                                                                                                               |  |  |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SSS<2:0>  | FSS      | Secure Segment Program Flash Code Protection Size<br>(FOR 128K and 256K DEVICES)<br>X11 = No Secure program Flash segment                                                                                                                                                 |  |  |

|           |          | Secure space is 8K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE<br>010 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x003FFE                                             |  |  |

|           |          | Secure space is 16K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE<br>001 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x007FFE                                            |  |  |

|           |          | Secure space is 32K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x00FFFE<br>000 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x00FFFE                                            |  |  |

|           |          | (FOR 64K DEVICES)<br>X11 = No Secure program Flash segment                                                                                                                                                                                                                |  |  |

|           |          | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x001FFE                                             |  |  |

|           |          | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE<br>001 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x003FFE                                             |  |  |

|           |          | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE<br>000 = High security; secure program Flash segment starts at End of BS, ends<br>at 0x007FFE                                            |  |  |

| RSS<1:0>  | FSS      | Secure Segment RAM Code Protection<br>11 = No Secure RAM defined<br>10 = Secure RAM is 256 Bytes less BS RAM<br>01 = Secure RAM is 2048 Bytes less BS RAM<br>00 = Secure RAM is 4096 Bytes less BS RAM                                                                    |  |  |

| GSS<1:0>  | FGS      | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard Security; general program Flash segment starts at End of SS,<br>ends at EOM<br>0x = High Security; general program Flash segment starts at End of ESS, ends<br>at EOM |  |  |

| GWRP      | FGS      | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                         |  |  |

#### TABLE 21-2: PIC24HJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field  | Register | Description                                                                                                                                                                                                                                                     |  |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FPWRT<2:0> | FPOR     | Power-on Reset Timer Value Select bits         111 = PWRT = 128 ms         110 = PWRT = 64 ms         101 = PWRT = 32 ms         100 = PWRT = 16 ms         011 = PWRT = 8 ms         010 = PWRT = 4 ms         001 = PWRT = 2 ms         000 = PWRT = Disabled |  |

| JTAGEN     | FICD     | JTAG Enable bits<br>1 = JTAG enabled<br>0 = JTAG disabled                                                                                                                                                                                                       |  |

| ICS<1:0>   | FICD     | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved                                                                                     |  |

#### TABLE 21-2: PIC24HJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

|                    | ABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED) |        |                 |                                                   |               |                |                          |

|--------------------|-------------------------------------------------|--------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic                            |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 35                 | INC                                             | INC    | f               | f = f + 1                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | INC    | f,WREG          | WREG = f + 1                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | INC    | Ws,Wd           | Wd = Ws + 1                                       | 1             | 1              | C,DC,N,OV,Z              |

| 36                 | INC2                                            | INC2   | f               | f = f + 2                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | INC2   | f,WREG          | WREG = f + 2                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | INC2   | Ws,Wd           | Wd = Ws + 2                                       | 1             | 1              | C,DC,N,OV,Z              |

| 37                 | IOR                                             | IOR    | f               | f = f .IOR. WREG                                  | 1             | 1              | N,Z                      |

|                    |                                                 | IOR    | f,WREG          | WREG = f .IOR. WREG                               | 1             | 1              | N,Z                      |

|                    |                                                 | IOR    | #lit10,Wn       | Wd = lit10 .IOR. Wd                               | 1             | 1              | N,Z                      |

|                    |                                                 | IOR    | Wb,Ws,Wd        | Wd = Wb .IOR. Ws                                  | 1             | 1              | N,Z                      |

|                    |                                                 | IOR    | Wb,#lit5,Wd     | Wd = Wb .IOR. lit5                                | 1             | 1              | N,Z                      |

| 38                 | LNK                                             | LNK    | #lit14          | Link Frame Pointer                                | 1             | 1              | None                     |

| 39                 | LSR                                             | LSR    | f               | f = Logical Right Shift f                         | 1             | 1              | C,N,OV,Z                 |

|                    |                                                 | LSR    | f,WREG          | WREG = Logical Right Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                                                 | LSR    | Ws,Wd           | Wd = Logical Right Shift Ws                       | 1             | 1              | C,N,OV,Z                 |

|                    |                                                 | LSR    | Wb,Wns,Wnd      | Wnd = Logical Right Shift Wb by Wns               | 1             | 1              | N,Z                      |

|                    |                                                 | LSR    | Wb,#lit5,Wnd    | Wnd = Logical Right Shift Wb by lit5              | 1             | 1              | N,Z                      |

| 40                 | MOV                                             | MOV    | f,Wn            | Move f to Wn                                      | 1             | 1              | None                     |

|                    |                                                 | MOV    | f               | Move f to f                                       | 1             | 1              | N,Z                      |

|                    |                                                 | MOV    | f,WREG          | Move f to WREG                                    | 1             | 1              | N,Z                      |

|                    |                                                 | MOV    | #lit16,Wn       | Move 16-bit literal to Wn                         | 1             | 1              | None                     |

|                    |                                                 | MOV.b  | #lit8,Wn        | Move 8-bit literal to Wn                          | 1             | 1              | None                     |

|                    |                                                 | MOV    | Wn,f            | Move Wn to f                                      | 1             | 1              | None                     |

|                    |                                                 | MOV    | Wso,Wdo         | Move Ws to Wd                                     | 1             | 1              | None                     |

|                    |                                                 | MOV    | WREG, f         | Move WREG to f                                    | 1             | 1              | N,Z                      |

|                    |                                                 | MOV.D  | Wns,Wd          | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |

|                    |                                                 | MOV.D  | Ws,Wnd          | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2              | None                     |

| 41                 | MUL                                             | MUL.SS | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |

|                    |                                                 | MUL.SU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                                                 | MUL.US | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                                                 | MUL.UU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                                                 | MUL.SU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1             | 1              | None                     |

|                    |                                                 | MUL.UU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                                                 | MUL    | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 42                 | NEG                                             | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                                                 | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 43                 | NOP                                             | NOP    |                 | No Operation                                      | 1             | 1              | None                     |

|                    |                                                 | NOPR   |                 | No Operation                                      | 1             | 1              | None                     |

| 44                 | POP                                             | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                                                 | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                                                 | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1) | 1             | 2              | None                     |

|                    |                                                 | POP.S  |                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 45                 | PUSH                                            | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                                                 | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                                                 | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1             | 2              | None                     |

|                    |                                                 | PUSH.S |                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 46                 | PWRSAV                                          | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

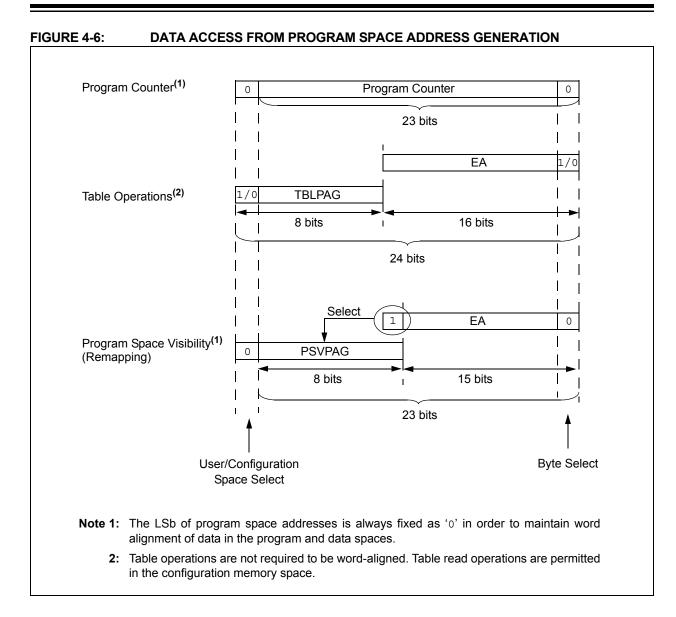

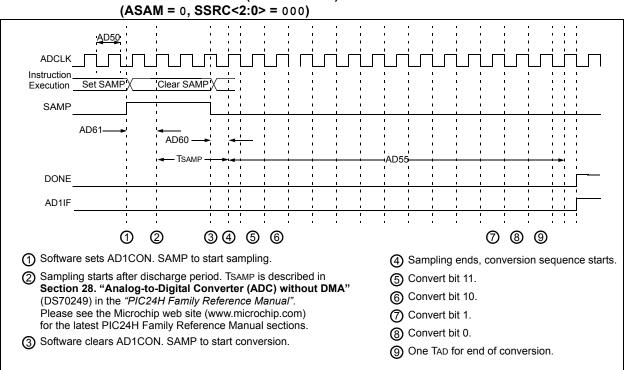

### FIGURE 24-18: ADC CONVERSION (12-BIT MODE) TIMING CHARACTERISTICS

#### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| Product Group Pin Count Tape and Reel Fla |                                                                                                          | <ul> <li>Examples:</li> <li>a) PIC24HJ256GP210I/PT:<br/>General-purpose PIC24H, 256 KB program<br/>memory, 100-pin, Industrial temp.,<br/>TQFP package.</li> <li>b) PIC24HJ64GP506I/PT-ES:<br/>General-purpose PIC24H, 64 KB program<br/>memory, 64-pin, Industrial temp.,<br/>TQFP package, Engineering Sample.</li> </ul> |  |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Architecture:                             | 24 = 16-bit Microcontroller                                                                              |                                                                                                                                                                                                                                                                                                                             |  |  |