Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | -                                                                              |

| Core Size                  | -                                                                              |

| Speed                      | -                                                                              |

| Connectivity               | -                                                                              |

| Peripherals                | -                                                                              |

| Number of I/O              | -                                                                              |

| Program Memory Size        | -                                                                              |

| Program Memory Type        | -                                                                              |

| EEPROM Size                | -                                                                              |

| RAM Size                   | -                                                                              |

| Voltage - Supply (Vcc/Vdd) | -                                                                              |

| Data Converters            | -                                                                              |

| Oscillator Type            | -                                                                              |

| Operating Temperature      | -                                                                              |

| Mounting Type              | -                                                                              |

| Package / Case             | -                                                                              |

| Supplier Device Package    | -                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m37641f8hp-u0 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

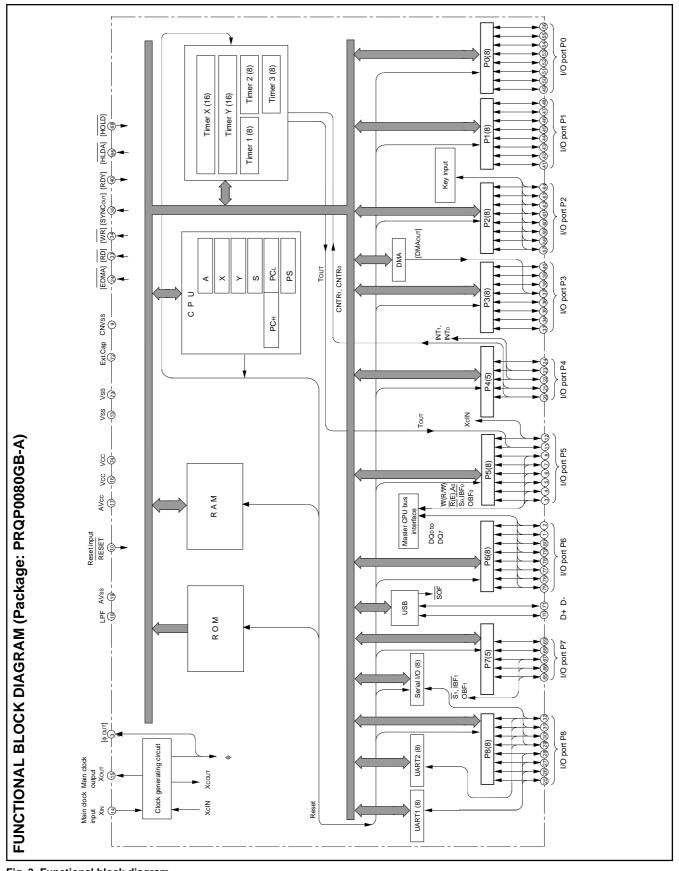

Fig. 3 Functional block diagram

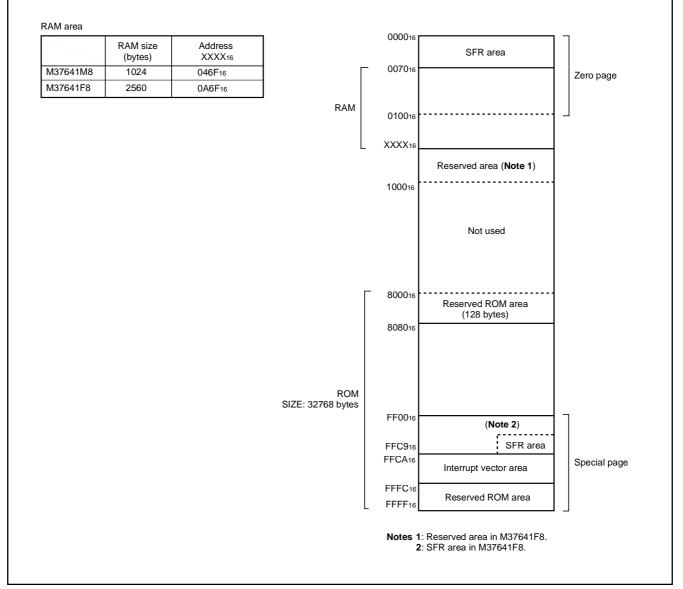

#### MEMORY Special Function Register (SFR) Area

The Special Function Register area in the zero page contains control registers such as I/O ports and timers.

### RAM

RAM is used for data storage and for stack area of subroutine calls and interrupts.

# ROM

The first 128 bytes and the last 4 bytes of ROM are reserved for device testing and the rest is user area for storing programs. In the flash memory version, program and erase can be performed in the reserved area.

#### **Interrupt Vector Area**

The interrupt vector area contains reset and interrupt vectors.

#### Zero Page

Access to this area with only 2 bytes is possible in the zero page addressing mode.

# **Special Page**

Access to this area with only 2 bytes is possible in the special page addressing mode.

Refer to page 74 for the memory map of memory expansion and microprocessor modes.

Fig. 9 Memory map diagram

#### Table 6 List of I/O port function

| Pin                                                                                                                                         | Name    | Input/Output                  | I/O format                                                                                                                | Non-port function                                                     | Related SFRs                                                                                                          | Ref. No.                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| P00/AB0-<br>P07/AB7                                                                                                                         | Port P0 | Input/Output, individual bits | CMOS input level<br>CMOS 3-state output                                                                                   | Lower address output                                                  | CPU mode register A<br>Port control register                                                                          | (1)                                                          |

| P10/AB8–<br>P17/AB15                                                                                                                        | Port P1 |                               |                                                                                                                           | Higher address output                                                 |                                                                                                                       |                                                              |

| P20/DB0–<br>P27/DB7                                                                                                                         | Port P2 |                               | CMOS input level/VIHL<br>input level<br>CMOS 3-state output                                                               | Data bus I/O                                                          | CPU mode register A<br>Port control register<br>Port P2 pull-up control<br>register                                   | (2)                                                          |

| P30/ <u>RD</u> Y–<br>P37/RD                                                                                                                 | Port P3 |                               | CMOS input level<br>CMOS 3-state output                                                                                   | Control signal I/O                                                    | CPU mode register A<br>CPU mode register B                                                                            | (1)                                                          |

| P40/EDMA,                                                                                                                                   | Port P4 |                               |                                                                                                                           |                                                                       | Port control register                                                                                                 | (3)                                                          |

| P41/INT0,<br>P42/INT1,                                                                                                                      |         |                               |                                                                                                                           | Control signal I/O<br>External interrupt                              | CPU mode register A<br>CPU mode register B                                                                            | (4)<br>(5)                                                   |

| P43/CNTR0,<br>P44/CNTR1                                                                                                                     | -       |                               |                                                                                                                           |                                                                       | Port control register<br>Timer X mode register<br>Timer Y mode register<br>Interrupt polarity select register         |                                                              |

| P50/XCIN,<br>P51/TOUT/<br>XCOUT                                                                                                             | Port P5 | -                             | CMOS input level<br>CMOS 3-state output                                                                                   | Timer 1, Timer 2<br>output pin<br>Sub-clock generat-<br>ing input pin | CPU mode register A<br>Port control register<br>Clock control register<br>Timer 123 mode register                     | (6)<br>(7)                                                   |

| P52/OBF0,<br>P53/IBF0,<br>P54/S0,<br>P55/A0,<br>P56/R(E),<br>P57/W(R/W)                                                                     |         |                               | CMOS input level<br>CMOS 3-state output<br>CMOS input level/TTL<br>input level in Master<br>CPU bus inferface<br>function | Master CPU bus<br>interface I/O pin                                   | Data bus buffer control<br>register 0<br>Port control register                                                        | (8)<br>(9)<br>(10)                                           |

| P60/DQ0-<br>P67/DQ7                                                                                                                         | Port P6 | -                             | CMOS input level/TTL<br>input level<br>CMOS 3-state output                                                                | Master CPU bus interface I/O pin                                      | Data bus buffer control<br>register 0<br>Port control register                                                        | (11)                                                         |

| P70/SOF,                                                                                                                                    | Port P7 | -                             | CMOS input level<br>CMOS 3-state output                                                                                   | USB function output pin                                               | USB control register<br>Port control register                                                                         | (12)                                                         |

| P71/HOLD,<br>P72/S1,<br><u>P73/IB</u> F1/<br>HLDA,<br>P74/OBF1                                                                              |         |                               | CMOS input level<br>CMOS 3-state output<br>CMOS input level/TTL<br>input level in Master<br>CPU bus inferface<br>function | Control signal I/O<br>Master CPU bus<br>interface I/O pin             | Data bus buffer control<br>register 1<br>Port control register<br>CPU mode register B                                 | (13)<br>(14)<br>(15)<br>(16)                                 |

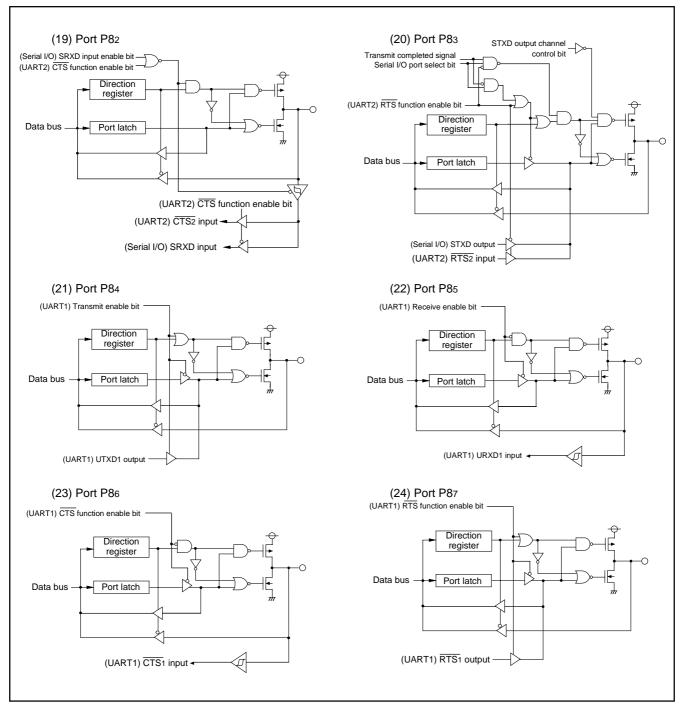

| P80/UTXD2/<br>SRDY,<br>P81/URXD2/<br>SCLK,<br>P82/CTS2/<br>SRXD,<br>P83/RTS2/<br>STXD,<br>P84/UTXD1,<br>P85/URXD1,<br>P86/CTS1,<br>P87/RTS1 | Port P8 |                               | CMOS input level<br>CMOS 3-state output                                                                                   | Serial I/O I/O pin<br>UART2 I/O pin<br>UART1 I/O pin                  | UART1, 2 control registers<br>Serial I/O control register 1<br>Serial I/O control register 2<br>Port control register | (17)<br>(18)<br>(19)<br>(20)<br>(21)<br>(22)<br>(23)<br>(24) |

Notes 1: For details of the ports functions in modes other than single-chip mode, and how to use double-function ports as function I/O ports, refer to the applicable sections.

2: Make sure that the input level at each pin is either 0 V or VCC during execution of the STP instruction.

When an input level is at an intermediate potential, a rush current will flow from VCC to VSS through the input-stage gate.

Fig. 15 Port block diagram (4)

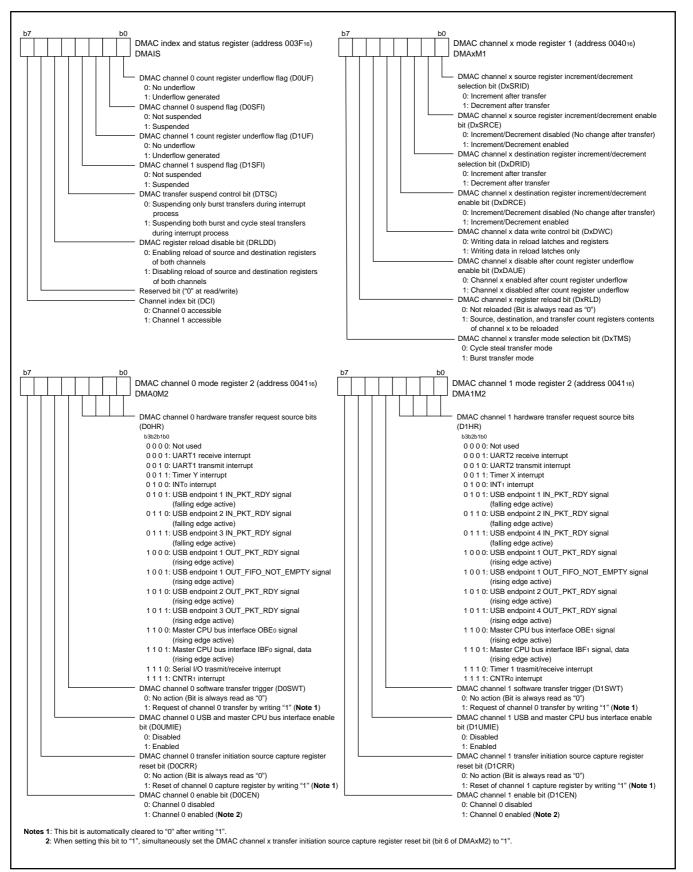

Fig. 32 Structure of DMACx related register

# (1) Cycle Steal Transfer Mode

When the DMAC Channel x (x = 0, 1) Transfer Mode Selection Bit (DxTMS) is set to "0", the respective DMAC Channel x operates in the cycle steal transfer mode.

When a request of the specified transfer factor is generated, the selected channel transfers one byte of data from the address indicated by the Source Register into the address indicated by the Destination Register.

There are two kinds of DMA transfer triggers supported: hardware transfer factor and software trigger. Hardware transfer factors can be selected by the DMACx (x = 0, 1) Hardware Transfer Request Factor Bit (DxHR). To only use the Interrupt Request Bit, the interrupt can be disabled by setting its Interrupt Enable Bit of Interrupt Control Register to "0".

The DMA transfer request as a software trigger can be generated by setting the DMA Channel x (x = 0, 1) Software Transfer Trigger Bit (DxSWT) to "1".

The Source Registers and Transfer Destination Registers can be either decreased or increased by 1 after transfer completion by setting bits 0 to 3 in the DMAC Channel x (x = 0, 1) Mode Register. When the Transfer Count Register underflows, the Source Registers and Destination Registers are reloaded from their latches if the DMAC Register Reload Disable Bit (DRLDD) is "0". The Transfer Count Register value is reloaded after an underflow regardless of DRLDD setting. At the same time, the DMAC Interrupt Request Bit and the DMA Channel x (x = 0, 1) Count Register Underflow Flag are set to "1".

The DMAC Channel x Disable After Count Register Underflow Enable Bit (DxDAUE) is "1", the DMAC Channel x Enable Bit (DxCEN) goes to "0" at an under flows of Transfer Count Register. By setting the DMAC Channel x (x = 0, 1) Register Reload Bit (DxRLD) to "1", the Source Registers, Destination Registers, and Transfer Count Registers can be updated to the values in their respective latches.

When one signal among USB endpoint signals is selected as the hardware transfer request factor, and DMAC Channel x (x = 0, 1) USB and Master CPU Bus Interface Enable Bit (DxUMIE) is "1"; transfer between the USB FIFO and the master CPU bus interface input/output buffer can be performed effectively. This transfer function is only valid in the cycle steal mode. To validate this function, the DMAC Channel x (x = 0, 1) USB and the Master CPU Bus Interface Enable Bit (bit 5 of DxTR) must be set to "1". The following shows an example of a transfer using this function.

# Packet Transfer from USB FIFO to Master CPU Bus Interface Buffer

When the USB OUT\_PKT\_RDY is selected as the hardware transfer request factor; if the USB OUT\_PKT\_RDY is "1" and the master CPU bus interface output buffer is empty, the transfer request is generated and the transfer is initiated. The OUT\_PKT\_RDY retains "1" and a transfer request is generated each time the output buffer empties until all the data in the corresponding endpoint FIFO has been transferred.

The transfer ends when the last byte in the USB receive packet is transferred and the OUT\_PKT\_RDY flag goes to "0" (in the case of AUTO\_CLR bit = "1").

# Byte Transfer from USB FIFO to Master CPU Bus Interface Buffer

When the USB Endpoint 1 OUT\_FIFO\_NOT\_EMPTY is selected as a hardware transfer request factor, if there is data in the USB Endpoint 1 FIFO and the master CPU bus interface output buffer is empty; a transfer request is generated and the transfer is initiated. The transfer is performed by unit of one byte.

# Transfer from Master CPU Bus Interface Buffer to USB FIFO

When the USB Endpoint X (X = 1 to 4) IN\_PKT\_RDY (IN\_PKT\_RDY = "0") is selected as a hardware transfer request factor, if there is data in the master CPU bus interface output buffer and the data in the USB FIFO is within the specified packet size, a transfer request is generated.

The DMA transfer is terminated when a command (A0 = "1") is input to the master CPU bus interface input buffer.

The timing chart for a cycle steal transfer caused by a hardwarerelated transfer request and a software trigger are shown in Figure 33 and 34, respectively.

### **USB** Reception

Endpoint 0 to Endpoint 4 have OUT (receive) FIFOs individually. Each endpoint's FIFO is configured in following way: Endpoint 0: 16-byte Endpoint 1: Mode 0: 800-byte Mode 1: 1024-byte Mode 2: 2048-byte Mode 3: 0-byte Mode 4: 1280-byte Mode 5: 1168-byte

Endpoint 2: Mode 0: 32-byte Mode 1: 128-byte Endpoint 3: 16-byte

Endpoint 3: 16 byte

Endpoint 4: 16-byte

When Endpoint 1 or Endpoint 2 is used for data receive, the OUT FIFO size can be selected. Endpoint 1 and Endpoint 2 have programmable IN-FIFOs size; 6 modes for Endpoint 1, and 2 modes for Endpoint 2. Each mode can be selected by the USB endpoint FIFO mode selection register (address 005F16).

Data transmitted from the host-PC is stored in Endpoint x FIFO (006016 to 006416). Every time the data is stored in the FIFO, the internal OUT FIFO write pointer is increased by 1. When one complete data packet is stored, the OUT\_PKT\_RDY flag is set to "1" and the number of received data packets is stored in USB Endpoint x OUT write count registers (Low and High). When the AUTO\_CLR bit is "1" and the received data is read out from the OUT FIFO, the OUT\_PKT\_RDY flag is cleared to "0". When the AUTO\_CLR bit is "1", the OUT\_PKT\_RDY flag will not be cleared automatically by the FIFO read; it must be cleared by software. (The AUTO-CLR bit function is not applicable in Endpoint 0.)

When MAXP size  $\leq$  (a half of OUT FIFO size), the OUT\_FIFO can receive 2 packets (double buffer). At this time, the OUT\_FIFO status can be checked by the OUT\_PKT\_RDY flag. When the FIFO holds two packets and one packet is read from the FIFO, the OUT\_PKT\_RDY flag is not cleared even if it is set to "0". (The flag returns from "0" to "1" in one  $\phi$  cycle after the read-out). During double buffer mode, the USB Endpoint x OUT write count registers (Low and High) holds the number of previously received packets. This count register is updated after reading out one of packets in the OUT FIFO and clearing the OUT\_PKT\_RDY flag to "0".

# **TOGGLE** Initialization

In order to initialize the data toggle sequence bit of the endpoint, in other words, resetting the next data packet to DATA0; set the ISO/TOGGLE\_INT bit to "1" and then clear back to "0".

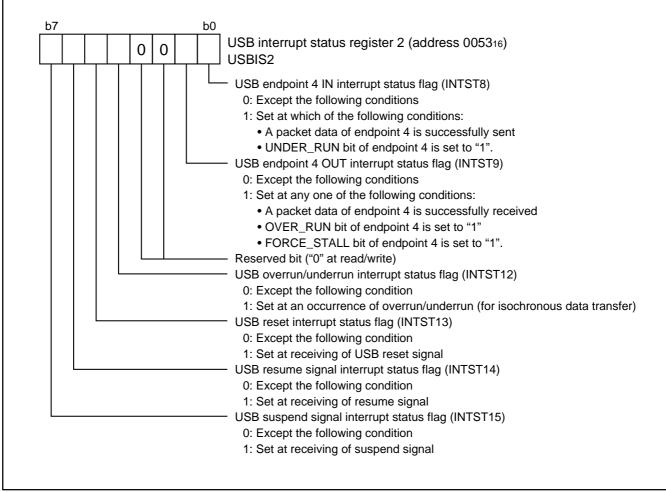

Fig. 41 Structure of USB interrupt status register 2

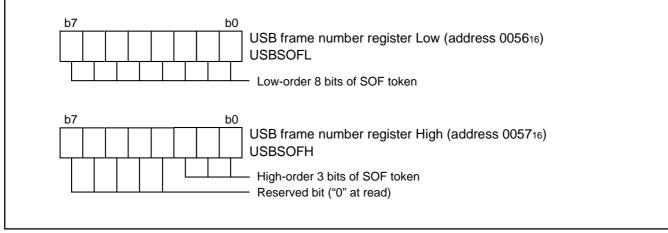

#### [USB Frame Number Registers Low and High ] USBSOFL, USBFOFH

These 11-bit registers contain the frame number of the SOF token received from the host computer. These are read-only registers.

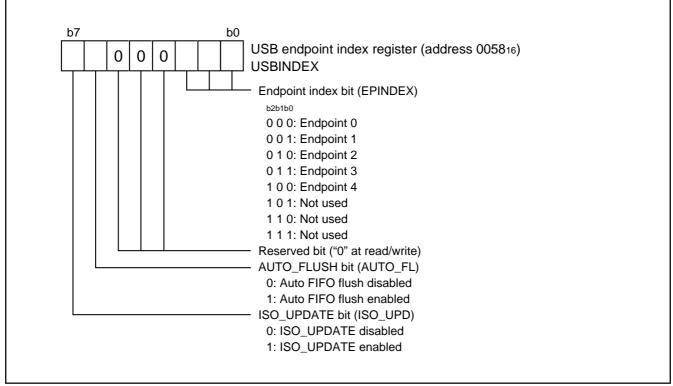

#### [USB Endpoint Index Register] USBINDEX

This register specifies the accessible endpoint. It serves as an index to endpoint-specific USB Endpoint x IN Control Register, USB Endpoint x OUT Control Register, USB Endpoint x IN Max. Packet Size Register, USB Endpoint x OUT Max. Packet Size Register, USB Endpoint x OUT Write Count Register, and USB FIFO Mode Selection Register (x = 0 to 4).

#### Fig. 44 Structure of USB frame number registers

Fig. 45 Structure of USB frame number registers

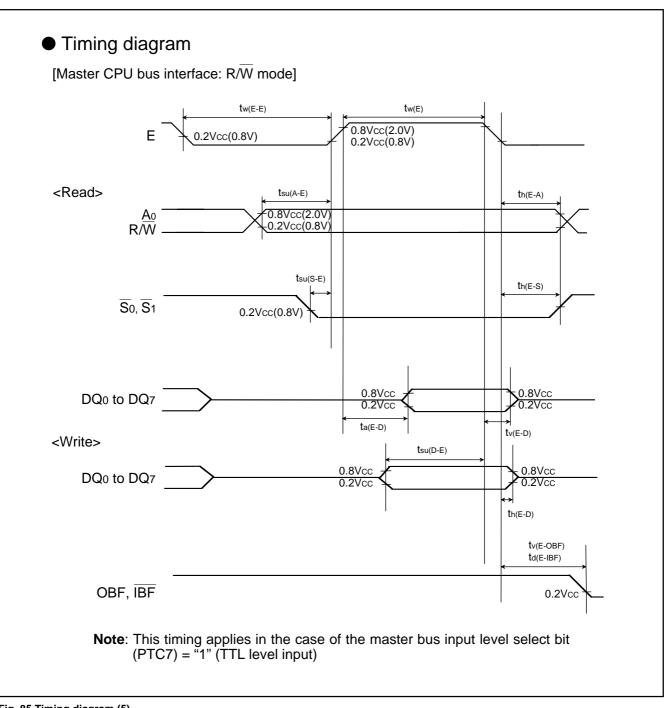

#### MASTER CPU BUS INTERFACE

The 7641 group internally has a 2-byte bus interface which control signals from the host CPU side can operate (slave mode).

This bus interface allows the 7641 group to be directly connected with a R/W type of CPU bus or a  $\overline{RD}$  and  $\overline{WR}$  separated type of CPU bus. Figure 56 shows the block diagram of master CPU bus interface function.

The data bus buffer function I/O pins (P52 - P57, P6, P72-P74) also function as the normal I/O ports. When the Master CPU Bus Interface Enable bit of Data Bus Buffer Control Register (bit 6 of address 004A16) is "0", these pins become the normal I/O ports. When it is "1", these pins become the master CPU bus interface function pins.

Additionally, when using the master CPU bus interface function, set port P6 to input mode by setting "0016" into its port direction register (address 001516).

The selection of either the single data bus buffer mode, which uses 1 byte: data bus buffer 0 only, or the double data bus buffer mode, which uses 2 bytes: data bus buffer 0 and data bus buffer 1, is performed by the Data Bus Buffer Function Select Bit of Data Bus Buffer Control Register 1 (bit 7 of address 004E16). Port P72 becomes  $\overline{S1}$  input pin in the double data bus buffer mode.

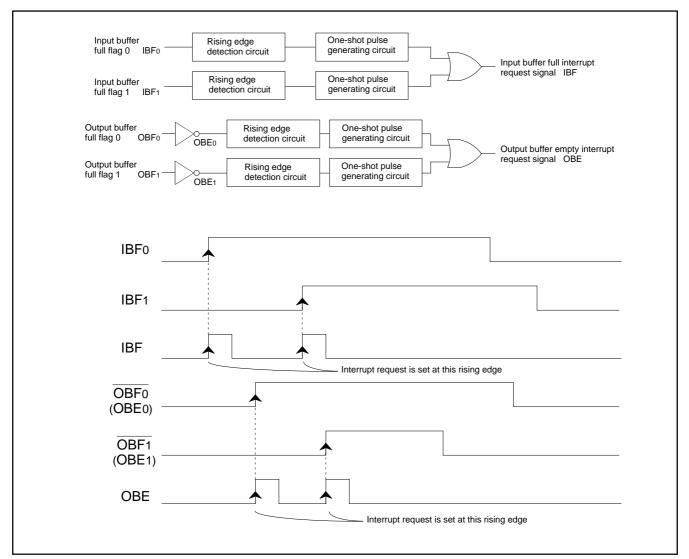

When data is written from the host CPU side, an input buffer full interrupt occurs. When data is read from the host CPU, an output buffer empty interrupt occurs. The 7641 group shares two input buffer full interrupt requests and two output buffer empty interrupt requests as shown in Figure 54, respectively.

The 7641 group can also operate the master CPU bus interface connecting with the Built-in DMAC. This could transfer a large amount of data fast.

An input signal level of data bus buffer function input pins can be selected between a CMOS level and a TTL level. Set it using the Master CPU Bus Input Level Select Bit of Port Control Register (address 001016)

Fig. 54 Interrupt request circuit of data bus buffer

| (1)  | CPU mode register A (CPUA)                | 000016   | 00001100 | (48) UART1 status register (U1STS)                                       | 003216 | 0000011         |

|------|-------------------------------------------|----------|----------|--------------------------------------------------------------------------|--------|-----------------|

| (2)  | CPU mode register B (CPUB)                |          | 1000011  | (49) UART1 control register (U1CON)                                      | 003316 | 0016            |

| (3)  | Interrupt request register A (IREQA)      | 000216   | 0016     | (50) UART1 RTS control register (U1RTSC)                                 |        | 10000000        |

| (4)  | Interrupt request register B (IREQB)      | 000316   | 0016     | (51) UART2 mode register (U2MOD)                                         | 003816 | 0016            |

| (5)  | Interrupt request register C (IREQC)      | 000416   | 0016     | (52) UART2 status register (U2STS)                                       |        |                 |

|      |                                           | 000416   |          |                                                                          | 003A16 |                 |

| (6)  | Interrupt control register A (ICONA)      | 000516   | 0016     | (53) UART2 control register (U2CON)                                      |        |                 |

| (7)  | Interrupt control register B (ICONB)      |          | 0016     | (54) UART2 RTS control register (U2RTSC)                                 |        | 10000000        |

| (8)  | Interrupt control register C (ICONC)      | 000716   | 0016     | (55) DMAC index and status register (DMAIS)                              | 003F16 |                 |

| (9)  | Port P0 (P0)                              | 000816   | 0016     | (56) DMAC channel x mode register 1 (DMAx1)                              | 004016 | 0016            |

|      | Port P0 direction register (P0D)          | 000916   | 0016     | (57) DMAC channel x mode register 2 (DMAx2)                              | 004116 | 0016            |

| (11) | Port P1 (P1)                              | 000A16   | 0016     | (58) DMAC channel x source register Low (DMAxSL)                         | 004216 | 0016            |

| (12) | Port P1 direction register (P1D)          | 000B16   | 0016     | (59) DMAC channel x source register High (DMAxSH)                        | 004316 | 0016            |

| (13) | Port P2 (P2)                              | 000C16   | 0016     | (60) DMAC channel x destination register Low (DMAxDL)                    | 004416 | 0016            |

| (14) | Port P2 direction register (P2D)          | 000D16   | 0016     | (61) DMAC channel x destination register High (DMAxDH)                   | 004516 | 0016            |

| (15) | Port P3 (P3)                              | 000E16   | 0016     | (62) DMAC channel x transfer count register Low (DMAxCL)                 | 004616 | 0016            |

| (16) | Port P3 direction register (P3D)          | 000F16   | 0016     | (63) DMAC channel x transfer count register High (DMAxCH)                | 004716 | 0016            |

| (17) | Port control register (PTC)               | 001016   | 0016     | (64) Data bus buffer register 0 (DBB0)                                   | 004816 | 0016            |

| (18) | Interrupt polarity select register (IPOL) | 001116   | 0016     | (65) Data bus buffer status register 0 (DBBS0)                           | 004916 | 0016            |

| (19) | Port P2 pull-up control register (PUP2)   | 001216   | 0016     | (66) Data bus buffer control register 0 (DBBC0)                          | 004A16 | 0016            |

| (20) | USB control register (USBC)               | 001316   | 0016     | (67) Data bus buffer register 1 (DBB1)                                   | 004C16 | 0016            |

| (21) | Port P6 (P6)                              | 001416   | 0016     | (68) Data bus buffer status register 1 (DBBS1)                           | 004D16 | 0016            |

| (22) | Port P6 direction register (P6D)          | 001516   | 0016     | (69) Data bus buffer control register 1 (DBBC1)                          | 004E16 | 0016            |

| (23) | Port P5 (P5)                              | 001616   | 0016     | (70) USB address register (USBA)                                         | 005016 | 0016            |

| (24) | Port P5 direction register (P5D)          | 001716   | 0016     | (71) USB power management register (USBPM)                               | 005116 | 0016            |

| (25) | Port P4 (P4)                              | 001816   | 0016     | (72) USB interrupt status register 1 (USBIS1)                            | 005216 | 0016            |

| (26) | Port P4 direction register (P4D)          | 001916   | 0016     | (73) USB interrupt status register 2 (USBIS2)                            | 005316 | 0016            |

|      | Port P7 (P7)                              | 001A16   | 0016     | (74) USB interrupt enable register 1 (USBIE1)                            | 005416 | FF16            |

|      | Port P7 direction register (P7D)          | 001B16   | 0016     | (75) USB interrupt enable register 2 (USBIE2)                            |        | 00110011        |

|      | Port P8 (P8)                              | 001C16   | 0016     | (76) USB frame number register Low (USBSOFL)                             | 005616 | 0016            |

|      | Port P8 direction register (P8D)          | 001D16   | 0016     | (77) USB frame number register High (USBSOFH)                            | 005716 | 0016            |

|      | Clock control register (CCR)              | 001E16   |          |                                                                          | 005816 | 0016            |

|      |                                           |          | 0016     | (78) USB endpoint index register (USBINDEX)                              |        |                 |

|      | Timer XL (TXL)                            | 002016   | FF16     | (79) USB endpoint x IN control register (IN_CSR)                         |        | 0016            |

|      | Timer XH (TXH)                            | 002116   | FF16     | (80) USB endpoint x OUT control register (OUT_CSR)                       | 005A16 |                 |

|      | Timer YL (TYL)                            | 002216   | FF16     | (81) USB endpoint x IN max. packet size register (IN_MAXP)<br>(Note 1)   |        |                 |

|      | Timer YH (TYH)                            | 002316   | FF16     | (82) USB endpoint x OUT max. packet size register (OUT_MAXP)<br>(Note 1) |        | r               |

|      | Timer 1 (T1)                              | 002416   | FF16     | (83) USB endpoint x OUT write count register Low (WRT_CNTL)              | 005D16 |                 |

|      | Timer 2 (T2)                              |          | 0000001  | (84) USB endpoint x OUT write count register High (WRT_CNTH)             | 005E16 |                 |

| (38) | Timer 3 (T3)                              | 002616   | FF16     | (85) USB endpoint FIFO mode register (USBFIFOMR)                         | 005F16 | 0016            |

| (39) | Timer X mode register (TXM)               | 002716   | 0016     | (86) Flash memory control register (FMCR)<br>(Note 3)                    |        | 0000001         |

| (40) | Timer Y mode register (TYM)               | 002816   | 0016     | (87) Frequency synthesizer control register (FSC)                        | 006C16 | 01100000        |

| (41) | Timer 123 mode register (T123M)           | 002916   | 0016     | (88) Frequency synthesizer multiply register 1 (FSM1)                    | 006D16 | FF16            |

| (42) | Serial I/O control register 1 (SIOCON1)   | 002B16   | 0100000  | (89) Frequency synthesizer multiply register 2 (FSM2)                    | 006E16 | FF16            |

| (43) | Serial I/O control register 2 (SIOCON2)   | 002C16   | 00011000 | (90) Frequency synthesizer divide register (FSM2)                        | 006F16 | FF16            |

| (44) | Special count source generator 1 (SCSG1)  | 002D16   | FF16     | (91) ROM code protect control register (ROMCP)                           | FFC91  | 6 FF16          |

| (45) | Special count source generator 2 (SCSG2)  | 002E16   | FF16     | (Note 3)<br>(92) Processor status register                               | (PS)   | x x x x x 1 x x |

| (46) | Special count source mode register (SCSGM | ) 002F16 | 0016     | (93) Program counter                                                     | (РСн)  | FFFB16 contents |

| (47) | UART1 mode register (U1MOD)               | 003016   | 0016     |                                                                          | (PCL)  | FFFA16 contents |

2: Since the initial values for other than above mentioned registers and RAM contents are indefinite at reset, they must be set. 3: The flash memory control register and the ROM code protect control register exists in the flash memory version only.

Fig. 63 Internal status at reset

### **Slow Memory Wait**

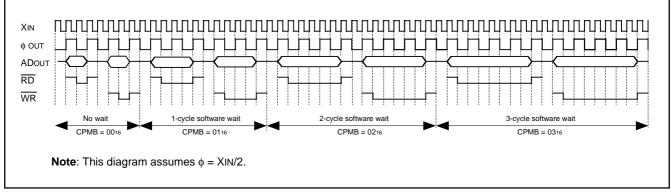

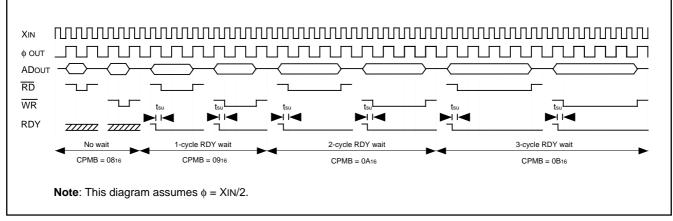

The 7641 Group is equipped with the slow memory wait function (Software wait, RDY wait, and Extended RDY wait: software wait plus RDY input anytime wait) for easier interfacing with external devices that have long access times. The slow memory wait function can be enabled in the memory expansion mode and microprocessor mode. The appropriate wait mode is selected by setting bits 0 to 3 of CPU mode register B (address 000116). This function can extend the read cycle or write cycle only for access to an external memory. However, this wait function cannot be enabled for access to addresses 000816 to 000F16.

# (1) Software wait

The software wait is selected by setting "00" to the Slow Memory Wait Mode Select Bits of CPU mode register B (address 000116). Read/write cycles ("L" width of  $\overline{\text{RD}}$  pin/WR pin) can be extended by one to three  $\phi$  cycles. The number of cycles to be extended can be selected with the Slow Memory Wait Select Bits. When the software wait function is selected, the RDY pin status becomes invalid.

# (2) RDY wait

RDY Wait is selected by setting "10" to the Slow Memory Wait Mode Select Bits of CPU mode register B (address 000116). When a fixed time of "L" is input to the RDY pin at the beginning of a read/write cycle (before  $\phi$  cycle falls), the MCU goes to the RDY state. The read/write cycle can then be extended by one to three  $\phi$ cycles. The number of  $\phi$  cycles to be added can be selected by the Slow Memory Wait Bits.

# (3) Software wait + Extended RDY wait

Extended RDY Wait is selected by setting "11" to the Slow Memory Wait Mode Select Bits of CPU mode register B (address 000116). The read/write cycle can be extended when a fixed time of "L" is input to the RDY pin at the beginning of a read/write cycle (before  $\phi$  cycle falls). The RDY pin state is checked continually at each fall of  $\phi$  cycle until the RDY pin goes to "H". When "H" is input to the RDY pin, the wait is released within 1, 2, or 3  $\phi$  cycles (as selected with the Slow Memory Wait Bits).

Fig. 72 Software wait timing diagram

Fig. 73 RDY wait timing diagram

# In Vcc = 5 V

#### Table 13 Electrical characteristics (2) (Vcc = 4.15 to 5.25 V, Vss = 0 V, Ta = -20 to 70°C, unless otherwise noted)

| Symbol                                                          | Parameter                                                                                                                      | To the second difference                                                                                                                                                   | Limits |      |      |        |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|--------|

|                                                                 |                                                                                                                                | Test conditions                                                                                                                                                            | Min.   | Тур. | Max. | - Unit |

| ICC Power source current<br>(Output transistor is<br>isolated.) | Normal mode ( <b>Note 1</b> )<br>$f(XiN) = 24 \text{ MHz}, \phi = 12 \text{ MHz}$<br>USB operating<br>Frequency synthesizer ON |                                                                                                                                                                            | 40     | 90   | mA   |        |

|                                                                 |                                                                                                                                | Wait mode ( <b>Note 2</b> )<br>$f(XiN) = 24 \text{ MHz}, \phi = 12 \text{ MHz}$<br>USB block enabled, USB clock<br>stopped, Frequency synthesizer ON                       |        | 5.0  | 11   | mA     |

|                                                                 |                                                                                                                                | Wait mode ( <b>Note 3</b> )<br>$f(XCIN) = 32 \text{ kHz}, \phi = 16 \text{ kHz}$<br>USB block disabled<br>Frequency synthesizer OFF<br>USB transceiver DC-DC converter OFF |        |      | 10   | μΑ     |

|                                                                 |                                                                                                                                | Stop mode<br>USB transceiver DC-DC converter ON<br>Low current mode (USBC3 = "1")                                                                                          |        | 100  | 250  | μA     |

|                                                                 |                                                                                                                                | Stop mode<br>USB transceiver DC-DC converter OFF<br>Ta = 25 °C                                                                                                             |        |      | 1.0  | μΑ     |

|                                                                 |                                                                                                                                | Stop mode<br>USB transceiver DC-DC converter OFF<br>Ta = 70 °C                                                                                                             |        |      | 10   | μΑ     |

#### <Test conditions>

Notes 1: Operating in single-chip mode

Clock input from XIN pin (XOUT oscillator stopped)

USB operating with USB transceiver DC-DC converter enabled

Operating functions: Frequency synthesizer, CPU, two UARTs, DMAC, Timers and Count source generator

Disabled functions: Master CPU bus interface and Serial I/O

2: Operating in single-chip mode with Wait mode

Clock input from XIN pin (XOUT oscillator stopped)

USB suspended due to USB clock stopped with USB transceiver DC-DC converter enabled

Operating functions: Frequency synthesizer, Timers and Count source generator

Disabled functions: CPU, two UARTs, DMAC, Master CPU bus interface and Serial I/O

3: Operating in single-chip mode with Wait mode XIN - XOUT oscillator stopped

Clock input from XCIN pin (XCOUT oscillator stopped)

USB stopped, USB clock stopped and USB transceiver DC-DC converter disabled

Operating functions: Timers and Count source generator

Disabled functions: Frequency synthesizer, CPU, two UARTs, DMAC, Master CPU bus interface and Serial I/O

- Notes 1: The total peak output current is the peak value of the peak currents flowing through all the applicable ports. The total average output current is the average value measured over 100 ms flowing through all the applicable ports.

- 2: The peak output current is the peak current flowing in each port.

- 3: The average output current is an average value measured over 100 ms.

- 4: The duty of oscillation frequency is 50 %.

- 5: Connect a ceramic resonator or a quartz-crystal oscillator between the XIN and XOUT pins. Its maximum oscillation frequency must be 24 MHz. However, make sure to set φ to 6 MHz or slower. More faster clocks are required as the f(XIN) when using the frequency synthesizer as possible.

- 6: Connect a ceramic resonator or a quartz-crystal oscillator between the XCIN and XCOUT pins. Its maximum oscillation frequency must be 50 kHz. Input an external clock having 5 MHz (max.) frequency from the XCIN pin.

# Timing Requirements In Vcc = 3 V

| Symbol          | Parameter                                              | Lim               | 1.1  |      |        |  |

|-----------------|--------------------------------------------------------|-------------------|------|------|--------|--|

| Symbol          | Falallelel                                             | Min.              | Тур. | Max. | - Unit |  |

| tw(RESET)       | Reset input "L" pulse width                            | 2                 |      |      | μs     |  |

| tC(XIN)         | Main clock input cycle time (Note)                     | 41.66             |      |      | ns     |  |

| twh(Xin)        | Main clock input "H" pulse width                       | 0.4•tc(XIN)       |      |      | ns     |  |

| twL(XIN)        | Main clock input "L" pulse width                       | 0.4•tc(XIN)       |      |      | ns     |  |

| tC(XCIN)        | Sub-clock input cycle time                             | 200               |      |      | ns     |  |

| tWH(XCIN)       | Sub-clock input "H" pulse width                        | 0.4•tc(XCIN)      |      |      | ns     |  |

| tWL(XCIN)       | Sub-clock input "L" pulse width                        | 0.4•tc(XCIN)      |      |      | ns     |  |

| tC(INT)         | INT0, INT1 input cycle time                            | 250               |      |      | ns     |  |

| twh(INT)        | INTo, INT1 input "H" pulse width                       | 110               |      |      | ns     |  |

| twL(INT)        | INT0, INT1 input "L" pulse width                       | 110               |      |      | ns     |  |

| tc(CNTRI)       | CNTR0, CNTR1 input cycle time                          | 250               |      |      | ns     |  |

| twH(CNTRI)      | CNTR0, CNTR1 input "H" pulse width                     | 110               |      |      | ns     |  |

| twL(CNTRI)      | CNTR0, CNTR1 input "L" pulse width                     | 110               |      |      | ns     |  |

| td(φ -TOUT)     | Timer Tout delay time                                  |                   |      | 17   | ns     |  |

| td(φ -CNTR0)    | Timer CNTRo delay time (Pulse output mode)             |                   |      | 16   | ns     |  |

| tC(CNTRE0)      | Timer CNTRo input cycle time (Event counter mode)      | 250               |      |      | ns     |  |

| tWH(CNTRE0)     | Timer CNTRo input "H" pulse width (Event counter mode) | 0.4•tc(CNTRE0)    |      |      | ns     |  |

| tWL(CNTRE0)     | Timer CNTR0 input "L" pulse width (Event counter mode) | 0.4•tc(CNTRE0)    |      |      | ns     |  |

| td(∳ -CNTR1)    | Timer CNTR1 delay time (Pulse output mode)             |                   |      | 15   | ns     |  |

| tC(CNTRE1)      | Timer CNTR1 input cycle time (Event counter mode)      | 250               |      |      | ns     |  |

| tWH(CNTRE1)     | Timer CNTR1 input "H" pulse width (Event counter mode) | 0.4•tc(CNTRE1)    |      |      | ns     |  |

| tWL(CNTRE1)     | Timer CNTR1 input "L" pulse width (Event counter mode) | 0.4•tc(CNTRE1)    |      |      | ns     |  |

| tC(SCLKE)       | Serial I/O external clock input cycle time             | 450               |      |      | ns     |  |

| tWH(SCLKE)      | Serial I/O external clock input "H" pulse width        | 220               |      |      | ns     |  |

| tWL(SCLKE)      | Serial I/O external clock input "L" pulse width        | 190               |      |      | ns     |  |

| tsu(SRXD-SCLKE) | Serial I/O input setup time (external clock)           | 20                |      |      | ns     |  |

| th(SCLKE-SRXD)  | Serial I/O input hold time (external clock)            | 15                |      |      | ns     |  |

| td(SCLKE-STXD)  | Serial I/O output delay time (external clock)          |                   |      | 34   | ns     |  |

| tv(SCLKE-SRDY)  | Serial I/O SRDY valid time (external clock)            |                   |      | 35   | ns     |  |

| tc(SCLKI)       | Serial I/O internal clock output cycle time            | 300               |      |      | ns     |  |

| twh(SCLKI)      | Serial I/O internal clock output "H" pulse width       | 0.5•tc(SCLKI) - 5 |      |      | ns     |  |

| twL(SCLKI)      | Serial I/O internal clock output "L" pulse width       | 0.5•tc(SCLKI) - 5 |      |      | ns     |  |

| tsu(SRXD-SCLKI) | Serial I/O input setup time (internal clock)           | 20                |      |      | ns     |  |

| th(SCLKI-SRXD)  | Serial I/O input hold time (internal clock)            | 5                 |      |      | ns     |  |

| td(SCLKI-STXD)  | Serial I/O output delay time (internal clock)          |                   |      | 5    | ns     |  |

#### Table 21 Timing requirements (Vcc = 3.0 to 3.6 V, Vss = 0 V, Ta = -20 to 70°C, unless otherwise noted)

Note: Make sure not to exceed 6 MHz of  $\phi,$  in other words,  $tc(\phi) \geq$  166.66 ns).

# **Outline Performance (CPU Rewrite Mode)**

CPU rewrite mode is usable in the single-chip, memory expansion or Boot mode. The only User ROM area can be rewritten in CPU rewrite mode.

In CPU rewrite mode, the CPU erases, programs and reads the internal flash memory by executing software commands. This rewrite control program must be transferred to a memory such as the internal RAM before it can be executed.

The MCU enters CPU rewrite mode by applying 4.50 V to 5.25 V to the CNVss pin and setting "1" to the CPU Rewrite Mode Select Bit (bit 1 of address 006A16). Software commands are accepted once the mode is entered.

Use software commands to control program and erase operations. Whether a program or erase operation has terminated normally or in error can be verified by reading the status register.

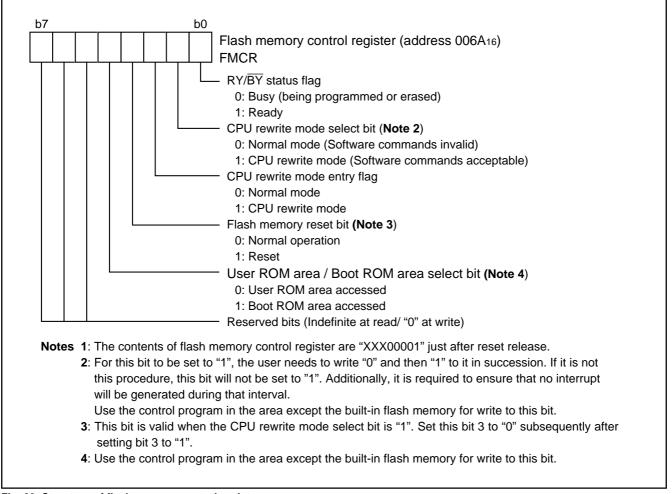

Figure 89 shows the flash memory control register.

Bit 0 is the RY/BY status flag used exclusively to read the operating status of the flash memory. During programming and erase operations, it is "0" (busy). Otherwise, it is "1" (ready).

Bit 1 is the CPU Rewrite Mode Select Bit. When this bit is set to "1", the MCU enters CPU rewrite mode. Software commands are accepted once the mode is entered. In CPU rewrite mode, the CPU becomes unable to access the internal flash memory directly. Therefore, use the control program in a memory other than internal flash memory for write to bit 1. To set this bit to "1", it is necessary to write "0" and then write "1" in succession. The bit can be set to "0" by only writing "0".

Bit 2 is the CPU Rewrite Mode Entry Flag. This flag indicates "1" in CPU rewrite mode, so that reading this flag can check whether CPU rewrite mode has been entered or not.

Bit 3 is the flash memory reset bit used to reset the control circuit of internal flash memory. This bit is used when exiting CPU rewrite mode and when flash memory access has failed. When the CPU Rewrite Mode Select Bit is "1", setting "1" for this bit resets the control circuit. To set this bit to "1", it is necessary to write "0" and then write "1" in succession. To release the reset, it is necessary to set this bit to "0".

Bit 4 is the User Area/Boot Area Select Bit. When this bit is set to "1", Boot ROM area is accessed, and CPU rewrite mode in Boot ROM area is available. In Boot mode, this bit is set to "1" automatically. Reprogramming of this bit must be in a memory other than internal flash memory.

Figure 90 shows a flowchart for setting/releasing CPU rewrite mode.

Fig. 89 Structure of flash memory control register

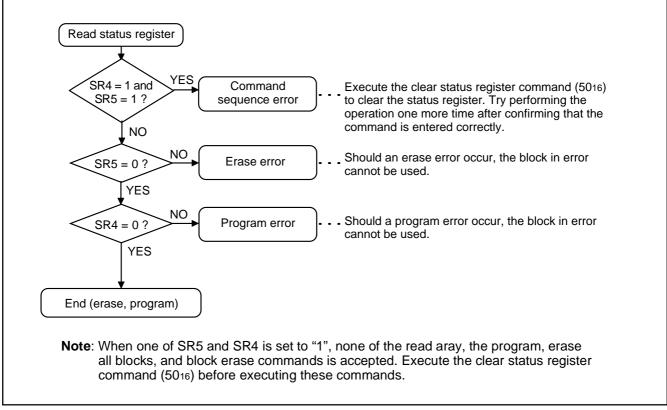

# **Full Status Check**

By performing full status check, it is possible to know the execution results of erase and program operations. Figure 93 shows a full status check flowchart and the action to be taken when each error occurs.

Fig. 93 Full status check flowchart and remedial procedure for errors

# (3) Standard serial I/O Mode

The standard serial I/O mode inputs and outputs the software commands, addresses and data needed to operate (read, program, erase, etc.) the internal flash memory. This I/O is clock synchronized serial. This mode requires the exclusive external equipment (flash programmer).

The standard serial I/O mode is different from the parallel I/O mode in that the CPU controls flash memory rewrite (uses the CPU rewrite mode), rewrite data input and so forth. The standard serial I/O mode is started by connecting "H" to the P36 ( $\overline{CE}$ ) pin and "H" to the P81 (SCLK) pin and "H" to the CNVss pin (apply 4.5 V to 5.25 V to Vpp from an external source), and releasing the reset operation. (In the ordinary microcomputer mode, set CNVss pin to "L" level.)

This control program is written in the Boot ROM area when the product is shipped from Mitsubishi. Accordingly, make note of the fact that the standard serial I/O mode cannot be used if the Boot ROM area is rewritten in parallel I/O mode. Figures 96 and 97 show the pin connections for the standard serial I/O mode.

In standard serial I/O mode, serial data I/O uses the four serial I/O pins SCLK, SRXD, STXD and  $\overline{\text{SRDY}}$  (BUSY). The SCLK pin is the transfer clock input pin through which an external transfer clock is input. The STXD pin is for CMOS output. The  $\overline{\text{SRDY}}$  (BUSY) pin outputs "L" level when ready for reception and "H" level when reception starts.

Serial data I/O is transferred serially in 8-bit units.

In standard serial I/O mode, only the User ROM area shown in Figure 88 can be rewritten. The Boot ROM area cannot.

In standard serial I/O mode, a 7-byte ID code is used. When there is data in the flash memory, commands sent from the peripheral unit (programmer) are not accepted unless the ID code matches.

# Outline Performance (Standard Serial I/O Mode)

In standard serial I/O mode, software commands, addresses and data are input and output between the MCU and peripheral units (flash programer, etc.) using 4-wire clock-synchronized serial I/O. In reception, software commands, addresses and program data are synchronized with the rise of the transfer clock that is input to the SCLK pin, and are then input to the MCU via the SRXD pin. In transmission, the read data and status are synchronized with the fall of the transfer clock, and output from the STXD pin.

The STXD pin is for CMOS output. Transfer is in 8-bit units with LSB first.

When busy, such as during transmission, reception, erasing or program execution, the SRDY (BUSY) pin is "H" level. Accordingly, always start the next transfer after the SRDY (BUSY) pin is "L" level.

Also, data and status registers in a memory can be read after inputting software commands. Status, such as the operating state of the flash memory or whether a program or erase operation ended successfully or not, can be checked by reading the status register. Here following explains software commands, status registers, etc.

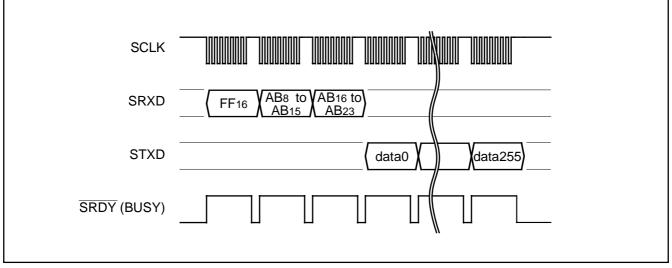

#### Page Read Command

This command reads the specified page (256 bytes) in the flash memory sequentially one byte at a time. Execute the page read command as explained here following.

- (1) Transfer the "FF16" command code with the 1st byte.

- (2) Transfer addresses AB8 to AB15 and AB16 to AB23 with the 2nd and 3rd bytes respectively.

- (3) From the 4th byte onward, data (DBo to DB7) for the page (256 bytes) specified with addresses AB8 to AB23 will be output sequentially from the smallest address first synchronized with the fall of the clock.

Fig. 98 Timing for page read

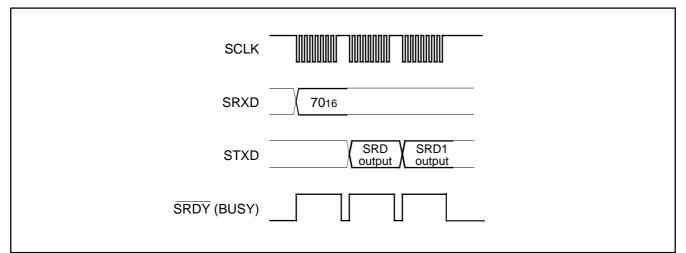

#### •Read Status Register Command

This command reads status information. When the "7016" command code is transferred with the 1st byte, the contents of the status register (SRD) with the 2nd byte and the contents of status register 1 (SRD1) with the 3rd byte are read.

Fig. 99 Timing for reading status register