Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 16KB (16K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25К х 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | ·                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5130a-rdtim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### The table below shows all SFRs with their address and their reset value.

### Table 20. SFR Descriptions

|     | Bit<br>Addressable  |                       |                      | Nc                   | on-Bit Addressat     | ble                 |                      |                      |     |

|-----|---------------------|-----------------------|----------------------|----------------------|----------------------|---------------------|----------------------|----------------------|-----|

|     | 0/8                 | 1/9                   | 2/A                  | 3/B                  | 4/C                  | 5/D                 | 6/E                  | 7/F                  |     |

| F8h | UEPINT<br>0000 0000 | CH<br>0000 0000       | CCAP0H<br>XXXX XXXX  | CCAP1H<br>XXXX XXXX  | CCAP2H<br>XXXX XXXX  | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX  |                      | FFh |

| F0h | B<br>0000 0000      | LEDCON<br>0000 0000   |                      |                      |                      |                     |                      |                      | F7h |

| E8h |                     | CL<br>0000 0000       | CCAP0L<br>XXXX XXXX  | CCAP1L<br>XXXX XXXX  | CCAP2L<br>XXXX XXXX  | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX  |                      | EFh |

| E0h | ACC<br>0000 0000    |                       | UBYCTLX<br>0000 0000 | UBYCTHX<br>0000 0000 |                      |                     |                      |                      | E7h |

| D8h | CCON<br>00X0 0000   | CMOD<br>00XX X000     | CCAPM0<br>X000 0000  | CCAPM1<br>X000 0000  | CCAPM2<br>X000 0000  | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000  |                      | DFh |

| D0h | PSW<br>0000 0000    | FCON (1)<br>XXXX 0000 | EECON<br>XXXX XX00   |                      | UEPCONX<br>1000 0000 | UEPRST<br>0000 0000 |                      |                      | D7h |

| C8h | T2CON<br>0000 0000  | T2MOD<br>XXXX XX00    | RCAP2L<br>0000 0000  | RCAP2H<br>0000 0000  | TL2<br>0000 0000     | TH2<br>0000 0000    | UEPSTAX<br>0000 0000 | UEPDATX<br>0000 0000 | CFh |

| C0h | P4<br>XXXX 1111     |                       | UEPIEN<br>0000 0000  | SPCON<br>0001 0100   | SPSTA<br>0000 0000   | SPDAT<br>XXXX XXXX  | USBADDR<br>1000 0000 | UEPNUM<br>0000 0000  | C7h |

| B8h | IPL0<br>X000 000    | SADEN<br>0000 0000    | UFNUML<br>0000 0000  | UFNUMH<br>0000 0000  | USBCON<br>0000 0000  | USBINT<br>0000 0000 | USBIEN<br>0000 0000  |                      | BFh |

| B0h | P3<br>1111 1111     | IEN1<br>X0XX X000     | IPL1<br>X0XX X000    | IPH1<br>X0XX X000    |                      |                     |                      | IPH0<br>X000 0000    | B7h |

| A8h | IEN0<br>0000 0000   | SADDR<br>0000 0000    |                      |                      |                      |                     |                      | CKCON1<br>0000 0000  | AFh |

| A0h | P2<br>1111 1111     |                       | AUXR1<br>XXXX X0X0   | PLLCON<br>XXXX XX00  | PLLDIV<br>0000 0000  |                     | WDTRST<br>XXXX XXXX  | WDTPRG<br>XXXX X000  | A7h |

| 98h | SCON<br>0000 0000   | SBUF<br>XXXX XXXX     | BRL<br>0000 0000     | BDRCON<br>XXX0 0000  | KBLS<br>0000 0000    | KBE<br>0000 0000    | KBF<br>0000 0000     |                      | 9Fh |

| 90h | P1<br>1111 1111     |                       |                      | SSCON<br>0000 0000   | SSCS<br>1111 1000    | SSDAT<br>1111 1111  | SSADR<br>1111 1110   |                      | 97h |

| 88h | TCON<br>0000 0000   | TMOD<br>0000 0000     | TL0<br>0000 0000     | TL1<br>0000 0000     | TH0<br>0000 0000     | TH1<br>0000 0000    | AUXR<br>XX0X 0000    | CKCON0<br>0000 0000  | 8Fh |

| 80h | P0<br>1111 1111     | SP<br>0000 0111       | DPL<br>0000 0000     | DPH<br>0000 0000     |                      |                     |                      | PCON<br>00X1 0000    | 87h |

|     | 0/8                 | 1/9                   | 2/A                  | 3/B                  | 4/C                  | 5/D                 | 6/E                  | 7/F                  | 1   |

Note: 1. FCON access is reserved for the Flash API and ISP software.

Reserved

## Table 57. CL Register

### CL - PCA Counter Register Low (0E9h)

| 7             | 6               | 5                    | 4   | 3 | 2 | 1 | 0 |

|---------------|-----------------|----------------------|-----|---|---|---|---|

| -             | -               | -                    | -   | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Descriptio           | n   |   |   |   |   |

| 7 - 0         | -               | PCA Coun<br>CL Value | ter |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

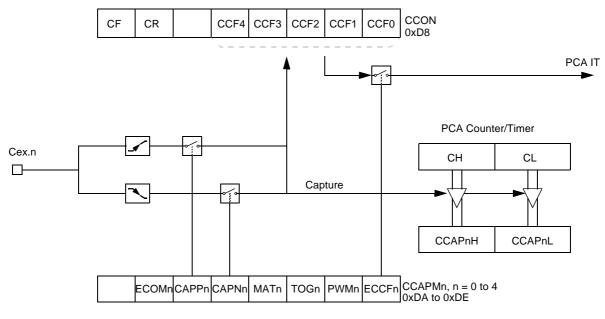

**PCA Capture Mode** To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated (see Figure 27).

#### Figure 27. PCA Capture Mode

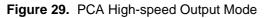

## 16-bit Software Timer/Compare Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 28).

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

Pulse Width Modulator<br/>ModeAll of the PCA modules can be used as PWM outputs. Figure 30 shows the PWM func-<br/>tion. The frequency of the output depends on the source for the PCA timer. All of the<br/>modules will have the same frequency of output because they all share the PCA timer.<br/>The duty cycle of each module is independently variable using the module's capture<br/>register CCAPLn. When the value of the PCA CL SFR is less than the value in the mod-<br/>ule's CCAPLn SFR the output will be low, when it is equal to or greater than the output<br/>will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in<br/>CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in<br/>the module's CCAPMn register must be set to enable the PWM mode.

| Baud Rates | F <sub>osc</sub> = 16 | .384 MHz  | F <sub>OSC</sub> = 24 MHz |           |  |

|------------|-----------------------|-----------|---------------------------|-----------|--|

| Data Nates | BRL                   | Error (%) | BRL                       | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                       | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                       | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                       | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                       | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                       | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                       | 0.16      |  |

| 4800       | 43                    | 1.23      | -                         | -         |  |

Example of computed value when X2 = 1, SMOD1 = 1, SPD = 1

Example of computed value when X2 = 0, SMOD1 = 0, SPD = 0

|            | F <sub>osc</sub> = 16 | .384 MHz      | F <sub>OSC</sub> = 24 MHz |           |  |

|------------|-----------------------|---------------|---------------------------|-----------|--|

| Baud Rates | BRL                   | BRL Error (%) |                           | Error (%) |  |

| 4800       | 247                   | 1.23          | 243                       | 0.16      |  |

| 2400       | 238                   | 1.23          | 230                       | 0.16      |  |

| 1200       | 220                   | 1.23          | 202                       | 3.55      |  |

| 600        | 185                   | 0.16          | 152                       | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 34.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 61.)

## **UART Registers**

#### SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | _ | - | Ι | Ι | - |

Reset Value = 0000 0000b

### SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = 0000 0000b

### SBUF - Serial Buffer Register for UART (99h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | _ | - | - | - |

Reset Value = XXXX XXXXb

## Table 63. IEN0 Register

IEN0 - Interrupt Enable Register (A8h)

| 7             | 6               | 5            | 4                                                                                                                                    | 3                                                          | 2       | 1   | 0   |  |  |

|---------------|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------|-----|-----|--|--|

| EA            | EC              | ET2          | ES                                                                                                                                   | ET1                                                        | EX1     | ET0 | EX0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description  | 1                                                                                                                                    |                                                            |         |     |     |  |  |

| 7             | EA              | Cleared to d | <b>interrupt bit</b><br>lisable all inte<br>e all interrupt                                                                          | •                                                          |         |     |     |  |  |

| 6             | EC              | Cleared to d | <b>CA interrupt enable bit</b><br>leared to disable.<br>et to enable.                                                                |                                                            |         |     |     |  |  |

| 5             | ET2             | Cleared to d | Timer 2 overflow interrupt Enable bit<br>Cleared to disable Timer 2 overflow interrupt.<br>Set to enable Timer 2 overflow interrupt. |                                                            |         |     |     |  |  |

| 4             | ES              |              |                                                                                                                                      | port interrupt.<br>nterrupt.                               |         |     |     |  |  |

| 3             | ET1             | Cleared to d | lisable Timer                                                                                                                        | <b>pt Enable bit</b><br>1 overflow inte<br>erflow interrup | errupt. |     |     |  |  |

| 2             | EX1             | Cleared to d | terrupt 1 Ena<br>lisable extern<br>e external inte                                                                                   | al interrupt 1.                                            |         |     |     |  |  |

| 1             | ET0             | Cleared to d | Timer 0 overflow interrupt Enable bit<br>Cleared to disable timer 0 overflow interrupt.<br>Set to enable timer 0 overflow interrupt. |                                                            |         |     |     |  |  |

| 0             | EX0             | Cleared to d | t <b>errupt 0 Ena</b><br>lisable extern<br>e external inte                                                                           | al interrupt 0.                                            |         |     |     |  |  |

Reset Value = 0000 0000b Bit addressable

## Table 67. IPL1 Register

IPL1 - Interrupt Priority Register (B2h)

| 7             | 6               | 5                        | 4                                                                               | 3               | 2               | 1             | 0     |  |  |  |

|---------------|-----------------|--------------------------|---------------------------------------------------------------------------------|-----------------|-----------------|---------------|-------|--|--|--|

| -             | PUSBL           | -                        | -                                                                               | -               | PSPIL           | PTWIL         | PKBDL |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description              | Description                                                                     |                 |                 |               |       |  |  |  |

| 7             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                 |               |       |  |  |  |

| 6             | PUSBL           |                          | JSB Interrupt Priority bit<br>Refer to PUSBH for priority level.                |                 |                 |               |       |  |  |  |

| 5             | -               | Reserved<br>The value re | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                 |                 |               |       |  |  |  |

| 4             | -               | Reserved<br>The value re | ead from this l                                                                 | pit is indeterm | inate. Do not s | set this bit. |       |  |  |  |

| 3             | -               | Reserved<br>The value re | ead from this I                                                                 | oit is indeterm | inate. Do not s | set this bit. |       |  |  |  |

| 2             | PSPIL           |                          | ot Priority bit                                                                 |                 |                 |               |       |  |  |  |

| 1             | PTWIL           |                          | TWI Interrupt Priority bit<br>Refer to PTWIH for priority level.                |                 |                 |               |       |  |  |  |

| 0             | PKBL            |                          | Keyboard Interrupt Priority bit           Refer to PKBH for priority level.     |                 |                 |               |       |  |  |  |

Reset Value = X0XX X000b Not bit addressable

## Table 71. KBE Register

KBE - Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                                                                                                                     | 3    | 2             | 1              | 0     |  |  |  |

|---------------|-----------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|----------------|-------|--|--|--|

| KBE7          | KBE6            | KBE5          | KBE4                                                                                                                                                  | KBE3 | KBE2          | KBE1           | KBE0  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   | Description                                                                                                                                           |      |               |                |       |  |  |  |

| 7             | KBE7            | Cleared to en | n <b>e 7 Enable k</b><br>nable standar<br>e KBF.7 bit in                                                                                              |      | o generate an | interrupt requ | iest. |  |  |  |

| 6             | KBE6            | Cleared to en | <b>Keyboard line 6 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.6 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 5             | KBE5            | Cleared to en | <b>Keyboard line 5 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF.5 bit in KBF register to generate an interrupt request. |      |               |                |       |  |  |  |

| 4             | KBE4            | Cleared to en | n <b>e 4 Enable k</b><br>nable standar<br>e KBF.4 bit in                                                                                              |      | o generate an | interrupt requ | iest. |  |  |  |

| 3             | KBE3            | Cleared to en | ne 3 Enable k<br>nable standar<br>e KBF.3 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |

| 2             | KBE2            | Cleared to en | ne 2 Enable k<br>nable standar<br>e KBF.2 bit in                                                                                                      |      | o generate an | interrupt requ | iest. |  |  |  |

| 1             | KBE1            | Cleared to en | Keyboard line 1 Enable bit<br>Cleared to enable standard I/O pin.<br>Set to enable KBF.1 bit in KBF register to generate an interrupt request.        |      |               |                |       |  |  |  |

| 0             | KBE0            | Cleared to en | n <b>e 0 Enable k</b><br>nable standar<br>e KBF.0 bit in                                                                                              |      | o generate an | interrupt requ | iest. |  |  |  |

Reset Value = 0000 0000b

Notes:

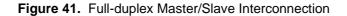

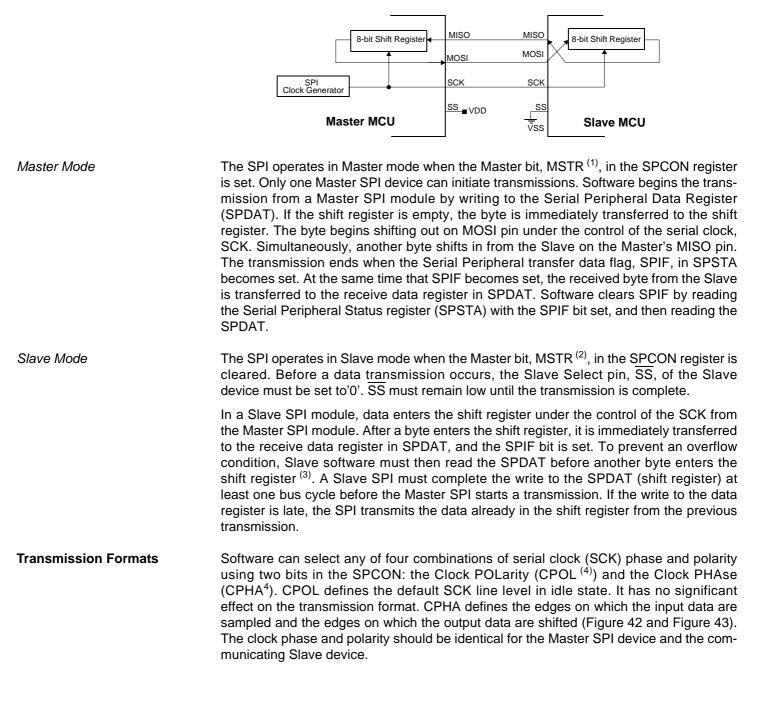

- The SPI module should be configured as a Master before it is enabled (SPEN set). Also the Master SPI should be configured before the Slave SPI.

- 2. The SPI module should be configured as a Slave before it is enabled (SPEN set).

- 3. The maximum frequency of the SCK for an SPI configured as a Slave is  $F_{CLK PERIPH}/2$ .

- Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN ='0').

94 AT89C5130A/31A-M

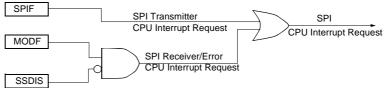

### Figure 45. SPI Interrupt Requests Generation

There are three registers in the module that provide control, status and data storage

### Registers

Serial Peripheral Control Register (SPCON) functions. These registers are describes in the following paragraphs.

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI module

- Frees the SS pin for a general-purpose

Table 76 describes this register and explains the use of each bit. **Table 76.** SPCON Register

| 7             | 6            | 5                          | 4                                                                                                                                                                                                         | 3                   | 2         | 1    | 0    |  |  |

|---------------|--------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|------|------|--|--|

| SPR2          | SPEN         | SSDIS                      | MSTR                                                                                                                                                                                                      | CPOL                | СРНА      | SPR1 | SPR0 |  |  |

| Bit<br>Number | Bit Mnemonic | Descriptio                 | n                                                                                                                                                                                                         |                     |           |      |      |  |  |

| 7             | SPR2         |                            | pheral Rate 2<br>R1 and SPR0                                                                                                                                                                              | 2<br>define the clo | ock rate. |      |      |  |  |

| 6             | SPEN         | Cleared to                 | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                                     |                     |           |      |      |  |  |

| 5             | SSDIS        | Cleared to<br>Set to disal | SS Disable<br>Cleared to enable $\overline{SS}$ in both Master and Slave modes.<br>Set to disable $\overline{SS}$ in both Master and Slave modes. In Slave mode, this bit has<br>no effect if CPHA = "0". |                     |           |      |      |  |  |

| 4             | MSTR         | Cleared to                 | pheral Maste<br>configure the<br>gure the SPI                                                                                                                                                             | SPI as a Slav       | e.        |      |      |  |  |

| 3             | CPOL         | Cleared to                 | Clock Polarity<br>Cleared to have the SCK set to "0" in idle state.<br>Set to have the SCK set to "1" in idle state.                                                                                      |                     |           |      |      |  |  |

| 2             | СРНА         | CPOL).                     | have the data                                                                                                                                                                                             | sampled whe         |           |      |      |  |  |

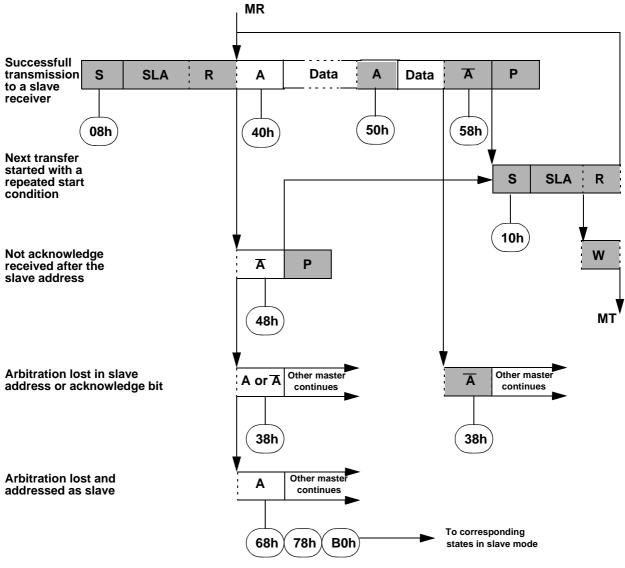

|               |                                                                 | Application software response |       |        |     |      |                                                                                                |  |

|---------------|-----------------------------------------------------------------|-------------------------------|-------|--------|-----|------|------------------------------------------------------------------------------------------------|--|

| Status        | Status of the Two-                                              |                               |       | To SSC | CON |      |                                                                                                |  |

| Code<br>SSSTA | wire Bus and Two-<br>wire Hardware                              | To/From SSDAT                 | SSSTA | SSSTO  | SSI | SSAA | Next Action Taken by Two-wire Hardware                                                         |  |

| 08h           | A START condition has been transmitted                          | Write SLA+W                   | х     | 0      | 0   | х    | SLA+W will be transmitted.                                                                     |  |

| 10h           | A repeated START<br>condition has been<br>transmitted           | Write SLA+W                   | х     | 0      | 0   | x    | SLA+W will be transmitted.                                                                     |  |

|               |                                                                 | Write SLA+R                   | х     | 0      | 0   | х    | SLA+R will be transmitted.<br>Logic will switch to master receiver mode                        |  |

|               |                                                                 | Write data byte               | 0     | 0      | 0   | x    | Data byte will be transmitted.                                                                 |  |

|               | SLA+W has been                                                  | No SSDAT action               | 1     | 0      | 0   | Х    | Repeated START will be transmitted.                                                            |  |

| 18h           | transmitted; ACK has<br>been received                           | No SSDAT action               | 0     | 1      | 0   | x    | STOP condition will be transmitted and SSSTO flag will be reset.                               |  |

|               |                                                                 | No SSDAT action               | 1     | 1      | 0   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |  |

|               | SLA+W has been<br>transmitted; NOT ACK<br>has been received     | Write data byte               | 0     | 0      | 0   | x    | Data byte will be transmitted.                                                                 |  |

|               |                                                                 | No SSDAT action               | 1     | 0      | 0   | х    | Repeated START will be transmitted.                                                            |  |

| 20h           |                                                                 | No SSDAT action               | 0     | 1      | 0   | х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |  |

|               |                                                                 | No SSDAT action               | 1     | 1      | 0   | x    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |  |

|               | Data byte has been<br>transmitted; ACK has<br>been received     | Write data byte               | 0     | 0      | 0   | х    | Data byte will be transmitted.                                                                 |  |

|               |                                                                 | No SSDAT action               | 1     | 0      | 0   | х    | Repeated START will be transmitted.                                                            |  |

| 28h           |                                                                 | No SSDAT action               | 0     | 1      | 0   | х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |  |

|               |                                                                 | No SSDAT action               | 1     | 1      | 0   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |  |

|               | Data byte has been<br>transmitted; NOT ACK<br>has been received | Write data byte               | 0     | 0      | 0   | х    | Data byte will be transmitted.                                                                 |  |

|               |                                                                 | No SSDAT action               | 1     | 0      | 0   | х    | Repeated START will be transmitted.                                                            |  |

| 30h           |                                                                 | No SSDAT action               | 0     | 1      | 0   | x    | STOP condition will be transmitted and SSSTO flag will be reset.                               |  |

|               |                                                                 | No SSDAT action               | 1     | 1      | 0   | х    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |  |

| 20h           | Arbitration lost in<br>SLA+W or data bytes                      | No SSDAT action               | 0     | 0      | 0   | х    | Two-wire bus will be released and not addressed slave mode will be entered.                    |  |

| 38h           |                                                                 | No SSDAT action               | 1     | 0      | 0   | х    | A START condition will be transmitted when the bus becomes free.                               |  |

## Table 83. Status in Master Transmitter Mode

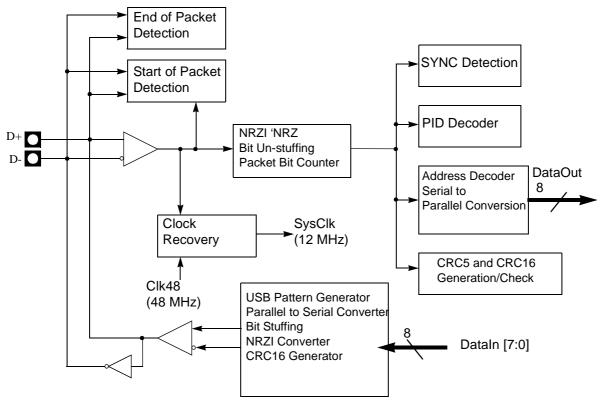

## Serial Interface Engine (SIE)

The SIE performs the following functions:

- NRZI data encoding and decoding.

- Bit stuffing and un-stuffing.

- CRC generation and checking.

- Handshakes.

- TOKEN type identifying.

- Address checking.

- Clock generation (via DPLL).

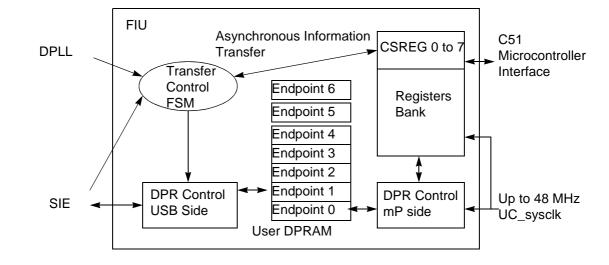

**Function Interface Unit (FIU)**

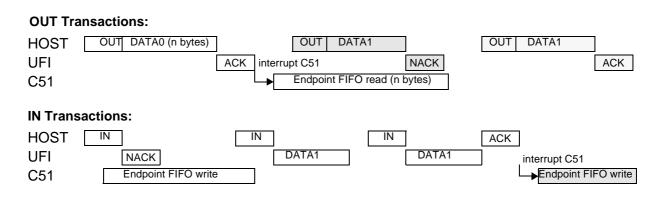

The Function Interface Unit provides the interface between the AT89C5131 and the SIE. It manages transactions at the packet level with minimal intervention from the device firmware, which reads and writes the endpoint FIFOs.

Figure 55. UFI Block Diagram

Figure 56. Minimum Intervention from the USB Device Firmware

## **Control Transactions**

| Sotup Stogo                  | The DIP bit in the LIEDSTAY register will be at 0                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Setup Stage                  | The DIR bit in the UEPSTAX register will be at 0.<br>Receiving Setup packets is the same as receiving Bulk Out packets, except that the<br>RXSETUP bit in the UEPSTAX register is set by the USB controller instead of the<br>RXOUTB0 bit to indicate that an Out packet with a Setup PID has been received on the<br>Control endpoint. When the RXSETUP bit has been set, all the other bits of the UEP-<br>STAX register are cleared and an interrupt is triggered if enabled. |  |  |  |  |

|                              | The firmware has to read the Setup request stored in the Control endpoint FIFO before clearing the RXSETUP bit to free the endpoint FIFO for the next transaction.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Data Stage: Control Endpoint | The data stage management is similar to Bulk management.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Direction                    | A Control endpoint is managed by the USB controller as a full-duplex endpoint: IN and OUT. All other endpoint types are managed as half-duplex endpoint: IN or OUT. The firmware has to specify the control endpoint direction for the data stage using the DIR bit in the UEPSTAX register.<br>The firmware has to use the DIR bit before data IN in order to meet the data-toggle requirements:                                                                                |  |  |  |  |

|                              | <ul> <li>If the data stage consists of INs,<br/>the firmware has to set the DIR bit in the UEPSTAX register before writing into the<br/>FIFO and sending the data by setting to 1 the TXRDY bit in the UEPSTAX register.<br/>The IN transaction is complete when the TXCMPL has been set by the hardware.<br/>The firmware will clear the TXCMPL bit before any other transaction.</li> </ul>                                                                                    |  |  |  |  |

|                              | <ul> <li>If the data stage consists of OUTs,<br/>the firmware has to leave the DIR bit at 0. The RXOUTB0 bit is set by hardware<br/>when a new valid packet has been received on the endpoint. The firmware must<br/>read the data stored into the FIFO and then clear the RXOUTB0 bit to reset the<br/>FIFO and to allow the next transaction.</li> </ul>                                                                                                                       |  |  |  |  |

|                              | To send a STALL handshake, see "STALL Handshake" on page 130.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Status Stage                 | The DIR bit in the UEPSTAX register will be reset at 0 for IN and OUT status stage.                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                              | The status stage management is similar to Bulk management.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                              | <ul> <li>For a Control Write transaction or a No-Data Control transaction, the status stage<br/>consists of a IN Zero Length Packet (see "Bulk/Interrupt IN Transactions in<br/>Standard Mode" on page 125). To send a STALL handshake, see "STALL<br/>Handshake" on page 130.</li> </ul>                                                                                                                                                                                        |  |  |  |  |

|                              | <ul> <li>For a Control Read transaction, the status stage consists of a OUT Zero Length<br/>Packet (see "Bulk/Interrupt OUT Transactions in Standard Mode" on page 123).</li> </ul>                                                                                                                                                                                                                                                                                              |  |  |  |  |

| IPHUSB | IPLUSB | USB Priority Level |

|--------|--------|--------------------|

| 0      | 0      | 0 Lowest           |

| 0      | 1      | 1                  |

| 1      | 0      | 2                  |

| 1      | 1      | 3 Highest          |

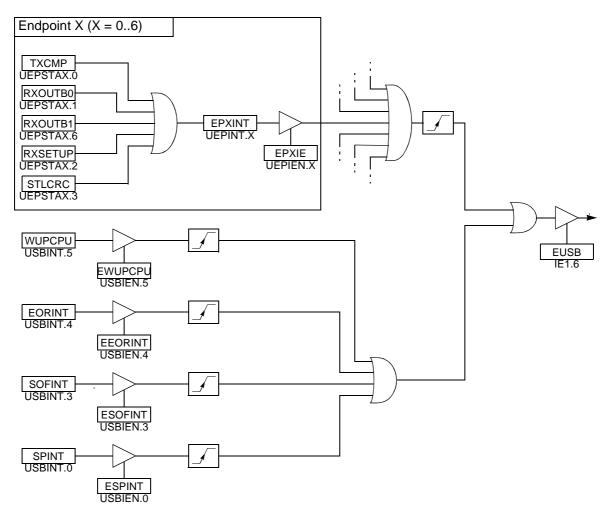

**USB Interrupt Control System** As shown in Figure 68, many events can produce a USB interrupt:

- TXCMPL: Transmitted In Data (see Table 100 on page 142). This bit is set by hardware when the Host accept a In packet.

- RXOUTB0: Received Out Data Bank 0 (see Table 100 on page 142). This bit is set by hardware when an Out packet is accepted by the endpoint and stored in bank 0.

- RXOUTB1: Received Out Data Bank 1 (only for Ping-pong endpoints) (see Table 100 on page 142). This bit is set by hardware when an Out packet is accepted by the endpoint and stored in bank 1.

- RXSETUP: Received Setup (see Table 100 on page 142). This bit is set by hardware when an SETUP packet is accepted by the endpoint.

- STLCRC: STALLED (only for Control, Bulk and Interrupt endpoints) (see Table 100 on page 142). This bit is set by hardware when a STALL handshake has been sent as requested by STALLRQ, and is reset by hardware when a SETUP packet is received.

- SOFINT: Start of Frame Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 139.). This bit is set by hardware when a USB Start of Frame packet has been received.

- WUPCPU: Wake-Up CPU Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 139.). This bit is set by hardware when a USB resume is detected on the USB bus, after a SUSPEND state.

- SPINT: Suspend Interrupt (See "USBIEN Register USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 139.). This bit is set by hardware when a USB suspend is detected on the USB bus.

Figure 68. USB Interrupt Control Block Diagram

Table 106.UEPIEN RegisterUEPIEN (S:C2h)USB Endpoint Interrupt Enable Register

| 7          | 6               | 5                                                                                                                                                      | 4                                                                                                                                                      | 3                                        | 2       | 1       | 0       |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------|---------|---------|--|

| -          | EP6INTE         | EP5INTE                                                                                                                                                | EP4INTE                                                                                                                                                | <b>EP3INTE</b>                           | EP2INTE | EP1INTE | EPOINTE |  |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                                            | Description                                                                                                                                            |                                          |         |         |         |  |

| 7          | -               | Reserved<br>The value rea                                                                                                                              | Reserved<br>The value read from this bit is always 0. Do not set this bit.                                                                             |                                          |         |         |         |  |

| 6          | EP6INTE         | Set this bit to                                                                                                                                        | Endpoint 6 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                          |         |         |         |  |

| 5          | EP5INTE         | Set this bit to                                                                                                                                        | Endpoint 5 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                          |         |         |         |  |

| 4          | EP4INTE         | Set this bit to                                                                                                                                        | Endpoint 4 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                          |         |         |         |  |

| 3          | EP3INTE         | Set this bit to                                                                                                                                        | Endpoint 3 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                          |         |         |         |  |

| 2          | EP2INTE         | Set this bit to                                                                                                                                        |                                                                                                                                                        | ble<br>terrupts for th<br>interrupts for |         |         |         |  |

| 1          | EP1INTE         | Set this bit to                                                                                                                                        | Endpoint 1 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                          |         |         |         |  |

| 0          | EPOINTE         | Endpoint 0 Interrupt Enable<br>Set this bit to enable the interrupts for this endpoint.<br>Clear this bit to disable the interrupts for this endpoint. |                                                                                                                                                        |                                          |         |         |         |  |

Reset Value = 00h

For timing purposes as port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $V_{OH}/V_{OL}$  level occurs.  $I_{OL}/I_{OH} \geq \pm 20$  mA.

## **Ordering Information**

Table 131. Possible Order Entries

| Part Number      | Memory Size (Kbytes) | Supply Voltage | Temperature Range  | Package | Packing            |

|------------------|----------------------|----------------|--------------------|---------|--------------------|

| AT89C5130A-RDTIM | 16                   | 2.7 to 5.5V    | Industrial         | VQFP64  | Tray               |

| AT89C5130A-PUTIM | 16                   | 2.7 to 5.5V    | Industrial         | QFN32   | Tray               |

| AT89C5130A-S3SIM | 16                   | 2.7 to 5.5V    | Industrial         | PLCC52  | Stick              |

| AT89C5131A-RDTIM | 32                   | 2.7 to 5.5V    | Industrial         | VQFP64  | Tray               |

| AT89C5131A-PUTIM | 32                   | 2.7 to 5.5V    | Industrial         | QFN32   | Tray               |

| AT89C5131A-S3SIM | 32                   | 2.7 to 5.5V    | Industrial         | PLCC52  | Stick              |

|                  |                      | •              | ·                  |         |                    |

| AT89C5130A-RDTUM | 16                   | 2.7 to 5.5V    | Industrial & Green | VQFP64  | Tray & Dry<br>Pack |

| AT89C5130A-PUTUM | 16                   | 2.7 to 5.5V    | Industrial & Green | QFN32   | Tray & Dry<br>Pack |

| AT89C5130A-S3SUM | 16                   | 2.7 to 5.5V    | Industrial & Green | PLCC52  | Tray & Dry<br>Pack |

| AT89C5131A-RDTUM | 32                   | 2.7 to 5.5V    | Industrial & Green | VQFP64  | Tray & Dry<br>Pack |

| AT89C5131A-PUTUM | 32                   | 2.7 to 5.5V    | Industrial & Green | QFN32   | Tray & Dry<br>Pack |

| AT89C5131A-S3SUM | 32                   | 2.7 to 5.5V    | Industrial & Green | PLCC52  | Tray & Dry<br>Pack |

Notes: 1. Optional Packing and Package options (please consult Atmel sales representative) -Tape and Reel -Dry Pack -Die form

| Registers                                     | . 43 |

|-----------------------------------------------|------|

| In-System Programming (ISP)                   | 44   |

| Flash Programming and Erasure                 |      |

| Boot Process                                  |      |

| Application-Programming-Interface             |      |

| XROW Bytes                                    |      |

| Hardware Conditions                           |      |

| On-chip Expanded RAM (ERAM)                   | 48   |

| Timer 2                                       | 51   |

| Auto-reload Mode                              |      |

| Programmable Clock Output                     |      |

| Programmable Counter Array (PCA)              | 56   |

| PCA Capture Mode                              |      |

| 16-bit Software Timer/Compare Mode            |      |

| High Speed Output Mode                        |      |

| Pulse Width Modulator Mode                    |      |

| PCA Watchdog Timer                            |      |

| Serial I/O Port                               | 67   |

| Framing Error Detection                       | 67   |

| Automatic Address Recognition                 |      |

| Baud Rate Selection for UART for Mode 1 and 3 | 70   |

| UART Registers                                | 73   |

| Interrupt System                              | 77   |

| Overview                                      | 77   |

| Registers                                     | 78   |

| Interrupt Sources and Vector Addresses        | . 85 |

| Keyboard Interface                            | 86   |

| Introduction                                  | 86   |

| Description                                   | 86   |

| Registers                                     | 87   |

| Programmable LED                              | 90   |

| Serial Peripheral Interface (SPI)             | 91   |

| Features                                      |      |