#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | LED, POR, PWM, WDT                                                         |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 4K x 8                                                                     |

| RAM Size                   | 1.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 52-LCC (J-Lead)                                                            |

| Supplier Device Package    | 52-PLCC (19.15x19.15)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c5131a-s3sim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Description

AT89C5130A/31A-M is a high-performance Flash version of the 80C51 single-chip 8-bit microcontrollers with full speed USB functions.

AT89C5130A/31A-M features a full-speed USB module compatible with the USB specifications Version 1.1 and 2.0. This module integrates the USB transceivers with a 3.3V voltage regulator and the Serial Interface Engine (SIE) with Digital Phase Locked Loop and 48 MHz clock recovery. USB Event detection logic (Reset and Suspend/Resume) and FIFO buffers supporting the mandatory control Endpoint (EP0) and up to 6 versatile Endpoints (EP1/EP2/EP3/EP4/EP5/EP6) with minimum software overhead are also part of the USB module.

AT89C5130A/31A-M retains the features of the Atmel 80C52 with extended Flash capacity (16/32-Kbytes), 256 bytes of internal RAM, a 4-level interrupt system, two 16-bit timer/counters (T0/T1), a full duplex enhanced UART (EUART) and an on-chip oscillator.

In addition, AT89C5130A/31A-M has an on-chip expanded RAM of 1024 bytes (ERAM), a dual data pointer, a 16-bit up/down Timer (T2), a Programmable Counter Array (PCA), up to 4 programmable LED current sources, a programmable hardware watchdog and a power-on reset.

AT89C5130A/31A-M has two software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the timers, the serial ports and the interrupt system are still operating. In the power-down mode the RAM is saved, the peripheral clock is frozen, but the device has full wake-up capability through USB events or external interrupts.

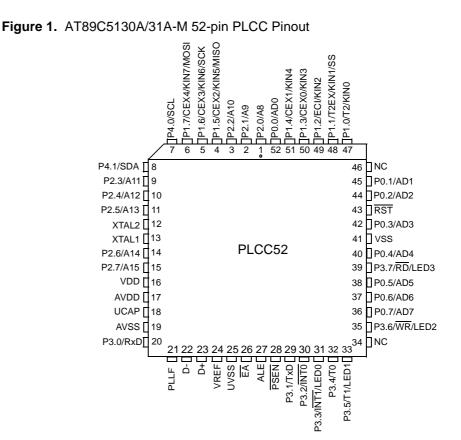

## **Pinout Description**

Pinout

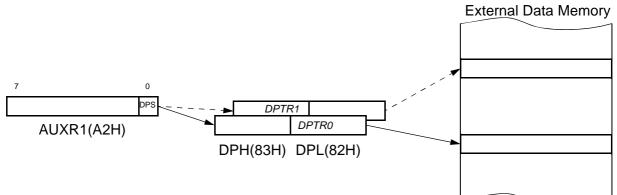

### Dual Data Pointer Register

The additional data pointer can be used to speed up code execution and reduce code size.

The dual DPTR structure is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1.0 (see Table 34) that allows the program code to switch between them (see Figure 10).

### Figure 10. Use of Dual Pointer

Table 34.

AUXR1 Register

AUXR1- Auxiliary Register 1(0A2h)

| 7             | 6               | 5                                                                          | 4                                                                               | 3                   | 2               | 1            | 0 |  |  |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|-----------------|--------------|---|--|--|--|--|--|

| -             | -               | ENBOOT                                                                     | ENBOOT - GF3 0 -                                                                |                     |                 |              |   |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                | Description                                                                     |                     |                 |              |   |  |  |  |  |  |

| 7             | -               | Reserved<br>The value rea                                                  | ad from this bi                                                                 | t is indetermir     | nate. Do not se | et this bit. |   |  |  |  |  |  |

| 6             | -               | Reserved<br>The value rea                                                  | ad from this bi                                                                 | t is indetermir     | nate. Do not se | et this bit. |   |  |  |  |  |  |

| 5             | ENBOOT          | Enable Boot<br>Cleared to dis<br>Set to map th                             | sable boot RC                                                                   | DM.<br>Detween F800 | h - 0FFFFh.     |              |   |  |  |  |  |  |

| 4             | -               | Reserved<br>The value rea                                                  | ad from this bi                                                                 | t is indetermir     | nate. Do not se | et this bit. |   |  |  |  |  |  |

| 3             | GF3             | This bit is a g                                                            | eneral-purpos                                                                   | se user flag.       |                 |              |   |  |  |  |  |  |

| 2             | 0               | Always cleare                                                              | ed.                                                                             |                     |                 |              |   |  |  |  |  |  |

| 1             | -               | Reserved<br>The value rea                                                  | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                     |                 |              |   |  |  |  |  |  |

| 0             | DPS             | Data Pointer Selection<br>Cleared to select DPTR0.<br>Set to select DPTR1. |                                                                                 |                     |                 |              |   |  |  |  |  |  |

| D ()/ )       |                 |                                                                            |                                                                                 |                     |                 |              |   |  |  |  |  |  |

Reset Value = XX[BLJB]X X0X0b

Not bit addressable

a. Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

The other memory spaces (user, extra row, hardware security) are made accessible in the code segment by programming bits FMOD0 and FMOD1 in FCON register in accordance with Table 36. A MOVC instruction is then used for reading these spaces.

Table 36.

FM0 Blocks Select Bits

| FMOD1 | FMOD0 | FM0 Adressable Space      |

|-------|-------|---------------------------|

| 0     | 0     | User (0000h-FFFFh)        |

| 0     | 1     | Extra Row(FF80h-FFFFh)    |

| 1     | 0     | Hardware Security (0000h) |

| 1     | 1     | reserved                  |

**Launching Programming** FPL3:0 bits in FCON register are used to secure the launch of programming. A specific sequence must be written in these bits to unlock the write protection and to launch the programming. This sequence is 5 followed by A. Table 37 summarizes the memory spaces to program according to FMOD1:0 bits.

Table 37.

Programming Spaces

|           |         | Write to |       |           |                                             |

|-----------|---------|----------|-------|-----------|---------------------------------------------|

|           | FPL3:0  | FPS      | FMOD1 | FMOD0     | Operation                                   |

|           | 5       | х        | 0     | 0         | No action                                   |

| User      | А       | х        | 0     | 0         | Write the column latches in user space      |

|           | 5 X 0 1 |          | 1     | No action |                                             |

| Extra Row | А       | х        | 0     | 1         | Write the column latches in extra row space |

| Security  | 5       | х        | 1     | 0         | No action                                   |

| Space     | А       | х        | 1     | 0         | Write the fuse bits space                   |

| Pasaniad  | 5       | х        | 1     | 1         | No action                                   |

| Reserved  | А       | Х        | 1     | 1         | No action                                   |

The Flash memory enters a busy state as soon as programming is launched. In this state, the memory is not available for fetching code. Thus to avoid any erratic execution during programming, the CPU enters Idle mode. Exit is automatically performed at the end of programming.

Note: Interrupts that may occur during programming time must be disabled to avoid any spurious exit of the idle mode.

**Status of the Flash Memory** The bit FBUSY in FCON register is used to indicate the status of programming.

FBUSY is set when programming is in progress.

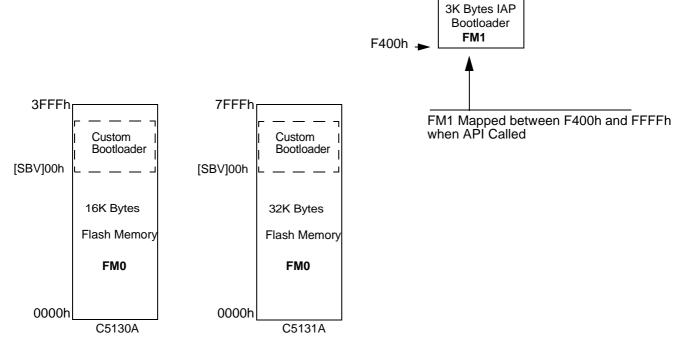

Selecting FM0/FM1 The bit ENBOOT in AUXR1 register is used to choose between FM0 and FM1 mapped up to F800h.

# <u>AMEL</u>

| In-System<br>Programming (ISP)   | <ul> <li>With the implementation of the User Space (FM0) and the Boot Space (FM1) in Flash technology the AT89C5130A/31A-M allows the system engineer the development of applications with a very high level of flexibility. This flexibility is based on the possibility to alter the customer program at any stages of a product's life:</li> <li>Before mounting the chip on the PCB, FM0 flash can be programmed with the application code. FM1 is always preprogrammed by Atmel with a USB bootloader.<sup>(1)</sup></li> <li>Once the chip is mounted on the PCB, it can be programmed by serial mode via the USB bus.</li> <li>Note: 1. The user can also program his own bootloader in FM1.</li> <li>This ISP allows code modification over the total lifetime of the product.</li> <li>Besides the default Bootloaders Atmel provide customers all the needed Application-Programming-Interfaces (API) which are needed for the ISP. The API are located in the Boot memory.</li> <li>This allow the customer to have a full use of the 32-Kbyte user memory.</li> </ul> |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash Programming and<br>Erasure | <ul> <li>There are three methods for programming the Flash memory:</li> <li>The Atmel bootloader located in FM1 is activated by the application. Low level API routines (located in FM1)will be used to program FM0. The interface used for serial downloading to FM0 is the USB. API can be called also by user's bootloader located in FM0 at [SBV]00h.</li> <li>A further method exist in activating the Atmel boot loader by hardware activation. See the Section "Hardware Registers".</li> <li>The FM0 can be programmed also by the parallel mode using a programmer.</li> <li>Figure 20. Flash Memory Mapping</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# 44 AT89C5130A/31A-M

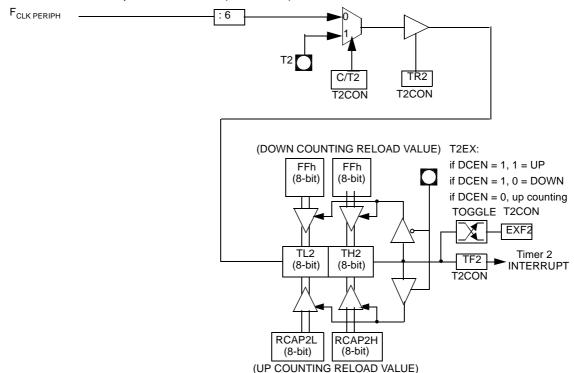

Figure 23. Auto-reload Mode Up/Down Counter (DCEN = 1)

### Programmable Clock Output

In the Clock-out mode, Timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 24). The input clock increments TL2 at frequency  $F_{CLK PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The following formula gives the Clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers

$$Clock - OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the Clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

# AT89C5130A/31A-M

### Table 65. IPH0 Register

IPH0 - Interrupt Priority High Register (B7h)

| 7             | errupt Priorii<br>6 | 5                          | -                                                                                                                                                  | (B711)<br>4 | 3                   | 2              | 1             | 0    |  |

|---------------|---------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|----------------|---------------|------|--|

| -             | PPCH                | PT2H                       | P                                                                                                                                                  | SH          | PT1H                | PX1H           | РТОН          | PX0H |  |

| Bit<br>Number | Bit<br>Mnemonic     | Descript                   | ion                                                                                                                                                |             |                     |                |               |      |  |

| 7             | -                   | Reserved<br>The value      |                                                                                                                                                    | m this b    | oit is indeterm     | ninate. Do not | set this bit. |      |  |

| 6             | PPCH                | 0<br>0<br>1                | rrupt Pri<br>PPCL<br>0<br>1<br>0<br>1                                                                                                              |             | <u>/ Level</u><br>t |                |               |      |  |

| 5             | PT2H                | <u>PT2H</u><br>0<br>0<br>1 | <b>Dverflow</b><br>PT2L<br>0<br>1<br>0<br>1                                                                                                        |             |                     | ligh bit       |               |      |  |

| 4             | PSH                 | 0<br>0<br>1                | o <b>rt Priorit</b><br>PSL<br>0<br>1<br>0<br>1                                                                                                     |             | <u>/ Level</u><br>t |                |               |      |  |

| 3             | PT1H                | <u>PT1H</u><br>0<br>0<br>1 | <b>Dverflow</b><br><u>PT1L</u><br>0<br>1<br>0<br>1                                                                                                 |             |                     | ligh bit       |               |      |  |

| 2             | PX1H                | <u>PX1H</u><br>0<br>0<br>1 | interrup<br>PX1L<br>0<br>1<br>0<br>1                                                                                                               |             |                     |                |               |      |  |

| 1             | РТОН                | <u>PT0H</u><br>0<br>0<br>1 | Timer 0 overflow interrupt Priority High bit         PT0H       PT0L       Priority Level         0       0       Lowest         0       1       0 |             |                     |                |               |      |  |

| 0             | РХОН                | <u>PX0H</u><br>0<br>0<br>1 | <b>interrup</b><br>PXOL<br>0<br>1<br>0<br>1                                                                                                        |             |                     |                |               |      |  |

Reset Value = X000 0000b Not bit addressable

### **Functional Description**

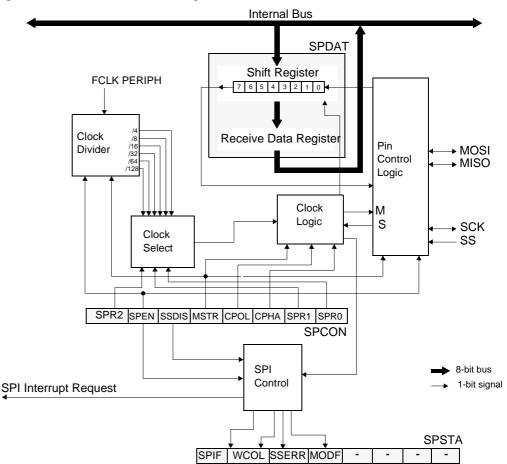

Figure 40 shows a detailed structure of the SPI module.

Figure 40. SPI Module Block Diagram

#### **Operating Modes**

The Serial Peripheral Interface can be configured as one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI module is made through one register:

The Serial Peripheral CONtrol register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 41).

|                |                                                                    | Application Software Response          |     |       |     |    |                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------|----------------------------------------|-----|-------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status         |                                                                    | To/from SSDAT                          |     | To SS | CON |    |                                                                                                                                                                                      |

| Code<br>(SSCS) | Status of the 2-wire bus and 2-wire hardware                       |                                        | STA | STO   | SI  | AA | Next Action Taken By 2-wire Software                                                                                                                                                 |

| COL            | Own SLA+W has been                                                 | No SSDAT action or                     | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 60h            | received; ACK has been<br>returned                                 | No SSDAT action                        | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

|                | Arbitration lost in SLA+R/W as master; own SLA+W has been          | No SSDAT action or                     | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 68h            | received; ACK has been returned                                    | No SSDAT action                        | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| 701            | General call address has been                                      | No SSDAT action or                     | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 70h            | received; ACK has been<br>returned                                 | No SSDAT action                        | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| 701            | Arbitration lost in SLA+R/W as<br>master; general call address     | No SSDAT action or                     | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 78h            | has been received; ACK has<br>been returned                        | No SSDAT action                        | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

|                | Previously addressed with<br>own SLA+W; data has been              | No SSDAT action or                     | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 80h            | received; ACK has been returned                                    | No SSDAT action                        | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

|                |                                                                    | Dood data buto or                      | 0   | 0     | 0   | 0  | Switched to the not addressed slave mode; no recognition of own SLA or GCA                                                                                                           |

|                |                                                                    | Read data byte or<br>Read data byte or | 0   | 0     | 0   | 1  | Switched to the not addressed slave mode; own SLA will be recognised; GCA will be recognised if                                                                                      |

|                | Previously addressed with                                          |                                        | Ũ   | Ŭ     | Ū   |    | GC=logic 1<br>Switched to the not addressed slave mode; no                                                                                                                           |

| 88h            | own SLA+W; data has been<br>received; NOT ACK has been<br>returned | Read data byte or                      | 1   | 0     | 0   | 0  | recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                                                                 |

|                |                                                                    | Read data byte                         | 1   | 0     | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |

|                | Previously addressed with general call; data has been              | Read data byte or                      | х   | 0     | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 90h            | received; ACK has been returned                                    | Read data byte                         | х   | 0     | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

Table 85. Status in Slave Receiver Mode

### Table 85. Status in Slave Receiver Mode (Continued)

|                |                                                                                                        | Application S                          | oftware | Respo  |        |        |                                                                                                                                                                                                   |

|----------------|--------------------------------------------------------------------------------------------------------|----------------------------------------|---------|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status         |                                                                                                        | To/from SSDAT To SSCON                 |         |        |        |        |                                                                                                                                                                                                   |

| Code<br>(SSCS) | Status of the 2-wire bus and 2-wire hardware                                                           |                                        | STA     | STO    | SI     | AA     | Next Action Taken By 2-wire Software                                                                                                                                                              |

|                |                                                                                                        | Read data byte or<br>Read data byte or | 0<br>0  | 0<br>0 | 0<br>0 | 0<br>1 | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1 |

| 98h            | 98h Previously addressed with<br>general call; data has been<br>received; NOT ACK has been<br>returned | Read data byte or                      | 1       | 0      | 0      | 0      | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                              |

|                |                                                                                                        | Read data byte                         | 1       | 0      | 0      | 1      | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free              |

|                |                                                                                                        | No SSDAT action or                     | 0       | 0      | 0      | 0      | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA<br>Switched to the not addressed slave mode; own                                                                    |

|                |                                                                                                        | No SSDAT action or                     | 0       | 0      | 0      | 1      | SLA will be recognised; GCA will be recognised if GC=logic 1                                                                                                                                      |

| A0h            | A STOP condition or repeated<br>START condition has been<br>received while still addressed<br>as slave | No SSDAT action or                     | 1       | 0      | 0      | 0      | Switched to the not addressed slave mode; no<br>recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                              |

|                |                                                                                                        | No SSDAT action                        | 1       | 0      | 0      | 1      | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free              |

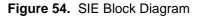

### Serial Interface Engine (SIE)

The SIE performs the following functions:

- NRZI data encoding and decoding.

- Bit stuffing and un-stuffing.

- CRC generation and checking.

- Handshakes.

- TOKEN type identifying.

- Address checking.

- Clock generation (via DPLL).

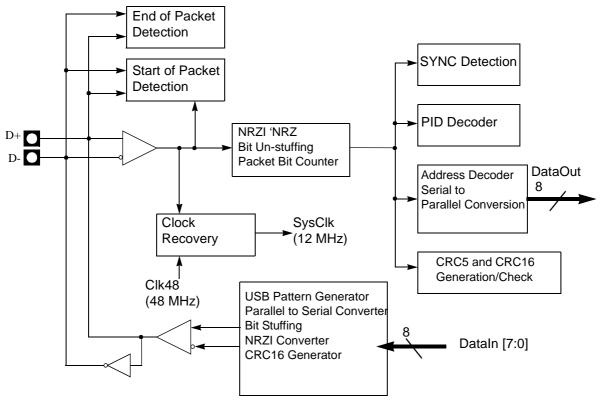

Bulk/Interrupt OUT Transactions in Ping-pong Mode Figure 60. Bulk/Interrupt OUT Transactions in Ping-pong Mode

An endpoint will be first enabled and configured before being able to receive Bulk or Interrupt packets.

When a valid OUT packet is received on the endpoint bank 0, the RXOUTB0 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware has to select the corresponding endpoint, store the number of data bytes by reading the UBYCTLX and UBYCTHX registers. If the received packet is a ZLP (Zero Length Packet), the UBYCTLX and UBYCTHX register values are equal to 0 and no data has to be read.

When all the endpoint FIFO bytes have been read, the firmware will clear the RXOUB0 bit to allow the USB controller to accept the next OUT packet on the endpoint bank 0. This action switches the endpoint bank 0 and 1. Until the RXOUTB0 bit has been cleared by the firmware, the USB controller will answer a NAK handshake for each OUT requests on the bank 0 endpoint FIFO.

When a new valid OUT packet is received on the endpoint bank 1, the RXOUTB1 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware empties the bank 1 endpoint FIFO before clearing the RXOUTB1 bit. Until the RXOUTB1 bit has been cleared by the firmware, the USB controller will answer a NAK handshake for each OUT requests on the bank 1 endpoint FIFO.

The RXOUTB0 and RXOUTB1 bits are alternatively set by the USB controller at each new valid packet receipt.

The firmware has to clear one of these two bits after having read all the data FIFO to allow a new valid packet to be stored in the corresponding bank.

A NAK handshake is sent by the USB controller only if the banks 0 and 1 has not been released by the firmware.

If the Host sends more bytes than supported by the endpoint FIFO, the overflow data won't be stored, but the USB controller will consider that the packet is valid if the CRC is correct.

### **Isochronous Transactions**

| Isochronous OUT<br>Transactions in Standard  | An endpoint will be first enabled and configured before being able to receive Isochro-<br>nous packets.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Mode                                         | When a OUT packet is received on an endpoint, the RXOUTB0 bit is set by the USE controller. This triggers an interrupt if enabled. The firmware has to select the corre sponding endpoint, store the number of data bytes by reading the UBYCTLX and UBYCTHX registers. If the received packet is a ZLP (Zero Length Packet), the UBYCTLX and UBYCTLX and UBYCTHX register values are equal to 0 and no data has to be read. |  |  |  |  |  |  |

|                                              | The STLCRC bit in the UEPSTAX register is set by the USB controller if the pack<br>stored in FIFO has a corrupted CRC. This bit is updated after each new packet receipt                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                              | When all the endpoint FIFO bytes have been read, the firmware will clear the RXOUTB0 bit to allow the USB controller to store the next OUT packet data into the endpoint FIFO. Until the RXOUTB0 bit has been cleared by the firmware, the data sent by the Host at each OUT transaction will be lost.                                                                                                                       |  |  |  |  |  |  |

|                                              | If the RXOUTB0 bit is cleared while the Host is sending data, the USB controller will store only the remaining bytes into the FIFO.                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                                              | If the Host sends more bytes than supported by the endpoint FIFO, the overflow data won't be stored, but the USB controller will consider that the packet is valid if the CRC is correct.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Isochronous OUT<br>Transactions in Ping-pong | An endpoint will be first enabled and configured before being able to receive Isochro-<br>nous packets.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Mode                                         | When a OUT packet is received on the endpoint bank 0, the RXOUTB0 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware has to select the corresponding endpoint, store the number of data bytes by reading the UBYCTLX and UBYCTHX registers. If the received packet is a ZLP (Zero Length Packet), the UBYCTLX and UBYCTLX register values are equal to 0 and no data has to be read.      |  |  |  |  |  |  |

|                                              | The STLCRC bit in the UEPSTAX register is set by the USB controller if the packet stored in FIFO has a corrupted CRC. This bit is updated after each new packet receipt.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                              | When all the endpoint FIFO bytes have been read, the firmware will clear the RXOUB0 bit to allow the USB controller to store the next OUT packet data into the endpoint FIFO bank 0. This action switches the endpoint bank 0 and 1. Until the RXOUTB0 bit has been cleared by the firmware, the data sent by the Host on the bank 0 endpoint FIFO will be lost.                                                             |  |  |  |  |  |  |

|                                              | If the RXOUTB0 bit is cleared while the Host is sending data on the endpoint bank 0, the USB controller will store only the remaining bytes into the FIFO.                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                              | When a new OUT packet is received on the endpoint bank 1, the RXOUTB1 bit is set by the USB controller. This triggers an interrupt if enabled. The firmware empties the bank 1 endpoint FIFO before clearing the RXOUTB1 bit. Until the RXOUTB1 bit has been cleared by the firmware, the data sent by the Host on the bank 1 endpoint FIFO will be lost.                                                                    |  |  |  |  |  |  |

|                                              | The RXOUTB0 and RXOUTB1 bits are alternatively set by the USB controller at each new packet receipt.                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                              | The firmware has to clear one of these two bits after having read all the data FIFO to allow a new packet to be stored in the corresponding bank.                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

### **USB** Registers

Table 94.USBCON RegisterUSBCON (S:BCh)USB Global Control Register

| 7          | 6         |     | 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                       |                  |               |                            |              |  |  |

|------------|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|---------------|----------------------------|--------------|--|--|

| USBE       | SUSPCLK   | SDR | MWUP DETACH UPRSM RMWUPE CONFG FADDE                                                                                                                                                                                                                                                                                                                                                                                            |                                                                       |                  |               |                            |              |  |  |

| Bit Number | Bit Mnemo | nic | Descri                                                                                                                                                                                                                                                                                                                                                                                                                          | ption                                                                 |                  |               |                            |              |  |  |

| 7          | USBE      |     | Clear th                                                                                                                                                                                                                                                                                                                                                                                                                        | n <b>able</b><br>bit to enable<br>his bit to disab<br>iver an to disa | le and reset the | he USB contro |                            | e the USB    |  |  |

| 6          | SUSPCL    | .K  | Suspend USB Clock<br>Set this bit to disable the 48 MHz clock input (Resume Detection is still<br>active).<br>Clear this bit to enable the 48 MHz clock input.                                                                                                                                                                                                                                                                  |                                                                       |                  |               |                            |              |  |  |

| 5          | SDRMW     | JP  | Send Remote Wake Up<br>Set this bit to force an external interrupt on the USB controller for Remote<br>Wake UP purpose.<br>An upstream resume is send only if the bit RMWUPE is set, all USB clock<br>are enabled AND the USB bus was in SUSPEND state for at least 5 ms.<br>See UPRSM below.<br>This bit is cleared by software.                                                                                               |                                                                       |                  |               |                            |              |  |  |

| 4          | DETACI    | Η   | Set this floating                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Command</b><br>bit to simulate<br>state.<br>his bit to maint       |                  |               | . The V <sub>REF</sub> pin | is then in a |  |  |

| 3          | UPRSN     | 1   | This bit<br>is enab                                                                                                                                                                                                                                                                                                                                                                                                             | am Resume (<br>is set by hard<br>led.<br>is cleared by                | ware when SI     |               |                            |              |  |  |

| 2          | RMWUP     | Έ   | Remote Wake-Up Enable<br>Set this bit to enabled request an upstream resume signaling to the host<br>Clear this bit otherwise.<br>Note: Do not set this bit if the host has not set the<br>DEVICE_REMOTE_WAKEUP feature for the device.                                                                                                                                                                                         |                                                                       |                  |               |                            |              |  |  |

| 1          | CONFO     | 6   | <b>Configured</b><br>This bit will be set by the device firmware after a SET_CONFIGURATION request with a non-zero value has been correctly processed.<br>It will be cleared by the device firmware when a SET_CONFIGURATION request with a zero value is received. It is cleared by hardware on hardware reset or when an USB reset is detected on the bus (SE0 state for at least 3: Full Speed bit times: typically 2.7 μs). |                                                                       |                  |               |                            |              |  |  |

| 0          | FADDEI    | N   | Function Address Enable<br>This bit will be set by the device firmware after a successful status phase of<br>a SET_ADDRESS transaction.<br>It will not be cleared afterwards by the device firmware. It is cleared by<br>hardware on hardware reset or when an USB reset is received (see above).<br>When this bit is cleared, the default function address is used (0).                                                        |                                                                       |                  |               |                            |              |  |  |

Table 96.USBIEN RegisterUSBIEN (S:BEh)USB Global Interrupt Enable Register

| 7          | 6          | 5                                     | 4                                                                                                                                                                                                                                                                 | 3               | 2             | 1              | 0      |  |  |  |

|------------|------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|----------------|--------|--|--|--|

| -          | -          | EWUPCPU                               | EEORINT                                                                                                                                                                                                                                                           | ESOFINT         | -             | -              | ESPINT |  |  |  |

| Bit Number | Bit Mnemor | nic Descript                          | ion                                                                                                                                                                                                                                                               |                 |               |                |        |  |  |  |

| 7-6        | -          |                                       | <b>Reserved</b><br>The value read from these bits is always 0. Do not set these bits.                                                                                                                                                                             |                 |               |                |        |  |  |  |

| 5          | EWUPCP     | U Set this b<br>USBIEN                | Enable Wake Up CPU Interrupt<br>Set this bit to enable Wake Up CPU Interrupt. (See "USBIEN Register<br>USBIEN (S:BEh) USB Global Interrupt Enable Register" on page 139.)<br>Clear this bit to disable Wake Up CPU Interrupt.                                     |                 |               |                |        |  |  |  |

| 4          | EEORIN     | Set this b<br>(S:BEh) U<br>after rese | Enable End Of Reset Interrupt<br>Set this bit to enable End Of Reset Interrupt. (See "USBIEN Register USBIEN<br>(S:BEh) USB Global Interrupt Enable Register" on page 139.). This bit is set<br>after reset.<br>Clear this bit to disable End Of Reset Interrupt. |                 |               |                |        |  |  |  |

| 3          | ESOFINT    | Set this b<br>USB Glob                | <b>Enable SOF Interrupt</b><br>Set this bit to enable SOF Interrupt. (See "USBIEN Register USBIEN (S:BEh)<br>USB Global Interrupt Enable Register" on page 139.).<br>Clear this bit to disable SOF Interrupt.                                                     |                 |               |                |        |  |  |  |

| 2          | -          | Reserved                              | 4                                                                                                                                                                                                                                                                 |                 |               |                |        |  |  |  |

| 1          | -          | The value                             | e read from the                                                                                                                                                                                                                                                   | ese bits is alw | ays 0. Do not | set these bits |        |  |  |  |

| 0          | ESPINT     | Set this b<br>(S:BEh) l               | Enable Suspend Interrupt<br>Set this bit to enable Suspend Interrupts (see the "USBIEN Register USBIEN<br>(S:BEh) USB Global Interrupt Enable Register" on page 139).<br>Clear this bit to disable Suspend Interrupts.                                            |                 |               |                |        |  |  |  |

Reset Value = 10h

**Table 97.** USBADDR RegisterUSBADDR (S:C6h)USB Address Register

| 7          | 6               | 5 4 3 2 1 0                        |                                                                                                                                                                                                          |       |       |       |       |  |  |  |  |

|------------|-----------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|--|

| FEN        | UADD6           | UADD5                              | UADD4                                                                                                                                                                                                    | UADD3 | UADD2 | UADD1 | UADD0 |  |  |  |  |

| Bit Number | Bit<br>Mnemonic | Description                        | Description                                                                                                                                                                                              |       |       |       |       |  |  |  |  |

| 7          | FEN             | Set this bit to                    | Function Enable<br>Set this bit to enable the address filtering function.<br>Cleared this bit to disable the function.                                                                                   |       |       |       |       |  |  |  |  |

| 6-0        | UADD[6:0]       | This field con<br>It will be writt | <b>USB Address</b><br>This field contains the default address (0) after power-up or USB bus reset.<br>It will be written with the value set by a SET_ADDRESS request received by the<br>device firmware. |       |       |       |       |  |  |  |  |

**Table 98.** UEPNUM RegisterUEPNUM (S:C7h)USB Endpoint Number

| 7          | 6         | 5                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3      | 2      | 1      | 0      |  |

|------------|-----------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--|

| -          | -         | -                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EPNUM3 | EPNUM2 | EPNUM1 | EPNUM0 |  |

| Bit Number | Bit Mnemo | nic Descrip                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |        |        |        |  |

| 7-4        | -         |                                                                               | Reserved<br>The value read from these bits is always 0. Do not set these bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |        |        |        |  |

| 3-0        | EPNUM[3   | :0] Set this<br>reading<br>Endpoin<br>Low Reg<br>USB En<br>Count H<br>(S:C7h) | Endpoint Number<br>Set this field with the number of the endpoint which will be accessed when<br>reading or writing to, UEPDATX Register UEPDATX (S:CFh) USB FIFO Data<br>Endpoint X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h) USB<br>Endpoint Number), UBYCTLX Register UBYCTLX (S:E2h) USB Byte Count<br>Low Register X (X = EPNUM set in UEPNUM Register UEPNUM (S:C7h)<br>USB Endpoint Number), UBYCTHX Register UBYCTHX (S:E3h) USB Byte<br>Count High Register X (X = EPNUM set in UEPNUM Register UEPNUM<br>(S:C7h) USB Endpoint Number) or UEPCONX Register UEPCONX (S:D4h)<br>USB Endpoint X Control Register. This value can be 0, 1, 2, 3, 4, 5 or 6. |        |        |        |        |  |

Table 104.UEPRST RegisterUEPRST (S:D5h)USB Endpoint FIFO Reset Register

| 7          | 6               | 5                         | 4                                                                        | 3             | 2              | 1                                              | 0      |  |

|------------|-----------------|---------------------------|--------------------------------------------------------------------------|---------------|----------------|------------------------------------------------|--------|--|

| -          | EP6RST          | EP5RST                    | EP4RST                                                                   | EP3RST        | EP2RST         | EP1RST                                         | EPORST |  |

| Bit Number | Bit<br>Mnemonic | Description               |                                                                          |               |                |                                                |        |  |

| 7          | -               | Reserved<br>The value rea | eserved<br>ne value read from this bit is always 0. Do not set this bit. |               |                |                                                |        |  |

| 6          | EP6RST          | hardware res              | nd reset the e<br>set or when ar                                         | i USB bus res | et has been re | her operation,<br>eceived.<br>d start using th | ·      |  |

| 5          | EP5RST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th |        |  |

| 4          | EP4RST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th | •      |  |

| 3          | EP3RST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th | •      |  |

| 2          | EP2RST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th |        |  |

| 1          | EP1RST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th |        |  |

| 0          | EPORST          | hardware res              | nd reset the e<br>set or when ar                                         | uUSB bus res  | et has been re | her operation,<br>eceived.<br>d start using th | •      |  |

**Table 107.**UFNUMH RegisterUFNUMH (S:BBh, read-only)USB Frame Number High Register

| 7             | 6               | 5                                                  | 4                                                                                                                                                                                                                                                                                              | 3                                | 2                                              | 1                                                                            | 0                       |  |

|---------------|-----------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------------|------------------------------------------------------------------------------|-------------------------|--|

| -             | -               | CRCOK                                              | CRCERR                                                                                                                                                                                                                                                                                         | -                                | FNUM10                                         | FNUM9                                                                        | FNUM8                   |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                        |                                                                                                                                                                                                                                                                                                |                                  |                                                |                                                                              |                         |  |

| 5             | CRCOK           | This bit is set<br>is received w<br>This bit is up | Frame Number CRC OK<br>This bit is set by hardware when a new Frame Number in Start of Frame Packet<br>s received without CRC error.<br>This bit is updated after every Start of Frame packet receipt.<br>mportant note: the Start of Frame interrupt is generated just after the PID receipt. |                                  |                                                |                                                                              |                         |  |

| 4             | CRCERR          | This bit is se<br>packet is rec<br>This bit is up  | Frame Number CRC Error<br>This bit is set by hardware when a corrupted Frame Number in Start of Frame<br>packet is received.<br>This bit is updated after every Start of Frame packet receipt.<br>Important note: the Start of Frame interrupt is generated just after the PID receipt.        |                                  |                                                |                                                                              |                         |  |

| 3             | -               | Reserved<br>The value rea                          | ad from this b                                                                                                                                                                                                                                                                                 | it is always 0.                  | Do not set thi                                 | s bit.                                                                       |                         |  |

| 2-0           | FNUM[10:8]      | Register UFN<br>page 148). It<br>"USBIEN Re        | are the upper<br>NUML (S:BAh<br>is provided in<br>gister USBIEN                                                                                                                                                                                                                                | , read-only) U<br>the last recei | SB Frame Nu<br>ved SOF pack<br>3 Global Interr | umber (see th<br>mber Low Reg<br>tet (see SOFII<br>rupt Enable Re<br>teived. | gister" on<br>NT in the |  |

Reset Value = 00h

**Table 108.**UFNUML RegisterUFNUML (S:BAh, read-only)USB Frame Number Low Register

| 7          | 6               | 5           | 4              | 3     | 2                             | 1     | 0     |

|------------|-----------------|-------------|----------------|-------|-------------------------------|-------|-------|

| FNUM7      | FNUM6           | FNUM5       | FNUM4          | FNUM3 | FNUM2                         | FNUM1 | FNUM0 |

| Bit Number | Bit<br>Mnemonic | Description |                |       |                               |       |       |

| 7 - 0      | FNUM[7:0]       |             | re the lower 8 |       | -bit Frame Nu<br>ISB Frame Nu |       |       |

# ONCE Mode (ON Chip Emulation)

The ONCE mode facilitates testing and debugging of systems using AT89C5130A/31A-M without removing the circuit from the board. The ONCE mode is invoked by driving certain pins of the AT89C5130A/31A-M; the following sequence must be exercised:

- Pull ALE low while the device is in reset (RST high) and PSEN is high.

- Hold ALE low as RST is deactivated.

While the AT89C5130A/31A-M is in ONCE mode, an emulator or test CPU can be used to drive the circuit Table 113 shows the status of the port pins during ONCE mode.

Normal operation is restored when normal reset is applied.

Table 113. External Pin Status during ONCE Mode

| ALE             | PSEN            | Port 0 | Port 1          | Port 2          | Port 3          | Port I2 | XTAL1/2 |

|-----------------|-----------------|--------|-----------------|-----------------|-----------------|---------|---------|

| Weak<br>pull-up | Weak<br>pull-up | Float  | Weak<br>pull-up | Weak<br>pull-up | Weak<br>pull-up | Float   | Active  |

| Reduced EMI Mode               | 159   |

|--------------------------------|-------|

| ONCE Mode (ON Chip Emulation)  | 158   |

|                                | 101   |

| WDT During Power-down and Idle |       |

| Using the WDT                  |       |

| Hardware Watchdog Timer        | 156   |

| Registers                      | 155   |

| Power-down Mode                |       |

| Idle Mode                      |       |

| Power Management               |       |

| Description                    | 101   |

|                                |       |

| Power Monitor                  | 151   |

| Reset Output                   | 150   |

| Reset Input                    |       |

| Introduction                   |       |

| Reset                          |       |

|                                |       |

| USB Registers                  | . 137 |

| USB Interrupt System           | 134   |

| Detach Simulation              |       |

| Suspend/Resume Management      |       |

| Miscellaneous                  |       |

| Isochronous Transactions       |       |

| Control Transactions           |       |

| Bulk/Interrupt Transactions    |       |

| Read/Write Data FIFO           |       |

| Configuration                  |       |

| Description                    |       |

| USB Controller                 | 117   |

| Registers                      | . 115 |

| Notes                          |       |

| Description                    |       |

| Two Wire Interface (TWI)       |       |

|                                |       |

| Functional Description         |       |

| Signal Description             | 91    |