#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 2.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-LQFP                                                                      |

| Supplier Device Package    | 44-VQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc03c-rlrim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | GND  | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TESTI    | I    | Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VCC      |      | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VAREF    |      | Reference Voltage for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAGND    |      | Reference Ground for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.0:7   | I/O  | <b>Port 0:</b><br>Is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in this state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pull-ups when emitting 1's.<br>Port 0 also outputs the code Bytes during program validation. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.0:7   | I/O  | Port 1:<br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins can be used for digital input/output or as analog inputs for<br>the Analog Digital Converter (ADC). Port 1 pins that have 1's written to them are pulled high by the internal pull-up transistors<br>and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled low externally will be the source of current<br>(IL), see section "Electrical Characteristic") because of the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups are disconnected).<br>As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA external clock input and<br>the PCA module I/O.<br>P1.0/AN0/T2<br>Analog input channel 0,<br>External clock input for Timer/counter2.<br>P1.1/AN1/T2EX<br>Analog input channel 1,<br>Trigger input for Timer/counter2.<br>P1.2/AN2/ECI<br>Analog input channel 2,<br>PCA external clock input.<br>P1.3/AN3/CEX0<br>Analog input channel 3,<br>PCA module 0 Entry of input/PWM output.<br>P1.4/AN4/CEX1<br>Analog input channel 4,<br>PCA module 1 Entry of input/PWM output.<br>P1.5/AN5/CEX2<br>Analog input channel 5,<br>PCA. Module 1 Entry of input/PWM output.<br>P1.5/ANS/CEX3<br>Analog input channel 6,<br>PCA module 2 Entry of input/PWM output. |

|          |      | P1.7/AN7/CEX4<br>Analog input channel 7,<br>PCA module 4 Entry ot input/PWM output.<br>Port 1 receives the low-order address byte during EPROM programming and program verification.<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.0:7   | I/O  | <b>Port 2:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups. Port 2 emits the high-order address byte during accesses to the external Program Memory and during accesses to external Data Memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1's. During accesses to external Data Memory that use 8 bit addresses (MOVX @Ri), Port 2 transmits the contents of the P2 special function register. It also receives high-order addresses and control signals during program validation. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# AT89C51CC03

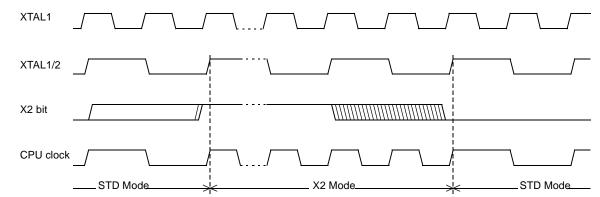

Figure 6. Mode Switching Waveforms

Note: In order to prevent any incorrect operation while operating in the X2 mode, users must be aware that all peripherals using the clock frequency as a time reference (UART, timers...) will have their time reference divided by two. For example a free running timer generating an interrupt every 20 ms will then generate an interrupt every 10 ms. A UART with a 4800 baud rate will have a 9600 baud rate.

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                     |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-2           | XRS1-0          | ERAM size:Accessible size of the ERAMXRS 2:0ERAM size000256 Bytes001512 Bytes010768 Bytes0111024 Bytes1001792 Bytes1012048 Bytes (default configuration after reset)110Reserved111Reserved      |

| 1             | EXTRAM          | Internal/External RAM (00h - FFh)<br>access using MOVX @ Ri/@ DPTR<br>0 - Internal ERAM access using MOVX @ Ri/@ DPTR.<br>1 - External data memory access.                                      |

| 0             | A0              | <b>Disable/Enable ALE)</b><br>0 - ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if X2<br>mode is used)<br>1 - ALE is active only during a MOVX or MOVC instruction. |

Reset Value = X001 0100b Not bit addressable

### Table 8. AUXR1 Register

AUXR1 (S:A2h) Auxiliary Control Register 1

| 7             | 6               | 5                                       | 4                                                                                                                       | 3                                  | 2              | 1               | 0           |  |

|---------------|-----------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|-----------------|-------------|--|

| -             | -               | ENBOOT                                  | -                                                                                                                       | GF3                                | 0              | -               | DPS         |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                             |                                                                                                                         |                                    |                |                 |             |  |

| 7-6           | -               | <b>Reserved</b><br>The value rea        | ad from these                                                                                                           | e bits is indeter                  | minate. Do no  | ot set these bi | ts.         |  |

| 5             | ENBOOT          | Set this bit fo                         | Enable Boot Flash<br>Set this bit for map the boot Flash between F800h -FFFFh<br>Clear this bit for disable boot Flash. |                                    |                |                 |             |  |

| 4             | -               | Reserved<br>The value rea               | ad from this b                                                                                                          | it is indetermi                    | nate. Do not s | et this bit.    |             |  |

| 3             | GF3             | General-pur                             | pose Flag 3                                                                                                             |                                    |                |                 |             |  |

| 2             | 0               | Always Zero<br>This bit is stu<br>flag. |                                                                                                                         | to allow INC A                     | UXR1 instruct  | tion without af | fecting GF3 |  |

| 1             | -               | Reserved fo                             | r Data Pointe                                                                                                           | er Extension.                      |                |                 |             |  |

| 0             | DPS             |                                         | second dual                                                                                                             | data pointer: I<br>ata pointer: DF |                |                 |             |  |

Reset Value = XXXX 00X0b

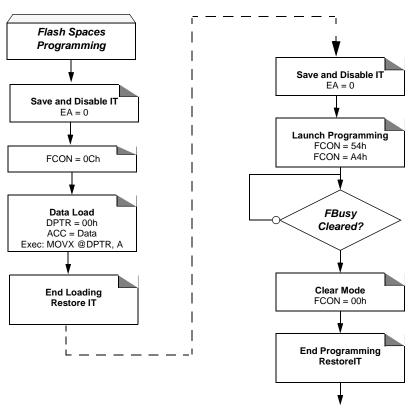

Figure 27. Hardware Programming Procedure

#### Reset the Column Latches

An automatic reset of the column latches is performed after a successful Flash write sequence. User can also reset the column latches manually, for instance to reload the column latches before writing the Flash. The following procedure is summarized below.

- Save and disable the interrupts.

- Launch the reset by writing the data sequence 56h followed by A6h in FCON register (only from FM1).

- Restore the interrupts.

#### **Error Reports**

Flash Programming Sequence Errors

*uence* When a wrong sequence is detected, the SEQERR bit in FSTA register is set. Possible wrong sequence are :

- MOV FCON, 5xh instruction not immediately followed by a MOV FCON, Ax instruction.

- A write Flash sequence is launched while no data were loaded in the column latches

The SEQERR bit can be cleared

- By software

- By hardware when a correct programming sequence is completed

When multiple pages are written into the Flash, the user should check FSTA for errors after each write page sequences, not only at the end of the multiple write pages.

52 AT89C51CC03

# AT89C51CC03

## Hardware Security Byte

Table 24.

Hardware Security Byte

| 7             | 6               | 5                         | 4                                                                                              | 3                               | 2                             | 1              | 0         |  |

|---------------|-----------------|---------------------------|------------------------------------------------------------------------------------------------|---------------------------------|-------------------------------|----------------|-----------|--|

| X2B           | BLJB            | -                         | -                                                                                              | -                               | LB2                           | LB1            | LB0       |  |

| Bit<br>Number | Bit<br>Mnemonic | Description               | Description                                                                                    |                                 |                               |                |           |  |

| 7             | X2B             |                           | <b>X2 Bit</b><br>Set this bit to start in standard mode<br>Clear this bit to start in X2 mode. |                                 |                               |                |           |  |

| 6             | BLJB            |                           | ne user's app                                                                                  | lication on nex<br>r(@F800h) lo | xt RESET (@0<br>cated in FM1. | 0000h) located | d in FM0, |  |

| 5-3           | -               | Reserved<br>The value rea | Reserved<br>The value read from these bits are indeterminate.                                  |                                 |                               |                |           |  |

| 2-0           | LB2:0           | Lock Bits                 |                                                                                                |                                 |                               |                |           |  |

After erasing the chip in parallel mode, the default value is : FFh

The erasing in ISP mode (from bootloader) does not modify this byte.

- Notes: 1. Only the 4 MSB bits can be accessed by software.

- 2. The 4 LSB bits can only be accessed by parallel mode.

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Registers

Table 25. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                                                                                                                               | 4                                                                                                                                                                                                                                                         | 3                                                  | 2                | 1                                             | 0       |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|-----------------------------------------------|---------|--|--|

| FE/SM0        | SM1             | SM2                                                                                                                             | REN                                                                                                                                                                                                                                                       | TB8                                                | RB8              | ТІ                                            | RI      |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                     |                                                                                                                                                                                                                                                           |                                                    |                  |                                               |         |  |  |

| 7             | FE              | Clear to rese                                                                                                                   | raming Error bit (SMOD0=1)<br>lear to reset the error state, not cleared by a valid stop bit.<br>et by hardware when an invalid stop bit is detected.                                                                                                     |                                                    |                  |                                               |         |  |  |

|               | SM0             | •                                                                                                                               | <b>Node bit 0 (S</b><br>I for serial por                                                                                                                                                                                                                  | MOD0=0)<br>t mode select                           | ion.             |                                               |         |  |  |

| 6             | SM1             | Serial port M           SM0         SM1           0         0           0         1           1         0           1         1 | Baud Rate       M0     SM1     Mode     Baud Rate       0     Shift Register     F <sub>XTAL</sub> /12 (or F <sub>XTAL</sub> /6 in mode X2)       1     8-bit UART     Variable       0     9-bit UART     F <sub>XTAL</sub> /64 or F <sub>XTAL</sub> /32 |                                                    |                  |                                               |         |  |  |

| 5             | SM2             | Clear to disa                                                                                                                   | ble multiproce                                                                                                                                                                                                                                            | essor commur                                       | nication feature | <b>ion Enable b</b> i<br>e.<br>n mode 2 and 2 |         |  |  |

| 4             | REN             |                                                                                                                                 | i <b>nable bit</b><br>ble serial rece<br>e serial recept                                                                                                                                                                                                  |                                                    |                  |                                               |         |  |  |

| 3             | TB8             | Clear to trans                                                                                                                  | Bit 8/Ninth b<br>smit a logic 0<br>nit a logic 1 in                                                                                                                                                                                                       | in the 9th bit.                                    | in modes 2 a     | ind 3                                         |         |  |  |

| 2             | RB8             | Cleared by h                                                                                                                    | ardware if 9th                                                                                                                                                                                                                                            | eceived in m<br>bit received i<br>received is a lo | 0                |                                               |         |  |  |

| 1             | ті              | Clear to ackr<br>Set by hardw                                                                                                   | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>stop bit in the other modes.                                                                         |                                                    |                  |                                               |         |  |  |

| 0             | RI              | Set by hardw                                                                                                                    | nowledge inte                                                                                                                                                                                                                                             | d of the 8th bi                                    | t time in mode   | 0, see Figure                                 | 33. and |  |  |

Reset Value = 0000 0000b Bit addressable

### Table 31. TMOD Register

TMOD (S:89h) Timer/Counter Mode Control Register

| 7             | 6               | 5                                          | 4                                                                                                                                                               | 3                                                     | 2             | 1            | 0             |  |

|---------------|-----------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|--------------|---------------|--|

| GATE1         | C/T1#           | M11                                        | M01                                                                                                                                                             | GATE0                                                 | C/T0#         | M10          | M00           |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                |                                                                                                                                                                 |                                                       |               |              |               |  |

| 7             | GATE1           | Clear to enal                              | <b>Timer 1 Gating Control Bit</b><br>Clear to enable Timer 1 whenever TR1 bit is set.<br>Set to enable Timer 1 only while INT1# pin is high and TR1 bit is set. |                                                       |               |              |               |  |

| 6             | C/T1#           | Clear for Tim                              | •                                                                                                                                                               | <b>elect Bit</b><br>Timer 1 count<br>Timer 1 count    |               |              |               |  |

| 5             | M11             |                                            | le Select Bit                                                                                                                                                   |                                                       |               |              |               |  |

| 4             | M01             | <u>M11 M01</u><br>0 0<br>0 1<br>1 0<br>1 1 | M11<br>0M01<br>Operating mode000Mode 0: 8-bit Timer/Counter (TH1) with 5-bit prescaler (TL1).0101100Mode 2: 8-bit auto-reload Timer/Counter (TL1) (1)           |                                                       |               |              |               |  |

| 3             | GATE0           | Clear to enal                              |                                                                                                                                                                 | <b>Bit</b><br>henever TR0 b<br>ter 0 only while       |               | high and TRC | ) bit is set. |  |

| 2             | C/T0#           | Clear for Tim                              | •                                                                                                                                                               | <b>elect Bit</b><br>Timer 0 count<br>Timer 0 count    |               |              |               |  |

| 1             | M10             | <b>Timer 0 Mod</b><br>M10 M00<br>0 0       | 0 0 Mode 0: 8-bit Timer/Counter (TH0) with 5-bit prescaler (TL0).                                                                                               |                                                       |               |              |               |  |

| 0             | M00             | 1 0<br>1 1                                 | Mode 2: 8-<br>Mode 3: Tl                                                                                                                                        | bit auto-reload<br>L0 is an 8-bit T<br>g Timer 1's TR | Timer/Counter |              |               |  |

1. Reloaded from TH1 at overflow.

2. Reloaded from TH0 at overflow.

Reset Value = 0000 0000b

#### Table 39. TL2 Register

#### TL2 (S:CCh) Timer 2 Low Byte Register

| 7             | 6               | 5           | 4        | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|----------|---|---|---|---|

| -             | -               | -           | -        | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |          |   |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2. |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

Table 40. RCAP2H Register

RCAP2H (S:CBh) Timer 2 Reload/Capture High Byte Register

| 7             | 6               | 5            | 4             | 3           | 2 | 1 | 0 |

|---------------|-----------------|--------------|---------------|-------------|---|---|---|

| -             | -               | -            | -             | -           | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |               |             |   |   |   |

| 7-0           |                 | High Byte of | Timer 2 Reloa | ad/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 41. RCAP2L Register

RCAP2L (S:CAн) TIMER 2 Reload/Capture Low Byte Register

| 7             | 6               | 5           | 4             | 3          | 2 | 1 | 0 |

|---------------|-----------------|-------------|---------------|------------|---|---|---|

| -             | -               | -           | -             | -          | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |               |            |   |   |   |

| 7-0           |                 | Low Byte of | Timer 2 Reloa | d/Capture. |   |   |   |

Reset Value = 0000 0000b Not bit addressable

# AT89C51CC03

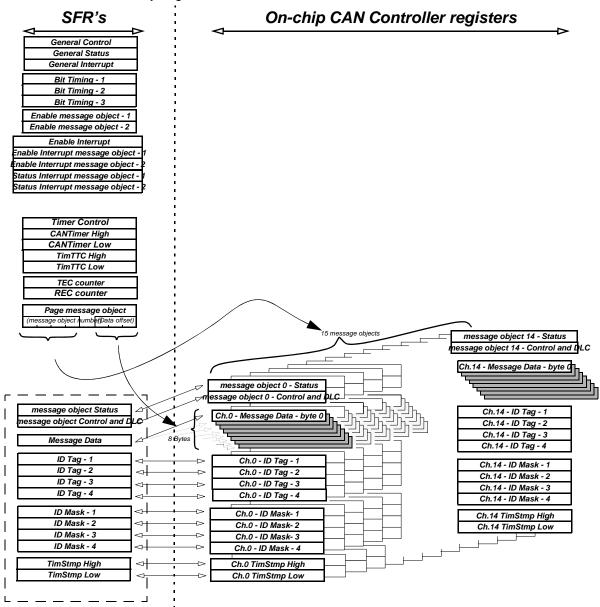

Figure 48. CAN Controller Memory Organization

message object Window SFRs

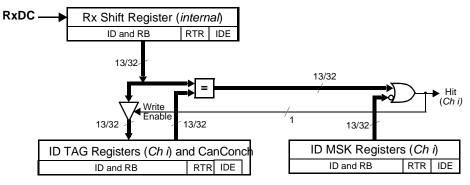

#### **Acceptance Filter**

Upon a reception hit (i.e., a good comparison between the ID+RTR+RB+IDE received and an ID+RTR+RB+IDE specified while taking the comparison mask into account) the ID+RTR+RB+IDE received are written over the ID TAG Registers.

ID => IDT0-29

RTR => RTRTAG

RB => RB0-1TAG

IDE => IDE in CANCONCH register

example: To accept only ID = 318h in part A. ID MSK = 111 1111 1111 b ID TAG = 011 0001 1000 b

CAN SFRs

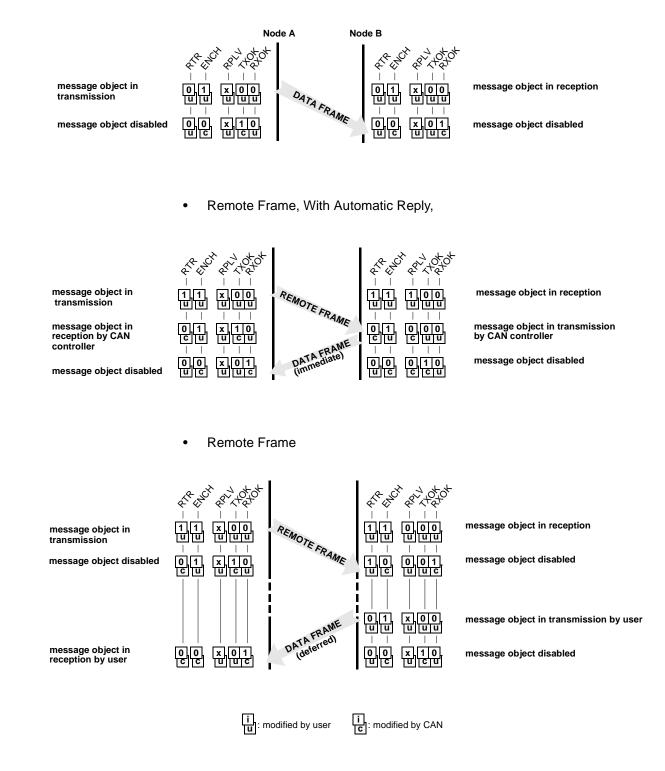

## **Data and Remote Frame**

Description of the different steps for:

Data Frame

# Registers

### Table 48. CANGCON Register

CANGCON (S:ABh) CAN General Control Register

| 7             | 6            | 5                                                                                                                                                                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                            | 2                             | 1                         | 0                              |  |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------|---------------------------|--------------------------------|--|

| ABRQ          | OVRQ         | TTC                                                                                                                                                                                                               | SYNCTTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AUTOBAUD                                                                     | TEST                          | ENA                       | GRES                           |  |

| Bit<br>Number | Bit Mnemonic | Descripti                                                                                                                                                                                                         | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |                               |                           |                                |  |

| 7             | ABRQ         | and DLC r<br>communic                                                                                                                                                                                             | to-resetable b<br>register) is dor<br>cations are imr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | it. A reset of the<br>ne for each mes<br>nediately aborte<br>setting the app | sage object.<br>ed but the or | The pending<br>going comm | transmission<br>unication will |  |

| 6             | OVRQ         | Overload frame request (initiator)<br>Auto-resetable bit.<br>Set to send an overload frame after the next received message.<br>Cleared by the hardware at the beginning of transmission of the overload<br>frame. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                               |                           |                                |  |

| 5             | ттс          | set to sele                                                                                                                                                                                                       | i <b>n Timer Trigg</b><br>ect node in TT<br>sable TTC fea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                            | ation                         |                           |                                |  |

| 4             | SYNCTTC      | When this<br>Frame.<br>When this                                                                                                                                                                                  | Synchronization of TTC<br>When this bit is set the TTC timer is caught on the last bit of the End Of<br>Frame.<br>When this bit is clear the TTC timer is caught on the Start Of Frame.<br>This bit is only used in the TTC mode.                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              |                               |                           |                                |  |

| 3             | AUTOBAUD     |                                                                                                                                                                                                                   | UD<br>ivate listening<br>isable listening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |                               |                           |                                |  |

| 2             | TEST         | Test mode<br>use.                                                                                                                                                                                                 | e. The test mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | de is intended f                                                             | or factory te                 | sting and not             | for customer                   |  |

| 1             | ENA/STB      | When this<br>When this<br>the CAN of<br>message<br>In the star<br>receiver is<br>During the                                                                                                                       | Enable/Standby CAN Controller<br>When this bit is set, it enables the CAN controller and its input clock.<br>When this bit is clear, the on-going communication is terminated normally and<br>the CAN controller state of the machine is frozen (the ENCH bit of each<br>message object does not change).<br>In the standby mode, the transmitter constantly provides a recessive level; the<br>receiver is not activated and the input clock is stopped in the CAN controller.<br>During the disable mode, the registers and the mailbox remain accessible.<br>Note that two clock periods are needed to start the CAN controller state of the |                                                                              |                               |                           |                                |  |

| 0             | GRES         | Auto-rese                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>re reset)</b><br>reset command<br>oller. After a res                      |                               |                           |                                |  |

Reset Value = 0000 0x00b

### Table 53. CANGIE Register

CANGIE (S:C1h) CAN General Interrupt Enable

| 7             | 6            | 5                                     | 4                                                                                   | 3                | 2             | 1               | 0 |  |  |

|---------------|--------------|---------------------------------------|-------------------------------------------------------------------------------------|------------------|---------------|-----------------|---|--|--|

| -             | -            | ENRX                                  | ENTX                                                                                | ENERCH           | ENBUF         | ENERG           | - |  |  |

| Bit<br>Number | Bit Mnemonio | c Descripti                           | on                                                                                  |                  |               |                 |   |  |  |

| 7-6           | -            | Reserved<br>The value                 | eserved<br>he values read from these bits are indeterminate. Do not set these bits. |                  |               |                 |   |  |  |

| 5             | ENRX         | Enable R<br>0 - Disable<br>1 - Enable |                                                                                     |                  |               |                 |   |  |  |

| 4             | ENTX         | 0 - Disabl                            | <b>Enable Transmit Interrupt</b><br>0 - Disable<br>1 - Enable                       |                  |               |                 |   |  |  |

| 3             | ENERCH       | Enable M<br>0 - Disabl<br>1 - Enable  | e                                                                                   | ct Error Inter   | rupt          |                 |   |  |  |

| 2             | ENBUF        | 0 - Disabl                            | <b>Enable BUF Interrupt</b><br>0 - Disable<br>1 - Enable                            |                  |               |                 |   |  |  |

| 1             | ENERG        | 0 - Disabl                            | <b>Enable General Error Interrupt</b><br>0 - Disable<br>1 - Enable                  |                  |               |                 |   |  |  |

| 0             | -            | Reserved<br>The value                 |                                                                                     | s bit is indeter | minate. Do no | t set this bit. |   |  |  |

Note: See Figure 50

Reset Value = xx00 000xb

In a Master configuration, the  $\overline{SS}$  line can be used in conjunction with the MODF flag in the SPI Status register (SPSCR) to prevent multiple masters from driving MOSI and SCK (see Error conditions).

A high level on the  $\overline{SS}$  pin puts the MISO line of a Slave SPI in a high-impedance state.

The  $\overline{SS}$  pin could be used as a general-purpose if the following conditions are met:

- The device is configured as a Master and the SSDIS control bit in SPCON is set. This kind of configuration can be found when only one Master is driving the network and there is no way that the SS pin could be pulled low. Therefore, the MODF flag in the SPSCR will never be set<sup>(1)</sup>.

- The Device is configured as a Slave with CPHA and SSDIS control bits set<sup>(2)</sup>. This kind of configuration can happen when the system includes one Master and one Slave only. Therefore, the device should always be selected and there is no reason that the Master uses the SS pin to select the communicating Slave device.

- Note: 1. Clearing SSDIS control bit does not clear MODF.

- 2. Special care should be taken not to set SSDIS control bit when CPHA ='0' because in this mode, the  $\overline{SS}$  is used to start the transmission.

Baud RateIn Master mode, the baud rate can be selected from a baud rate generator which is con-<br/>trolled by three bits in the SPCON register: SPR2, SPR1 and SPR0. The Master clock is<br/>selected from one of seven clock rates resulting from the division of the internal clock by<br/>4, 8, 16, 32, 64 or 128.

Table 90 gives the different clock rates selected by SPR2:SPR1:SPR0.

In Slave mode, the maximum baud rate allowed on the SCK input is limited to  $F_{svs}/4$

| SPR2 | SPR1 | SPR0 | Clock Rate                   | Baud Rate Divisor (BD) |

|------|------|------|------------------------------|------------------------|

| 0    | 0    | 0    | Don't Use                    | No BRG                 |

| 0    | 0    | 1    | F <sub>CLK PERIPH</sub> /4   | 4                      |

| 0    | 1    | 0    | F <sub>CLK PERIPH</sub> /8   | 8                      |

| 0    | 1    | 1    | F <sub>CLK PERIPH</sub> /16  | 16                     |

| 1    | 0    | 0    | F <sub>CLK PERIPH</sub> /32  | 32                     |

| 1    | 0    | 1    | F <sub>CLK PERIPH</sub> /64  | 64                     |

| 1    | 1    | 0    | F <sub>CLK PERIPH</sub> /128 | 128                    |

| 1    | 1    | 1    | Don't Use                    | No BRG                 |

#### Table 90. SPI Master Baud Rate Selection

# **PCA Registers**

#### Table 95. CMOD Register

CMOD (S:D9h) PCA Counter Mode Register

| 7             | 6               | 5                                                                                                                                                                                  | 4 | 3 | 2    | 1    | 0   |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------|------|-----|--|--|

| CIDL          | WDTE            | -                                                                                                                                                                                  | - | - | CPS1 | CPS0 | ECF |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                        |   |   |      |      |     |  |  |

| 7             | CIDL            | PCA Counter Idle Control bit<br>Clear to let the PCA run during Idle mode.<br>Set to stop the PCA when Idle mode is invoked.                                                       |   |   |      |      |     |  |  |

| 6             | WDTE            | WatchDog Timer Enable<br>Clear to disable WatchDog Timer function on PCA Module 4,<br>Set to enable it.                                                                            |   |   |      |      |     |  |  |

| 5             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                             |   |   |      |      |     |  |  |

| 4             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                             |   |   |      |      |     |  |  |

| 3             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                             |   |   |      |      |     |  |  |

| 2             | CPS1            | EWC Count Pulse Select bitsCPS1CPS0Clock source00Internal Clock, FPca/601Internal Clock, FPca/210Timer 0 overflow11External clock at ECI/P1.2 pin (Max. Rate = FPca/4)             |   |   |      |      |     |  |  |

| 1             | CPS0            | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                             |   |   |      |      |     |  |  |

| 0             | ECF             | Enable PCA Counter Overflow Interrupt bit<br>Clear to disable CF bit in CCON register to generate an interrupt.<br>Set to enable CF bit in CCON register to generate an interrupt. |   |   |      |      |     |  |  |

Reset Value = 00XX X000b

## STANDARD NOTES FOR PQFP/ VQFP / TQFP / DQFP

1/ CONTROLLING DIMENSIONS : INCHES

2/ ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y 14.5M - 1982.

3/ "D1 AND E1" DIMENSIONS DO NOT INCLUDE MOLD PROTUSIONS. MOLD PROTUSIONS SHALL NOT EXCEED 0.25 mm (0.010 INCH). THE TOP PACKAGE BODY SIZE MAY BE SMALLER THAN THE BOTTOM PACKAGE BODY SIZE BY AS MUCH AS 0.15 mm.

4/ DATUM PLANE "H" LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

5/ DATUM "A" AND "D" TO BE DETERMINED AT DATUM PLANE H.

6/ DIMENSION " f " DOES NOT INCLUDE DAMBAR PROTUSION ALLOWABLE DAMBAR PROTUSION SHALL BE 0.08mm/.003" TOTAL IN EXCESS OF THE " f " DIMENSION AT MAXIMUM MATERIAL CONDITION . DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

## STANDARD NOTES FOR PQFP/ VQFP / TQFP / DQFP

1/ CONTROLLING DIMENSIONS : INCHES

2/ ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y 14.5M - 1982.

3/ "D1 AND E1" DIMENSIONS DO NOT INCLUDE MOLD PROTUSIONS. MOLD PROTUSIONS SHALL NOT EXCEED 0.25 mm (0.010 INCH). THE TOP PACKAGE BODY SIZE MAY BE SMALLER THAN THE BOTTOM PACKAGE BODY SIZE BY AS MUCH AS 0.15 mm.

4/ DATUM PLANE "H" LOCATED AT MOLD PARTING LINE AND COINCIDENT WITH LEAD, WHERE LEAD EXITS PLASTIC BODY AT BOTTOM OF PARTING LINE.

5/ DATUM "A" AND "D" TO BE DETERMINED AT DATUM PLANE H.

6/ DIMENSION " f " DOES NOT INCLUDE DAMBAR PROTUSION ALLOWABLE DAMBAR PROTUSION SHALL BE 0.08mm/.003" TOTAL IN EXCESS OF THE " f " DIMENSION AT MAXIMUM MATERIAL CONDITION . DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. Changes from 4182N 03/08 to 4182O 09/08

1. Correction to SPDT register address Table 94 on page 139.

# **Table of Contents**

| Features 1                            |

|---------------------------------------|

| Description2                          |

| Block Diagram2                        |

| Pin Configuration                     |

| I/O Configurations7                   |

| Port 1, Port 3 and Port 4 7           |

| Port 0 and Port 2 8                   |

| Read-Modify-Write Instructions 9      |

| Quasi-Bidirectional Port Operation 10 |

| SFR Mapping11                         |

| Clock                                 |

| Description                           |

| Registers                             |

| Data Memory                           |

| Internal Space                        |

| External Space 24                     |

| Dual Data Pointer                     |

| Registers                             |

| Power Monitor                         |

| Description                           |

| Reset                                 |

| Introduction                          |

| Reset Input 31                        |

| Reset Output                          |

| Power Management                      |

| Introduction                          |

| Idle Mode                             |

| Power-Down Mode 33                    |

| Registers                             |

| EEPROM Data Memory                    |

| Write Data in the Column Latches      |

| Programming                           |

| Read Data                             |

| Examples                              |

# AT89C51CC03

| DC Parameters for A/D Converter 17           | ′1         |

|----------------------------------------------|------------|

| AC Parameters17                              | '1         |

| Timings                                      | 31         |

| Ordering Information18                       | 4          |

| Package Drawings                             | 5          |

| VQFP44                                       | 35         |

| PLCC44                                       | 37         |

| VQFP64                                       | 39         |

| PLCC52 19                                    | )1         |

| Datasheet Change Log 19                      | 2          |

| Changes from 4182B - 09/03 to 4182C 12/03 19 | )2         |

| Changes from 4182C - 12/03 to 4182D 01/04 19 | )2         |

| Changes from 4182D - 01/04 to 4182E 05/04 19 | )2         |

| Changes from 4182E -05/04 to 4182F 10/04 19  | )2         |

| Changes from 4182F - 10/04 to 4182G 03/05 19 | )2         |

| Changes from 4182G 03/05 to 4182H 04/05 19   | )2         |

| Changes from 4182H 04/05 to 4182I 06/05 19   | )2         |

| Changes from 4182I 06/05 to 4182J 03/06 19   | )2         |

| Changes from 4182J 03/06 to 4182K 04/06 19   | )2         |

| Changes from 4182K 04/06 to 4182L 06/07 19   | )2         |

| Changes from 4182L 06/07 to 4182M 02/08 19   | )2         |

| Changes from 4182M 02/087 to 4182N 03/08 19  | )2         |

| Changes from 4182N 03/08 to 4182O 09/08 19   | )3         |

| Table of Contents                            | . <b>i</b> |