Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 40MHz                                                                         |

| Connectivity               | CANbus, UART/USART                                                            |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 36                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 2K x 8                                                                        |

| RAM Size                   | 2.25K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-LCC (J-Lead)                                                               |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc03ca-slsum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS      | GND  | Circuit ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TESTI    | I    | Must be connected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VCC      |      | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VAREF    |      | Reference Voltage for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VAGND    |      | Reference Ground for ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.0:7   | I/O  | <b>Port 0:</b><br>Is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in this state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and Data Memory. In this application it uses strong internal pull-ups when emitting 1's.<br>Port 0 also outputs the code Bytes during program validation. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.0:7   | I/O  | Port 1:<br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins can be used for digital input/output or as analog inputs for<br>the Analog Digital Converter (ADC). Port 1 pins that have 1's written to them are pulled high by the internal pull-up transistors<br>and can be used as inputs in this state. As inputs, Port 1 pins that are being pulled low externally will be the source of current<br>(IL), see section "Electrical Characteristic") because of the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups. Port 1 pins are assigned to be used as analog<br>inputs via the ADCCF register (in this case the internal pull-ups are disconnected).<br>As a secondary digital function, port 1 contains the Timer 2 external trigger and clock input; the PCA external clock input and<br>the PCA module I/O.<br>P1.0/AN0/T2<br>Analog input channel 0,<br>External clock input for Timer/counter2.<br>P1.1/AN1/T2EX<br>Analog input channel 1,<br>Trigger input for Timer/counter2.<br>P1.2/AN2/ECI<br>Analog input channel 2,<br>PCA external clock input.<br>P1.3/AN3/CEX0<br>Analog input channel 3,<br>PCA module 0 Entry of input/PWM output.<br>P1.4/AN4/CEX1<br>Analog input channel 4,<br>PCA module 1 Entry of input/PWM output.<br>P1.5/AN5/CEX2<br>Analog input channel 5,<br>PCA. Module 1 Entry of input/PWM output.<br>P1.5/ANS/CEX3<br>Analog input channel 6,<br>PCA module 2 Entry of input/PWM output. |

|          |      | P1.7/AN7/CEX4<br>Analog input channel 7,<br>PCA module 4 Entry ot input/PWM output.<br>Port 1 receives the low-order address byte during EPROM programming and program verification.<br>It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.0:7   | I/O  | <b>Port 2:</b><br>Is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and can be used as inputs in this state. As inputs, Port 2 pins that are being pulled low externally will be a source of current (I <sub>IL</sub> , see section "Electrical Characteristic") because of the internal pull-ups. Port 2 emits the high-order address byte during accesses to the external Program Memory and during accesses to external Data Memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1's. During accesses to external Data Memory that use 8 bit addresses (MOVX @Ri), Port 2 transmits the contents of the P2 special function register. It also receives high-order addresses and control signals during program validation. It can drive CMOS inputs without external pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

write the new byte back to the latch. These Read-Modify-Write instructions are directed to the latch rather than the pin in order to avoid possible misinterpretation of voltage (and therefore, logic) levels at the pin. For example, a Port bit used to drive the base of an external bipolar transistor can not rise above the transistor's base-emitter junction voltage (a value lower than VIL). With a logic one written to the bit, attempts by the CPU to read the Port at the pin are misinterpreted as logic zero. A read of the latch rather than the pins returns the correct logic-one value.

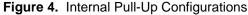

# Quasi-Bidirectional Port Operation

Port 1, Port 2, Port 3 and Port 4 have fixed internal pull-ups and are referred to as "quasi-bidirectional" Ports. When configured as an input, the pin impedance appears as logic one and sources current in response to an external logic zero condition. Port 0 is a "true bidirectional" pin. The pins float when configured as input. Resets write logic one to all Port latches. If logical zero is subsequently written to a Port latch, it can be returned to input conditions by a logical one written to the latch.

Note: Port latch values change near the end of Read-Modify-Write instruction cycles. Output buffers (and therefore the pin state) update early in the instruction after Read-Modify-Write instruction cycle.

Logical zero-to-one transitions in Port 1, Port 2, Port 3 and Port 4 use an additional pullup (p1) to aid this logic transition (see Figure 4.). This increases switch speed. This extra pull-up sources 100 times normal internal circuit current during 2 oscillator clock periods. The internal pull-ups are field-effect transistors rather than linear resistors. Pullups consist of three p-channel FET (pFET) devices. A pFET is on when the gate senses logical zero and off when the gate senses logical one. pFET #1 is turned on for two oscillator periods immediately after a zero-to-one transition in the Port latch. A logical one at the Port pin turns on pFET #3 (a weak pull-up) through the inverter. This inverter and pFET pair form a latch to drive logical one. pFET #2 is a very weak pull-up switched on whenever the associated nFET is switched off. This is traditional CMOS switch convention. Current strengths are 1/10 that of pFET #3.

Note: Port 2 p1 assists the logic-one output for memory bus cycles.

# Table 1. SFR Mapping

|     | 0/8 <sup>(2)</sup> | 1/9                  | 2/A                  | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   |     |

|-----|--------------------|----------------------|----------------------|-----------------------|----------------------|----------------------|-----------------------|-----------------------|-----|

| F8h | IPL1<br>xxxx x000  | CH<br>0000 0000      | CCAP0H<br>0000 0000  | CCAP1H<br>0000 0000   | CCAP2H<br>0000 0000  | CCAP3H<br>0000 0000  | CCAP4H<br>0000 0000   |                       | FFh |

| F0h | B<br>0000 0000     |                      | ADCLK<br>xxx0 0000   | ADCON<br>x000 0000    | ADDL<br>0000 0000    | ADDH<br>0000 0000    | ADCF<br>0000 0000     | IPH1<br>xxxx x000     | F7h |

| E8h | IEN1<br>xxxx x000  | CL<br>0000 0000      | CCAP0L<br>0000 0000  | CCAP1L<br>0000 0000   | CCAP2L<br>0000 0000  | CCAP3L<br>0000 0000  | CCAP4L<br>0000 0000   |                       | EFh |

| E0h | ACC<br>0000 0000   |                      |                      |                       |                      |                      |                       |                       | E7h |

| D8h | CCON<br>0000 0000  | CMOD<br>00xx x000    | CCAPM0<br>x000 0000  | CCAPM1<br>x000 0000   | CCAPM2<br>x000 0000  | CCAPM3<br>x000 0000  | CCAPM4<br>x000 0000   |                       | DFh |

| D0h | PSW<br>0000 0000   | FCON<br>0000 0000    | EECON<br>xxxx xx00   | FSTA<br>xxxx xx00     | SPCON<br>0001 0100   | SPSCR<br>0000 0000   | SPDAT<br>xxxx xxxx    |                       | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>xxxx xx00   | RCAP2L<br>0000 0000  | RCAP2H<br>0000 0000   | TL2<br>0000 0000     | TH2<br>0000 0000     | CANEN1<br>x000 0000   | CANEN2<br>0000 0000   | CFh |

| C0h | P4<br>xxx1 1111    | CANGIE<br>xx00 000x  | CANIE1<br>x000 0000  | CANIE2<br>0000 0000   | CANIDM1<br>xxxx xxxx | CANIDM2<br>xxxx xxxx | CANIDM3<br>xxxx xxxx  | CANIDM4<br>xxxx xxxx  | C7h |

| B8h | IPL0<br>x000 0000  | SADEN<br>0000 0000   | CANSIT1<br>0000 0000 | CANSIT2<br>0000 0000  | CANIDT1<br>xxxx xxxx | CANIDT2<br>xxxx xxxx | CANIDT3<br>xxxx xxxx  | CANIDT4<br>xxxx xxxx  | BFh |

| B0h | P3<br>1111 1111    | CANPAGE<br>0000 0000 | CANSTCH<br>xxxx xxxx | CANCONCH<br>xxxx xxxx | CANBT1<br>xxxx xxxx  | CANBT2<br>xxxx xxxx  | CANBT3<br>xxxx xxxx   | IPH0<br>x000 0000     | B7h |

| A8h | IEN0<br>0000 0000  | SADDR<br>0000 0000   | CANGSTA<br>x0x0 0000 | CANGCON<br>0000 0x00  | CANTIML<br>0000 0000 | CANTIMH<br>0000 0000 | CANSTMPL<br>0000 0000 | CANSTMPH<br>0000 0000 | AFh |

| A0h | P2<br>1111 1111    | CANTCON<br>0000 0000 | AUXR1<br>xxxx 00x0   | CANMSG<br>xxxx xxxx   | CANTTCL<br>0000 0000 | CANTTCH<br>0000 0000 | WDTRST<br>1111 1111   | WDTPRG<br>xxxx x000   | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>0000 0000    |                      | CANGIT<br>0x00 0000   | CANTEC<br>0000 0000  | CANREC<br>0000 0000  |                       | CKCON1<br>xxxx xxx0   | 9Fh |

| 90h | P1<br>1111 1111    |                      |                      |                       |                      |                      |                       |                       | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000    | TL0<br>0000 0000     | TL1<br>0000 0000      | TH0<br>0000 0000     | TH1<br>0000 0000     | AUXR<br>x001 0100     | CKCON0<br>0000 0000   | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111      | DPL<br>0000 0000     | DPH<br>0000 0000      |                      |                      |                       | PCON<br>00x1 0000     | 87h |

| L   | 0/8 <sup>(2)</sup> | 1/9                  | 2/A                  | 3/B                   | 4/C                  | 5/D                  | 6/E                   | 7/F                   | -   |

Reserved

Note: 1. Do not read or write Reserved Registers

These registers are bit-addressable. Sixteen addresses in the SFR space are both byte-addressable and bit-addressable. The bit-addressable SFR's are those whose address ends in 0 and 8. The bit addresses, in this area, are 0x80 through to 0xFF.

# Registers

# Table 6. PSW Register

PSW (S:8Eh) Program Status Word Register

| 7             | 6               | 5                           | 4                                                                                                             | 3           | 2  | 1  | 0 |

|---------------|-----------------|-----------------------------|---------------------------------------------------------------------------------------------------------------|-------------|----|----|---|

| CY            | AC              | F0                          | RS1                                                                                                           | RS0         | ov | F1 | Р |

| Bit<br>Number | Bit<br>Mnemonic | Description                 | Description                                                                                                   |             |    |    |   |

| 7             | CY              | Carry Flag<br>Carry out fro | m bit 1 of ALL                                                                                                | J operands. |    |    |   |

| 6             | AC              | -                           | Auxiliary Carry Flag<br>Carry out from bit 1 of addition operands.                                            |             |    |    |   |

| 5             | F0              | User Defina                 | ble Flag 0.                                                                                                   |             |    |    |   |

| 4-3           | RS1:0           | -                           | nk Select Bit<br>e 4 for bits de                                                                              |             |    |    |   |

| 2             | OV              | Overflow Fl<br>Overflow set | <b>ag</b><br>by arithmetic                                                                                    | operations. |    |    |   |

| 1             | F1              | User Defina                 | ble Flag 1                                                                                                    |             |    |    |   |

| 0             | Р               |                             | Parity Bit<br>Set when ACC contains an odd number of 1's.<br>Cleared when ACC contains an even number of 1's. |             |    |    |   |

Reset Value = 0000 0000b

# Table 7. AUXR Register

AUXR (S:8Eh) Auxiliary Register

| 7             | 6               | 5                                                                                                                                                                                            | 4                                                                                         | 3    | 2    | 1      | 0  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|--------|----|

| -             | -               | MO                                                                                                                                                                                           | XRS2                                                                                      | XRS1 | XRS0 | EXTRAM | A0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                  |                                                                                           |      |      |        |    |

| 7-6           | -               | Reserved<br>The value re                                                                                                                                                                     | <b>Reserved</b><br>The value read from these bits are indeterminate. Do not set this bit. |      |      |        |    |

| 5             | MO              | Stretch MOVX control:         the RD/ and the WR/ pulse length is increased according to the value of M0.         M0       Pulse length in clock period         0       6         1       30 |                                                                                           |      |      |        |    |

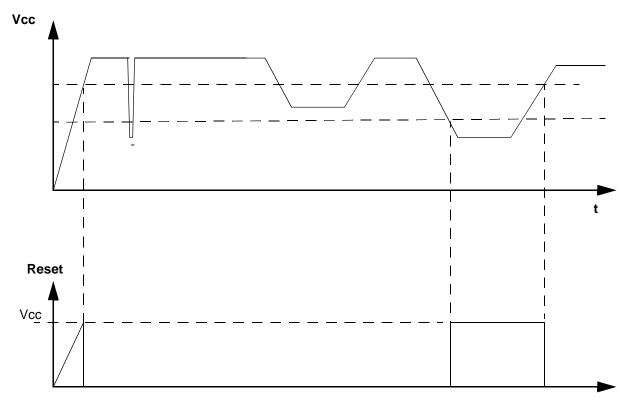

### Figure 15. Power Fail Detect

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

.

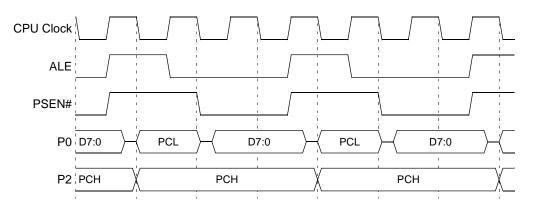

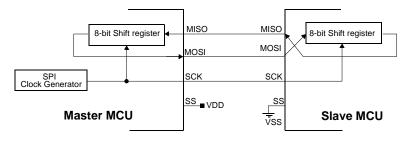

# Figure 22. External Code Fetch Waveforms

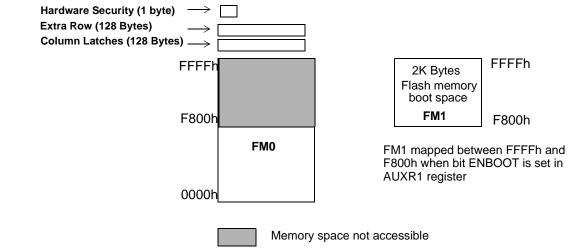

## Flash Memory Architecture

AT89C51CC03 features two on-chip Flash memories:

- Flash memory FM0: containing 64K Bytes of p

- containing 64K Bytes of program memory (user space) organized into 128 byte pages,

- Flash memory FM1:

2K Bytes for boot loader and Application Programming Interfaces (API).

The FM0 can be program by both parallel programming and Serial In-System Programming (ISP) whereas FM1 supports only parallel programming by programmers. The ISP mode is detailed in the "In-System Programming" section.

All Read/Write access operations on Flash Memory by user application are managed by a set of API described in the "In-System Programming" section.

The bit ENBOOT in AUXR1 register is used to map FM1 from F800h to FFFFh. Figure 23 and Figure 24 show the Flash memory configuration with ENBOOT=1 and ENBOOT=0.

# Figure 23. Flash Memory Architecture with ENBOOT=1 (boot mode)

# Table 22. Read MOVC A, @DPTR

|                                              | FC    | ON Regis | ter |               |                                     |               |          |                 | Hardware | Externa |  |  |  |  |   |   |                |    |  |  |  |  |

|----------------------------------------------|-------|----------|-----|---------------|-------------------------------------|---------------|----------|-----------------|----------|---------|--|--|--|--|---|---|----------------|----|--|--|--|--|

| Code Execution                               | FMOD1 | FMOD0    | FPS | ENBOOT        | DPTR                                | FM1           | FM0      | XROW            | Byte     | Code    |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     | 0             | 0000h to FFFFh                      |               | ОК       |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              | 0     | 0        | х   |               | 0000h to F7FF                       |               | ОК       |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     | 1             | F800h to FFFFh                      |               | Do not u | se this configu | uration  |         |  |  |  |  |   |   |                |    |  |  |  |  |

| From FM0                                     | 0     | 1        | х   | x             | 0000 to 007Fh<br>See <sup>(1)</sup> |               |          | ОК              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

| 1                                            | 1     | 0        | Х   | Х             | х                                   |               |          |                 | ОК       |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     | 0             | 000h to FFFFh                       |               | ОК       |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              | 1     | 1 1      | 1   | Х             |                                     | 0000h to F7FF |          | ОК              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     | 1             | F800h to FFFFh                      |               | Do not u | se this configu | uration  |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          | 1   | 0000h to F7FF |                                     | ОК            |          |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     |               |                                     |               | 1        | 1               |          | l       |  |  |  |  | 0 | I | F800h to FFFFh | ОК |  |  |  |  |

|                                              | 0     | 0        |     | 0             | х                                   |               |          | NA              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          | 1   | 1             | х                                   |               | ОК       |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          | I   | 0             | Х                                   |               |          | NA              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

| From FM1<br>(ENBOOT =1                       | 0     | 1        | х   | 1             | 0000h to 007h                       |               |          | ОК              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              | 0     | I        | Λ   | 0             | See <sup>(2)</sup>                  |               |          | NA              |          | -       |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              | 1     | 0        | х   | 1             | x                                   |               |          |                 | ОК       |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       | Ű        | Χ   | 0             | ~                                   |               | -        | NA              |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              | 1     | 1        | х   | 1             | 000h to FFFFh                       |               | ОК       |                 |          |         |  |  |  |  |   |   |                |    |  |  |  |  |

|                                              |       |          |     | 0             |                                     |               | 1        | NA              |          | i       |  |  |  |  |   |   |                |    |  |  |  |  |

| External code :<br>EA=0 or Code<br>Roll Over | х     | 0        | х   | x             | х                                   |               |          |                 |          | ОК      |  |  |  |  |   |   |                |    |  |  |  |  |

1. For DPTR higher than 007Fh only lowest 7 bits are decoded, thus the behavior is the same as for addresses from 0000h to 007Fh

2. For DPTR higher than 007Fh only lowest 7 bits are decoded, thus the behavior is the same as for addresses from 0000h to 007Fh

### Table 26. SADEN Register

SADEN (S:B9h) Slave Address Mask Register

| 7             | 6               | 5           | 4              | 3             | 2  | 1 | 0 |

|---------------|-----------------|-------------|----------------|---------------|----|---|---|

| -             | -               | -           | -              | -             | -  | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |                |               |    |   |   |

| 7-0           |                 | Mask Data f | or Slave Indiv | vidual Addres | SS |   |   |

Reset Value = 0000 0000b Not bit addressable

Table 27. SADDR Register

SADDR (S:A9h) Slave Address Register

| 7             | 6               | 5            | 4            | 3 | 2 | 1 | 0 |

|---------------|-----------------|--------------|--------------|---|---|---|---|

| -             | -               | -            | -            | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |              |   |   |   |   |

| 7-0           |                 | Slave Indivi | dual Address | 5 |   |   |   |

Reset Value = 0000 0000b Not bit addressable

### Table 28. SBUF Register

SBUF (S:99h) Serial Data Buffer

| 7             | 6               | 5            | 4            | 3              | 2 | 1 | 0 |

|---------------|-----------------|--------------|--------------|----------------|---|---|---|

| _             | -               | -            | -            | -              | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description  |              |                |   |   |   |

| 7-0           |                 | Data sent/re | ceived by Se | erial I/O Port |   |   |   |

Reset Value = 0000 0000b Not bit addressable

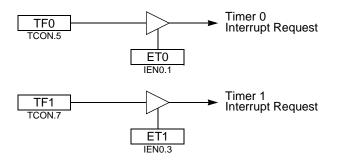

# Interrupt

Each Timer handles one interrupt source that is the timer overflow flag TF0 or TF1. This flag is set every time an overflow occurs. Flags are cleared when vectoring to the Timer interrupt routine. Interrupts are enabled by setting ETx bit in IEN0 register. This assumes interrupts are globally enabled by setting EA bit in IEN0 register.

Figure 39. Timer Interrupt System

# Registers

**Table 30.** TCON RegisterTCON (S:88h)Timer/Counter Control Register

| 7             | 6               | 5                                                                                                                                                                                                    | 4                                                                                                | 3                                   | 2   | 1          | 0          |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|-----|------------|------------|

| TF1           | TR1             | TF0                                                                                                                                                                                                  | TR0                                                                                              | IE1                                 | IT1 | IE0        | IT0        |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                          |                                                                                                  |                                     |     |            |            |

| 7             | TF1             | -                                                                                                                                                                                                    | ardware whe                                                                                      | n processor ve<br>/Counter overl    |     | •          | overflows. |

| 6             | TR1             | Clear to turn                                                                                                                                                                                        | Timer 1 Run Control Bit<br>Clear to turn off Timer/Counter 1.<br>Set to turn on Timer/Counter 1. |                                     |     |            |            |

| 5             | TF0             | Timer 0 Overflow Flag<br>Cleared by hardware when processor vectors to interrupt routine.<br>Set by hardware on Timer/Counter overflow, when Timer 0 register overflows.                             |                                                                                                  |                                     |     |            | overflows. |

| 4             | TR0             | Clear to turn                                                                                                                                                                                        | off Timer/Countries                                                                              |                                     |     |            |            |

| 3             | IE1             | -                                                                                                                                                                                                    | ardware whe                                                                                      | n interrupt is p<br>ernal interrupt |     | 0 00       | (see IT1). |

| 2             | IT1             | Interrupt 1 Type Control Bit<br>Clear to select low level active (level triggered) for external interrupt 1 (INT1#).<br>Set to select falling edge active (edge triggered) for external interrupt 1. |                                                                                                  |                                     |     |            |            |

| 1             | IE0             | Interrupt 0 Edge Flag<br>Cleared by hardware when interrupt is processed if edge-triggered (see IT0).<br>Set by hardware when external interrupt is detected on INT0# pin.                           |                                                                                                  |                                     |     | (see IT0). |            |

| 0             | ITO             | Interrupt 0 Type Control Bit<br>Clear to select low level active (level triggered) for external interrupt 0 (INT0#).<br>Set to select falling edge active (edge triggered) for external interrupt 0. |                                                                                                  |                                     |     |            | ```        |

Reset Value = 0000 0000b

72 AT89C51CC03

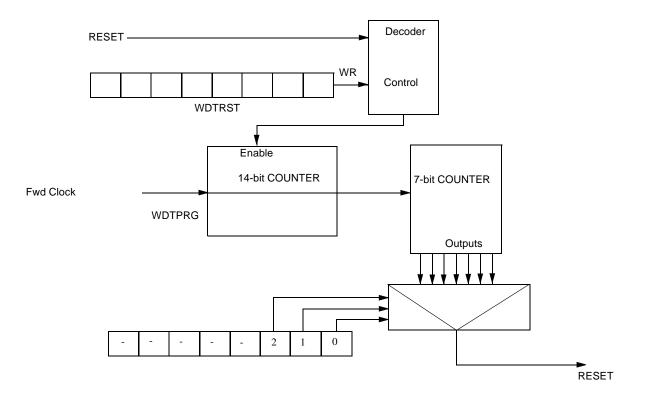

# Watchdog Timer

AT89C51CC03 contains a powerful programmable hardware Watchdog Timer (WDT) that automatically resets the chip if it software fails to reset the WDT before the selected time interval has elapsed. It permits large Time-Out ranking from 16ms to 2s @Fosc = 12MHz in X1 mode.

This WDT consists of a 14-bit counter plus a 7-bit programmable counter, a Watchdog Timer reset register (WDTRST) and a Watchdog Timer programming (WDTPRG) register. When exiting reset, the WDT is -by default- disable.

To enable the WDT, the user has to write the sequence 1EH and E1H into WDTRST register no instruction in between. When the Watchdog Timer is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is  $96xT_{OSC}$ , where  $T_{OSC}=1/F_{OSC}$ . To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset

Note: When the Watchdog is enable it is impossible to change its period.

#### **Buffer Mode**

Any message object can be used to define one buffer, including non-consecutive message objects, and with no limitation in number of message objects used up to 15.

Each message object of the buffer must be initialized CONCH2 = 1 and CONCH1 = 1;

| -                 |   |              |

|-------------------|---|--------------|

| message object 14 | 7 |              |

| message object 13 | - |              |

| message object 12 |   | Block buffer |

| message object 11 |   |              |

| message object 10 |   | buffer 7     |

| message object 9  |   | buffer 6     |

| message object 8  | - | buffer 5     |

| message object 7  |   | buffer 4     |

| message object 6  |   | buffer 3     |

| message object 5  |   | buffer 2     |

| message object 4  |   | buffer 1     |

| message object 3  |   | buffer 0     |

| message object 2  |   |              |

| message object 1  | 1 |              |

| message object 0  | 1 |              |

| -                 | - |              |

The same acceptance filter must be defined for each message objects of the buffer. When there is no mask on the identifier or the IDE, all messages are accepted.

A received frame will always be stored in the lowest free message object.

When the flag Rxok is set on one of the buffer message objects, this message object can then be read by the application. This flag must then be cleared by the software and the message object re-enabled in buffer reception in order to free the message object.

The OVRBUF flag in the CANGIT register is set when the buffer is full. This flag can generate an interrupt.

The frames following the buffer-full interrupt will not stored and no status will be overwritten in the CANSTCH registers involved in the buffer until at least one of the buffer message objects is re-enabled in reception.

This flag must be cleared by the software in order to acknowledge the interrupt.

# Table 51. CANTEC Register

CANTEC (S:9Ch Read Only) CAN Transmit Error Counter

| 7             | 6            | 5                     | 4            | 3    | 2    | 1    | 0    |  |

|---------------|--------------|-----------------------|--------------|------|------|------|------|--|

| TEC7          | TEC6         | TEC5                  | TEC4         | TEC3 | TEC2 | TEC1 | TEC0 |  |

| Bit<br>Number | Bit Mnemonio | : Descripti           | Description  |      |      |      |      |  |

| 7-0           | TEC7:0       | Transmit<br>see Figur | Error Counte | er   |      |      |      |  |

Reset Value = 00h

# Table 52. CANREC Register

CANREC (S:9Dh Read Only) CAN Reception Error Counter

| 7             | 6            | 5                   | 4                     | 3    | 2    | 1    | 0    |  |  |

|---------------|--------------|---------------------|-----------------------|------|------|------|------|--|--|

| REC7          | REC6         | REC5                | REC4                  | REC3 | REC2 | REC1 | REC0 |  |  |

| Bit<br>Number | Bit Mnemonic | Descriptio          | Description           |      |      |      |      |  |  |

| 7-0           | REC7:0       | Reception see Figur | n Error Count<br>e 53 | ter  |      |      |      |  |  |

Reset Value = 00h

## Table 60. CANBT1 Register

CANBT1 (S:B4h) CAN Bit Timing Registers 1

| 7             | 6          | 5             | 4                                                                                                                                                                                               | 3     | 2     | 1     | 0 |  |  |

|---------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|---|--|--|

| -             | BRP 5      | BRP 4         | BRP 3                                                                                                                                                                                           | BRP 2 | BRP 1 | BRP 0 | - |  |  |

| Bit<br>Number | Bit Mnemon | ic Descriptio | Description                                                                                                                                                                                     |       |       |       |   |  |  |

| 7             | -          |               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                 |       |       |       |   |  |  |

| 6-1           | BRP5:0     | The period    | Baud rate prescaler<br>The period of the CAN controller system clock Tscl is programmable and<br>determines the individual bit timing.<br>$\frac{BRP[50] + 1}{Tscl} = \frac{BRP[50] + 1}{Tscl}$ |       |       |       |   |  |  |

|               |            | Reserved      |                                                                                                                                                                                                 | F     | can   |       |   |  |  |

| 0             | -          |               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                          |       |       |       |   |  |  |

Note: The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0. See Figure 52.

No default value after reset.

# Table 62. CANBT3 Register

### CANBT3 (S:B6h) CAN Bit Timing Registers 3

| 7             | 6            | 5                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                                                   | 3      | 2      | 1      | 0   |  |  |

|---------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-----|--|--|

| -             | PHS2 2       | PHS2 1                                                                                                                                                                                                                                                                                  | PHS2 0                                                                                                                                                                              | PHS1 2 | PHS1 1 | PHS1 0 | SMP |  |  |

| Bit<br>Number | Bit Mnemonic | Descriptio                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                         |        |        |        |     |  |  |

| 7             | -            |                                                                                                                                                                                                                                                                                         | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                     |        |        |        |     |  |  |

| 6-4           | PHS2 2:0     | Phase Segment 2<br>This phase is used to compensate for phase edge errors. This segment can<br>be shortened by the re-synchronization jump width.<br>Tphs2 = Tscl x (PHS2[20] + 1)<br>Phase segment 2 is the maximum of Phase segment 1 and the Information<br>Processing Time (= 2TQ). |                                                                                                                                                                                     |        |        |        |     |  |  |

| 3-1           | PHS1 2:0     | This phase                                                                                                                                                                                                                                                                              | Phase Segment 1<br>This phase is used to compensate for phase edge errors. This segment can<br>be lengthened by the re-synchronization jump width.<br>Tphs1 = Tscl x (PHS1[20] + 1) |        |        |        |     |  |  |

| 0             | SMP          | Sample Type<br>0 - once, at the sample point.<br>1 - three times, the threefold sampling of the bus is the sample point and twice<br>over a distance of a 1/2 period of the Tscl. The result corresponds to the<br>majority decision of the three values.                               |                                                                                                                                                                                     |        |        |        |     |  |  |

Note: The CAN controller bit timing registers must be accessed only if the CAN controller is disabled with the ENA bit of the CANGCON register set to 0. See Figure 52.

No default value after reset.

## Table 79. CANIDM2 Register for V2.0 part B

CANIDM2 for V2.0 part B (S:C5h) CAN Identifier Mask Registers 2

| 7             | 6           | 5           | 4                                                       | 3        | 2        | 1        | 0        |  |

|---------------|-------------|-------------|---------------------------------------------------------|----------|----------|----------|----------|--|

| IDMSK 20      | IDMSK 19    | IDMSK 18    | IDMSK 17                                                | IDMSK 16 | IDMSK 15 | IDMSK 14 | IDMSK 13 |  |

| Bit<br>Number | Bit Mnemoni | c Descripti | Description                                             |          |          |          |          |  |

| 7-0           | IDMSK20:1   | 0 - compa   | Mask Value<br>rison true forc<br>nparison enab<br>e 54. |          |          |          |          |  |

Note: The ID Mask is only used for reception.

No default value after reset.

#### Table 80. CANIDM3 Register for V2.0 part B

CANIDM3 for V2.0 part B (S:C6h) CAN Identifier Mask Registers 3

| 7             | 6          | 5              | 4                                                      | 3       | 2       | 1       | 0       |

|---------------|------------|----------------|--------------------------------------------------------|---------|---------|---------|---------|

| IDMSK 12      | IDMSK 11   | IDMSK 10       | IDMSK 9                                                | IDMSK 8 | IDMSK 7 | IDMSK 6 | IDMSK 5 |

| Bit<br>Number | Bit Mnemon | ic Description | Description                                            |         |         |         |         |

| 7-0           | IDMSK12:5  | 0 - compa      | Mask Value<br>rison true forc<br>parison enab<br>e 54. |         |         |         |         |

Note: The ID Mask is only used for reception.

No default value after reset.

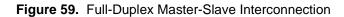

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 59).

| Master Mode          | The SPI operates in Master mode when the Master bit, MSTR <sup>(1)</sup> , in the SPCON register<br>is set. Only one Master SPI device can initiate transmissions. Software begins the trans-<br>mission from a Master SPI Module by writing to the Serial Peripheral Data Register<br>(SPDAT). If the shift register is empty, the Byte is immediately transferred to the shift<br>register. The Byte begins shifting out on MOSI pin under the control of the serial clock,<br>SCK. Simultaneously, another Byte shifts in from the Slave on the Master's MISO pin.<br>The transmission ends when the Serial Peripheral transfer data flag, SPIF, in SPSCR<br>becomes set. At the same time that SPIF becomes set, the received Byte from the Slave<br>is transferred to the receive data register in SPDAT. Software clears SPIF by reading<br>the Serial Peripheral Status register (SPSCR) with the SPIF bit set, and then reading the<br>SPDAT. |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slave Mode           | The SPI operates in Slave mode when the Master bit, MSTR $^{(2)}$ , in the SPCON register is cleared. Before a data transmission occurs, the Slave Select pin, $\overline{SS}$ , of the Slave device must be set to'0'. $\overline{SS}$ must remain low until the transmission is complete.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      | In a Slave SPI Module, data enters the shift register under the control of the SCK from the Master SPI Module. After a Byte enters the shift register, it is immediately transferred to the receive data register in SPDAT, and the SPIF bit is set. To prevent an overflow condition, Slave software must then read the SPDAT before another Byte enters the shift register <sup>(3)</sup> . A Slave SPI must complete the write to the SPDAT (shift register) at least one bus cycle before the Master SPI starts a transmission. If the write to the data register is late, the SPI transmits the data already in the shift register from the previous transmission.                                                                                                                                                                                                                                                                               |

| Transmission Formats | Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPCON: the Clock Polarity (CPOL <sup>(4)</sup> ) and the Clock Phase (CPHA <sup>4</sup> ). CPOL defines the default SCK line level in idle state. It has no significant effect on the transmission format. CPHA defines the edges on which the input data are sampled and the edges on which the output data are shifted (Figure 60 and Figure 61). The clock phase and polarity should be identical for the Master SPI device and the communicating Slave device.                                                                                                                                                                                                                                                                                                                                                                        |

|                      | <ol> <li>The SPI Module should be configured as a Master before it is enabled (SPEN set). Also,<br/>the Master SPI should be configured before the Slave SPI.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | <ol> <li>The SPI Module should be configured as a Slave before it is enabled (SPEN set).</li> <li>The maximum frequency of the SCK for an SPI configured as a Slave is the bus clock speed.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | 4. Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN ='0').                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 132 AT89C51CC        | C03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register. This register also contains a global disable bit which must be cleared to disable all the interrupts at the same time.

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing a bit in the Interrupt Priority registers. The Table below shows the bit values and priority levels associated with each combination.

| IPH.x | IPL.x | Interrupt Level Priority |

|-------|-------|--------------------------|

| 0     | 0     | 0 (Lowest)               |

| 0     | 1     | 1                        |

| 1     | 0     | 2                        |

| 1     | 1     | 3 (Highest)              |

Table 108. Priority Level Bit Values

A low-priority interrupt can be interrupted by a high priority interrupt but not by another low-priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of the higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence, see Table 109.

| Interrupt Name                  | Interrupt Address Vector | Priority Number |

|---------------------------------|--------------------------|-----------------|

| external interrupt (INT0)       | 0003h                    | 1               |

| Timer0 (TF0)                    | 000Bh                    | 2               |

| external interrupt (INT1)       | 0013h                    | 3               |

| Timer1 (TF1)                    | 001Bh                    | 4               |

| PCA (CF or CCFn)                | 0033h                    | 5               |

| UART (RI or TI)                 | 0023h                    | 6               |

| Timer2 (TF2)                    | 002Bh                    | 7               |

| CAN (Txok, Rxok, Err or OvrBuf) | 003Bh                    | 8               |

| ADC (ADCI)                      | 0043h                    | 9               |

| CAN Timer Overflow (OVRTIM)     | 004Bh                    | 10              |

| SPI interrupt                   | 0053h                    | 11              |

Table 109.

Interrupt priority Within level

# AT89C51CC03

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter | Units |

|-------------------|------|-------------------|-----------|-------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 20          | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 20          | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 25          | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0           | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 20          | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 40          | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 60          | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 25          | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 25          | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 25          | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 25          | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 10          | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0           | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 15          | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 15          | ns    |

Table 123.

AC Parameters for a Variable Clock

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

# AT89C51CC03

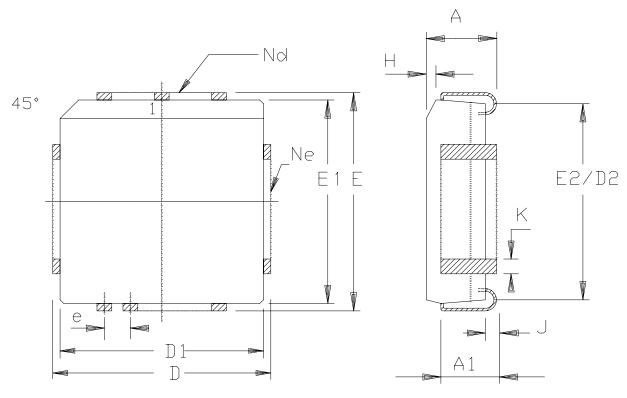

PLCC44

|         | MM     |        | INCH  |       |

|---------|--------|--------|-------|-------|

| А       | 4, 20  | 4, 57  | . 165 | . 180 |

| Α1      | 2, 29  | 3, 04  | , 090 | . 120 |

| D       | 17,40  | 17,65  | . 685 | . 695 |

| D 1     | 16, 44 | 16, 66 | , 647 | . 656 |

| D2      | 14, 99 | 16,00  | . 590 | , 630 |

| E       | 17,40  | 17,65  | , 685 | . 695 |

| E 1     | 16, 44 | 16, 66 | , 647 | . 656 |

| E2      | 14, 99 | 16.00  | . 590 | . 630 |

| e       | 1, 27  | BSC    | . 050 | BSC   |

| Η       | 1. 07  | 1.42   | . 042 | . 056 |

| J       | 0,51   | -      | . 020 | —     |

| К       | 0, 33  | 0, 53  | . 013 | . 021 |

| Nd      | 1 1    |        | 1     | 1     |

| Ne      | 1 1    |        | 1     | 1     |

| PKG STD |        | 00     |       |       |