#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | 80C51                                                                        |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CANbus, SPI, UART/USART                                                      |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 2.25K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                    |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

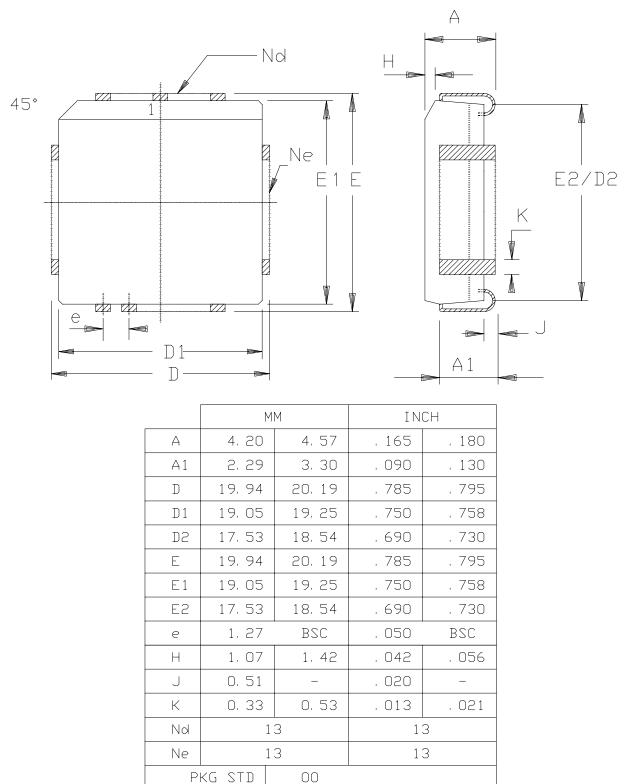

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-LQFP                                                                      |

| Supplier Device Package    | 44-VQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51cc03u-rdrim |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

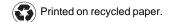

Figure 3. Port 2 Structure

- Notes: 1. Port 2 is precluded from use as general-purpose I/O Ports when as address/data bus drivers.

- 2. Port 2 internal strong pull-ups FET (P1 in FiGURE) assist the logic-one output for memory bus cycle.

When Port 0 and Port 2 are used for an external memory cycle, an internal control signal switches the output-driver input from the latch output to the internal address/data line.

# Read-Modify-Write Instructions

Some instructions read the latch data rather than the pin data. The latch based instructions read the data, modify the data and then rewrite the latch. These are called "Read-Modify-Write" instructions. Below is a complete list of these special instructions (see Table ). When the destination operand is a Port or a Port bit, these instructions read the latch rather than the pin:

| Instruction | Description                       | Example         |  |  |

|-------------|-----------------------------------|-----------------|--|--|

| ANL         | logical AND                       | ANL P1, A       |  |  |

| ORL         | logical OR                        | ORL P2, A       |  |  |

| XRL         | logical EX-OR                     | XRL P3, A       |  |  |

| JBC         | jump if bit = 1 and clear bit     | JBC P1.1, LABEL |  |  |

| CPL         | complement bit                    | CPL P3.0        |  |  |

| INC         | increment                         | INC P2          |  |  |

| DEC         | decrement                         | DEC P2          |  |  |

| DJNZ        | decrement and jump if not zero    | DJNZ P3, LABEL  |  |  |

| MOV Px.y, C | move carry bit to bit y of Port x | MOV P1.5, C     |  |  |

| CLR Px.y    | clear bit y of Port x             | CLR P2.4        |  |  |

| SET Px.y    | set bit y of Port x               | SET P3.3        |  |  |

It is not obvious the last three instructions in this list are Read-Modify-Write instructions. These instructions read the port (all 8 bits), modify the specifically addressed bit and

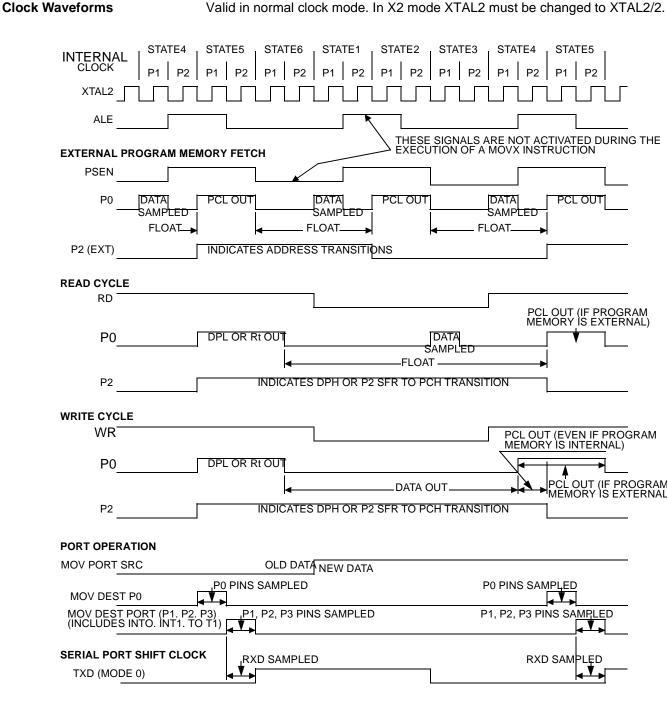

| Clock       | <ul> <li>The AT89C51CC03 core needs only 6 clock periods per machine cycle. This feature, called"X2", provides the following advantages:</li> <li>Divides frequency crystals by 2 (cheaper crystals) while keeping the same CPU power.</li> <li>Saves power consumption while keeping the same CPU power (oscillator power saving).</li> <li>Saves power consumption by dividing dynamic operating frequency by 2 in operating and idle modes.</li> <li>Increases CPU power by 2 while keeping the same crystal frequency.</li> <li>In order to keep the original C51 compatibility, a divider-by-2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by the software.</li> <li>An extra feature is available to start after Reset in the X2 mode. This feature can be enabled by a bit X2B in the Hardware Security Byte. This bit is described in the section</li> </ul> |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description | "In-System Programming".<br>The X2 bit in the CKCON register (see Table 2) allows switching from 12 clock cycles per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             | <ul><li>(STD mode).</li><li>Setting this bit activates the X2 feature (X2 mode) for the CPU Clock only (see Figure 5.).</li><li>The Timers 0, 1 and 2, Uart, PCA, WatchDog or CAN switch in X2 mode only if the cor-</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             | responding bit is cleared in the CKCON register.<br>The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on the XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 5. shows the clock generation block diagram. The X2 bit is validated on the XTAL1÷2 rising edge to avoid glitches when switching from the X2 to the STD mode. Figure 6 shows the mode switching waveforms.                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

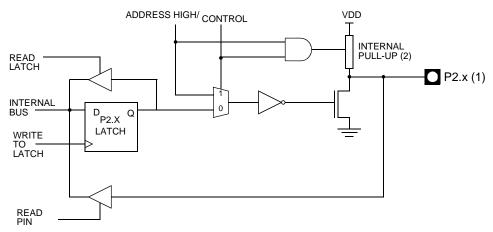

#### Figure 15. Power Fail Detect

When the power is applied, the Power Monitor immediately asserts a reset. Once the internal supply after the voltage regulator reach a safety level, the power monitor then looks at the XTAL clock input. The internal reset will remain asserted until the Xtal1 levels are above and below VIH and VIL. Further more. An internal counter will count 1024 clock periods before the reset is de-asserted.

If the internal power supply falls below a safety level, a reset is immediately asserted.

.

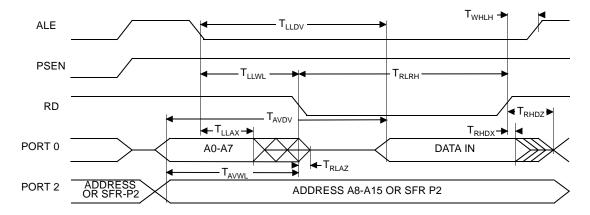

### **External Code Memory Access**

#### **Memory Interface**

The external memory interface comprises the external bus (port 0 and port 2) as well as the bus control signals (PSEN#, and ALE).

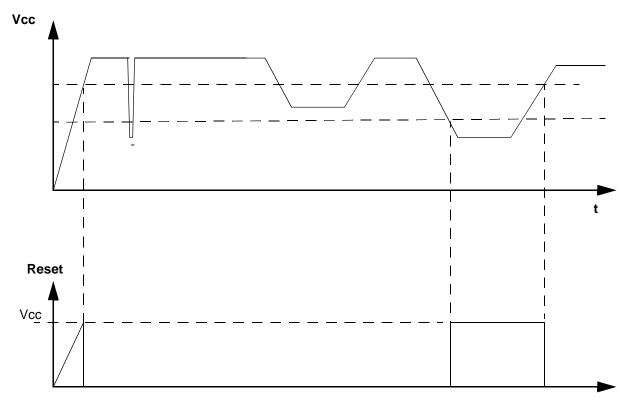

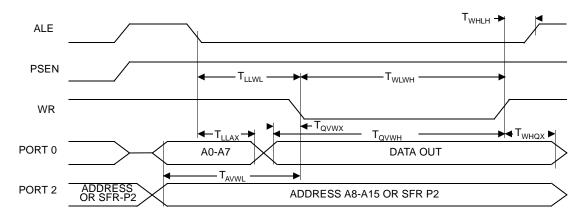

Figure 21 shows the structure of the external address bus. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0. Table 21 describes the external memory interface signals.

Figure 21. External Code Memory Interface Structure

#### Table 12. External Code Memory Interface Signals

| Signal<br>Name | Туре | Description                                                                                                                      | Alternate<br>Function |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A15:8          | 0    | Address Lines<br>Upper address lines for the external bus.                                                                       | P2.7:0                |

| AD7:0          | I/O  | Address/Data Lines<br>Multiplexed lower address lines and data for the external memory.                                          | P0.7:0                |

| ALE            | ο    | Address Latch Enable<br>ALE signals indicates that valid address information are available on lines<br>AD7:0.                    | -                     |

| PSEN#          | 0    | Program Store Enable Output<br>This signal is active low during external code fetch or external code read<br>(MOVC instruction). | -                     |

#### **External Bus Cycles**

This section describes the bus cycles the AT89C51CC03 executes to fetch code (see Figure 22) in the external program/code memory.

External memory cycle takes 6 CPU clock periods. This is equivalent to 12 oscillator clock period in standard mode or 6 oscillator clock periods in X2 mode. For further information on X2 mode see section "Clock ".

For simplicity, the accompanying figure depicts the bus cycle waveforms in idealized form and do not provide precise timing information.

For bus cycling parameters refer to the 'AC-DC parameters' section.

## AT89C51CC03

| Power Down Request       | Before entering in Power Down (Set bit PD in PCON register) the user should check that<br>no write sequence is in progress (check BUSY=0), then check that the column latches<br>are reset (FLOAD=0 in FSTA register. Launch a reset column latches to clear FLOAD if<br>necessary. |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Reading the Flash Spaces |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| User                     | The following procedure is used to read the User space:                                                                                                                                                                                                                             |  |  |  |  |

|                          | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with<br/>A+DPTR=read@.</li> </ul>                                                                                                                                                                                 |  |  |  |  |

|                          | Note: FCON is supposed to be reset when not needed.                                                                                                                                                                                                                                 |  |  |  |  |

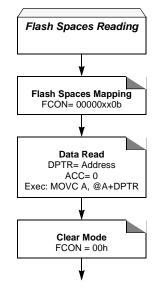

| Extra Row                | The following procedure is used to read the Extra Row space and is summarized in Figure 28:                                                                                                                                                                                         |  |  |  |  |

|                          | <ul> <li>Map the Extra Row space by writing 02h in FCON register.</li> </ul>                                                                                                                                                                                                        |  |  |  |  |

|                          | <ul> <li>Read one byte in Accumulator by executing MOVC A,@A+DPTR with A = 0 and<br/>DPTR = FF80h to FFFFh.</li> </ul>                                                                                                                                                              |  |  |  |  |

|                          | Clear FCON to unmap the Extra Row.                                                                                                                                                                                                                                                  |  |  |  |  |

| Hardware Security Byte   | The following procedure is used to read the Hardware Security space and is summarized in Figure 28:                                                                                                                                                                                 |  |  |  |  |

|                          | <ul> <li>Map the Hardware Security space by writing 04h in FCON register.</li> </ul>                                                                                                                                                                                                |  |  |  |  |

|                          | • Read the byte in Accumulator by executing MOVC A @A+DPTR with A = 0 and                                                                                                                                                                                                           |  |  |  |  |

Read the byte in Accumulator by executing MOVC A,@A+DPTR with A = 0 and DPTR = 0000h.

Figure 28. Clear FCON to unmap the Hardware Security Byte.Reading Procedure

#### Flash Protection from Parallel Programming

The three lock bits in Hardware Security Byte (see "In-System Programming" section) are programmed according to Table 17 provide different level of protection for the onchip code and data located in FM0 and FM1.

The only way to write this bits are the parallel mode. They are set by default to level 4

|                       | Boot Loader Jump Bit (BLJB):<br>- This bit indicates if on RESET the user wants to jump to this application at address<br>@0000h on FM0 or execute the boot loader at address @F800h on FM1.<br>- BLJB = 0 on parts delivered with bootloader programmed.<br>- To read or modify this bit, the APIs are used. |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Boot Vector Address (SBV):<br>- This byte contains the MSB of the user boot loader address in FM0.<br>- The default value of SBV is FCh (no user boot loader in FM0).<br>- To read or modify this byte, the APIs are used.                                                                                    |

|                       | Extra Byte (EB) and Boot Status Byte (BSB):<br>- These Bytes are reserved for customer use.<br>- To read or modify these Bytes, the APIs are used.                                                                                                                                                            |

| Hardware Boot Process | At the falling edge of RESET, the bit ENBOOT in AUXR1 register is initialized with the value of Boot Loader Jump Bit (BLJB).                                                                                                                                                                                  |

|                       | Further at the falling edge of RESET if the following conditions (called Hardware condi-<br>tion) are detected:                                                                                                                                                                                               |

|                       | PSEN low,                                                                                                                                                                                                                                                                                                     |

|                       | EA high,                                                                                                                                                                                                                                                                                                      |

|                       | ALE high (or not connected).                                                                                                                                                                                                                                                                                  |

|                       | <ul> <li>After Hardware Condition the FCON register is initialized with the value 00h<br/>and the PC is initialized with F800h (FM1).</li> </ul>                                                                                                                                                              |

|                       | The Hardware condition makes the bootloader to be executed, whatever BLJB value is.                                                                                                                                                                                                                           |

|                       | If no hardware condition is detected, the FCON register is initialized with the value F0h.                                                                                                                                                                                                                    |

|                       | Check of the BLJB value.                                                                                                                                                                                                                                                                                      |

|                       | • If bit BLJB = 1:                                                                                                                                                                                                                                                                                            |

|                       | User application in FM0 will be started at @0000h (standard reset).                                                                                                                                                                                                                                           |

|                       | <ul> <li>If bit BLJB = 0:<br/>Boot loader will be started at @F800h in FM1.</li> </ul>                                                                                                                                                                                                                        |

|                       | <ol> <li>Note: 1. As PSEN is an output port in normal operating mode (running user applications or<br/>bootloader applications) after reset it is recommended to release PSEN after the fall-<br/>ing edge of Reset is signaled.</li> </ol>                                                                   |

The hardware conditions are sampled at reset signal Falling Edge, thus they can be released at any time when reset input is low.

2. To ensure correct microcontroller startup, the PSEN pin should not be tied to ground during power-on.

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Registers

Table 25. SCON Register

SCON (S:98h) Serial Control Register

| 7             | 6               | 5                                                                                                                               | 4                                                                                                                                                                                  | 3                        | 2                                  | 1                                             | 0  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------|-----------------------------------------------|----|--|--|

| FE/SM0        | SM1             | SM2                                                                                                                             | REN                                                                                                                                                                                | TB8                      | RB8                                | ТІ                                            | RI |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                     |                                                                                                                                                                                    |                          |                                    |                                               |    |  |  |

| 7             | FE              | Clear to rese                                                                                                                   |                                                                                                                                                                                    | ,                        | d by a valid sto<br>t is detected. | op bit.                                       |    |  |  |

|               | SM0             | •                                                                                                                               | <b>Node bit 0 (S</b><br>I for serial por                                                                                                                                           | MOD0=0)<br>t mode select | ion.                               |                                               |    |  |  |

| 6             | SM1             | Serial port M           SM0         SM1           0         0           0         1           1         0           1         1 |                                                                                                                                                                                    |                          |                                    |                                               |    |  |  |

| 5             | SM2             | Clear to disa                                                                                                                   | ble multiproce                                                                                                                                                                     | essor commur             | nication feature                   | <b>ion Enable b</b> i<br>e.<br>n mode 2 and 2 |    |  |  |

| 4             | REN             |                                                                                                                                 | i <b>nable bit</b><br>ble serial rece<br>e serial recept                                                                                                                           |                          |                                    |                                               |    |  |  |

| 3             | TB8             | Clear to trans                                                                                                                  | Bit 8/Ninth b<br>smit a logic 0<br>hit a logic 1 in                                                                                                                                | in the 9th bit.          | in modes 2 a                       | ind 3                                         |    |  |  |

| 2             | RB8             | Cleared by h                                                                                                                    | Receiver Bit 8/Ninth bit received in modes 2 and 3<br>Cleared by hardware if 9th bit received is a logic 0.<br>Set by hardware if 9th bit received is a logic 1.                   |                          |                                    |                                               |    |  |  |

| 1             | ті              | Clear to ackr<br>Set by hardw                                                                                                   | Transmit Interrupt flag<br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0 or at the beginning of the<br>stop bit in the other modes.  |                          |                                    |                                               |    |  |  |

| 0             | RI              | Clear to ackr<br>Set by hardw                                                                                                   | <b>Receive Interrupt flag</b><br>Clear to acknowledge interrupt.<br>Set by hardware at the end of the 8th bit time in mode 0, see Figure 33. and<br>Figure 34. in the other modes. |                          |                                    |                                               |    |  |  |

Reset Value = 0000 0000b Bit addressable

#### Table 26. SADEN Register

SADEN (S:B9h) Slave Address Mask Register

| 7             | 6               | 5                                      | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|----------------------------------------|---|---|---|---|---|

| -             | -               | -                                      | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                            |   |   |   |   |   |

| 7-0           |                 | Mask Data for Slave Individual Address |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

Table 27. SADDR Register

SADDR (S:A9h) Slave Address Register

| 7             | 6               | 5                        | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|--------------------------|---|---|---|---|---|

| -             | -               | -                        | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |   |   |   |   |

| 7-0           |                 | Slave Individual Address |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

#### Table 28. SBUF Register

SBUF (S:99h) Serial Data Buffer

| 7             | 6               | 5                                     | 4 | 3 | 2 | 1 | 0 |

|---------------|-----------------|---------------------------------------|---|---|---|---|---|

| _             | -               | -                                     | - | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description                           |   |   |   |   |   |

| 7-0           |                 | Data sent/received by Serial I/O Port |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Table 35. TL1 Register

TL1 (S:8Bh) Timer 1 Low Byte Register

| 7             | 6               | 5           | 4        | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|----------|---|---|---|---|

| -             | -               | -           | -        | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |          |   |   |   |   |

| 7:0           |                 | Low Byte of | Timer 1. |   |   |   |   |

Reset Value = 0000 0000b

Table 45. WDTRST Register

WDTRST (S:A6h Write only) Watchdog Timer Enable Register

| 7             | 6               | 5           | 4            | 3 | 2 | 1 | 0 |

|---------------|-----------------|-------------|--------------|---|---|---|---|

| -             | -               | -           | -            | - | - | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description |              |   |   |   |   |

| 7             | -               | Watchdog Co | ontrol Value |   |   |   |   |

Reset Value = 1111 1111b

Note: The WDRST register is used to reset/enable the WDT by writing 1EH then E1H in sequence without instruction between these two sequences.

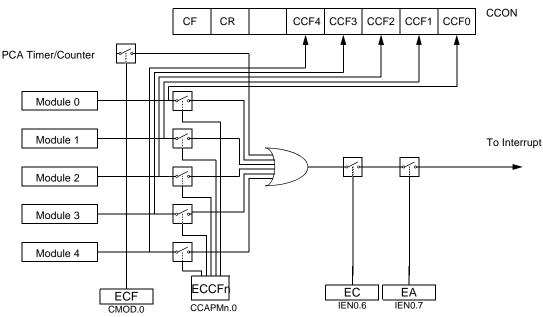

Each module in the PCA has a special function register associated with it (CCAPM0 for module 0 ...). The CCAPM0:4 registers contain the bits that control the mode that each module will operate in.

- The ECCF bit enables the CCF flag in the CCON register to generate an interrupt when a match or compare occurs in the associated module.

- The PWM bit enables the pulse width modulation mode.

- The TOG bit when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register.

- The match bit MAT when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

- The two bits CAPN and CAPP in CCAPMn register determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled.

- The bit ECOM in CCAPM register when set enables the comparator function.

## **PCA Interrupt**

#### Figure 68. PCA Interrupt System

#### **PCA Capture Mode**

To use one of the PCA modules in capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated.

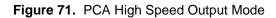

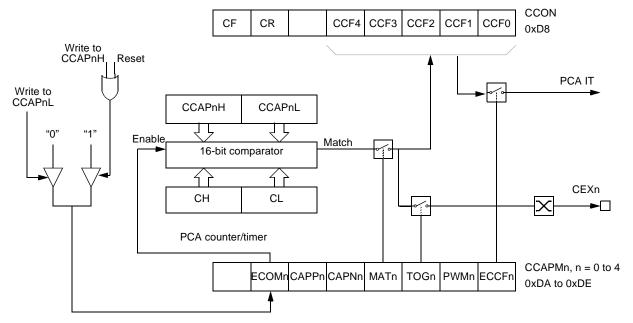

## High Speed Output Mode

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set.

# Pulse Width Modulator Mode

All the PCA modules can be used as PWM outputs. The output frequency depends on the source for the PCA timer. All the modules will have the same output frequency because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than it, the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows the PWM to be updated without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

## AT89C51CC03

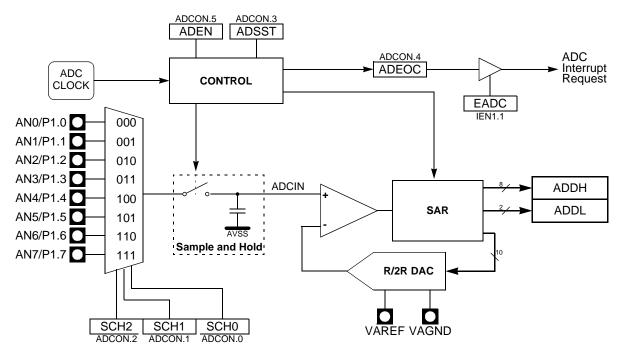

#### Figure 73. ADC Description

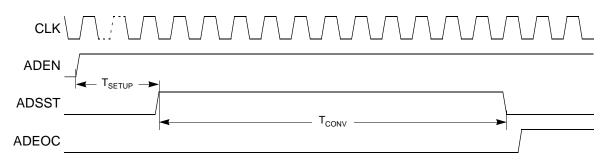

Figure 74 shows the timing diagram of a complete conversion. For simplicity, the figure depicts the waveforms in idealized form and do not provide precise timing information. For ADC characteristics and timing parameters refer to the Section "AC Characteristics" of the AT89C51CC03 datasheet.

#### Figure 74. Timing Diagram

Note: Tsetup min = 4 us

Tconv=11 clock ADC = 1sample and hold + 10 bit conversion The user must ensure that 4 us minimum time between setting ADEN and the start of the first conversion.

## Registers

#### Table 103. ADCF Register

ADCF (S:F6h) ADC Configuration

| 7             | 6               | 5            | 4                                                                                                 | 3    | 2    | 1    | 0    |

|---------------|-----------------|--------------|---------------------------------------------------------------------------------------------------|------|------|------|------|

| CH 7          | CH 6            | CH 5         | CH 4                                                                                              | CH 3 | CH 2 | CH 1 | CH 0 |

| Bit<br>Number | Bit<br>Mnemonic | Description  |                                                                                                   |      |      |      |      |

| 7-0           | CH 0:7          | Set to use P | Channel Configuration<br>Set to use P1.x as ADC input.<br>Clear to use P1.x as standart I/O port. |      |      |      |      |

Reset Value =0000 0000b

#### Table 104. ADCON Register

ADCON (S:F3h) ADC Control Register

| 7             | 6               | 5                                             | 4                                                                                                                                                 | 3                      | 2              | 1    | 0    |

|---------------|-----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|------|------|

| -             | PSIDLE          | ADEN                                          | ADEOC                                                                                                                                             | ADSST                  | SCH2           | SCH1 | SCH0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   |                                                                                                                                                   |                        |                |      |      |

| 7             | -               |                                               |                                                                                                                                                   |                        |                |      |      |

| 6             | PSIDLE          | Set to put in                                 | Mode (Best<br>idle mode dur<br>vert without id                                                                                                    | ing conversion         | n              |      |      |

| 5             | ADEN            | Enable/Stan<br>Set to enable<br>Clear for Sta | ADC                                                                                                                                               | ower dissipati         | on 1 uW).      |      |      |

| 4             | ADEOC           | Set by hardwinterrupt.                        | End Of Conversion<br>Set by hardware when ADC result is ready to be read. This flag can generate an<br>interrupt.<br>Must be cleared by software. |                        |                |      |      |

| 3             | ADSST           |                                               | n A/D convers                                                                                                                                     | sion.<br>completion of | the conversion | on   |      |

| 2-0           | SCH2:0          | Selection of see Table 10                     | <b>Channel to (</b><br>2                                                                                                                          | Convert                |                |      |      |

Reset Value =X000 0000b

Table 105. ADCLK Register

ADCLK (S:F2h) ADC Clock Prescaler

| 7             | 6               | 5                                      | 4                                                                                    | 3     | 2     | 1     | 0     |

|---------------|-----------------|----------------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|-------|

| -             | -               | -                                      | PRS 4                                                                                | PRS 3 | PRS 2 | PRS 1 | PRS 0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                            |                                                                                      |       |       |       |       |

| 7-5           | -               | Reserved<br>The value re               | Reserved<br>The value read from these bits are indeterminate. Do not set these bits. |       |       |       |       |

| 4-0           | PRS4:0          | Clock Preso<br>See Note <sup>(1)</sup> | aler                                                                                 |       |       |       |       |

Reset Value = XXX0 0000b

Note:

1. In X1 mode: For PRS > 0  $F_{ADC} = \frac{EXTAL}{4xPRS}$ For PRS = 0  $F_{ADC} = \frac{FXTAL}{128}$ In X2 mode: For PRS > 0  $F_{ADC} = \frac{FXTAL}{2xPRS}$ For PRS = 0  $F_{ADC} = \frac{FXTAL}{64}$

Table 106. ADDH Register

ADDH (S:F5h Read Only) ADC Data High Byte Register

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADAT 9 | ADAT 8 | ADAT 7 | ADAT 6 | ADAT 5 | ADAT 4 | ADAT 3 | ADAT 2 |

| Bit    | Bit    |        |        |        |        |        |        |

| Number | Mnemonic | Description            |

|--------|----------|------------------------|

| 7-0    | ADAT9:2  | ADC result<br>bits 9-2 |

Reset Value = 00h

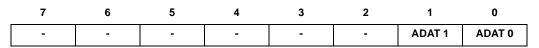

Table 107. ADDL Register

ADDL (S:F4h Read Only) ADC Data Low Byte Register

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

| Ambiant Temperature Under Bias:                                      |  |  |  |  |

|----------------------------------------------------------------------|--|--|--|--|

| I = industrial40°C to $85^{\circ}$ C<br>A = automotive40°C to +125°C |  |  |  |  |

| Voltage on $V_{CC}$ from $V_{SS}$ 0.5V to + 6V                       |  |  |  |  |

| Voltage on Any Pin from $V_{SS}$ -0.5V to $V_{CC}$ + 0.2V            |  |  |  |  |

| Power Dissipation1 W                                                 |  |  |  |  |

Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

The power dissipation is based on the maximum allowable die temperature and the thermal resistance of the package.

## **ICCOP Test Conditions**

Power Consumption<br/>ManagementSince the introduction of the first C51 device, every manufacturer made operating I<sub>CC</sub><br/>measurements under Reset, which made sense for the designs where the CPU was<br/>running under reset. In our new devices, the CPU is no longer active during reset, so the<br/>power consumption is very low but not representative of what will happen in the cus-<br/>tomer system. Thus, while keeping measurements under Reset, we present a new way<br/>to measure the operating I<sub>CC</sub>.<br/>Using an internal test ROM, the following code is executed.<br/>Label: SJMP Label (80FE)<br/>Ports 1 and 4 are disconnected, RST = Vcc, XTAL2 is not connected and XTAL1 is<br/>driven by the clock.

This is much more representative of the real operating Icc.

### **DC Parameters for Standard Voltage**

Industrial  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ;  $V_{SS} = 0V$ ; Automotive  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ ;  $V_{SS} = 0V$

Automotive  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C,  $v_{SS} = 0^{\circ}$

$V_{CC}$  =3.0V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only)

Table 116. DC Parameters in Standard Voltage

| Symbol           | Parameter                                            | Min                       | Typ <sup>(5)</sup> | Мах                   | Unit | Test Conditions                                                                                                      |

|------------------|------------------------------------------------------|---------------------------|--------------------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                    | -0.5                      |                    | 0.2Vcc - 0.1          | V    |                                                                                                                      |

| V <sub>IH</sub>  | Input High Voltage except XTAL1, RST                 | 0.2 V <sub>CC</sub> + 0.9 |                    | V <sub>CC</sub> + 0.5 | V    |                                                                                                                      |

| V <sub>IH1</sub> | Input High Voltage, XTAL1, RST                       | 0.7 V <sub>CC</sub>       |                    | V <sub>CC</sub> + 0.5 | V    |                                                                                                                      |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3 and $4^{(6)}$      |                           |                    | 0.3<br>0.45<br>1.0    | V    | $\begin{split} I_{OL} &= 100 \; \mu A^{(4)} \\ I_{OL} &= 1.6 \; m A^{(4)} \\ I_{OL} &= 3.5 \; m A^{(4)} \end{split}$ |

| V <sub>OL1</sub> | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup> |                           |                    | 0.3<br>0.45<br>1.0    | V    | $\begin{split} I_{OL} &= 200 \; \mu A^{(4)} \\ I_{OL} &= 3.2 \; m A^{(4)} \\ I_{OL} &= 7.0 \; m A^{(4)} \end{split}$ |

#### **External Data Memory Write Cycle**

### **External Data Memory Read Cycle**

#### Serial Port Timing – Shift Register Mode

#### Table 124. Symbol Description (F = 40 MHz)

| Symbol            | Parameter                                |

|-------------------|------------------------------------------|

| T <sub>XLXL</sub> | Serial port clock cycle time             |

| T <sub>QVHX</sub> | Output data set-up to clock rising edge  |

| T <sub>XHQX</sub> | Output data hold after clock rising edge |

| T <sub>XHDX</sub> | Input data hold after clock rising edge  |

| T <sub>XHDV</sub> | Clock rising edge to input data valid    |

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A=25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

## AT89C51CC03

PLCC52

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectualproperty right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORYWAR-RANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICU-LARPURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMA-TION) ARISING OUTOF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAM-AGES. Atmel makes norepresentationsor warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specificationsand product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

©2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are registered trademarks, or the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.